Cadence IC 设计实验

中国科技大学

电子科学与技术系 IC 教研组

黄鲁 胡新伟 白雪飞

2005 年 10 月

(实验例题由 Cadence 公司提供)

致 谢!

电子科学技术系刘烃海、矫逸书、祝超、梅汪生等同学帮助编写了部分实验章节;信

息实验中心屈玉贵主任和方毅、周远远、刘贵英等老师不仅为实验提供了技术支持,准备

好 EDA 软件 licence、配置了计算机和软件运行环境,而且热情参与了本实验教学。对于上

述老师和同学们的辛勤工作和所做出的贡献,在此一并表示衷心地感谢!

预备知识:UNIX

你掌握 UNIX 操作系统的基本命令吗?下面几条常用命令可能会对你有用处。提醒一

下,UNIX 命令是区分大小写的。

查文件:ls (不显示隐含文件)、la (或 ls –a,显示所有文件)、ls |mpre(帧显)、la |more

删文件:rm 文件名

建新目录:mkdir 目录名

删目录:\rm –r 目录名 ( 慎用!!!)

拷贝:cp 源文件名(含路径)目标文件名(含路径),

例 将 isc 用户的 abc.suf 文件拷贝到自己的当前目录下:cp ~isc/abc.suf .

解.tar 打包文件:tar vxf 打包文件名

解.tar.Z 压缩文件:tar vxfZ 压缩文件名

文件改名: mv 原文件名 新文件名

查命令与参数功能:man 命令

***************************************************************************

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为功能键;“单

击”指鼠标左键按下一次。

****************************************************************************

1

�

实验一、Virtuoso Schematic Editor

实验目的:掌握电原理图(schematic)设计输入方法。

边学边做

[1]启动 IC Design 软件:

开机后运行 Exceed 进入服务器 SOLARIS 登录界面,输入用户名和密码

(由系统管理员提供);

点击一下 cpu disk 菜单项上方的三角箭头,点击 This Host 出现Terminal 窗口,(或点击 Console

出现 Console 窗口);

cp /eva01/cdsmgr/ training_IC_data/SchemEd.tar . (提醒:最后是个小点,稍等)

tar vxf SchemEd.tar (稍等)

cd adelabic5

icfb & (或 icms &,你知道后缀&的作用吗?在 UNIX 命令后加&表示后台运行)

若出现“What’s New”窗口,关掉它。

出现“icfb-log:/…”窗口(CIW:Command Interpreter Window)了吗?

[2]建立新库、新单元以及新视图(view):

在 CIW 中,File->New->Library,

在弹出的“New Library”窗口,Name 栏中:mylib

选中右下方:* Don’t need techfile

OK

查看 CIW 窗口:Tools->Library Manager,在 Library 中应有 mylib,单击它。

在 Library Manager 窗口,File->New->Cellview,

在弹出的“Create New File”窗口 Cell Name 栏中,nand2

Tool 栏中,选 Composer-Schematic

OK

[3]添加元件(实例 instance)

在弹出的“Virtuoso Schematic Editing:…”窗口中,左边为工具栏,选 instance 图标(或 i)

单击“Add instance”窗口 Library 栏最右侧 Browser,

弹出“Library Browser-…”窗口,Library 选 analogLib,Cell 选 nmos4, View 选 symbol

鼠标回到“Add instance”窗口,Model name 栏:trnmos, width: 3.0u , Length: 0.5u,Hide

在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,

这样就增加了 2 个 nmos4 元件,ESC(试一试:先选中一个元件,再 q ,查看/改变属性)。

仿照上述方法,增加 pmos4 元件。在“Add instance”窗口,Model name 栏:trpmos,

width: 2.0u , Length: 0.5u;放置 2 个 pmos4,ESC。(试一试热键 f,[,]的功能)

[4]添加管脚(PIN)

2

�

选“Virtuoso Schematic Editing:…”窗口左边工具栏中的 Pin 图标(或 p)

在“Add Pin”窗口中,Pin Names:INA INB,Direction 选 input, Usage 选 schematic,Hide

在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,

放置 2 个输入 PIN,

p,在“Add Pin”窗口中,Pin Names:OUT,Direction 选 output, Usage 选 schematic,在“Virtuoso

Schematic Editing:…”窗口放置输出 PIN,

[5]添加电源和地:

i (或单击 instance 工具图标)

弹出“Add instance”窗口,Browse,Library 选 analogLib,Cell 栏:vdd, View 选 symbol

在“Virtuoso Schematic Editing:…”窗口放置 vdd,

回到“Add instance”窗口,Browse,Cell 栏:gnd, 在“Virtuoso Schematic Editing:…”窗口

放置 gnd,

ESC , Cancel 掉“Add instance”窗口。

[6]摆放元件并加网线:

参照下图放好元件(symbol):(移动用 m 键,删除用 Delete 键,取消命令用 ESC 键)

选“Virtuoso Schematic Editing:…”窗口左边工具栏中的 Wire(narrow),连好网线,ESC

[7]保存文件:“Virtuoso Schematic Editing:…”窗口左上角 Check and Save 工具。

DIY(Do It Yourself)

3

�

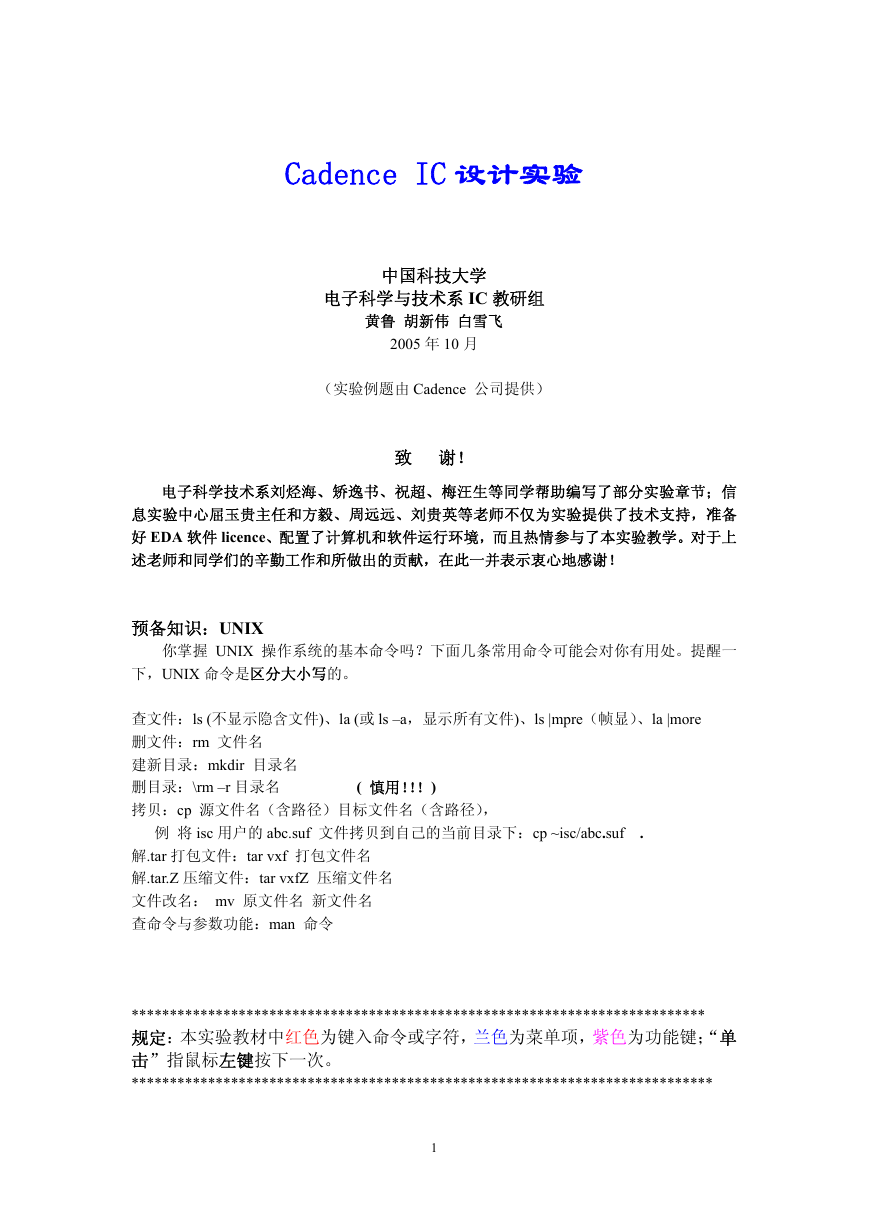

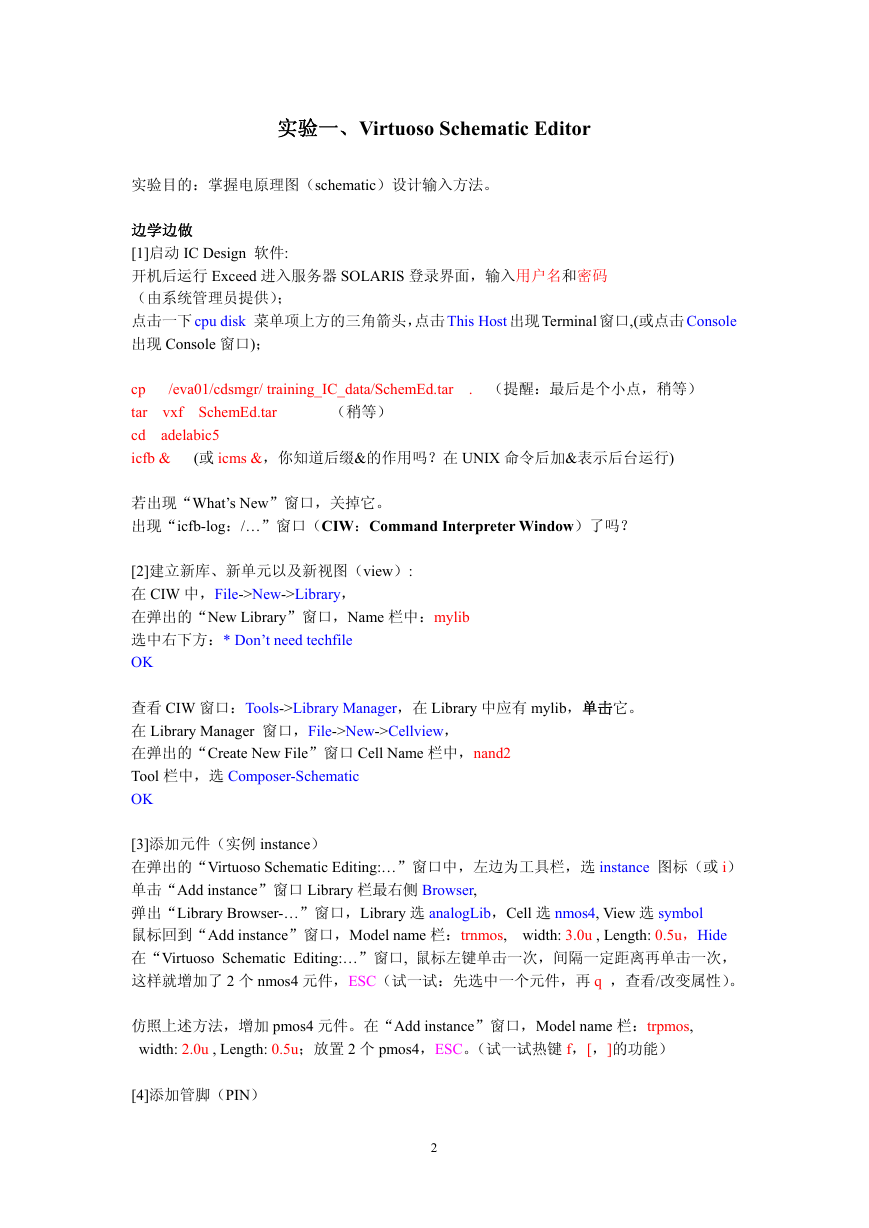

在 mylib 库中建立 amplifier 单元(Cell)如下图所示。

For Q0,Q1:Model Name=trnpn

For Q2,Q3,Q4:Model Name=trpnp

For M1: Model Name=trpmos, Length=8u, Width=iPar(“l”)*16

For M2,M5: Model Name=trnmos, Length=10u, Width=100u

For M3: Model Name=trpmos, Length=iPar(“w”)/16, Width=128u

Resistance=2.5K

Capacitance=CAP (设计变量)

注意 vss 是负电源,不是 gnd

图中所有单元来自 analoglib 库,参数如下表:

Cell Name 属性 properties

npn

pnp

pmos4

nmos4

pmos4

res

cap

vdd, vss

PIN 管脚: 输入管脚: iref, inm, inp, 输出管脚: out

Wire Name

注意:你画的 schematic 电路中,双极晶体管 Q 和 FET 管 M 的下标编号可能与上图不同,

可用 q 查看/改变属性,另外可能使用 m (移动),r(旋转),f(全屏),先 m 再 shift + r (左

右翻转),先 m 再 Ctrl + r (上下翻转)等命令。

ESC(终止操作)

标注线网名:用 Wire Name 工具(或 l)将 M1 与 M3 的衬底连线、M2 与 M5 的栅极连线

vdd! , gnode

4

�

分别标注为 vdd!和 gnode。

如发生了错误删除,用“Virtuoso Schematic Editing:…”窗口左边中间的 undo 工具(或 u),

注意:只能恢复前一个被删除的对象。最后 check and save.

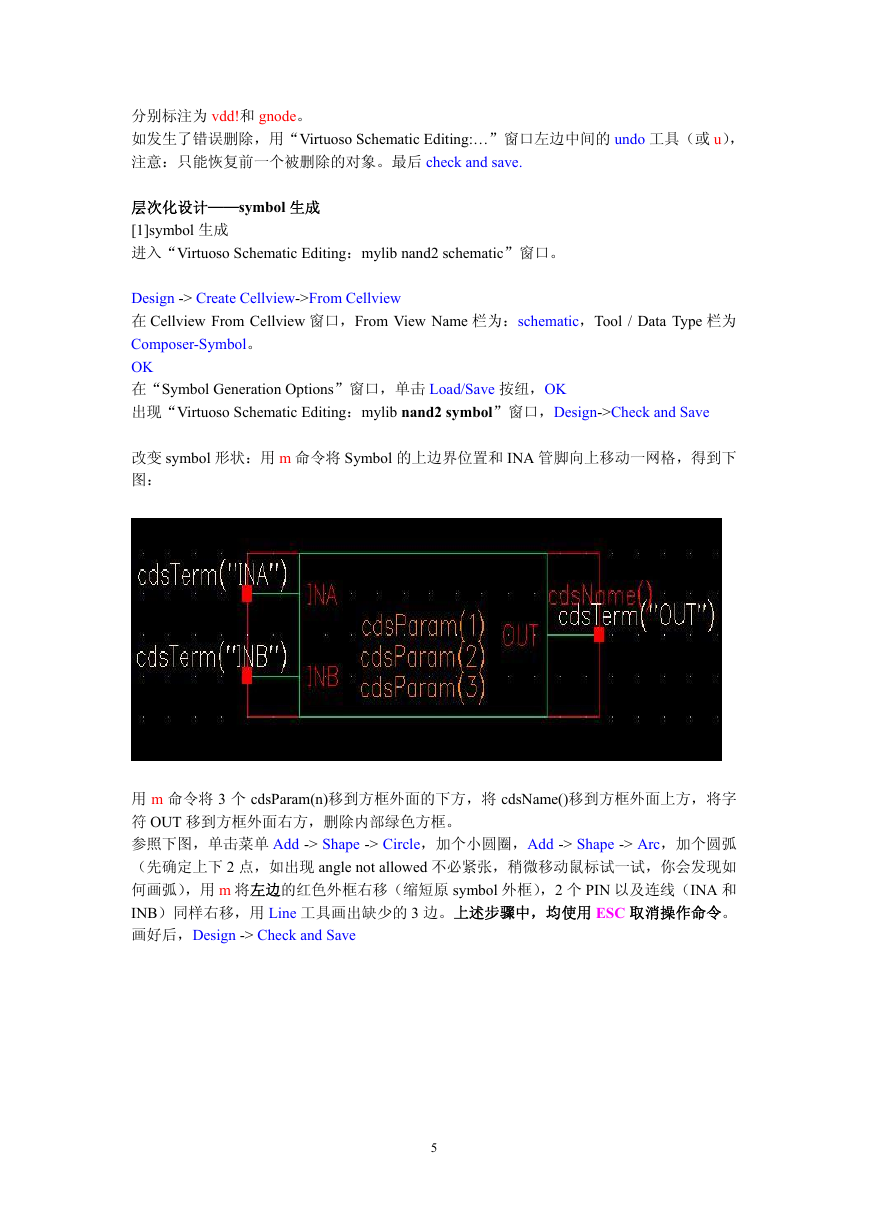

层次化设计——symbol 生成

[1]symbol 生成

进入“Virtuoso Schematic Editing:mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

在 Cellview From Cellview 窗口,From View Name 栏为:schematic,Tool / Data Type 栏为

Composer-Symbol。

OK

在“Symbol Generation Options”窗口,单击 Load/Save 按纽,OK

出现“Virtuoso Schematic Editing:mylib nand2 symbol”窗口,Design->Check and Save

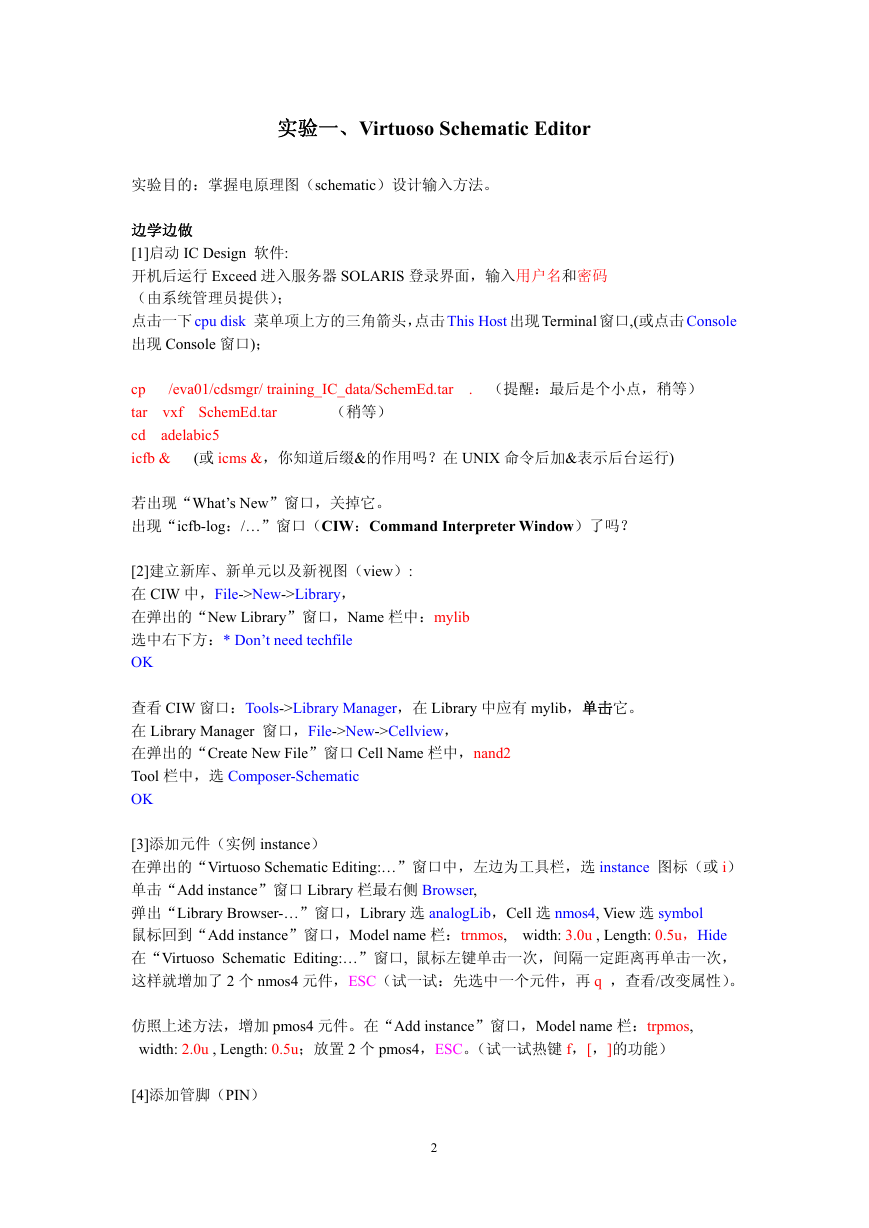

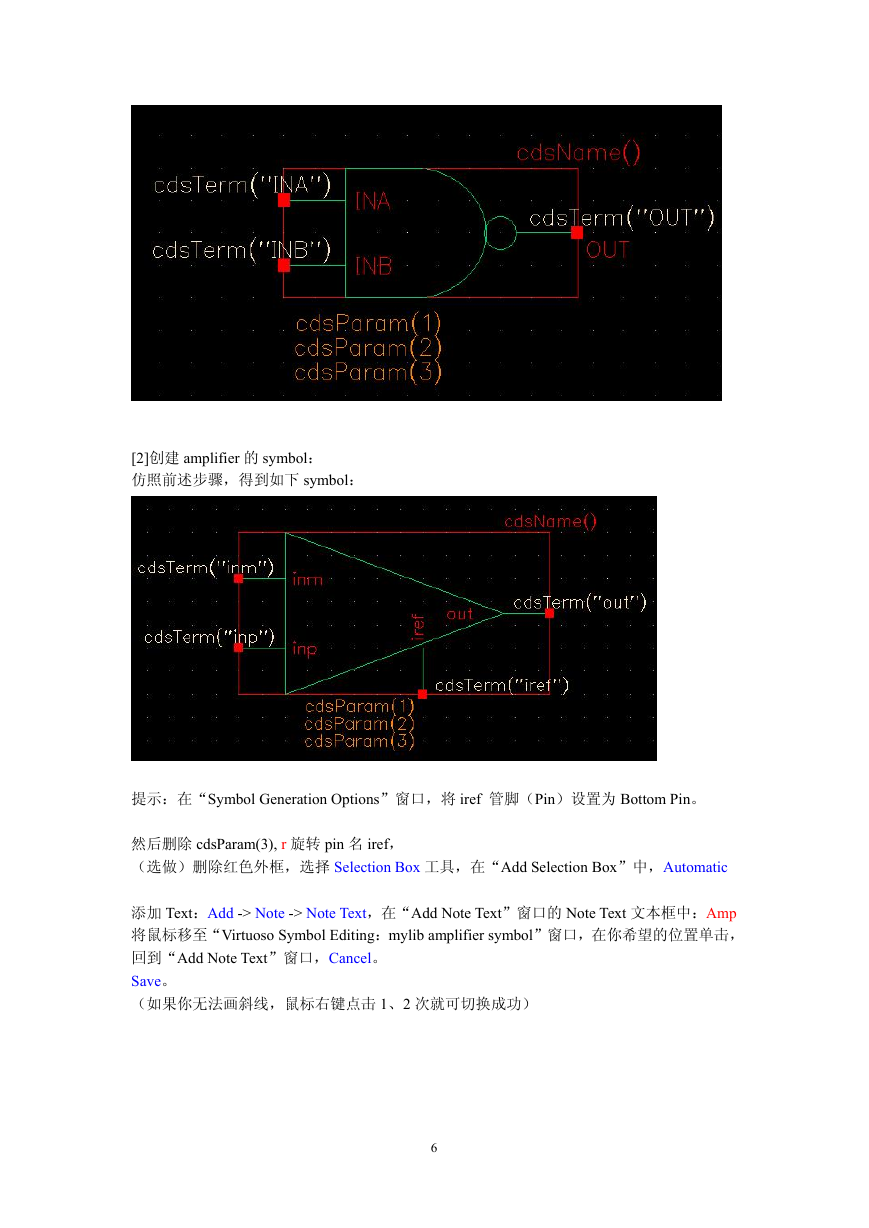

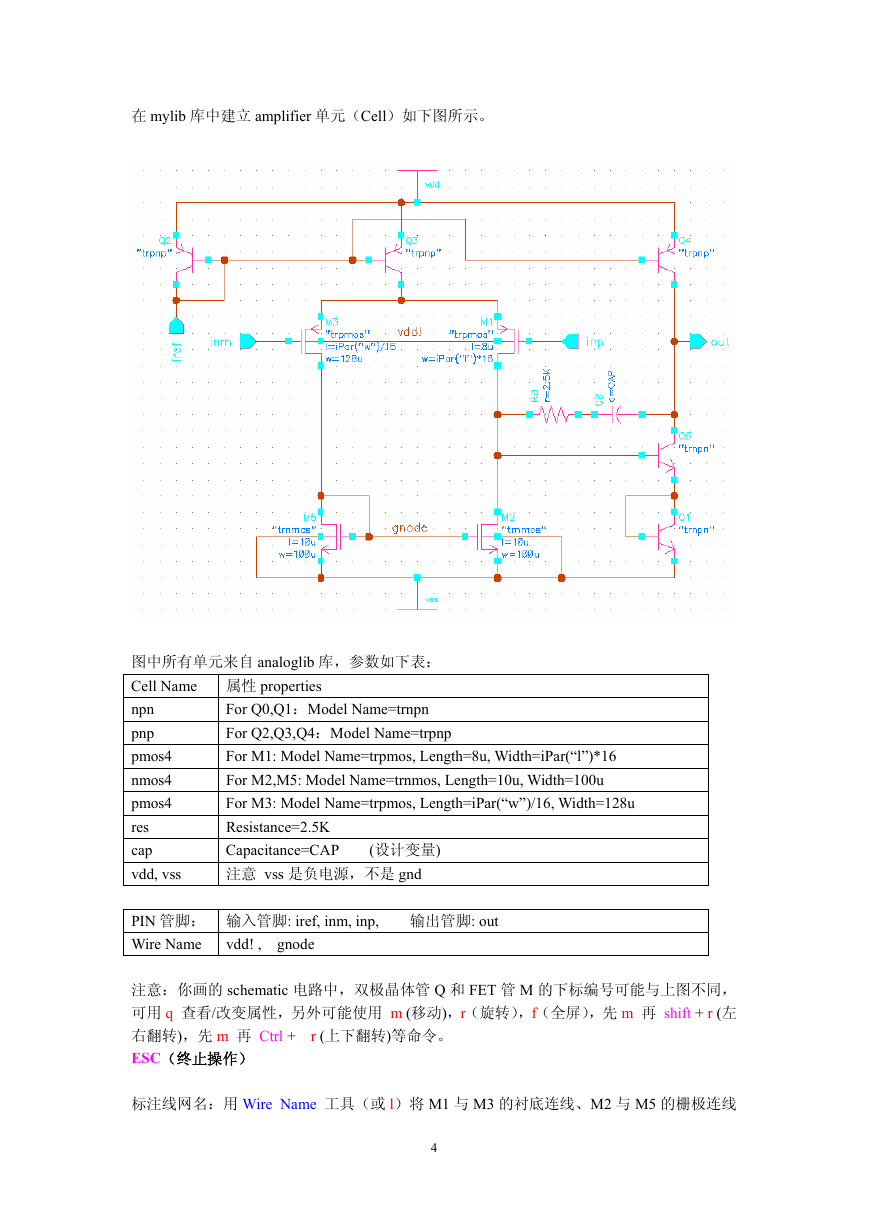

改变 symbol 形状:用 m 命令将 Symbol 的上边界位置和 INA 管脚向上移动一网格,得到下

图:

用 m 命令将 3 个 cdsParam(n)移到方框外面的下方,将 cdsName()移到方框外面上方,将字

符 OUT 移到方框外面右方,删除内部绿色方框。

参照下图,单击菜单 Add -> Shape -> Circle,加个小圆圈,Add -> Shape -> Arc,加个圆弧

(先确定上下 2 点,如出现 angle not allowed 不必紧张,稍微移动鼠标试一试,你会发现如

何画弧),用 m 将左边的红色外框右移(缩短原 symbol 外框),2 个 PIN 以及连线(INA 和

INB)同样右移,用 Line 工具画出缺少的 3 边。上述步骤中,均使用 ESC 取消操作命令。

画好后,Design -> Check and Save

5

�

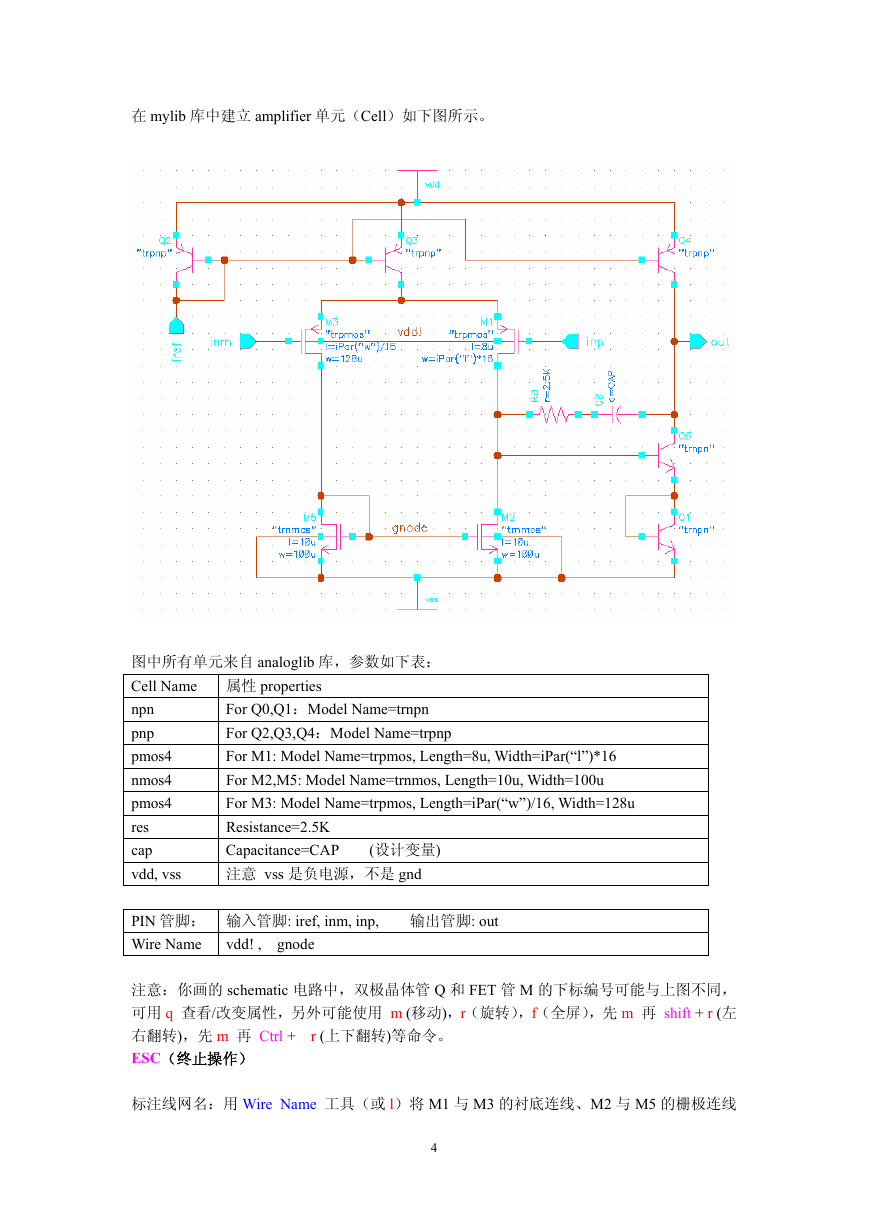

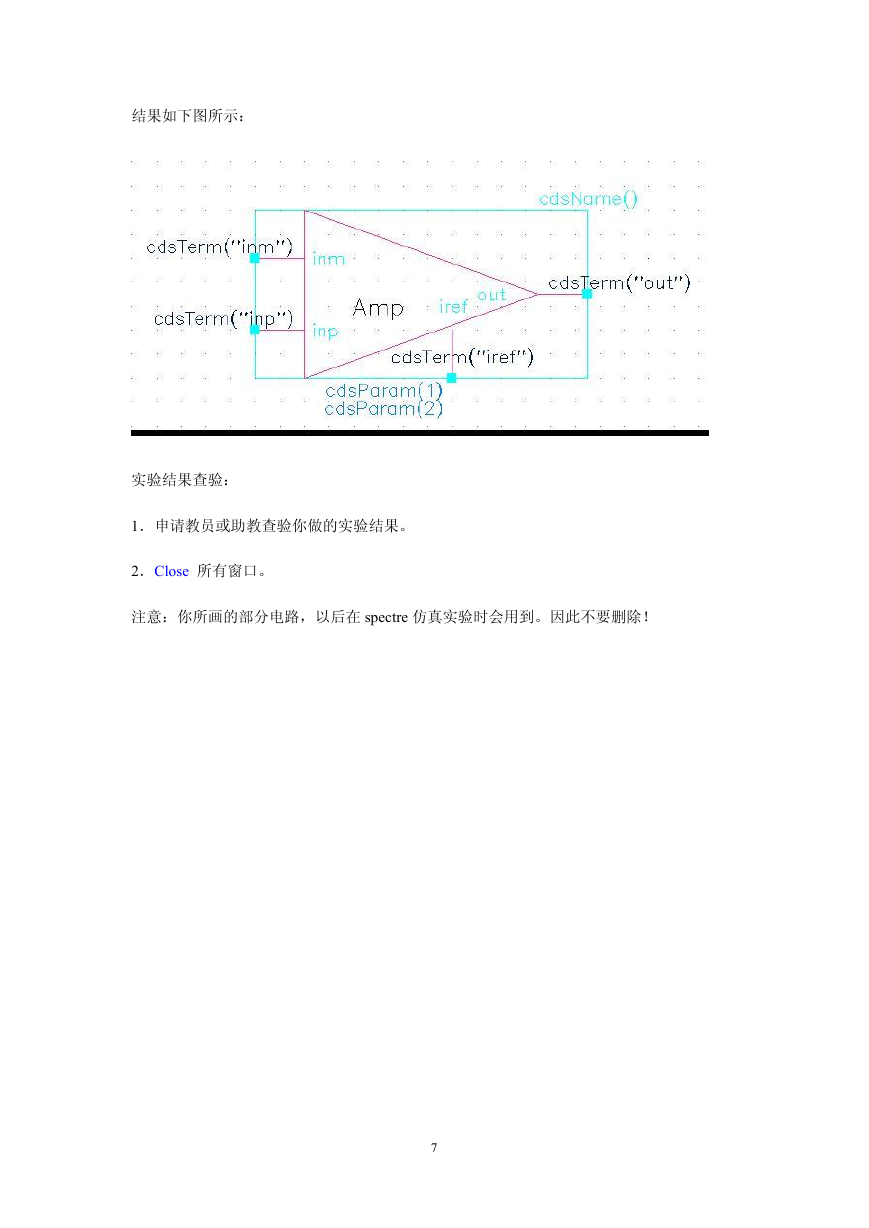

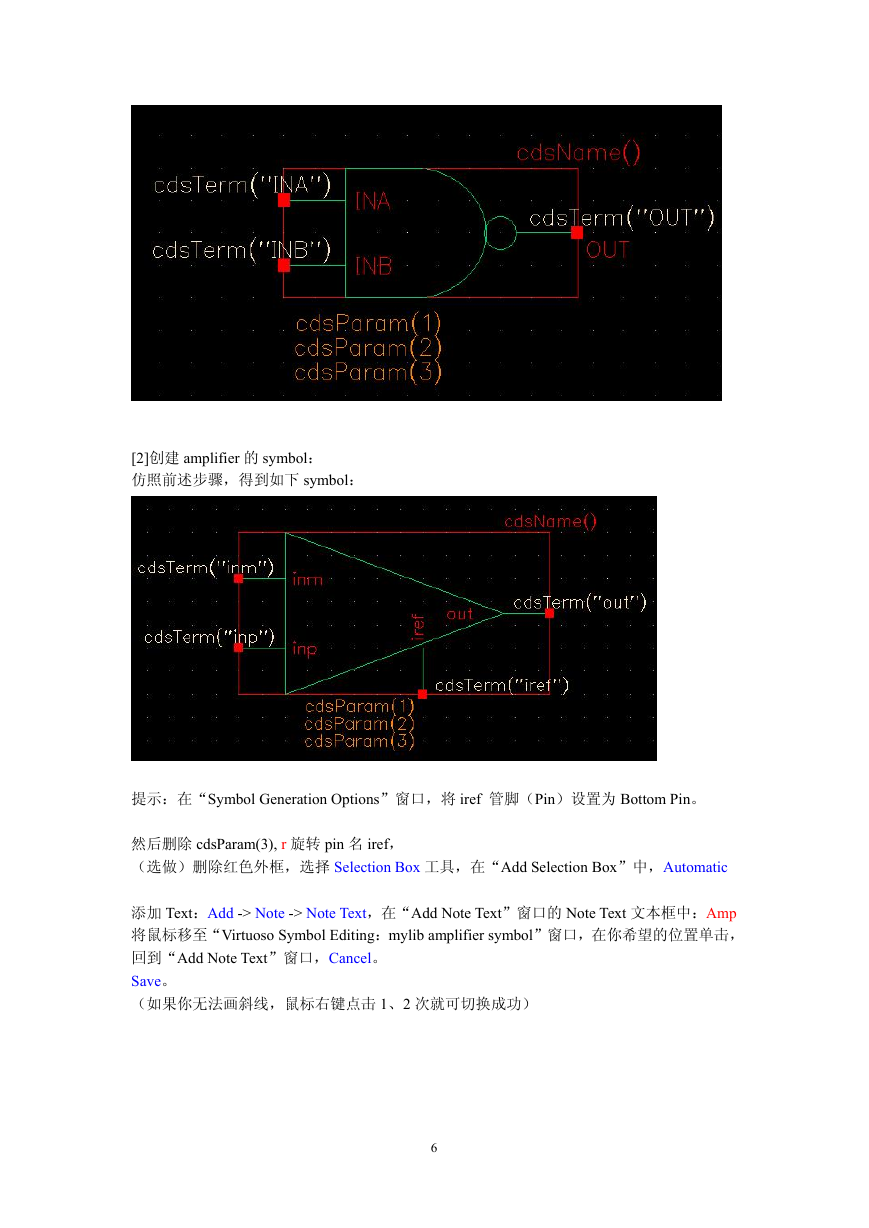

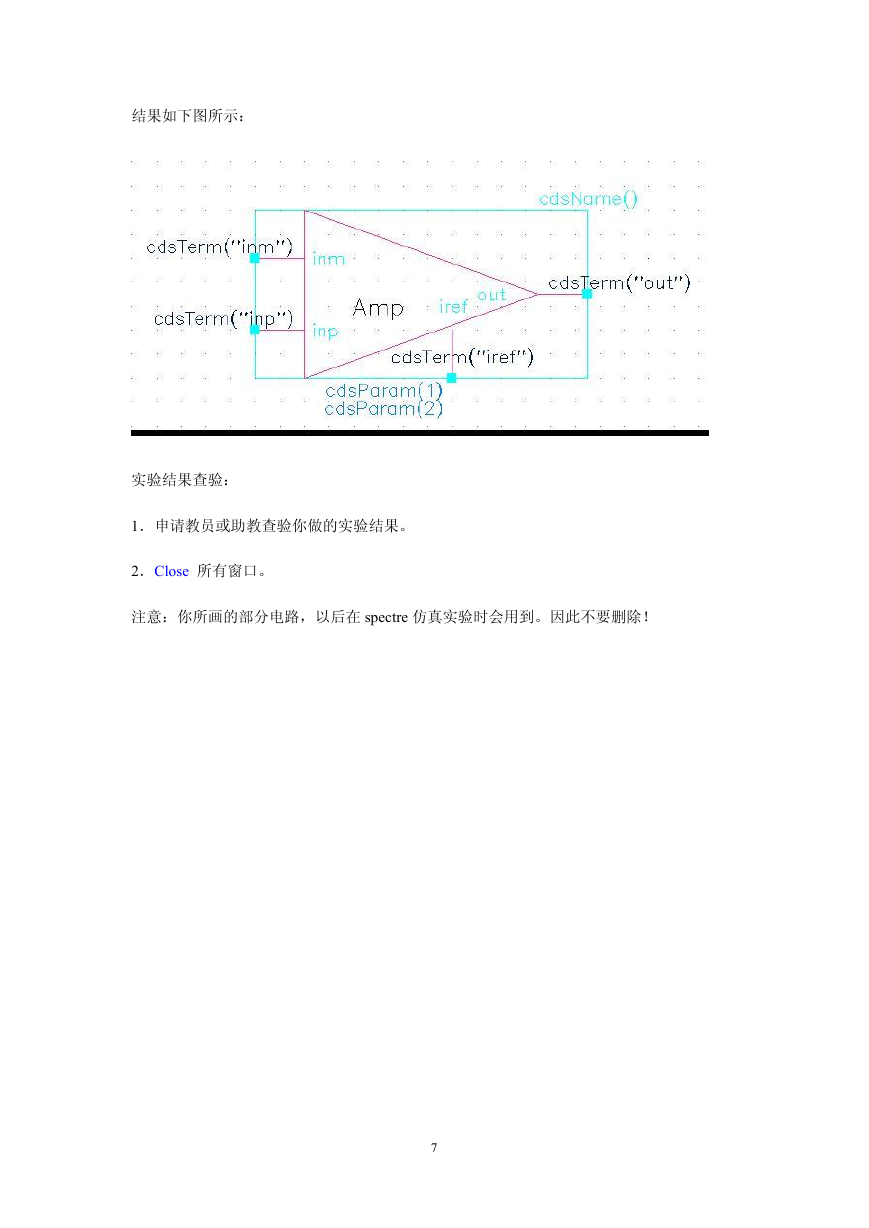

[2]创建 amplifier 的 symbol:

仿照前述步骤,得到如下 symbol:

提示:在“Symbol Generation Options”窗口,将 iref 管脚(Pin)设置为 Bottom Pin。

然后删除 cdsParam(3), r 旋转 pin 名 iref,

(选做)删除红色外框,选择 Selection Box 工具,在“Add Selection Box”中,Automatic

添加 Text:Add -> Note -> Note Text,在“Add Note Text”窗口的 Note Text 文本框中:Amp

将鼠标移至“Virtuoso Symbol Editing:mylib amplifier symbol”窗口,在你希望的位置单击,

回到“Add Note Text”窗口,Cancel。

Save。

(如果你无法画斜线,鼠标右键点击 1、2 次就可切换成功)

6

�

结果如下图所示:

实验结果查验:

1.申请教员或助教查验你做的实验结果。

2.Close 所有窗口。

注意:你所画的部分电路,以后在 spectre 仿真实验时会用到。因此不要删除!

7

�

Cadence IC 设计实验

实验二、 Spectre Simulation

实验目的:掌握电路特性仿真方法

进入 Cadence 系统:

cd adelabic5

icfb &

实验内容与步骤:

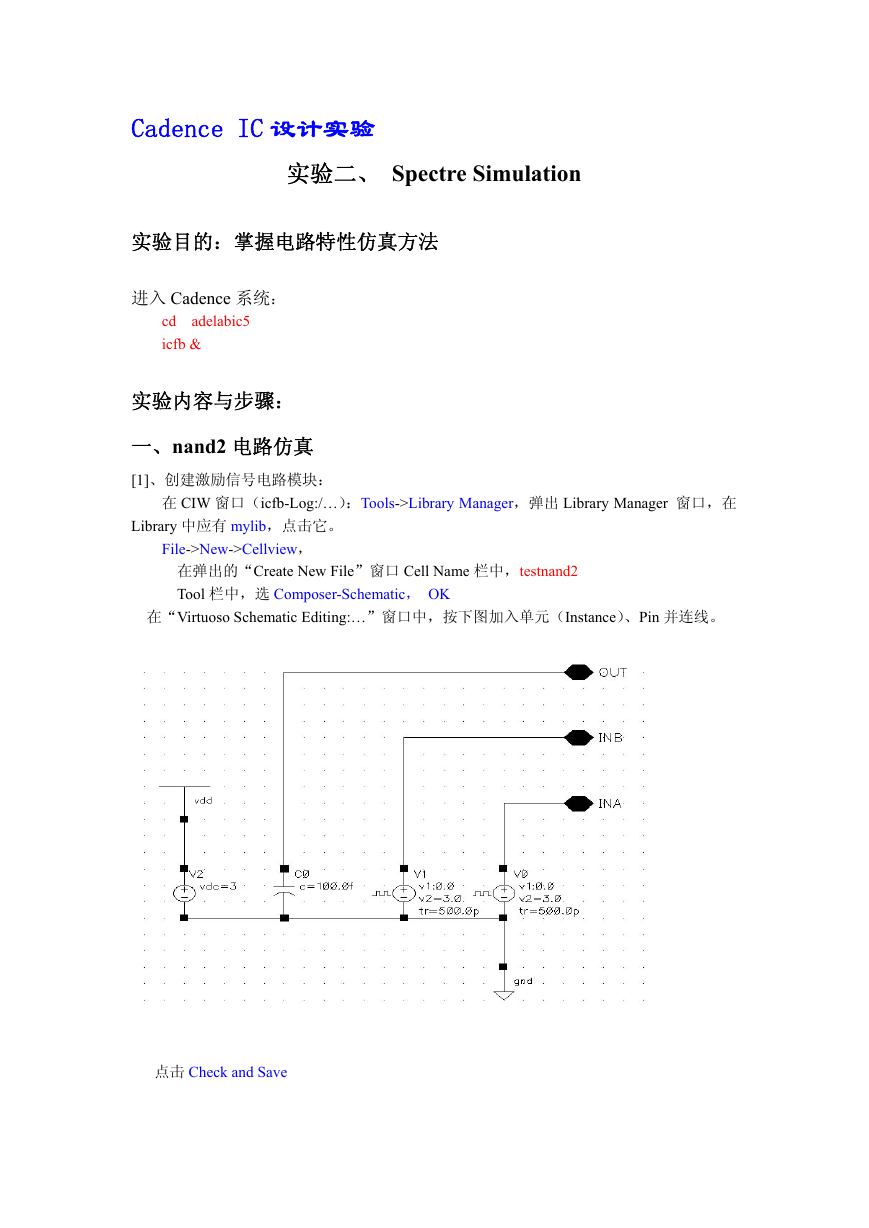

一、nand2 电路仿真

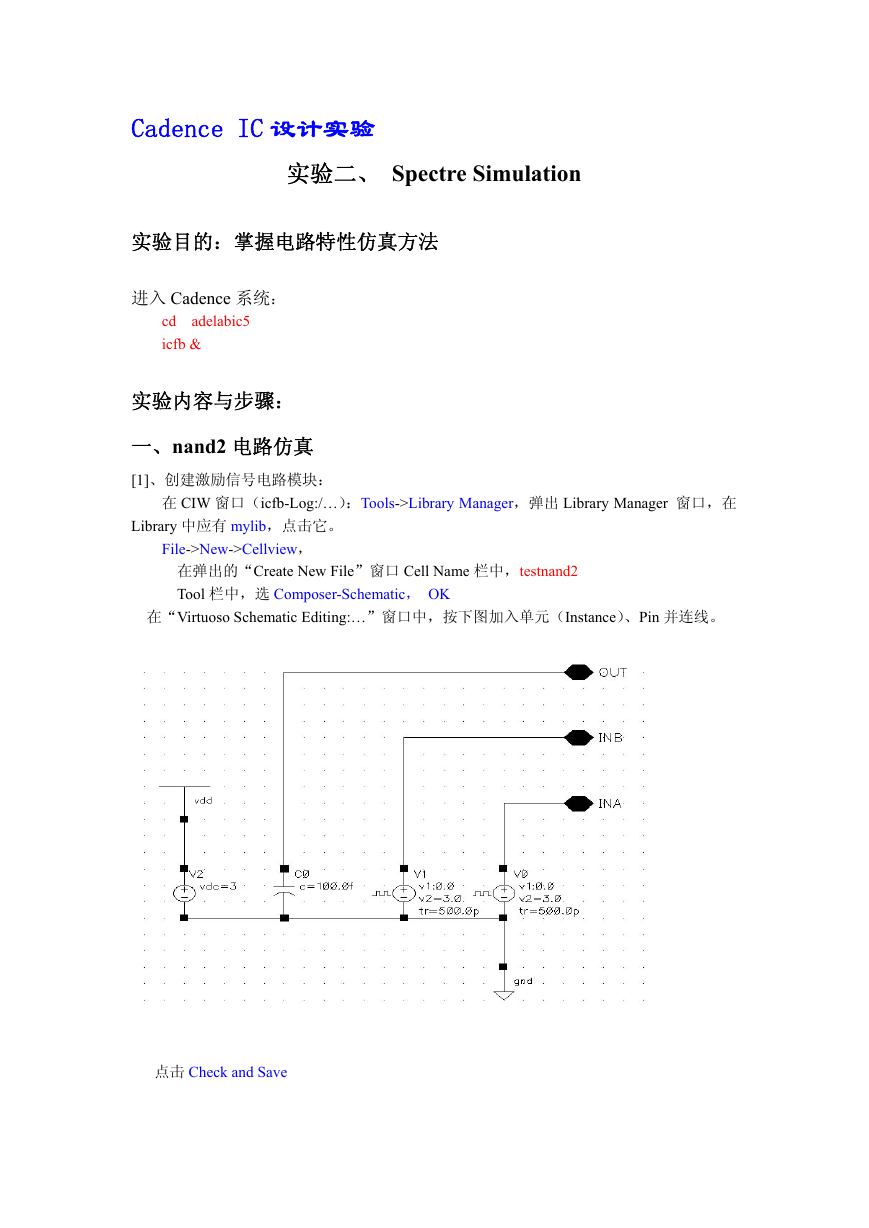

[1]、创建激励信号电路模块:

在 CIW 窗口(icfb-Log:/…):Tools->Library Manager,弹出 Library Manager 窗口,在

Library 中应有 mylib,点击它。

File->New->Cellview,

在弹出的“Create New File”窗口 Cell Name 栏中,testnand2

Tool 栏中,选 Composer-Schematic, OK

在“Virtuoso Schematic Editing:…”窗口中,按下图加入单元(Instance)、Pin 并连线。

点击 Check and Save

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc