Block Memory Generator v8.3

Table of Contents

IP Facts

Ch. 1: Overview

Feature Summary

Features Common to the Native Interface and AXI4 BMG Cores

Native Block Memory Generator Specific Features

AXI4 Interface Block Memory Generator Specific Features

Native Block Memory Generator Feature Summary

Memory Types

Selectable Memory Algorithm

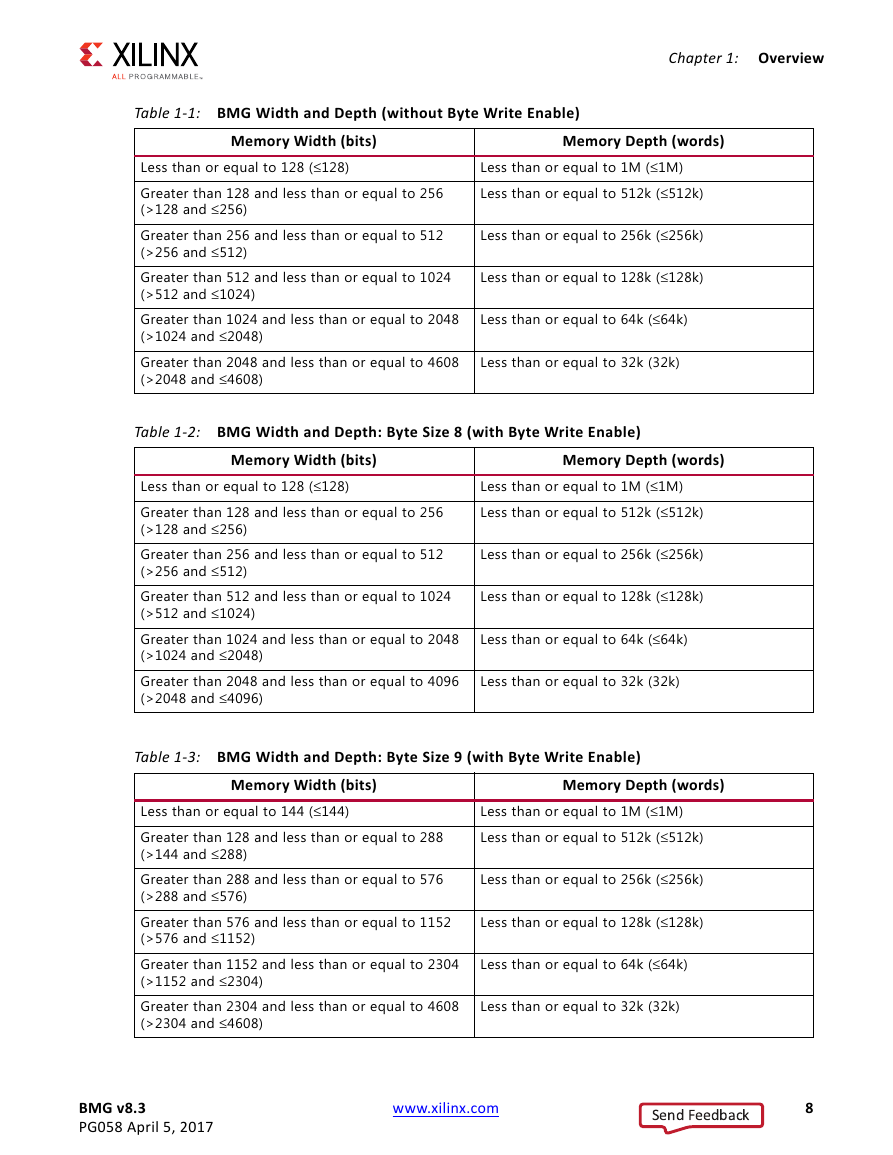

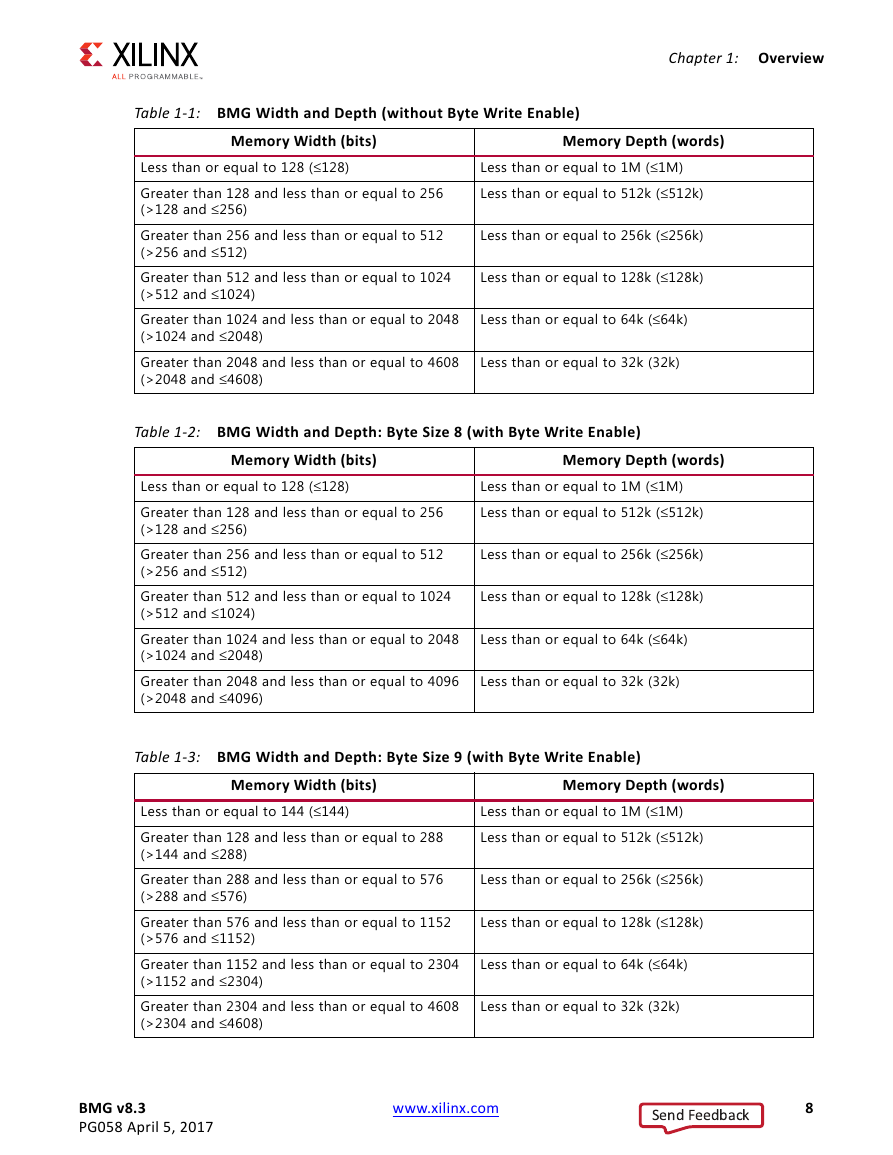

Configurable Width and Depth

Selectable Operating Mode per Port

Selectable Port Aspect Ratios

Optional Byte-Write Enable

Optional Output Registers

Optional Pipeline Stages

Optional Enable Pin

Optional Set/Reset Pin

Memory Initialization

Hamming Error Correction Capability

AXI4 Interface Block Memory Generator Feature Summary

Overview

Applications

AXI4 Block Memories–Memory Slave Mode

AXI4-Lite Block Memories–Memory Slave Mode

AXI4 Block Memories–Peripheral Slave Mode

AXI4-Lite Block Memories–Peripheral Slave Mode

AXI4 BMG Core Channel Handshake Sequence

AXI4-Lite Single Burst Transactions

AXI4 Incremental Burst Support

AXI4 Wrap Burst Support

AXI4 Narrow Transactions

AXI4 Unaligned Transactions

Configurable Width and Depth

AXI4 Interface Block Memory Addressing

Throughput and Performance

Selectable Port Aspect Ratios

Optional Output Register

Optional Pipeline Stages

Memory Initialization Capability

Applications

Licensing and Ordering Information

Ch. 2: Product Specification

Performance

Resource Utilization

Latency

Port Descriptions

Native Block Memory Generator Signals

AXI4 Interface Block Memory Generator Signals

AXI4 Interface - Global Signals

AXI4-Interface Signals

AXI4-Lite Interface Signals

Ch. 3: Designing with the Core

General Design Guidelines

Memory Type

Selectable Memory Algorithm

Minimum Area Algorithm

Low Power Algorithm

Fixed Primitive Algorithm

Selectable Width and Depth

Operating Mode

Data Width Aspect Ratios

Port Aspect Ratios

Port Aspect Ratio Example

Read-to-Write Aspect Ratios

Aspect Ratio Limitations

Byte-Writes

Byte-Write Example

Write First Mode Considerations

Collision Behavior

Collisions and Asynchronous Clocks: General Guidelines

Collisions and Synchronous Clocks: General Guidelines

Collisions and Simple Dual-port RAM

Additional Memory Collision Restrictions: Address Space Overlap

Optional Output Registers

Optional Pipeline Stages

Optional Register Clock Enable Pins

Optional Set/Reset Pins

Memory Output Flow Control

Read Data and Read Enable Latency

Reset Priority

Special Reset Behavior

Controlling Reset Operations

Built-in Error Correction Capability and Error Injection

Error Injection

Soft Error Correction Capability and Error injection

Overview

Details

Timing Diagrams

Device Utilization and Performance Benchmarks

Lower Data Widths in SDP Configurations

UltraScale Architecture-Based Device Features

Standard DOUT Block RAM Cascading

Pipe Line Register Addition in the Built ECC Mode

Clocking

Resets

Ch. 4: Design Flow Steps

Customizing and Generating the Core

Native Block Memory Generator Basic Tab

Port Options Tab

Other Options Tab

Specifying Initial Memory Contents

Summary Tab

Power Estimate Options Tab

Block RAM Usage

LUT Utilization and Performance

Generating the AXI4 Interface Block Memory Generator Core

Basic Tab

AXI4 Tab

Customizing the Core with IP Integrator

User Parameters

Constraining the Core

Simulation

Synthesis and Implementation

Ch. 5: Detailed Example Design

Ch. 6: Test Bench

Core with Native Interface

Core with AXI4 Interface

Messages and Warnings

Appx. A: Verification, Compliance, and Interoperability

Simulation

Appx. B: Migrating and Upgrading

Migrating to the Vivado Design Suite

Upgrading in the Vivado Design Suite

Auto Upgrade Feature

Appx. C: Debugging

Finding Help on Xilinx.com

Documentation

Answer Records

Technical Support

Debug Tools

Vivado Design Suite Debug Feature

Simulation Debug

Hardware Debug

General Checks

Appx. D: Native Block Memory Generator Supplemental Information

Low Power Designs

Native Block Memory Generator SIM Parameters

AXI4 Interface Block Memory Generator SIM Parameters

Output Register Configurations

Memory with Primitive and Core Output Registers

Memory with Primitive Output Registers and without Special Reset Behavior Option

Memory with Primitive Output Registers and with Special Reset Behavior Option

Memory with Core Output Registers

Memory with No Output Registers

Appx. E: Additional Resources and Legal Notices

Xilinx Resources

References

Revision History

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc