2

2

2

2

第 31 卷第 1 期

2005 年 1 月 电 子 工 程 师

EL ECTRON IC EN GIN EER

Vol. 31 No. 1

Jan. 2005

AHB 总线仲裁器的设计

李 玲 , 王祖强

(山东大学信息科学与工程学院 , 山东省济南市 250100)

【摘 要】 介绍了 AHB 总线仲裁信号 ,对其仲裁机制和仲裁过程进行了详细的说明 。在 MAX

+ plus Ⅱ软件平台上 ,采用自顶向下的设计方法 ,将整个设计分为 3 个模块 ,底层模块使用甚高速集成

电路硬件描述语言 (V HDL) 设计 ,然后包装入库 ,顶层文件采用原理图输入法 ,实现 AHB 总线仲裁器

的设计 ,并给出仿真结果 。

关键词 :AHB 总线 , 仲裁器 , SoC , MAX + plus Ⅱ

中图分类号 : TN492

0 引 言

随着集成电路规模的不断增加 ,集成电路设计已

进入片上系统 ( SoC) 时代 ,而 SoC 设计的关键问题之

一就是采用片上总线技术 。ARM 公司提出的 AMBA

总线 ,由于其本身的高性能和 ARM 处理器的广泛应

用 ,已经成为 SoC 设计中使用相当广泛的总线标准 。

目前 AMBA 总线的版本为 2. 0 , 定义了 3 组总线 :

AHB (AMBA 高性能总线) 、ASB (AMBA 系统总线) 和

APB (AMBA 外设总线) 。其中 AHB ( advanced high

performance bus) 是一种常用的片上总线 ,采用地址/

数据分离格式 ,支持固定长/ 不定长猝发 ( burst) 交易 、

分裂 (split) 交易特性和多个主设备的总线管理 ,具有

高带宽 、高性能特性 ,适合于嵌入式处理器与高性能外

围设备 、片内存储器及接口功能单元的连接 。

本文在 AMBA 总线版本 2. 0 基础上 ,采用自顶向

下设计方法完成了 AHB 总线仲裁器的设计 。

1 AHB 总线仲裁机制

仲裁器是 AHB 系统总线的主要管理机构 ,监视主

设备发出的总线请求 ,根据内部设定的仲裁算法进行

仲裁 ,给出相应的控制信号 。总线的优先级仲裁算法

通常有固定优先级算法和循环优先级算法两种 ,它们

各有优缺点 ,但两种算法都要满足总线的基本要求 :每

一时刻只能有一个主设备占用总线 ;先请求者先相应 ;

同一时刻请求时 ,按优先级确定 ;每个交易都不允许被

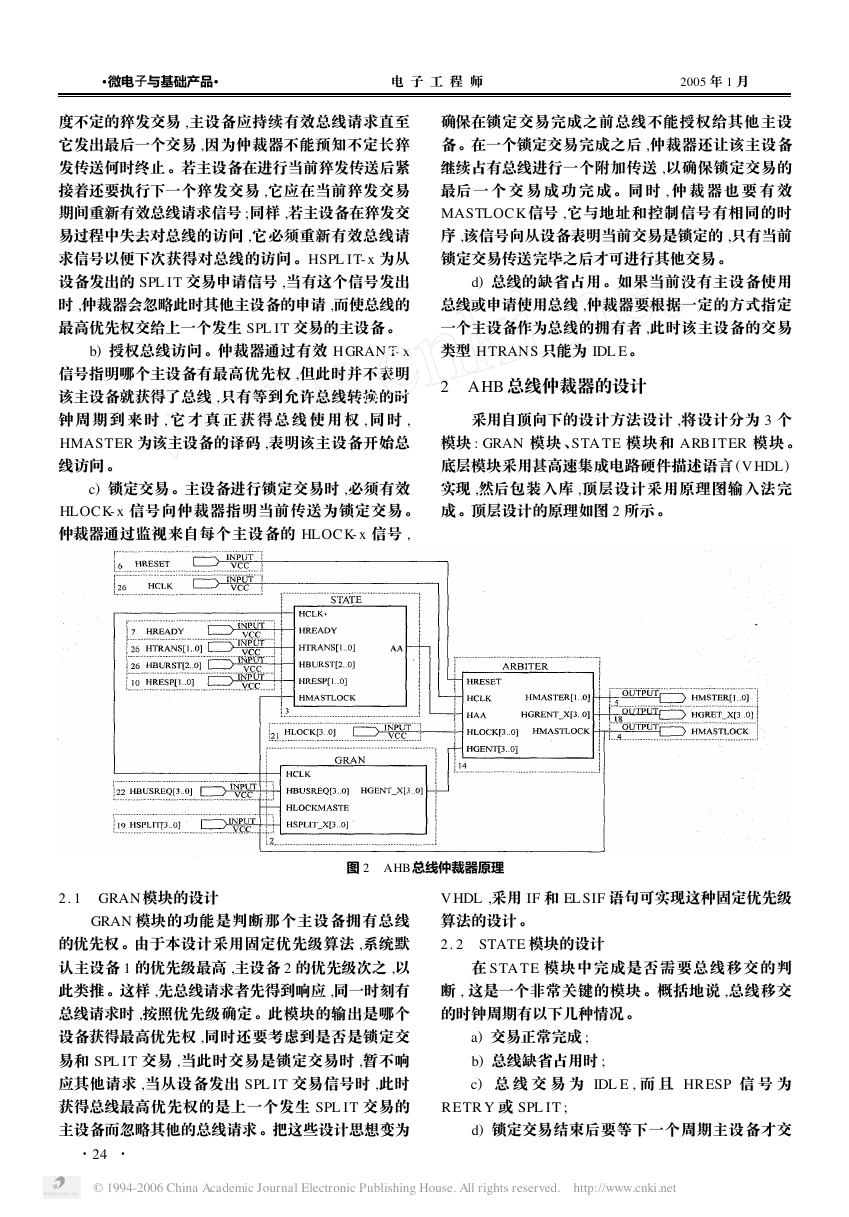

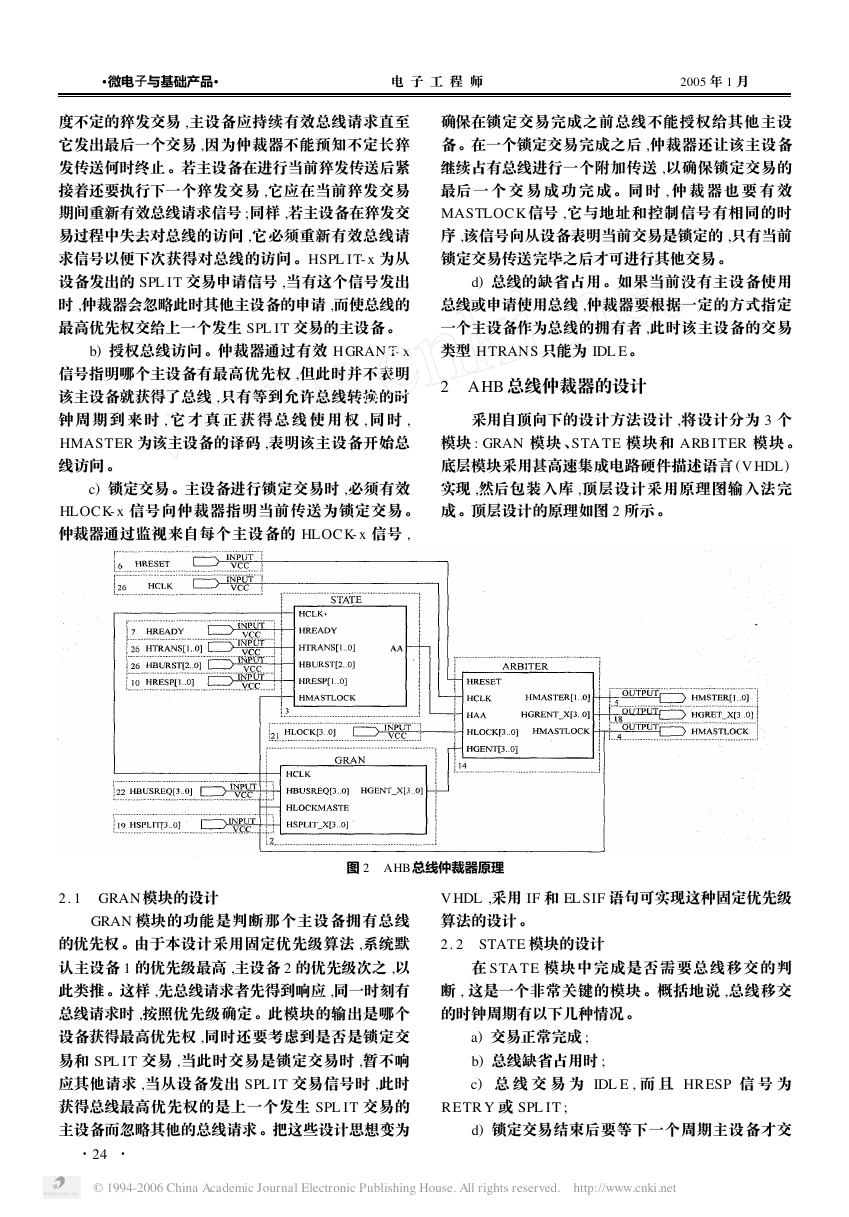

打断 。AHB 总线仲裁器的结构如图 1 所示 。

图 1 中 : HCL K 和 HRESET 分别为时钟信号和复

位信号 ; HREAD Y 是指从设备准备好信号 ; HTRANS

是指总线交易类型 ,包括 IDL E、BU SY、NONSEQ 和

收稿日期 : 2004

10

26 ; 修回日期 : 2004

12

06 。

SEQ 等 4 种交易类型 ; HRESP 是指在交易过程中从

设备给出的反应信号 ,包括 O KA Y、ERROR、RETR Y

和 SPL IT ; HBU RST 是指猝发类型 ,共有 8 种不同的

猝发交易 ,可分为单个交易 SIN GL E、不定长猝发交易

INCR 和固定长猝发交易 3 类 ; HREQ- x 和 HLOC K- x

分别指主设备总线请求信号和锁定信号 ; H GRAN T- x

是总线允许信号 ,表示该主设备有总线使用的最高优

先权 ; HMASTER 是指允许使用总线的主设备译码 ,

只有此信号有效时主设备才可使用总线 ; HMASTER

LOC K 有 效 是 指 此 时 的 交 易 是 锁 定 序 列 的 交 易 ;

HSPL IT- x 是指从设备要求完成分裂交易 SPL IT 的请

求信号 ,分裂交易是 AHB 系统总线的一个显著特性 ,

它可以防止系统死锁和充分利用总线 。

图 1 AHB总线仲裁器的结构

具体仲裁过程说明如下 。

a) 总线申请 。AHB 总线的仲裁是“隐含的”,一次

仲裁可以在上一次总线访问期间完成 ,从而仲裁不必

占用 AHB 总线周期 (总线空闲时除外) 。正常情况下 ,

仲裁器只有当一个交易完成之后才把总线移交给另外

一个主设备 ,当主设备被授权总线并开始一个固定长

度猝发交易后 ,没有必要继续请求总线 ,因为仲裁器通

过监 视 猝 发 交 易 过 程 HTRANS 信 号 和 猝 发 类 型

HBU RST信号可知道当前猝发交易何时结束 ;对于长

·32·

© 1994-2006 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

·微电子与基础产品· 电 子 工 程 师 2005 年 1 月

度不定的猝发交易 ,主设备应持续有效总线请求直至

它发出最后一个交易 ,因为仲裁器不能预知不定长猝

发传送何时终止 。若主设备在进行当前猝发传送后紧

接着还要执行下一个猝发交易 ,它应在当前猝发交易

期间重新有效总线请求信号 ;同样 ,若主设备在猝发交

易过程中失去对总线的访问 ,它必须重新有效总线请

求信号以便下次获得对总线的访问 。HSPL IT- x 为从

设备发出的 SPL IT 交易申请信号 ,当有这个信号发出

时 ,仲裁器会忽略此时其他主设备的申请 ,而使总线的

最高优先权交给上一个发生 SPL IT 交易的主设备 。

b) 授权总线访问 。仲裁器通过有效 H GRAN T- x

信号指明哪个主设备有最高优先权 ,但此时并不表明

该主设备就获得了总线 ,只有等到允许总线转换的时

钟周 期 到 来 时 , 它 才 真 正 获 得 总 线 使 用 权 , 同 时 ,

HMASTER 为该主设备的译码 ,表明该主设备开始总

线访问 。

c) 锁定交易 。主设备进行锁定交易时 ,必须有效

HLOC K- x 信号向仲裁器指明当前传送为锁定交易 。

仲裁器通过监视来自每个主设备的 HLOC K- x 信号 ,

确保在锁定交易完成之前总线不能授权给其他主设

备 。在一个锁定交易完成之后 ,仲裁器还让该主设备

继续占有总线进行一个附加传送 ,以确保锁定交易的

最后 一 个 交 易 成 功 完 成 。同 时 , 仲 裁 器 也 要 有 效

MASTLOC K信号 ,它与地址和控制信号有相同的时

序 ,该信号向从设备表明当前交易是锁定的 ,只有当前

锁定交易传送完毕之后才可进行其他交易 。

d) 总线的缺省占用 。如果当前没有主设备使用

总线或申请使用总线 ,仲裁器要根据一定的方式指定

一个主设备作为总线的拥有者 ,此时该主设备的交易

类型 HTRANS 只能为 IDL E。

2 AHB 总线仲裁器的设计

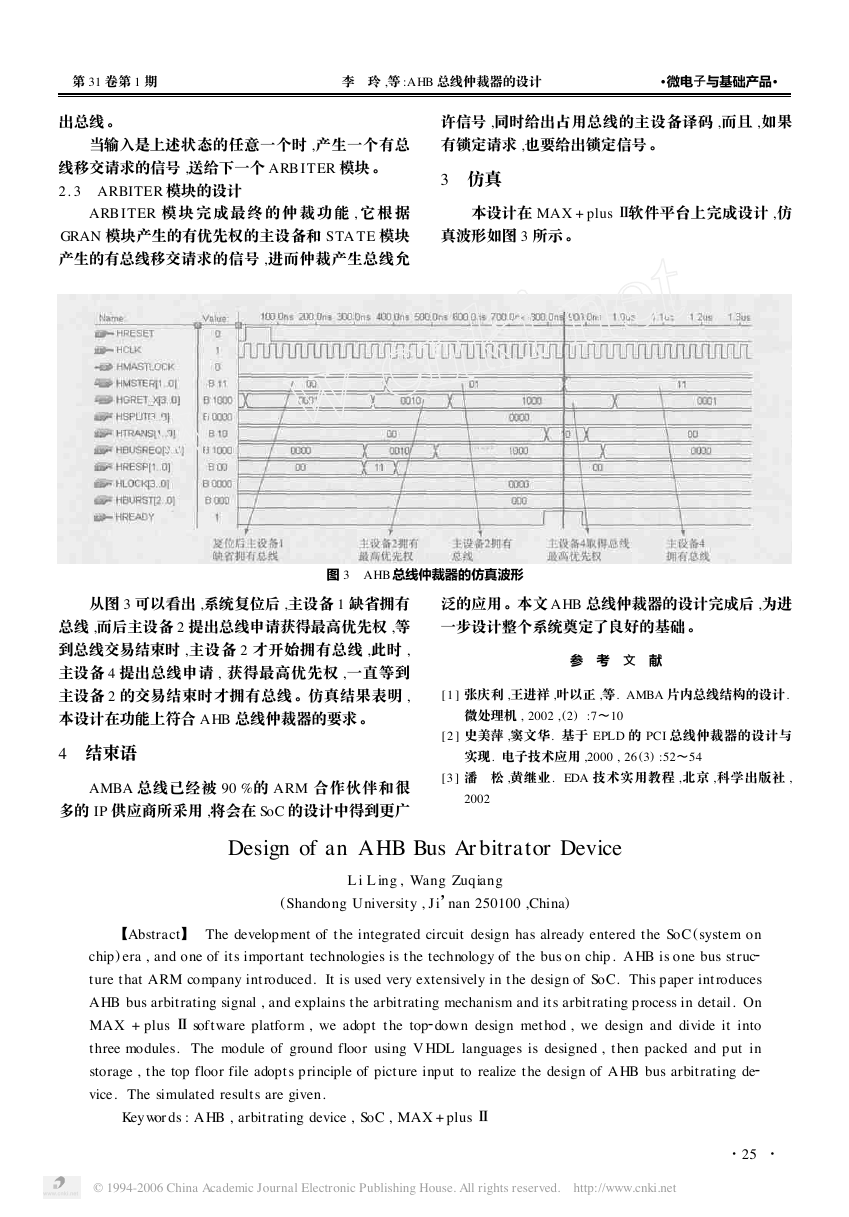

采用自顶向下的设计方法设计 ,将设计分为 3 个

模块 : GRAN 模块 、STA TE 模块和 ARB ITER 模块 。

底层模块采用甚高速集成电路硬件描述语言 (V HDL)

实现 ,然后包装入库 ,顶层设计采用原理图输入法完

成 。顶层设计的原理如图 2 所示 。

图 2 AHB总线仲裁器原理

2. 1 GRAN 模块的设计

GRAN 模块的功能是判断那个主设备拥有总线

的优先权 。由于本设计采用固定优先级算法 ,系统默

认主设备 1 的优先级最高 ,主设备 2 的优先级次之 ,以

此类推 。这样 ,先总线请求者先得到响应 ,同一时刻有

总线请求时 ,按照优先级确定 。此模块的输出是哪个

设备获得最高优先权 ,同时还要考虑到是否是锁定交

易和 SPL IT 交易 ,当此时交易是锁定交易时 ,暂不响

应其他请求 ,当从设备发出 SPL IT 交易信号时 ,此时

获得总线最高优先权的是上一个发生 SPL IT 交易的

主设备而忽略其他的总线请求 。把这些设计思想变为

·42·

V HDL ,采用 IF 和 EL SIF 语句可实现这种固定优先级

算法的设计 。

2. 2 STATE 模块的设计

在 STA TE 模块中完成是否需要总线移交的判

断 , 这是一个非常关键的模块 。概括地说 ,总线移交

的时钟周期有以下几种情况 。

a) 交易正常完成 ;

b) 总线缺省占用时 ;

c) 总 线 交 易 为 IDL E , 而 且 HRESP 信 号 为

RETR Y 或 SPL IT ;

d) 锁定交易结束后要等下一个周期主设备才交

© 1994-2006 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2

2

第 31 卷第 1 期 李 玲 ,等 :AHB 总线仲裁器的设计 ·微电子与基础产品·

出总线 。

当输入是上述状态的任意一个时 ,产生一个有总

线移交请求的信号 ,送给下一个 ARB ITER 模块 。

2. 3 ARBITER模块的设计

ARB ITER 模 块 完 成 最 终 的 仲 裁 功 能 , 它 根 据

GRAN 模块产生的有优先权的主设备和 STA TE 模块

产生的有总线移交请求的信号 ,进而仲裁产生总线允

许信号 ,同时给出占用总线的主设备译码 ,而且 ,如果

有锁定请求 ,也要给出锁定信号 。

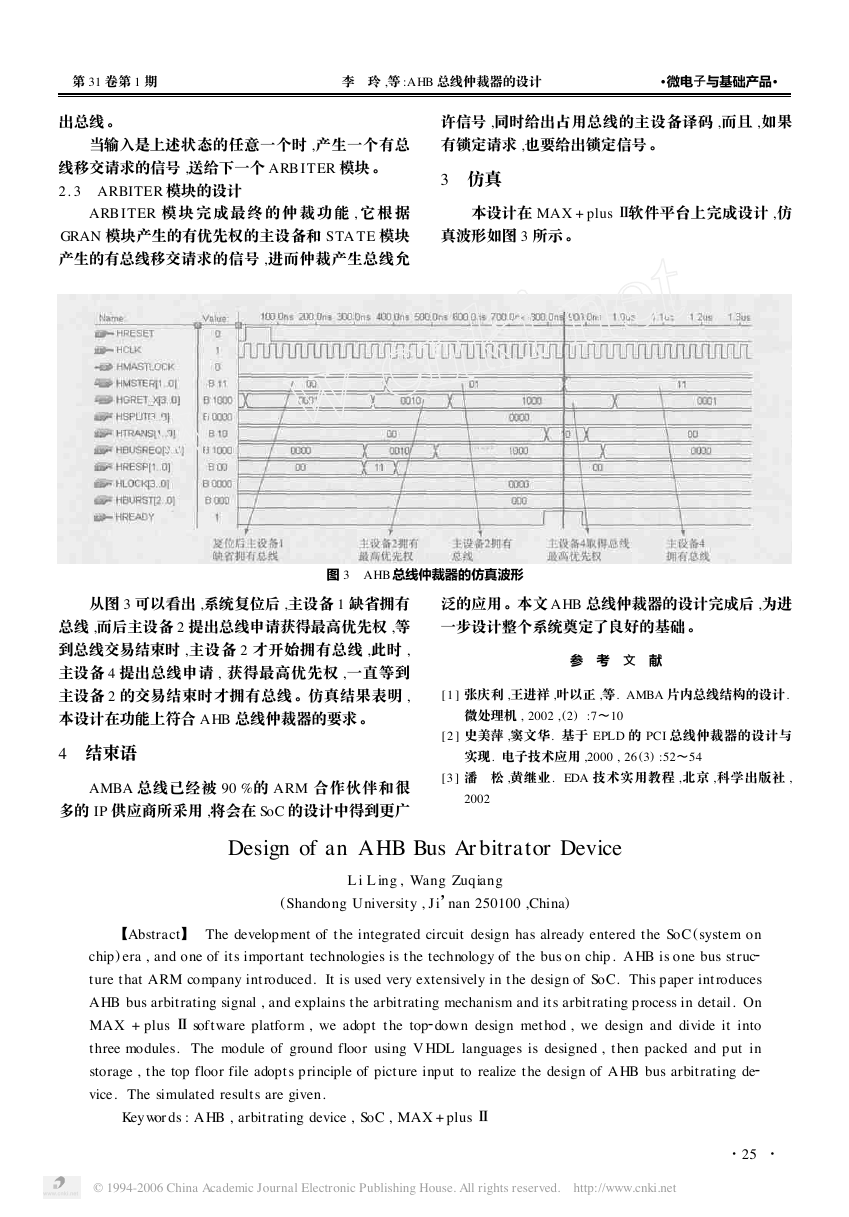

3 仿真

本设计在 MAX + plus Ⅱ软件平台上完成设计 ,仿

真波形如图 3 所示 。

图 3 AHB总线仲裁器的仿真波形

从图 3 可以看出 ,系统复位后 ,主设备 1 缺省拥有

总线 ,而后主设备 2 提出总线申请获得最高优先权 ,等

到总线交易结束时 ,主设备 2 才开始拥有总线 ,此时 ,

主设备 4 提出总线申请 , 获得最高优先权 ,一直等到

主设备 2 的交易结束时才拥有总线 。仿真结果表明 ,

本设计在功能上符合 AHB 总线仲裁器的要求 。

4 结束语

AMBA 总线已经被 90 %的 ARM 合作伙伴和很

多的 IP 供应商所采用 ,将会在 SoC 的设计中得到更广

泛的应用 。本文 AHB 总线仲裁器的设计完成后 ,为进

一步设计整个系统奠定了良好的基础 。

参 考 文 献

1 张庆利 ,王进祥 ,叶以正 ,等. AMBA 片内总线结构的设计.

微处理机 , 2002 , (2)

:7~10

2 史美萍 ,窦文华. 基于 EPLD 的 PCI 总线仲裁器的设计与

实现. 电子技术应用 ,2000 , 26 (3) :52~54

3 潘 松 ,黄继业. EDA 技术实用教程 ,北京 ,科学出版社 ,

2002

Design of an AHB Bus Arbitrator Device

Li Ling , Wang Zuqiang

(Shandong University , Ji’nan 250100 ,China)

【Abstract】 The development of the integrated circuit design has already entered the SoC (system on

chip) era , and one of its important technologies is the technology of the bus on chip . AHB is one bus struc

ture that ARM company introduced. It is used very extensively in the design of SoC. This paper introduces

AHB bus arbitrating signal , and explains the arbitrating mechanism and its arbitrating process in detail. On

MAX + plus Ⅱ software platform , we adopt the top

down design method , we design and divide it into

three modules. The module of ground floor using V HDL languages is designed , then packed and put in

storage , the top floor file adopts principle of picture input to realize the design of AHB bus arbitrating de

vice. The simulated results are given.

Keywords : AHB , arbitrating device , SoC , MAX + plus Ⅱ

© 1994-2006 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

·52·

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc