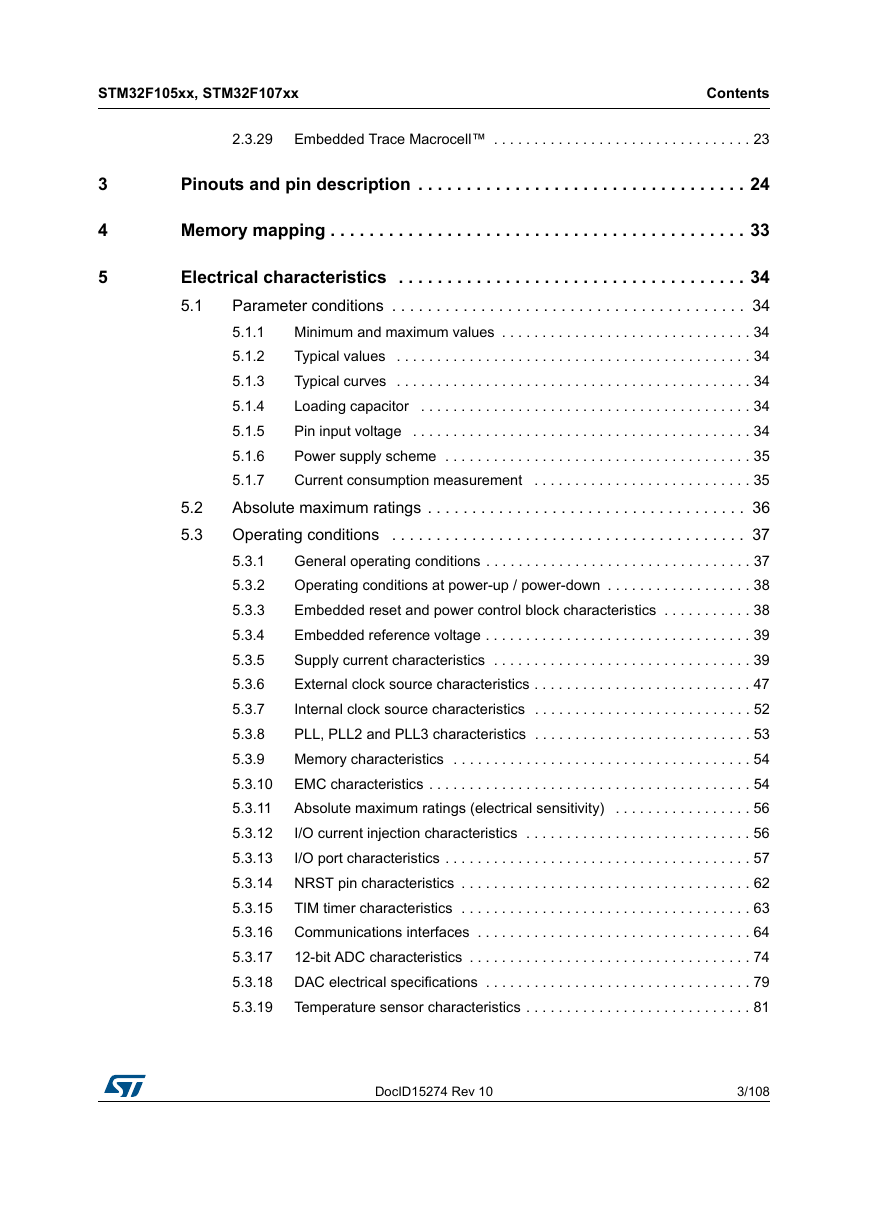

1 Introduction

2 Description

2.1 Device overview

2.2 Full compatibility throughout the family

2.3 Overview

2.3.1 ARM Cortex-M3 core with embedded Flash and SRAM

2.3.2 Embedded Flash memory

2.3.3 CRC (cyclic redundancy check) calculation unit

2.3.4 Embedded SRAM

2.3.5 Nested vectored interrupt controller (NVIC)

2.3.6 External interrupt/event controller (EXTI)

2.3.7 Clocks and startup

2.3.8 Boot modes

2.3.9 Power supply schemes

2.3.10 Power supply supervisor

2.3.11 Voltage regulator

2.3.12 Low-power modes

2.3.13 DMA

2.3.14 RTC (real-time clock) and backup registers

2.3.15 Timers and watchdogs

2.3.16 I²C bus

2.3.17 Universal synchronous/asynchronous receiver transmitters (USARTs)

2.3.18 Serial peripheral interface (SPI)

2.3.19 Inter-integrated sound (I2S)

2.3.20 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

2.3.21 Controller area network (CAN)

2.3.22 Universal serial bus on-the-go full-speed (USB OTG FS)

2.3.23 GPIOs (general-purpose inputs/outputs)

2.3.24 Remap capability

2.3.25 ADCs (analog-to-digital converters)

2.3.26 DAC (digital-to-analog converter)

2.3.27 Temperature sensor

2.3.28 Serial wire JTAG debug port (SWJ-DP)

2.3.29 Embedded Trace Macrocell™

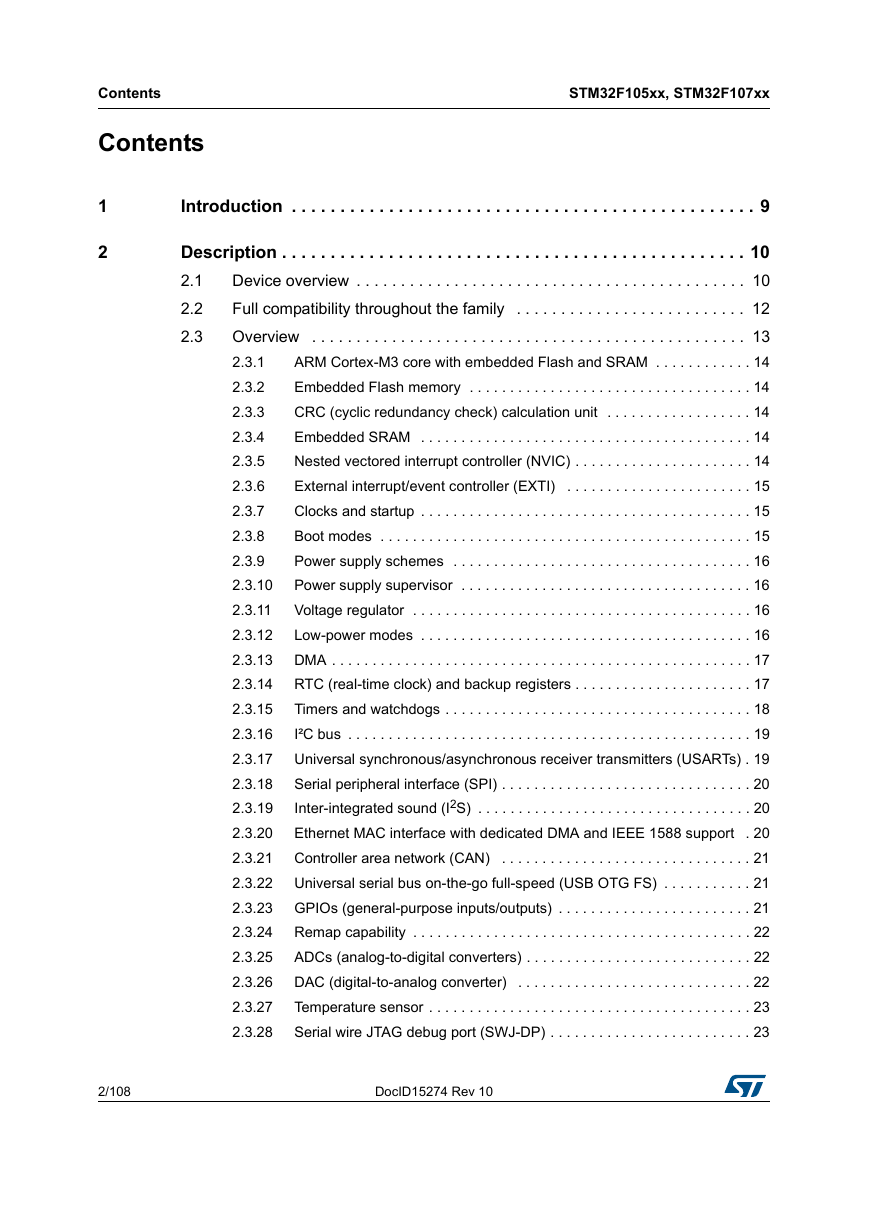

3 Pinouts and pin description

4 Memory mapping

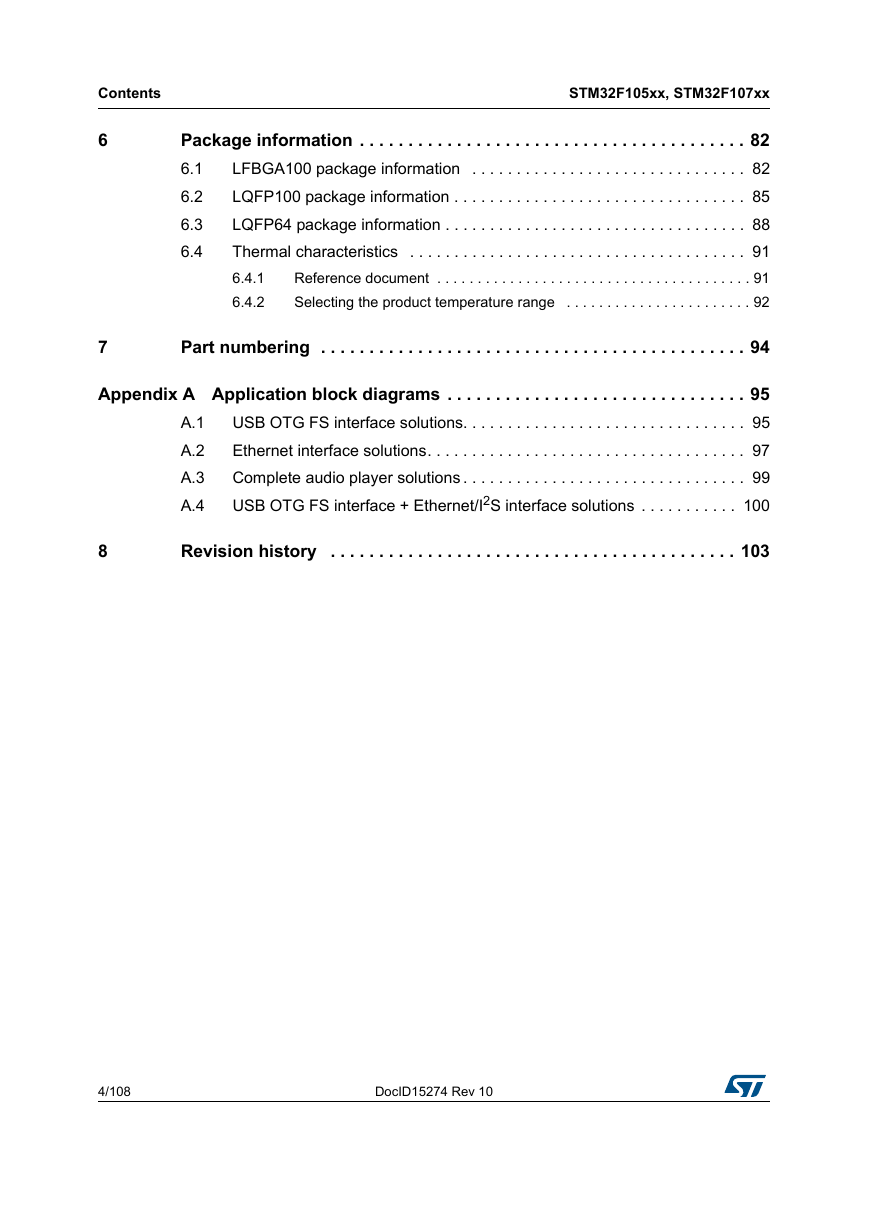

5 Electrical characteristics

5.1 Parameter conditions

5.1.1 Minimum and maximum values

5.1.2 Typical values

5.1.3 Typical curves

5.1.4 Loading capacitor

5.1.5 Pin input voltage

5.1.6 Power supply scheme

5.1.7 Current consumption measurement

5.2 Absolute maximum ratings

5.3 Operating conditions

5.3.1 General operating conditions

5.3.2 Operating conditions at power-up / power-down

5.3.3 Embedded reset and power control block characteristics

5.3.4 Embedded reference voltage

5.3.5 Supply current characteristics

5.3.6 External clock source characteristics

5.3.7 Internal clock source characteristics

5.3.8 PLL, PLL2 and PLL3 characteristics

5.3.9 Memory characteristics

5.3.10 EMC characteristics

5.3.11 Absolute maximum ratings (electrical sensitivity)

5.3.12 I/O current injection characteristics

5.3.13 I/O port characteristics

5.3.14 NRST pin characteristics

5.3.15 TIM timer characteristics

5.3.16 Communications interfaces

5.3.17 12-bit ADC characteristics

5.3.18 DAC electrical specifications

5.3.19 Temperature sensor characteristics

6 Package information

6.1 LFBGA100 package information

6.2 LQFP100 package information

6.3 LQFP64 package information

6.4 Thermal characteristics

6.4.1 Reference document

6.4.2 Selecting the product temperature range

7 Part numbering

Appendix A Application block diagrams

A.1 USB OTG FS interface solutions

A.2 Ethernet interface solutions

A.3 Complete audio player solutions

A.4 USB OTG FS interface + Ethernet/I2S interface solutions

8 Revision history

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc