IC5141 中网表导入成电路的详细步骤

徐宏伟 2011-12-22

针对本次项目中设计人员只提供纸档电路图及电路网表(cdlcdlcdlcdl 格式的)而未提供

schematic

virtuoso

virtuoso

virtuoso

schematic

virtuoso

schematic 的情况,本文讲解一种简单的方法来将网表导入成 virtuoso

virtuoso schematic

virtuoso

virtuoso

layout-xl

schematic

schematic

layout-xl

schematic,以方便进行 layout-xl

schematic

layout-xl 的版图操作。

首先我来讲一下我这边的操作步骤。

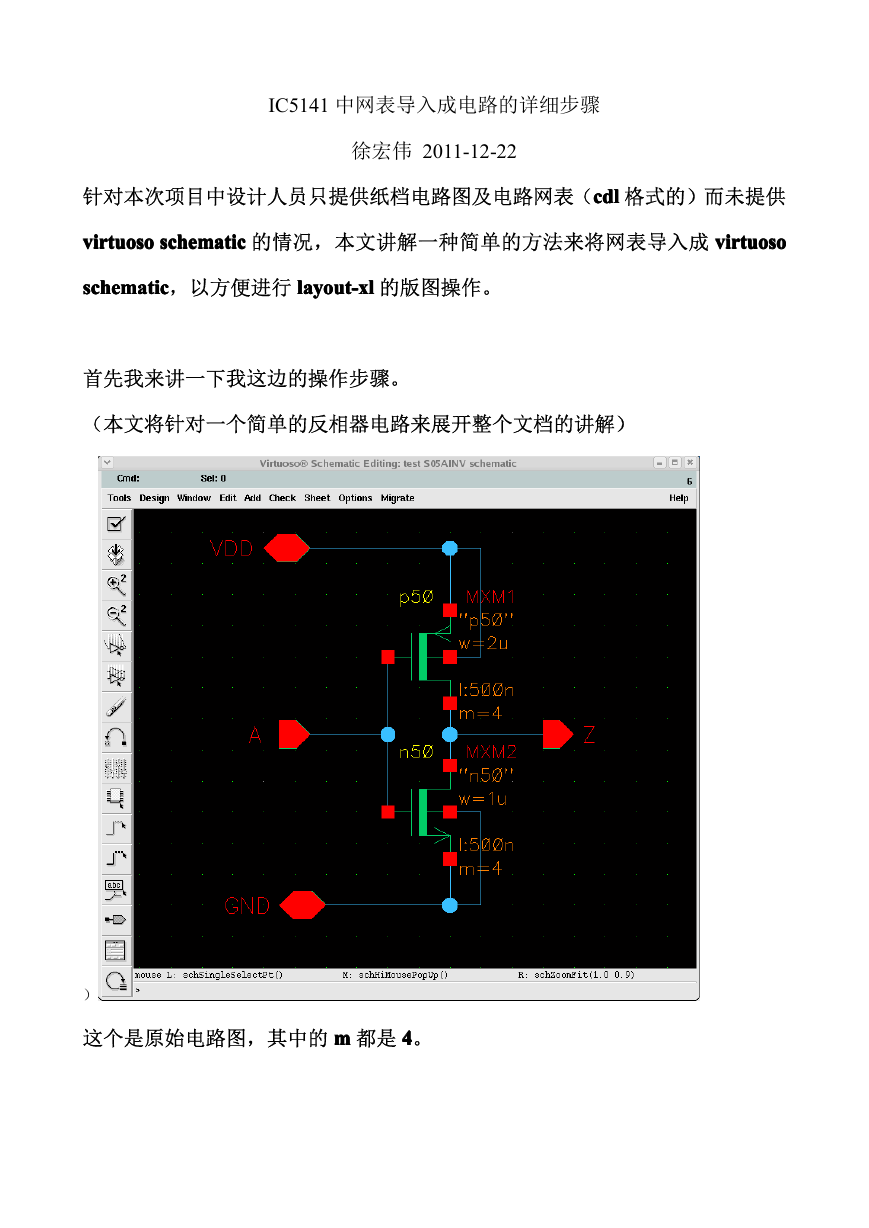

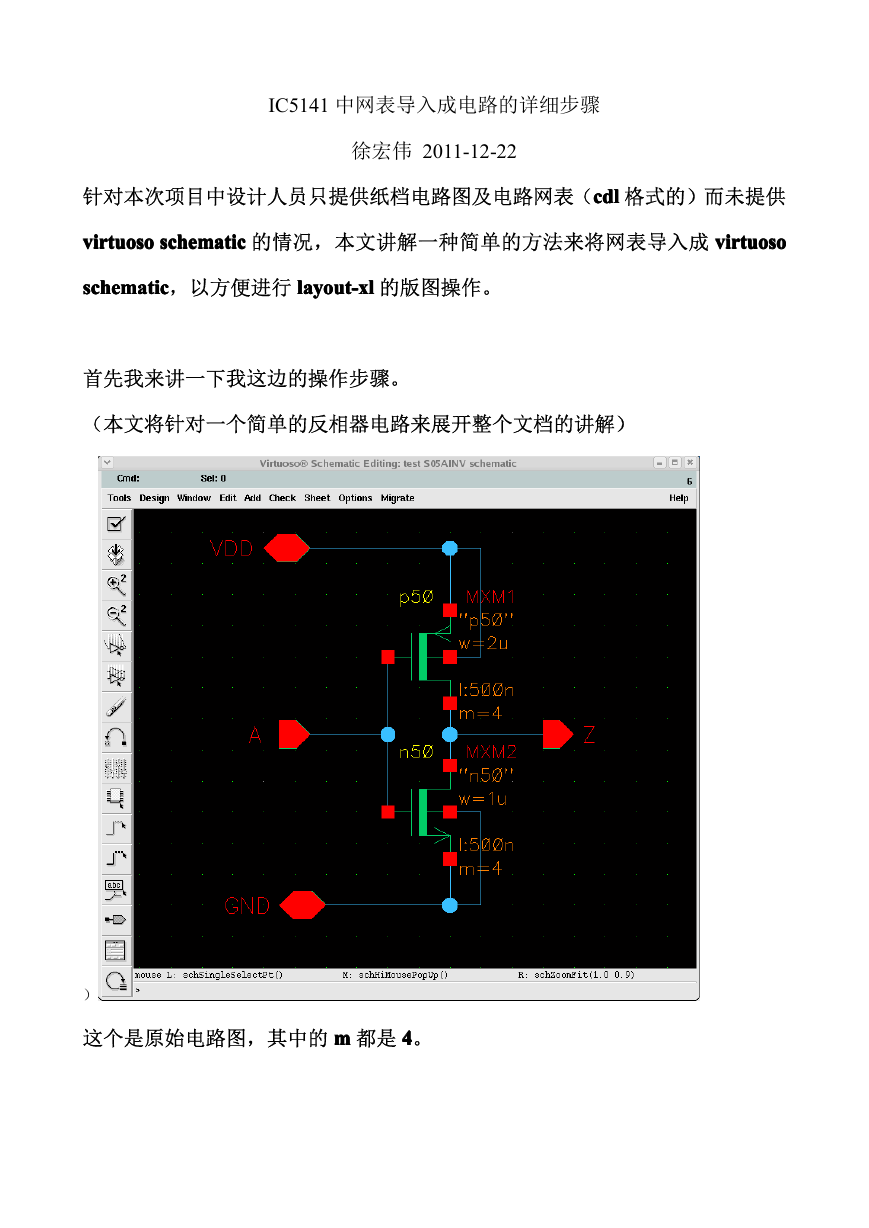

(本文将针对一个简单的反相器电路来展开整个文档的讲解)

)

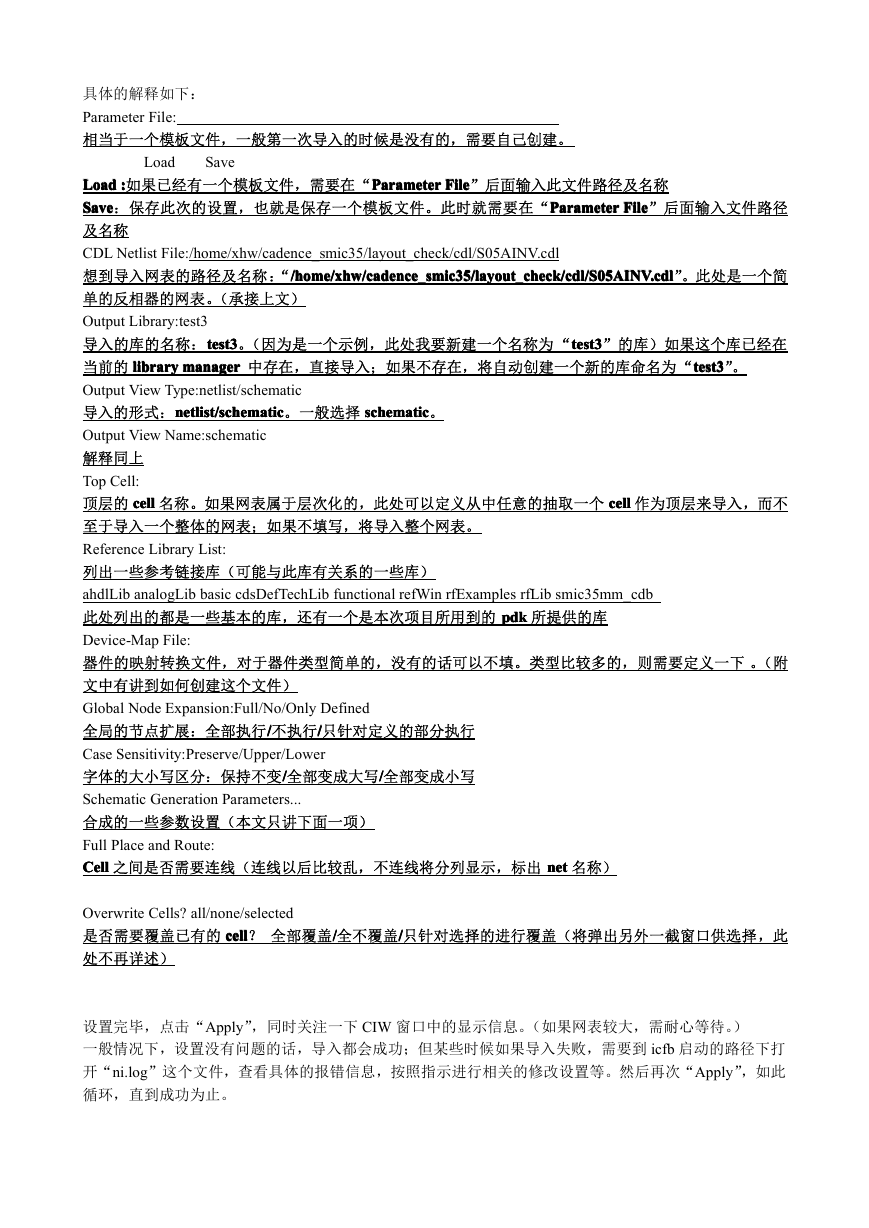

这个是原始电路图,其中的 mmmm 都是 4444。

�

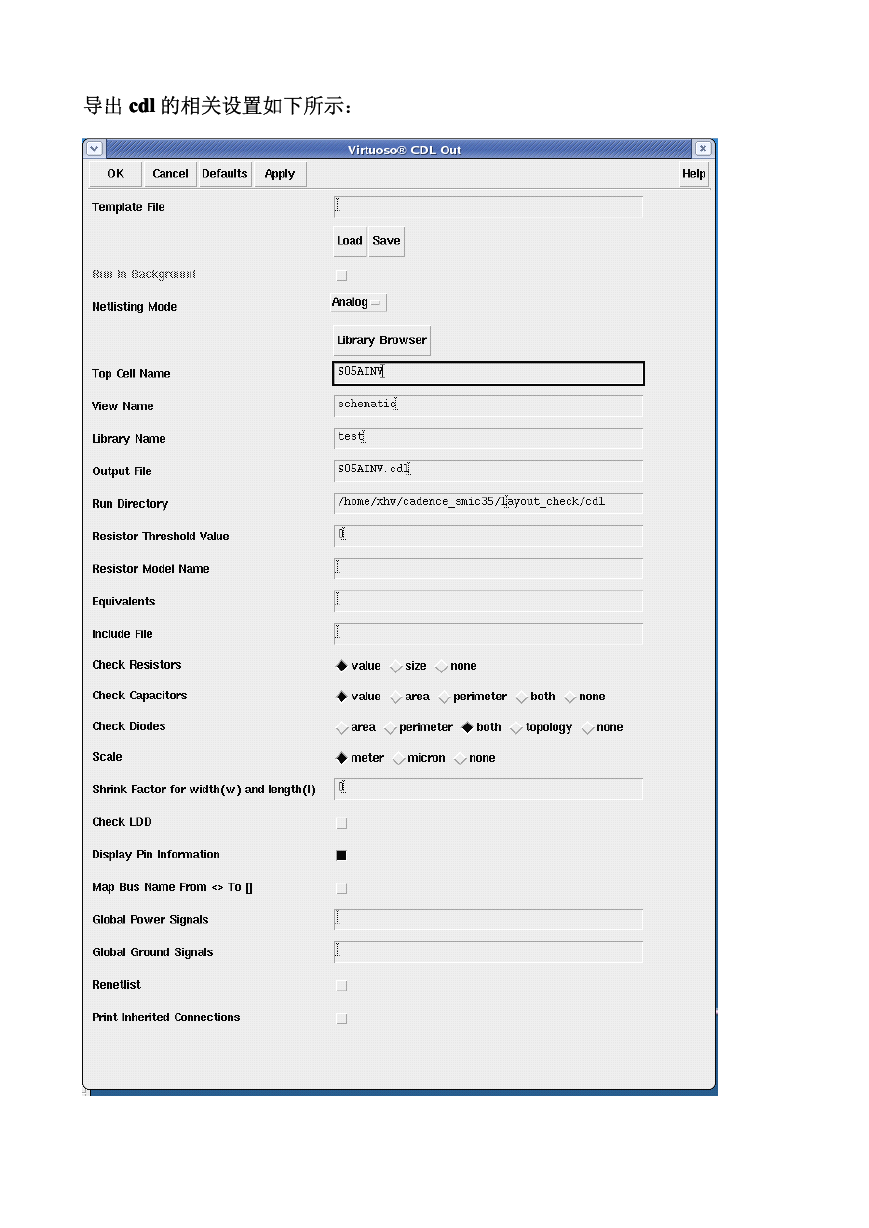

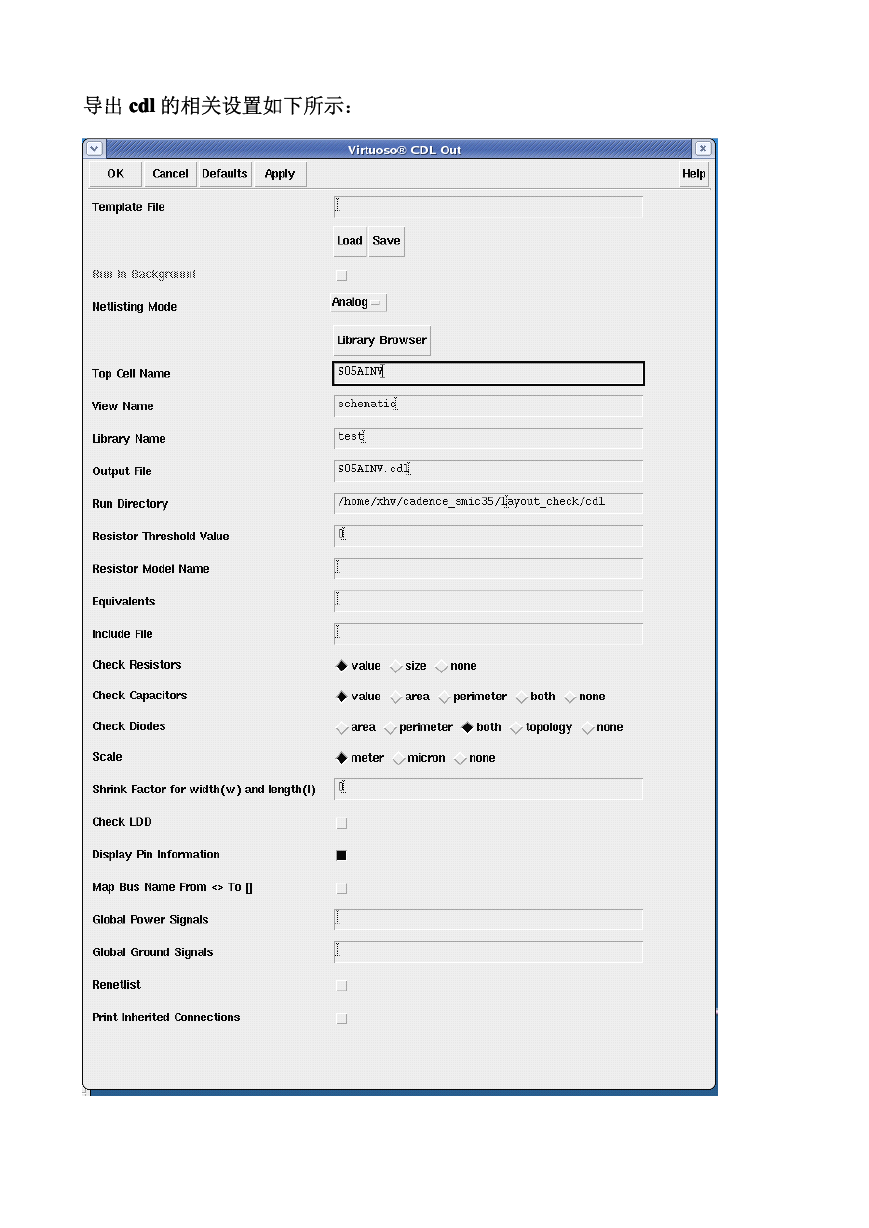

导出 cdlcdlcdlcdl 的相关设置如下所示:

�

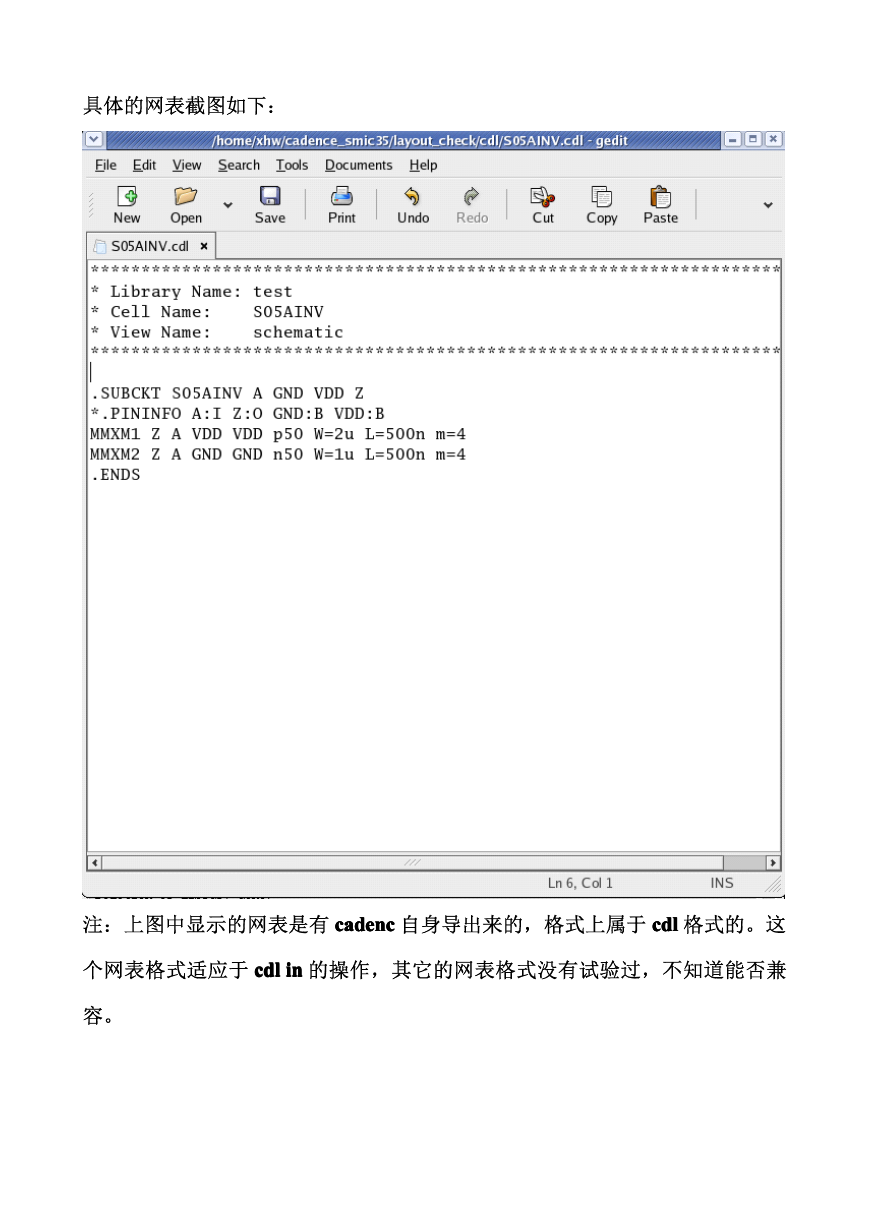

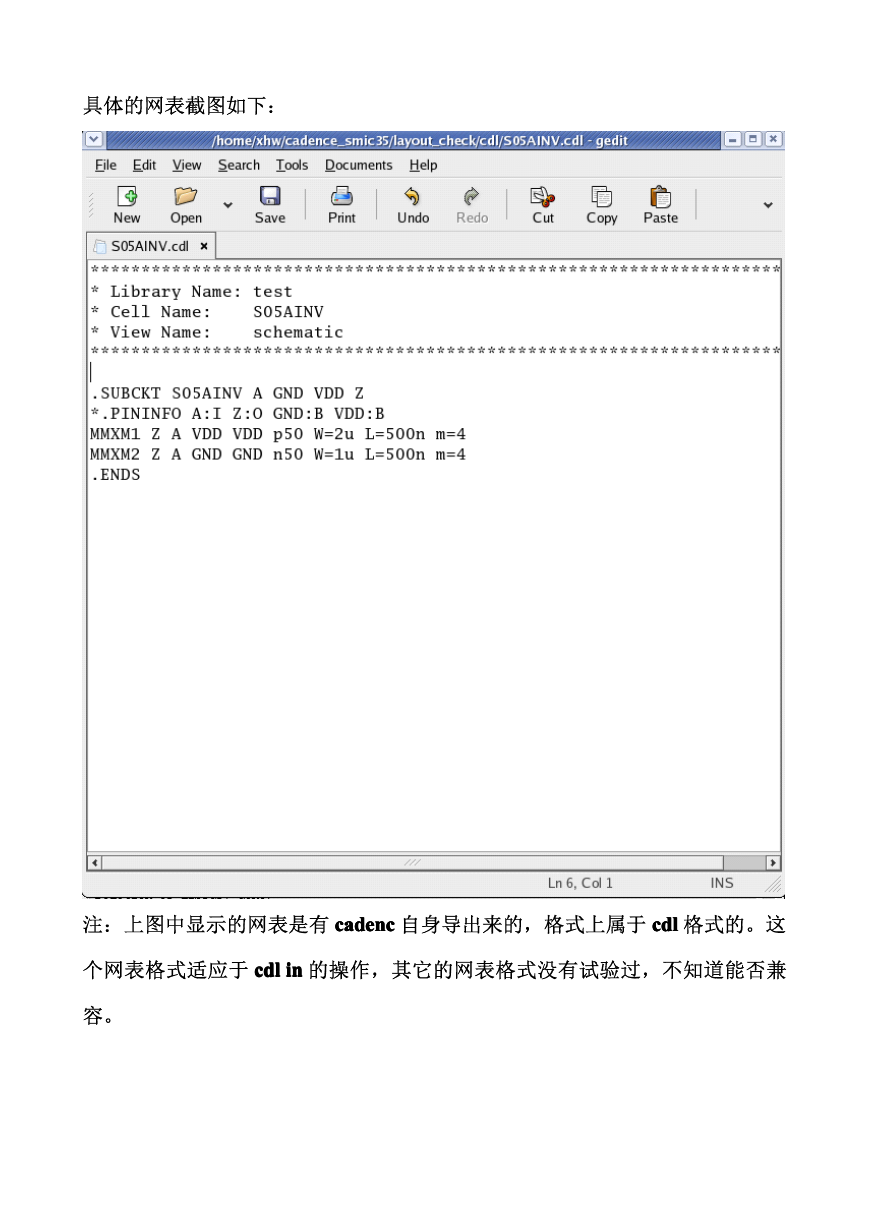

具体的网表截图如下:

cadenc 自身导出来的,格式上属于 cdlcdlcdlcdl 格式的。这

cadenc

cadenc

注:上图中显示的网表是有 cadenc

个网表格式适应于 cdlcdlcdlcdl inininin 的操作,其它的网表格式没有试验过,不知道能否兼

容。

�

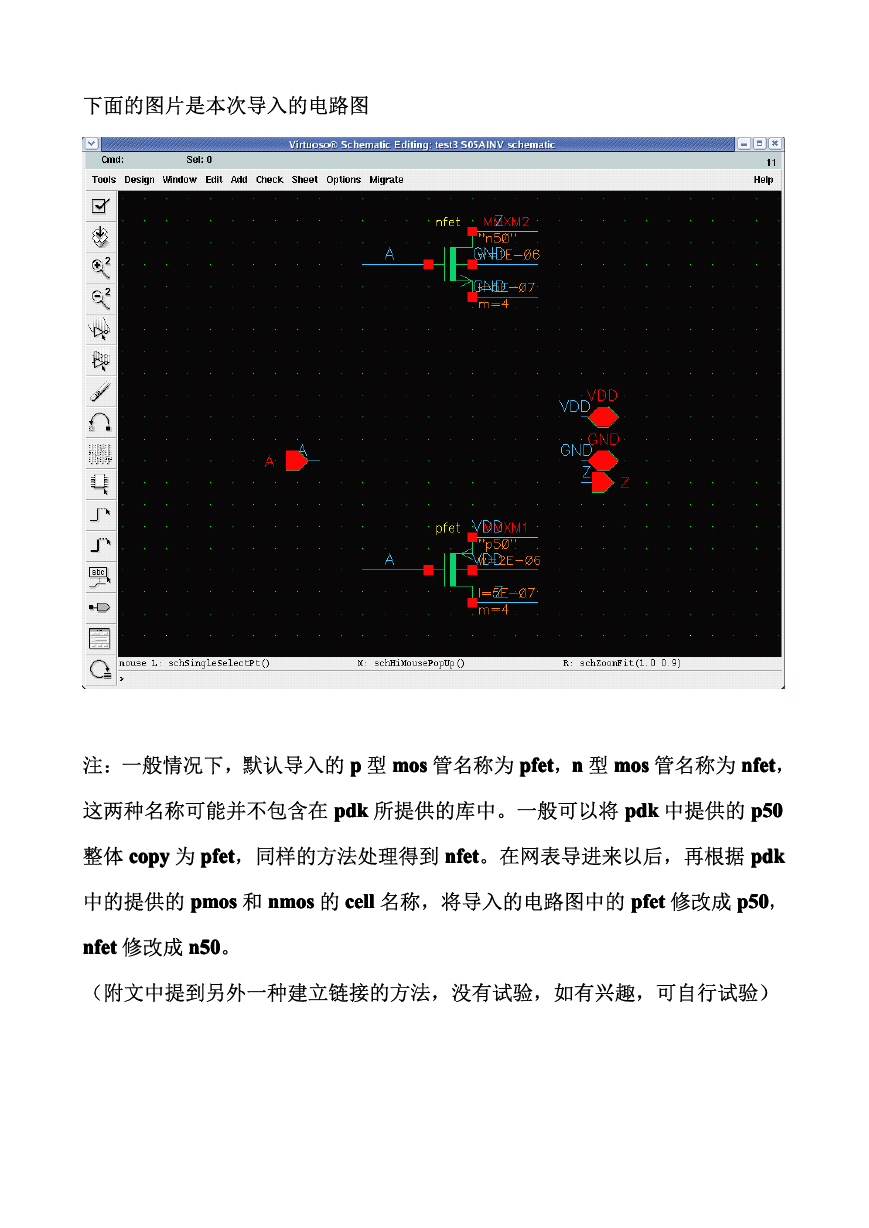

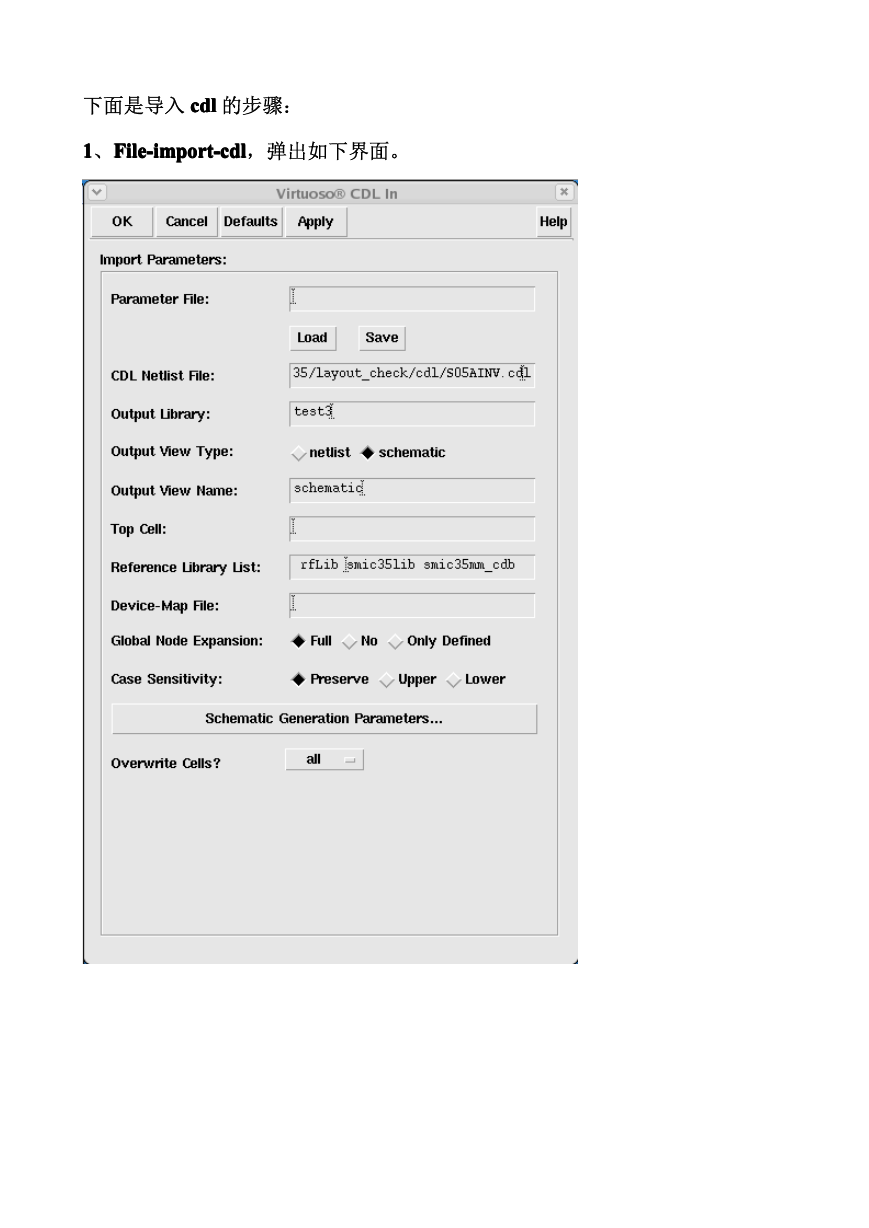

下面是导入 cdlcdlcdlcdl 的步骤:

File-import-cdl

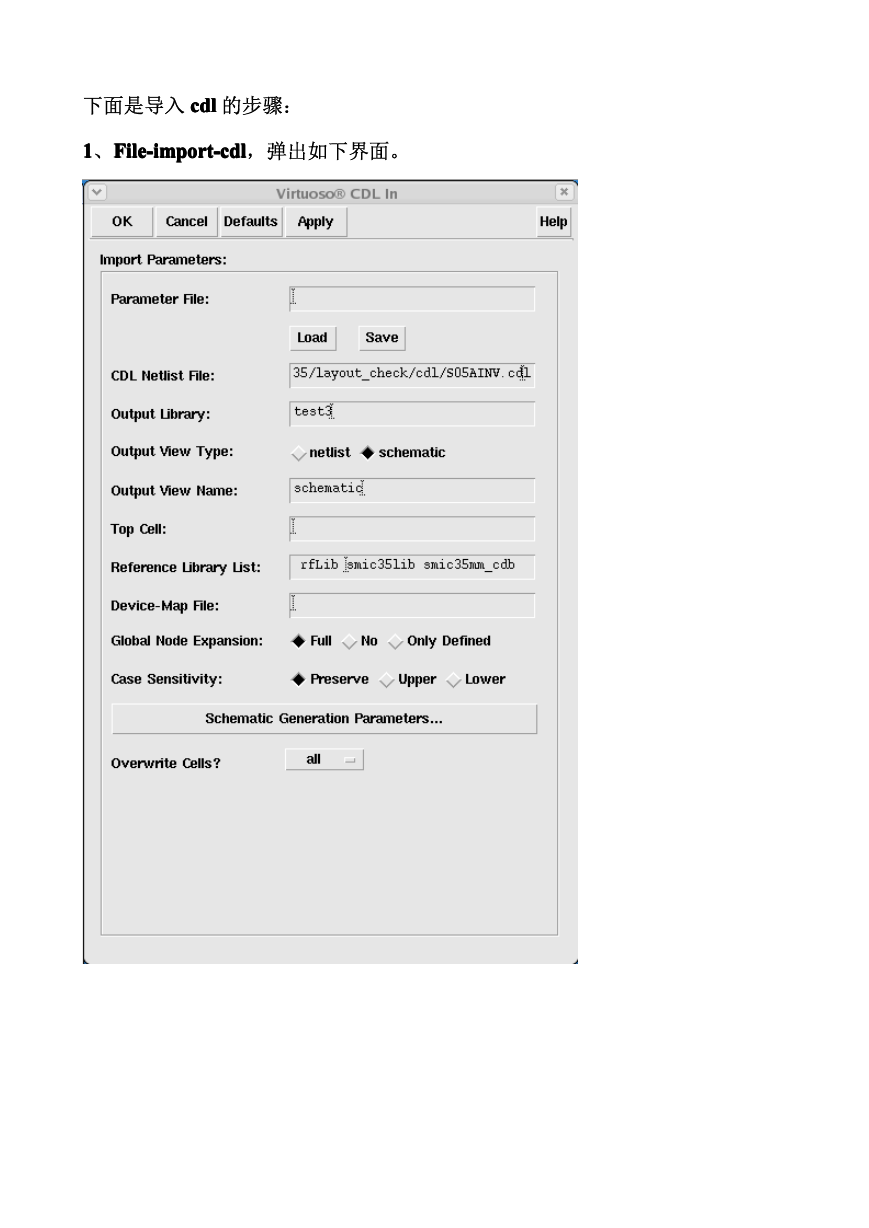

1111、File-import-cdl

File-import-cdl

File-import-cdl,弹出如下界面。

�

具体的解释如下:

Parameter File:

相当于一个模板文件,一般第一次导入的时候是没有的,需要自己创建。

Load

Save

Parameter

LoadLoadLoadLoad ::::如果已经有一个模板文件,需要在“Parameter

Parameter FileFileFileFile”后面输入此文件路径及名称

Parameter

SaveSaveSaveSave:保存此次的设置,也就是保存一个模板文件。此时就需要在“Parameter

Parameter

Parameter FileFileFileFile”后面输入文件路径

Parameter

及名称

CDL Netlist File:/home/xhw/cadence_smic35/layout_check/cdl/S05AINV.cdl

/home/xhw/cadence_smic35/layout_check/cdl/S05AINV.cdl

/home/xhw/cadence_smic35/layout_check/cdl/S05AINV.cdl

想到导入网表的路径及名称:“/home/xhw/cadence_smic35/layout_check/cdl/S05AINV.cdl

/home/xhw/cadence_smic35/layout_check/cdl/S05AINV.cdl”。此处是一个简

单的反相器的网表。(承接上文)

Output Library:test3

test3

test3

test3

test3

导入的库的名称:test3

test3”的库)如果这个库已经在

test3。(因为是一个示例,此处我要新建一个名称为 “test3

test3

manager

library

manager

library

test3

当前的 library

manager 中存在,直接导入;如果不存在,将自动创建一个新的库命名为 “test3

library manager

test3”。

Output View Type:netlist/schematic

schematic

netlist/schematic

netlist/schematic

schematic

netlist/schematic。一般选择 schematic

导入的形式:netlist/schematic

schematic。

Output View Name:schematic

解释同上

Top Cell:

顶层的 cellcellcellcell 名称。如果网表属于层次化的,此处可以定义从中任意的抽取一个 cellcellcellcell 作为顶层来导入,而不

至于导入一个整体的网表;如果不填写,将导入整个网表。

Reference Library List:

列出一些参考链接库(可能与此库有关系的一些库)

ahdlLib analogLib basic cdsDefTechLib functional refWin rfExamples rfLib smic35mm_cdb

此处列出的都是一些基本的库,还有一个是本次项目所用到的 pdkpdkpdkpdk 所提供的库

Device-Map File:

器件的映射转换文件,对于器件类型简单的,没有的话可以不填。类型比较多的,则需要定义一下 。(附

文中有讲到如何创建这个文件)

Global Node Expansion:Full/No/Only Defined

全局的节点扩展:全部执行////不执行////只针对定义的部分执行

Case Sensitivity:Preserve/Upper/Lower

字体的大小写区分:保持不变////全部变成大写////全部变成小写

Schematic Generation Parameters...

合成的一些参数设置(本文只讲下面一项)

Full Place and Route:

CellCellCellCell 之间是否需要连线(连线以后比较乱,不连线将分列显示,标出 netnetnetnet 名称)

Overwrite Cells? all/none/selected

是否需要覆盖已有的 cellcellcellcell? 全部覆盖////全不覆盖////只针对选择的进行覆盖(将弹出另外一截窗口供选择,此

处不再详述)

设置完毕,点击“Apply”,同时关注一下 CIW 窗口中的显示信息。(如果网表较大,需耐心等待。)

一般情况下,设置没有问题的话,导入都会成功;但某些时候如果导入失败,需要到 icfb 启动的路径下打

开“ni.log”这个文件,查看具体的报错信息,按照指示进行相关的修改设置等。然后再次“Apply”,如此

循环,直到成功为止。

�

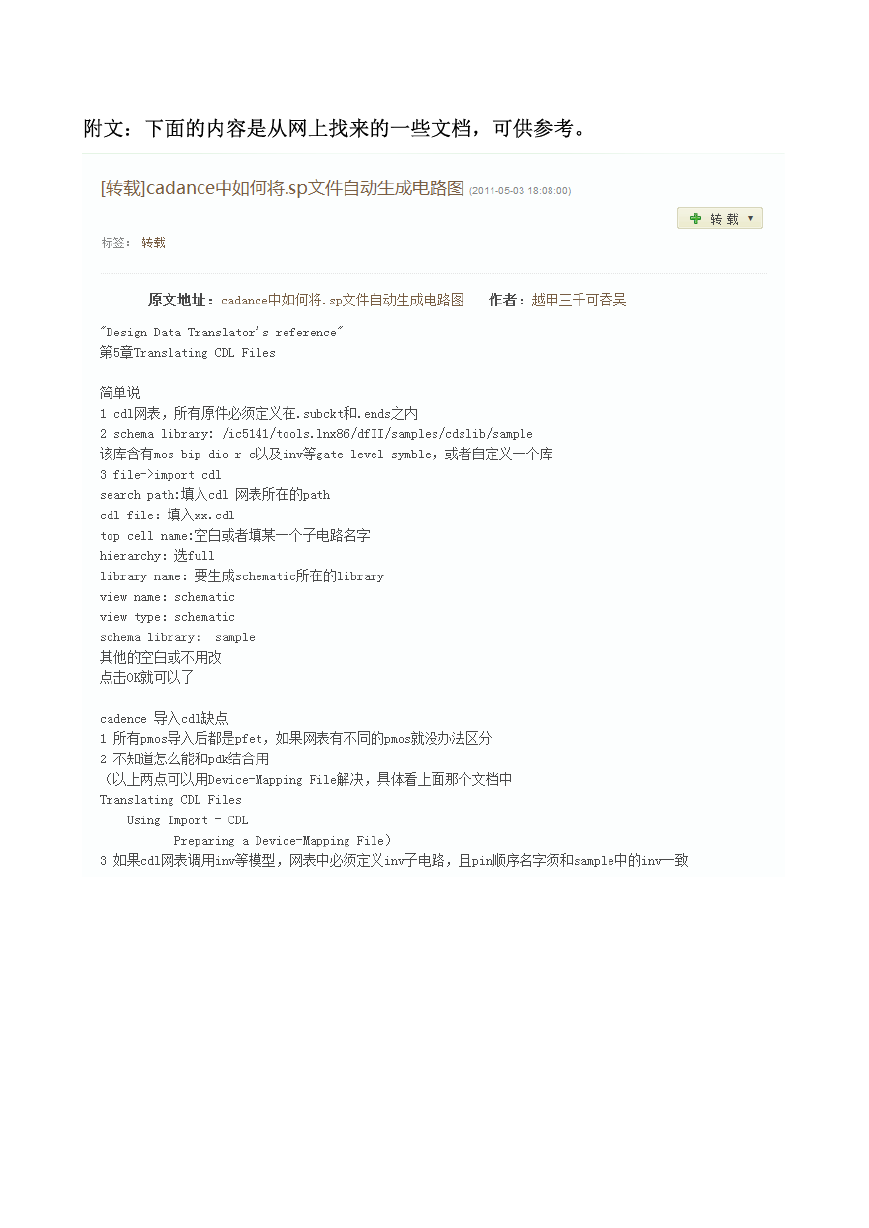

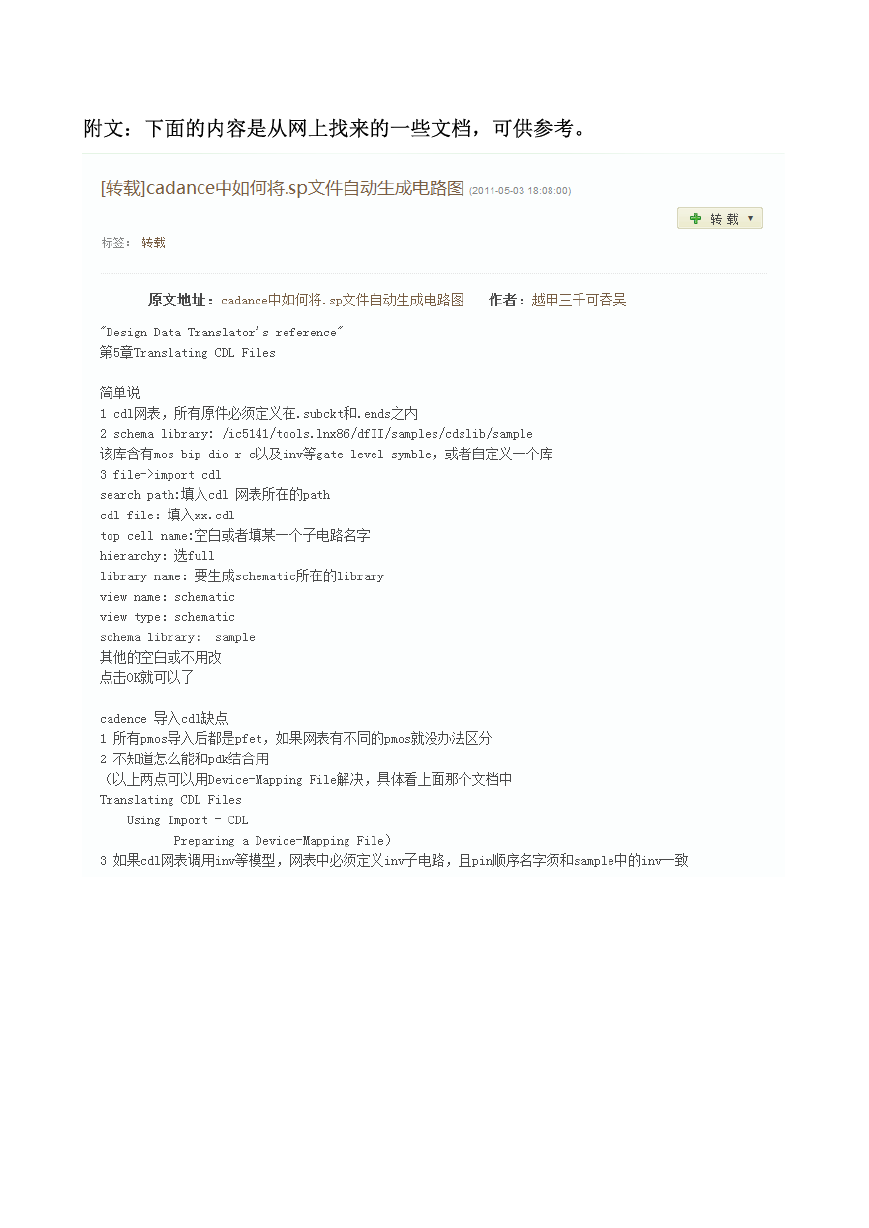

下面的图片是本次导入的电路图

注:一般情况下,默认导入的 pppp 型 mosmosmosmos 管名称为 pfetpfetpfetpfet,nnnn 型 mosmosmosmos 管名称为 nfetnfetnfetnfet,

这两种名称可能并不包含在 pdkpdkpdkpdk 所提供的库中。一般可以将 pdkpdkpdkpdk 中提供的 p5p5p5p50000

copy

copy 为 pfetpfetpfetpfet,同样的方法处理得到 nfetnfetnfetnfet。在网表导进来以后,再根据 pdpdpdpdkkkk

copy

整体 copy

nmos

pmos

nmos 的 cellcellcellcell 名称,将导入的电路图中的 pfetpfetpfetpfet 修改成 p50p50p50p50,

pmos

nmos

pmos 和 nmos

中的提供的 pmos

nfetnfetnfetnfet 修改成 n50n50n50n50。

(附文中提到另外一种建立链接的方法,没有试验,如有兴趣,可自行试验)

�

附文:下面的内容是从网上找来的一些文档,可供参考。

�

下面这段文档介绍了 Devicemapfile 的创建:

建一个 Devicemap 文件,把网表中的器件用需要替换的器件代替:

网表

库

devMap := Resistor

rm1

propMatch := subType

M1(电阻的不同类型)

devMap := Resistor

rphpoly

devMap := nfet nmos2v

propMatch := subType N

devMap := pfet pmos2v

propMatch := subType P

devMap := Diode diodesd3v

propMatch := subType DB

有更简单的办法. CDL 导入是默认参考到 sample 这个库的。其实它

也只能参考这个库才能成功。所以最简单的就是在 sample 库里面把

nfet 做一个 softlink 指向 foundry 提供的 PDK 库里面就可以了。完

全可以仿真。我自己就是这么做的。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc