Preface

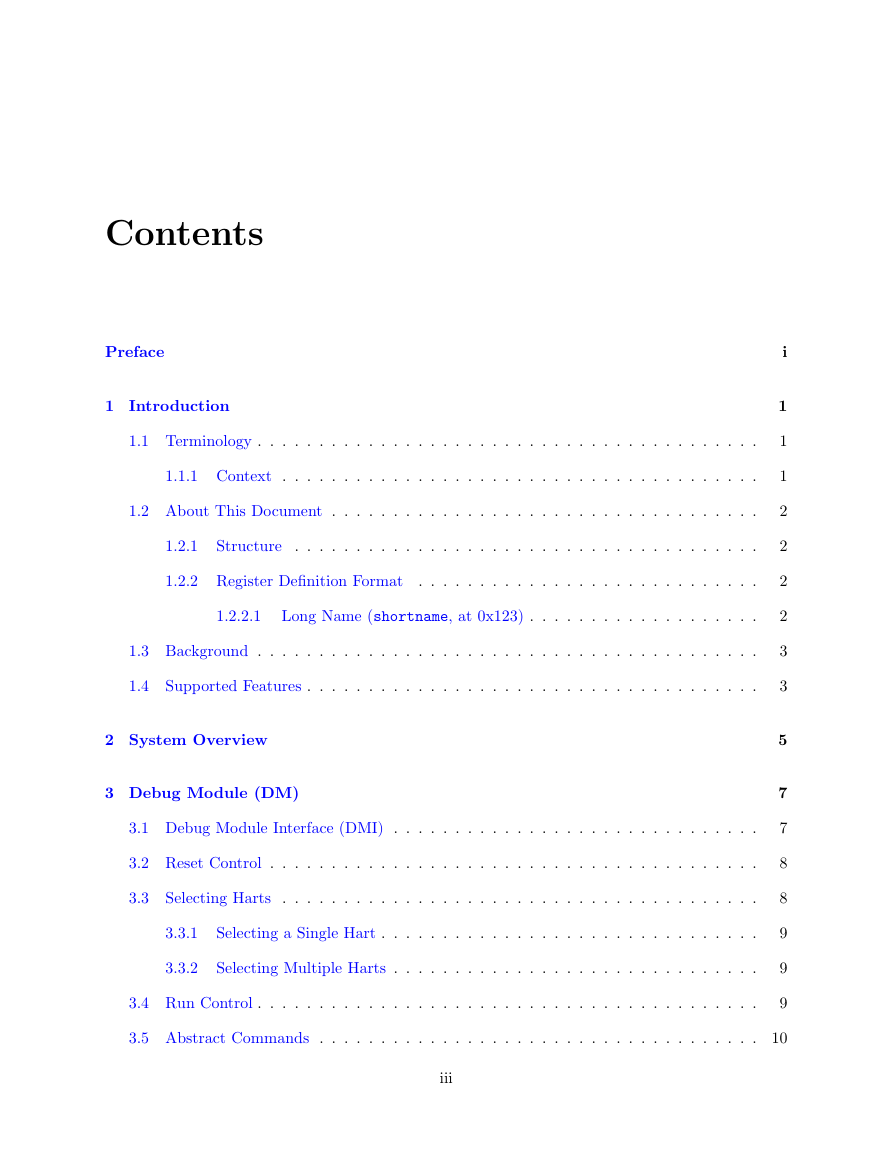

Introduction

Terminology

Context

About This Document

Structure

Register Definition Format

Long Name (shortname, at 0x123)

Background

Supported Features

System Overview

Debug Module (DM)

Debug Module Interface (DMI)

Reset Control

Selecting Harts

Selecting a Single Hart

Selecting Multiple Harts

Run Control

Abstract Commands

Abstract Command Listing

Access Register

Quick Access

Program Buffer

Overview of States

System Bus Access

Quick Access

Security

Debug Module DMI Registers

Debug Module Status (dmstatus, at 0x11)

Debug Module Control (dmcontrol, at 0x10)

Hart Info (hartinfo, at 0x12)

Halt Summary (haltsum, at 0x13)

Hart Array Window Select (hawindowsel, at 0x14)

Hart Array Window (hawindow, at 0x15)

Abstract Control and Status (abstractcs, at 0x16)

Abstract Command (command, at 0x17)

Abstract Command Autoexec (abstractauto, at 0x18)

Device Tree Addr 0 (devtreeaddr0, at 0x19)

Abstract Data 0 (data0, at 0x04)

Program Buffer 0 (progbuf0, at 0x20)

Authentication Data (authdata, at 0x30)

System Bus Access Control and Status (sbcs, at 0x38)

System Bus Address 31:0 (sbaddress0, at 0x39)

System Bus Address 63:32 (sbaddress1, at 0x3a)

System Bus Address 95:64 (sbaddress2, at 0x3b)

System Bus Data 31:0 (sbdata0, at 0x3c)

System Bus Data 63:32 (sbdata1, at 0x3d)

System Bus Data 95:64 (sbdata2, at 0x3e)

System Bus Data 127:96 (sbdata3, at 0x3f)

RISC-V Debug

Debug Mode

Load-Reserved/Store-Conditional Instructions

Single Step

Reset

dret Instruction

Core Debug Registers

Debug Control and Status (dcsr, at 0x7b0)

Debug PC (dpc, at 0x7b1)

Debug Scratch Register 0 (dscratch0, at 0x7b2)

Debug Scratch Register 1 (dscratch1, at 0x7b3)

Virtual Debug Registers

Privilege Level (priv, at virtual)

Trigger Module

Trigger Registers

Trigger Select (tselect, at 0x7a0)

Trigger Data 1 (tdata1, at 0x7a1)

Trigger Data 2 (tdata2, at 0x7a2)

Trigger Data 3 (tdata3, at 0x7a3)

Match Control (mcontrol, at 0x7a1)

Instruction Count (icount, at 0x7a1)

Debug Transport Module (DTM)

JTAG Debug Transport Module

JTAG Background

JTAG DTM Registers

IDCODE (at 0x01)

DTM Control and Status (dtmcs, at 0x10)

Debug Module Interface Access (dmi, at 0x11)

BYPASS (at 0x1f)

Recommended JTAG Connector

Hardware Implementations

Abstract Command Based

Execution Based

Debugger Implementation

Debug Module Interface Access

Main Loop

Halting

Running

Single Step

Accessing Registers

Using Abstract Command

Using Program Buffer

Reading Memory

Using System Bus Access

Using Program Buffer

Writing Memory

Using System Bus Access

Using Program Buffer

Handling Exceptions

Quick Access

Future Ideas

Serial Ports

Serial Control and Status (sercs, at 0x34)

Serial TX Data (sertx, at 0x35)

Serial RX Data (serrx, at 0x36)

Index

Change Log

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc