ARM Generic Interrupt Controller Architecture Specification GIC architecture version 3.0 and version 4.0

Contents

Preface

About this specification

Intended audience

Using this specification

Conventions

Typographic conventions

Signals

Numbers

Pseudocode descriptions

Additional reading

ARM publications

Other publications

Feedback

Feedback on this manual

1: Introduction

1.1 About the Generic Interrupt Controller (GIC)

1.1.1 Changes to the GIC architecture from GICv2

1.2 Terminology

1.2.1 Interrupt types

1.2.2 Interrupt states

1.2.3 Models for handling interrupts

1.2.4 Additional terms

1.3 Supported configurations and compatibility

1.3.1 Affinity routing configuration

1.3.2 System register configuration

1.3.3 GIC control and configuration

1.3.4 References to the ARMv8 architectural state

1.3.5 GICv3 with no legacy operation

1.3.6 GICv3 with legacy operation

2: Distribution and Routing of Interrupts

2.1 The Distributor and Redistributors

2.2 INTIDs

2.2.1 Special INTIDs

2.2.2 Implementations with mixed INTD sizes

2.2.3 Valid interrupt ID check pseudocode

2.3 Affinity routing

2.3.1 Routing SPIs and SGIs by PE affinity

2.3.2 Participating nodes

2.3.3 Changing affinity routing enables

3: GIC Partitioning

3.1 The GIC logical components

3.2 Interrupt bypass support

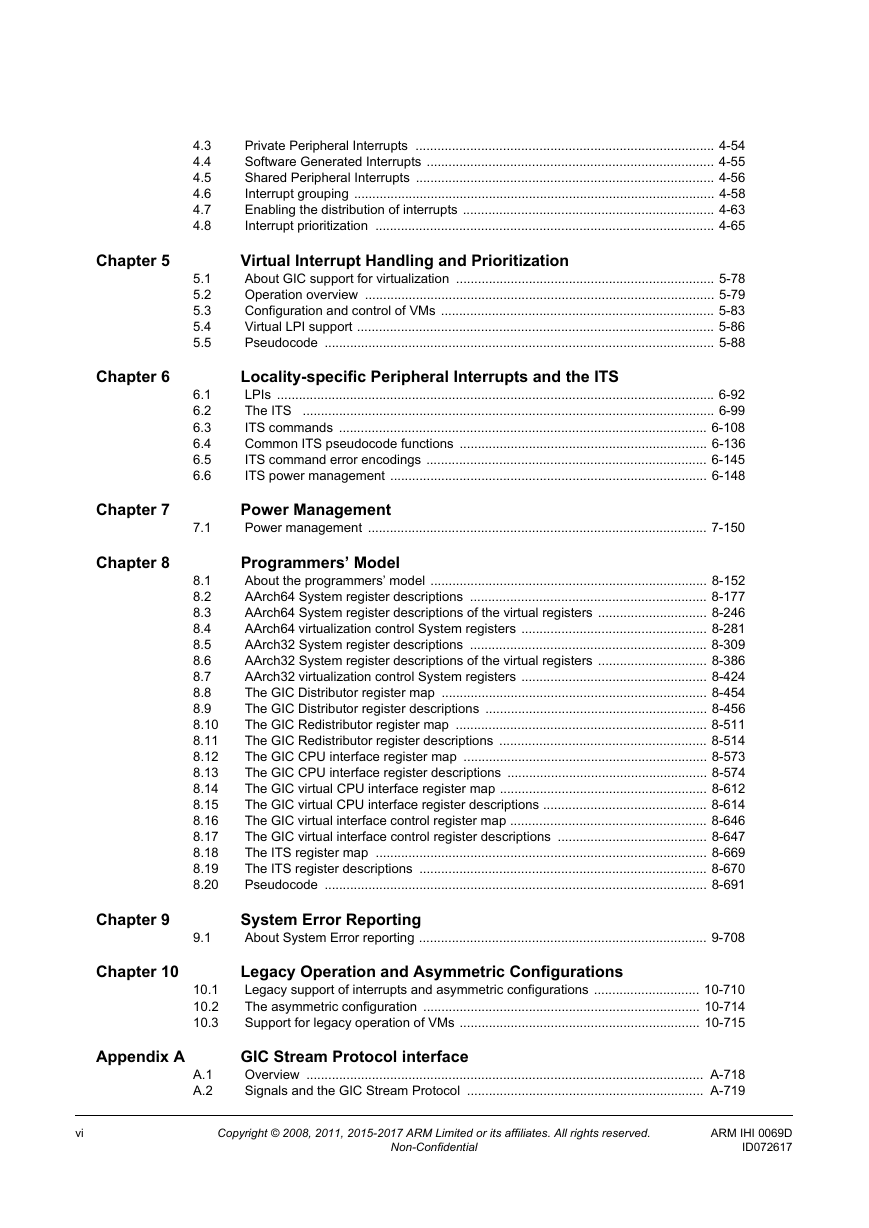

4: Physical Interrupt Handling and Prioritization

4.1 Interrupt lifecycle

4.1.1 Physical CPU interface

4.1.2 Interrupt handling state machine

4.2 Locality-specific Peripheral Interrupts

4.3 Private Peripheral Interrupts

4.4 Software Generated Interrupts

4.5 Shared Peripheral Interrupts

4.6 Interrupt grouping

4.6.1 Interrupt grouping and security

4.6.2 Interrupt assignment to IRQ and FIQ signals

4.6.3 Interrupt routing and System register access

4.7 Enabling the distribution of interrupts

4.7.1 Enabling individual interrupts

4.7.2 Interaction of group and individual interrupt enables

4.7.3 Effect of disabling interrupts

4.8 Interrupt prioritization

4.8.1 Non-secure accesses to register fields for Secure interrupt priorities

4.8.2 Priority grouping

4.8.3 System register access to the Active Priorities registers

4.8.4 Preemption

4.8.5 Priority masking

4.8.6 Software accesses of interrupt priority

4.8.7 Changing the priority of enabled PPIs, SGIs, and SPIs

5: Virtual Interrupt Handling and Prioritization

5.1 About GIC support for virtualization

5.2 Operation overview

5.2.1 Usage model for the List registers

5.2.2 List register usage resulting in UNPREDICTABLE behavior

5.3 Configuration and control of VMs

5.3.1 Association of virtual interrupts with physical interrupts

5.3.2 The Active Priorities registers

5.3.3 Maintenance interrupts

5.4 Virtual LPI support

5.4.1 Direct injection of virtual interrupts

5.4.2 Doorbell interrupts

5.5 Pseudocode

6: Locality-specific Peripheral Interrupts and the ITS

6.1 LPIs

6.1.1 LPI Configuration tables

6.1.2 LPI Pending tables

6.1.3 Virtual LPI Configuration tables and virtual LPI Pending tables

6.2 The ITS

6.2.1 The ITS tables

6.2.2 Interrupt collections

6.2.3 The Device table

6.2.4 The Interrupt translation table

6.2.5 The Collection table

6.2.6 The vPE table

6.2.7 Control and configuration of the ITS

6.2.8 The ITS command interface

6.2.9 Ordering of translations with the output to ITS commands

6.2.10 Restrictions for INTID mapping rules

6.3 ITS commands

6.3.1 IMPLEMENTATION DEFINED sizes in ITS command parameters

6.3.2 Command errors

6.3.3 CLEAR

6.3.4 DISCARD

6.3.5 INT

6.3.6 INV

6.3.7 INVALL

6.3.8 MAPC

6.3.9 MAPD

6.3.10 MAPI

6.3.11 MAPTI

6.3.12 MOVALL

6.3.13 MOVI

6.3.14 SYNC

6.3.15 VINVALL

6.3.16 VMAPI

6.3.17 VMAPP

6.3.18 VMAPTI

6.3.19 VMOVI

6.3.20 VMOVP

6.3.21 VSYNC

6.4 Common ITS pseudocode functions

6.4.1 ITS helper functions

6.5 ITS command error encodings

6.6 ITS power management

6.6.1 Enabling an ITS

6.6.2 Disabling an ITS

7: Power Management

7.1 Power management

8: Programmers’ Model

8.1 About the programmers’ model

8.1.1 GIC register names

8.1.2 Relation between System registers and memory-mapped registers

8.1.3 GIC memory-mapped register access

8.1.4 Access to memory-mapped registers when System register access is enabled

8.1.5 Execution state

8.1.6 Observability of the effects of accesses to the GIC registers

8.1.7 GIC System register access

8.1.8 Access to Common registers

8.1.9 Traps and enables for the ICC_SRE_ELx registers

8.1.10 Use of control registers for SGI forwarding

8.1.11 GIC Security States

8.1.12 Register banking

8.1.13 Identification registers

8.1.14 CPU interface register reset domain

8.2 AArch64 System register descriptions

8.2.1 ICC_AP0R_EL1, Interrupt Controller Active Priorities Group 0 Registers, n = 0 - 3

8.2.2 ICC_AP1R_EL1, Interrupt Controller Active Priorities Group 1 Registers, n = 0 - 3

8.2.3 ICC_ASGI1R_EL1, Interrupt Controller Alias Software Generated Interrupt Group 1 Register

8.2.4 ICC_BPR0_EL1, Interrupt Controller Binary Point Register 0

8.2.5 ICC_BPR1_EL1, Interrupt Controller Binary Point Register 1

8.2.6 ICC_CTLR_EL1, Interrupt Controller Control Register (EL1)

8.2.7 ICC_CTLR_EL3, Interrupt Controller Control Register (EL3)

8.2.8 Interrupt Controller Deactivate Interrupt Register

8.2.9 ICC_EOIR0_EL1, Interrupt Controller End Of Interrupt Register 0

8.2.10 ICC_EOIR1_EL1, Interrupt Controller End Of Interrupt Register 1

8.2.11 ICC_HPPIR0_EL1, Interrupt Controller Highest Priority Pending Interrupt Register 0

8.2.12 ICC_HPPIR1_EL1, Interrupt Controller Highest Priority Pending Interrupt Register 1

8.2.13 ICC_IAR0_EL1, Interrupt Controller Interrupt Acknowledge Register 0

8.2.14 ICC_IAR1_EL1, Interrupt Controller Interrupt Acknowledge Register 1

8.2.15 ICC_IGRPEN0_EL1, Interrupt Controller Interrupt Group 0 Enable register

8.2.16 ICC_IGRPEN1_EL1, Interrupt Controller Interrupt Group 1 Enable register

8.2.17 ICC_IGRPEN1_EL3, Interrupt Controller Interrupt Group 1 Enable register (EL3)

8.2.18 ICC_PMR_EL1, Interrupt Controller Interrupt Priority Mask Register

8.2.19 ICC_RPR_EL1, Interrupt Controller Running Priority Register

8.2.20 ICC_SGI0R_EL1, Interrupt Controller Software Generated Interrupt Group 0 Register

8.2.21 ICC_SGI1R_EL1, Interrupt Controller Software Generated Interrupt Group 1 Register

8.2.22 ICC_SRE_EL1, Interrupt Controller System Register Enable register (EL1)

8.2.23 ICC_SRE_EL2, Interrupt Controller System Register Enable register (EL2)

8.2.24 ICC_SRE_EL3, Interrupt Controller System Register Enable register (EL3)

8.3 AArch64 System register descriptions of the virtual registers

8.3.1 ICV_AP0R_EL1, Interrupt Controller Virtual Active Priorities Group 0 Registers, n = 0 - 3

8.3.2 ICV_AP1R_EL1, Interrupt Controller Virtual Active Priorities Group 1 Registers, n = 0 - 3

8.3.3 ICV_BPR0_EL1, Interrupt Controller Virtual Binary Point Register 0

8.3.4 ICV_BPR1_EL1, Interrupt Controller Virtual Binary Point Register 1

8.3.5 ICV_CTLR_EL1, Interrupt Controller Virtual Control Register

8.3.6 ICV_DIR_EL1, Interrupt Controller Deactivate Virtual Interrupt Register

8.3.7 ICV_EOIR0_EL1, Interrupt Controller Virtual End Of Interrupt Register 0

8.3.8 ICV_EOIR1_EL1, Interrupt Controller Virtual End Of Interrupt Register 1

8.3.9 ICV_HPPIR0_EL1, Interrupt Controller Virtual Highest Priority Pending Interrupt Register 0

8.3.10 ICV_HPPIR1_EL1, Interrupt Controller Virtual Highest Priority Pending Interrupt Register 1

8.3.11 ICV_IAR0_EL1, Interrupt Controller Virtual Interrupt Acknowledge Register 0

8.3.12 ICV_IAR1_EL1, Interrupt Controller Virtual Interrupt Acknowledge Register 1

8.3.13 ICV_IGRPEN0_EL1, Interrupt Controller Virtual Interrupt Group 0 Enable register

8.3.14 ICV_IGRPEN1_EL1, Interrupt Controller Virtual Interrupt Group 1 Enable register

8.3.15 ICV_PMR_EL1, Interrupt Controller Virtual Interrupt Priority Mask Register

8.3.16 ICV_RPR_EL1, Interrupt Controller Virtual Running Priority Register

8.4 AArch64 virtualization control System registers

8.4.1 ICH_AP0R_EL2, Interrupt Controller Hyp Active Priorities Group 0 Registers, n = 0 - 3

8.4.2 ICH_AP1R_EL2, Interrupt Controller Hyp Active Priorities Group 1 Registers, n = 0 - 3

8.4.3 ICH_EISR_EL2, Interrupt Controller End of Interrupt Status Register

8.4.4 ICH_ELRSR_EL2, Interrupt Controller Empty List Register Status Register

8.4.5 ICH_HCR_EL2, Interrupt Controller Hyp Control Register

8.4.6 ICH_LR_EL2, Interrupt Controller List Registers, n = 0 - 15

8.4.7 ICH_MISR_EL2, Interrupt Controller Maintenance Interrupt State Register

8.4.8 ICH_VMCR_EL2, Interrupt Controller Virtual Machine Control Register

8.4.9 ICH_VTR_EL2, Interrupt Controller VGIC Type Register

8.5 AArch32 System register descriptions

8.5.1 ICC_AP0R, Interrupt Controller Active Priorities Group 0 Registers, n = 0 - 3

8.5.2 ICC_AP1R, Interrupt Controller Active Priorities Group 1 Registers, n = 0 - 3

8.5.3 ICC_ASGI1R, Interrupt Controller Alias Software Generated Interrupt Group 1 Register

8.5.4 ICC_BPR0, Interrupt Controller Binary Point Register 0

8.5.5 ICC_BPR1, Interrupt Controller Binary Point Register 1

8.5.6 ICC_CTLR, Interrupt Controller Control Register

8.5.7 ICC_DIR, Interrupt Controller Deactivate Interrupt Register

8.5.8 ICC_EOIR0, Interrupt Controller End Of Interrupt Register 0

8.5.9 ICC_EOIR1, Interrupt Controller End Of Interrupt Register 1

8.5.10 ICC_HPPIR0, Interrupt Controller Highest Priority Pending Interrupt Register 0

8.5.11 ICC_HPPIR1, Interrupt Controller Highest Priority Pending Interrupt Register 1

8.5.12 ICC_HSRE, Interrupt Controller Hyp System Register Enable register

8.5.13 ICC_IAR0, Interrupt Controller Interrupt Acknowledge Register 0

8.5.14 ICC_IAR1, Interrupt Controller Interrupt Acknowledge Register 1

8.5.15 ICC_IGRPEN0, Interrupt Controller Interrupt Group 0 Enable register

8.5.16 ICC_IGRPEN1, Interrupt Controller Interrupt Group 1 Enable register

8.5.17 ICC_MCTLR, Interrupt Controller Monitor Control Register

8.5.18 ICC_MGRPEN1, Interrupt Controller Monitor Interrupt Group 1 Enable register

8.5.19 ICC_MSRE, Interrupt Controller Monitor System Register Enable register

8.5.20 ICC_PMR, Interrupt Controller Interrupt Priority Mask Register

8.5.21 ICC_RPR, Interrupt Controller Running Priority Register

8.5.22 ICC_SGI0R, Interrupt Controller Software Generated Interrupt Group 0 Register

8.5.23 ICC_SGI1R, Interrupt Controller Software Generated Interrupt Group 1 Register

8.5.24 ICC_SRE, Interrupt Controller System Register Enable register

8.6 AArch32 System register descriptions of the virtual registers

8.6.1 ICV_AP0R, Interrupt Controller Virtual Active Priorities Group 0 Registers, n = 0 - 3

8.6.2 ICV_AP1R, Interrupt Controller Virtual Active Priorities Group 1 Registers, n = 0 - 3

8.6.3 ICV_BPR0, Interrupt Controller Virtual Binary Point Register 0

8.6.4 ICV_BPR1, Interrupt Controller Virtual Binary Point Register 1

8.6.5 ICV_CTLR, Interrupt Controller Virtual Control Register

8.6.6 ICV_DIR, Interrupt Controller Deactivate Virtual Interrupt Register

8.6.7 ICV_EOIR0, Interrupt Controller Virtual End Of Interrupt Register 0

8.6.8 ICV_EOIR1, Interrupt Controller Virtual End Of Interrupt Register 1

8.6.9 ICV_HPPIR0, Interrupt Controller Virtual Highest Priority Pending Interrupt Register 0

8.6.10 ICV_HPPIR1, Interrupt Controller Virtual Highest Priority Pending Interrupt Register 1

8.6.11 ICV_IAR0, Interrupt Controller Virtual Interrupt Acknowledge Register 0

8.6.12 ICV_IAR1, Interrupt Controller Virtual Interrupt Acknowledge Register 1

8.6.13 ICV_IGRPEN0, Interrupt Controller Virtual Interrupt Group 0 Enable register

8.6.14 ICV_IGRPEN1, Interrupt Controller Virtual Interrupt Group 1 Enable register

8.6.15 ICV_PMR, Interrupt Controller Virtual Interrupt Priority Mask Register

8.6.16 ICV_RPR, Interrupt Controller Virtual Running Priority Register

8.7 AArch32 virtualization control System registers

8.7.1 ICH_AP0R, Interrupt Controller Hyp Active Priorities Group 0 Registers, n = 0 - 3

8.7.2 ICH_AP1R, Interrupt Controller Hyp Active Priorities Group 1 Registers, n = 0 - 3

8.7.3 ICH_EISR, Interrupt Controller End of Interrupt Status Register

8.7.4 ICH_ELRSR, Interrupt Controller Empty List Register Status Register

8.7.5 ICH_HCR, Interrupt Controller Hyp Control Register

8.7.6 ICH_LR, Interrupt Controller List Registers, n = 0 - 15

8.7.7 ICH_LRC, Interrupt Controller List Registers, n = 0 - 15

8.7.8 ICH_MISR, Interrupt Controller Maintenance Interrupt State Register

8.7.9 ICH_VMCR, Interrupt Controller Virtual Machine Control Register

8.7.10 ICH_VTR, Interrupt Controller VGIC Type Register

8.8 The GIC Distributor register map

8.9 The GIC Distributor register descriptions

8.9.1 GICD_CLRSPI_NSR, Clear Non-secure SPI Pending Register

8.9.2 GICD_CLRSPI_SR, Clear Secure SPI Pending Register

8.9.3 GICD_CPENDSGIR, SGI Clear-Pending Registers, n = 0 - 3

8.9.4 GICD_CTLR, Distributor Control Register

8.9.5 GICD_ICACTIVER, Interrupt Clear-Active Registers, n = 0 - 31

8.9.6 GICD_ICENABLER, Interrupt Clear-Enable Registers, n = 0 - 31

8.9.7 GICD_ICFGR, Interrupt Configuration Registers, n = 0 - 63

8.9.8 GICD_ICPENDR, Interrupt Clear-Pending Registers, n = 0 - 31

8.9.9 GICD_IGROUPR, Interrupt Group Registers, n = 0 - 31

8.9.10 GICD_IGRPMODR, Interrupt Group Modifier Registers, n = 0 - 31

8.9.11 GICD_IIDR, Distributor Implementer Identification Register

8.9.12 GICD_IPRIORITYR, Interrupt Priority Registers, n = 0 - 254

8.9.13 GICD_IROUTER, Interrupt Routing Registers, n = 32 - 1019

8.9.14 GICD_ISACTIVER, Interrupt Set-Active Registers, n = 0 - 31

8.9.15 GICD_ISENABLER, Interrupt Set-Enable Registers, n = 0 - 31

8.9.16 GICD_ISPENDR, Interrupt Set-Pending Registers, n = 0 - 31

8.9.17 GICD_ITARGETSR, Interrupt Processor Targets Registers, n = 0 - 254

8.9.18 GICD_NSACR, Non-secure Access Control Registers, n = 0 - 63

8.9.19 GICD_SETSPI_NSR, Set Non-secure SPI Pending Register

8.9.20 GICD_SETSPI_SR, Set Secure SPI Pending Register

8.9.21 GICD_SGIR, Software Generated Interrupt Register

8.9.22 GICD_SPENDSGIR, SGI Set-Pending Registers, n = 0 - 3

8.9.23 GICD_STATUSR, Error Reporting Status Register

8.9.24 GICD_TYPER, Interrupt Controller Type Register

8.10 The GIC Redistributor register map

8.11 The GIC Redistributor register descriptions

8.11.1 GICR_CLRLPIR, Clear LPI Pending Register

8.11.2 GICR_CTLR, Redistributor Control Register

8.11.3 GICR_ICACTIVER0, Interrupt Clear-Active Register 0

8.11.4 GICR_ICENABLER0, Interrupt Clear-Enable Register 0

8.11.5 GICR_ICFGR0, Interrupt Configuration Register 0

8.11.6 GICR_ICFGR1, Interrupt Configuration Register 1

8.11.7 GICR_ICPENDR0, Interrupt Clear-Pending Register 0

8.11.8 GICR_IGROUPR0, Interrupt Group Register 0

8.11.9 GICR_IGRPMODR0, Interrupt Group Modifier Register 0

8.11.10 GICR_IIDR, Redistributor Implementer Identification Register

8.11.11 GICR_INVALLR, Redistributor Invalidate All Register

8.11.12 GICR_INVLPIR, Redistributor Invalidate LPI Register

8.11.13 GICR_IPRIORITYR, Interrupt Priority Registers, n = 0 - 7

8.11.14 GICR_ISACTIVER0, Interrupt Set-Active Register 0

8.11.15 GICR_ISENABLER0, Interrupt Set-Enable Register 0

8.11.16 GICR_ISPENDR0, Interrupt Set-Pending Register 0

8.11.17 GICR_NSACR, Non-secure Access Control Register

8.11.18 GICR_PENDBASER, Redistributor LPI Pending Table Base Address Register

8.11.19 GICR_PROPBASER, Redistributor Properties Base Address Register

8.11.20 GICR_SETLPIR, Set LPI Pending Register

8.11.21 GICR_STATUSR, Error Reporting Status Register

8.11.22 GICR_SYNCR, Redistributor Synchronize Register

8.11.23 GICR_TYPER, Redistributor Type Register

8.11.24 GICR_VPENDBASER, Virtual Redistributor LPI Pending Table Base Address Register

8.11.25 GICR_VPROPBASER, Virtual Redistributor Properties Base Address Register

8.11.26 GICR_WAKER, Redistributor Wake Register

8.12 The GIC CPU interface register map

8.13 The GIC CPU interface register descriptions

8.13.1 GICC_ABPR, CPU Interface Aliased Binary Point Register

8.13.2 GICC_AEOIR, CPU Interface Aliased End Of Interrupt Register

8.13.3 GICC_AHPPIR, CPU Interface Aliased Highest Priority Pending Interrupt Register

8.13.4 GICC_AIAR, CPU Interface Aliased Interrupt Acknowledge Register

8.13.5 GICC_APR, CPU Interface Active Priorities Registers, n = 0 - 3

8.13.6 GICC_BPR, CPU Interface Binary Point Register

8.13.7 GICC_CTLR, CPU Interface Control Register

8.13.8 GICC_DIR, CPU Interface Deactivate Interrupt Register

8.13.9 GICC_EOIR, CPU Interface End Of Interrupt Register

8.13.10 GICC_HPPIR, CPU Interface Highest Priority Pending Interrupt Register

8.13.11 GICC_IAR, CPU Interface Interrupt Acknowledge Register

8.13.12 GICC_IIDR, CPU Interface Identification Register

8.13.13 GICC_NSAPR, CPU Interface Non-secure Active Priorities Registers, n = 0 - 3

8.13.14 GICC_PMR, CPU Interface Priority Mask Register

8.13.15 GICC_RPR, CPU Interface Running Priority Register

8.13.16 GICC_STATUSR, CPU Interface Status Register

8.14 The GIC virtual CPU interface register map

8.15 The GIC virtual CPU interface register descriptions

8.15.1 GICV_ABPR, Virtual Machine Aliased Binary Point Register

8.15.2 GICV_AEOIR, Virtual Machine Aliased End Of Interrupt Register

8.15.3 GICV_AHPPIR, Virtual Machine Aliased Highest Priority Pending Interrupt Register

8.15.4 GICV_AIAR, Virtual Machine Aliased Interrupt Acknowledge Register

8.15.5 GICV_APR, Virtual Machine Active Priorities Registers, n = 0 - 3

8.15.6 GICV_BPR, Virtual Machine Binary Point Register

8.15.7 GICV_CTLR, Virtual Machine Control Register

8.15.8 GICV_DIR, Virtual Machine Deactivate Interrupt Register

8.15.9 GICV_EOIR, Virtual Machine End Of Interrupt Register

8.15.10 GICV_HPPIR, Virtual Machine Highest Priority Pending Interrupt Register

8.15.11 GICV_IAR, Virtual Machine Interrupt Acknowledge Register

8.15.12 GICV_IIDR, Virtual Machine CPU Interface Identification Register

8.15.13 GICV_PMR, Virtual Machine Priority Mask Register

8.15.14 GICV_RPR, Virtual Machine Running Priority Register

8.15.15 GICV_STATUSR, Virtual Machine Error Reporting Status Register

8.16 The GIC virtual interface control register map

8.17 The GIC virtual interface control register descriptions

8.17.1 GICH_APR, Active Priorities Registers, n = 0 - 3

8.17.2 GICH_EISR, End Interrupt Status Register

8.17.3 GICH_ELRSR, Empty List Register Status Register

8.17.4 GICH_HCR, Hypervisor Control Register

8.17.5 GICH_LR, List Registers, n = 0 - 15

8.17.6 GICH_MISR, Maintenance Interrupt Status Register

8.17.7 GICH_VMCR, Virtual Machine Control Register

8.17.8 GICH_VTR, Virtual Type Register

8.18 The ITS register map

8.19 The ITS register descriptions

8.19.1 GITS_BASER, ITS Translation Table Descriptors, n = 0 - 7

8.19.2 GITS_CBASER, ITS Command Queue Descriptor

8.19.3 GITS_CREADR, ITS Read Register

8.19.4 GITS_CTLR, ITS Control Register

8.19.5 GITS_CWRITER, ITS Write Register

8.19.6 GITS_IIDR, ITS Identification Register

8.19.7 GITS_TRANSLATER, ITS Translation Register

8.19.8 GITS_TYPER, ITS Type Register

8.20 Pseudocode

8.20.1 AArch64 functions

8.20.2 Functions for memory-mapped registers

9: System Error Reporting

9.1 About System Error reporting

9.1.1 Pseudocode

10: Legacy Operation and Asymmetric Configurations

10.1 Legacy support of interrupts and asymmetric configurations

10.1.1 Use of the special INTID 1022

10.1.2 Legacy configurations

10.1.3 Legacy operation and bypass support

10.2 The asymmetric configuration

10.2.1 Asymmetric operation and the use of ICC_CTLR_EL3.RM

10.3 Support for legacy operation of VMs

10.3.1 Accessing GIC virtual CPU interface registers using the memory-mapped register interface

A: GIC Stream Protocol interface

A.1 Overview

A.1.1 Terminology

A.2 Signals and the GIC Stream Protocol

A.2.1 Signals

A.2.2 Packet format

A.3 The GIC Stream Protocol

A.3.1 Rules associated with the downstream Redistributor commands

A.3.2 Rules associated with the upstream CPU interface commands

A.4 Alphabetic list of command and response packet formats

A.4.1 Activate (ICC)

A.4.2 Activate Acknowledge (IRI)

A.4.3 Clear (IRI)

A.4.4 Clear Acknowledge (ICC)

A.4.5 Deactivate (ICC)

A.4.6 Deactivate Acknowledge (IRI)

A.4.7 Downstream Control (IRI)

A.4.8 Downstream Control Acknowledge (ICC)

A.4.9 Generate SGI (ICC)

A.4.10 Generate SGI Acknowledge (IRI)

A.4.11 Quiesce (IRI)

A.4.12 Quiesce Acknowledge (ICC)

A.4.13 Release (ICC)

A.4.14 Set (IRI)

A.4.15 Upstream Control (ICC)

A.4.16 Upstream Control Acknowledge (IRI)

A.4.17 VClear (IRI)

A.4.18 VSet (IRI)

B: Pseudocode Definition

B.1 About ARM pseudocode

B.1.1 General limitations of ARM pseudocode

B.2 Data types

B.2.1 General data type rules

B.2.2 Bitstrings

B.2.3 Integers

B.2.4 Reals

B.2.5 Booleans

B.2.6 Enumerations

B.2.7 Lists

B.2.8 Arrays

B.3 Expressions

B.3.1 General expression syntax

B.3.2 Operators and functions - polymorphism and prototypes

B.3.3 Precedence rules

B.4 Operators and built-in functions

B.4.1 Operations on generic types

B.4.2 Operations on Booleans

B.4.3 Bitstring manipulation

B.4.4 Arithmetic

B.5 Statements and program structure

B.5.1 Simple statements

B.5.2 Compound statements

B.5.3 Comments

B.6 Pseudocode terminology

B.7 Miscellaneous helper procedures and support functions

B.7.1 Helper functions

B.7.2 Support functions

Glossary

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc