FFT 的 FPGA 实现

摘要:结合工程实践,介绍了一种利用 FFT IP Core 实现 FFT 的方法,设计能同时对两路实数序列进行 256 点 FFT

运算,并对转换结果进行求模平方运算,且对数据具有连续处理的能力。设计采用低成本的 FPGA 实现,具有成本低、性能高、

灵活性强、速度快等特点,而且通过工程应用证明了设计是正确可行的。

由于 FFT(快速傅里叶变换)的问世,促进了数字信号处理这门学科的成熟,它可应用于傅里叶变换理论所能涉及的任何领域。

FFT 传统实现

方法无非是软件(软件编程)和硬件(专用芯片 ASIC)两种,FPGA 的出现使人们在 FFT 的实现方面又多了一种选择。FPGA 同时具

有软件编程的灵活性和 ASIC 电路的快速性等优点,适合高速数字信号处理。大多数 FPGA 厂商都提供了可配置的逻辑核(Core)

实现各种算法功能,其中包括 FFT IP Core(知识产权核)。使用这些资源允许设计师将更多的时间和精力放在改善增加系统功能

上,这无疑将大大减少设计风险及缩短开发周期。

本设计采用了 Altera 公司的 FFT IP Core 实现 FFT 功能,可同时实现两路 256 点实数数据的 FFT 转换,并对转换结果进行求

模平方运算,设计对数据具有连续处理的能力。FPGA 芯片选用的是有史以来成本最低的 Altera 公司的 Cyclone 系列的芯片,FFT

内核是 Altera MegaCore FFT-V2.0.0,整个设计成本低、性能好,已经成功地应用到雷达产品中。

2 算法原理和 FFT Core 介绍

设计用到的算法包括同时计算两个实函数的 FFT 算法和 CORDIC 算法。

2.1 同时计算两个实函数的 FFT 算法

DFT(离散傅里叶变换)的定义为:

式(1)中,都假定时间函数 x(n)是一个复函数。但是在许多 FFT 的实际应用中,时间函数往往是实函数。下面介绍的算法可以有

效地减少实数序列 FFT 的计算工作量,从而提高计算速度。该方法可归纳为如下几个步骤:

①函数 h(n)和 g(n)是两个实函数,n=0,1,…,N-1;

②将其中的一个作为实部而另一个作为虚部,构成复函数 z(n)为:

z(n)=h(n)+jg(n), n=0,1,…,N-1;

③计算 z(n)的 N 点 DFT 得:

式中,Zr(k)和 Zi(k)分别是 Z(k)的实部和虚部;

④从 z(k)中分析出 H(k)和 G(k):

式中,H(k)和 G(k)分别是 h(n)和 g(n)的 DFT。

详细的推导过程参见文献[2]。

2.2 CORDIC 算法原理

CORDIC(The Coordinate Rotational Digital Computer)算法是一种循环迭代算法,其基本思想是用一系列与运算基数相关角度

的不断偏摆从而逼近所需旋转的角度。从广义上讲它是一个数值性计算逼近的方法,由于这些固定的角度与计算基数有关,运

算只有移位和加减。可用该算法来计算的函数包括乘、除、平方根、正弦、余弦正切、向量旋转(即复数乘法)以及指数运算等。

�

CORDIC 的基本原理如下。

向量 x+jy,旋转角度θ到向量 x'+jy',假设的方向用δ表示,旋转的角度为θi,并且θi 满足关系:tanθi=2i。则由文献[3]的推

导可知:

假设 x[0]=b,y[0]=a,z[0]=0,则有:

式中,

为畸变因子,对于字长一定的运算,它为一常数,如字长为 16 位时,K=1.6667。

δi 表示每一次旋转的方向,当 y[i]≥0 时,其值为 1;当 y[i]≤0 时,其值为-1。

2.3 FFT Core 简介

FFT-V2.0.0 是 Altera 公司 2004 年 2 月新发布的 FFT 知识产权核,它是一个高性能、高度参数化的快速傅里叶变换(FFT)处理

器,支持 Cyclone、

Stratix II、Stratix GX、Stratix 系列 FPGA 器件。该 FFT Core 功能是执行高性能的正向复数 FFT 或反向的 FFT(IFFT),采用基 2/4

频域抽取(DIF)的 FFT 算法,其转换长度为 2m,这里 6≤m≤14。在其内部,FFT 采用块浮点结构,以在最大信噪比(SNR)和最小

资源需求之间获得最大的收益。FFT Core 接收一个长度为 N 的、二进制补码格式、顺序输入的复数

序列作为输入,输出转换域的、顺序的复数数据序列。同时,一个累加块指数被输出,表示块浮点的量化因

子。FFT Core 的转换方向事先由一个输入端口为每个数据转换块指定。

FFT Core 可以设置两种不同的引擎结构:四输出(Quad-output FFT engine)和单输出(Single-output FFT engine)。对于要求转

换时间尽量小的应用,四输出引擎结构是最佳的选择;对于要求资源尽量少的应用,单输出引擎结构比较合适。为了增加整个

FFT Core 的吞吐量,可以采用多并行引擎结构。

FFT Core 支持 3 种 I/O 数据流结构:连续(streaming)、缓冲突发(Buffered Burst)、突发(Burst)。连续 I/O 数据流结构允许

处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发 I/O 数据流结构与连续结构相比,需要更少的

存储资源,但是,这是以减少平均吞吐量为代价的;突发数据流结构的操作与缓冲突发方式基本上一致,但突发方式则需要更

少的存储资源,这也是以降低吞吐量为代价的。

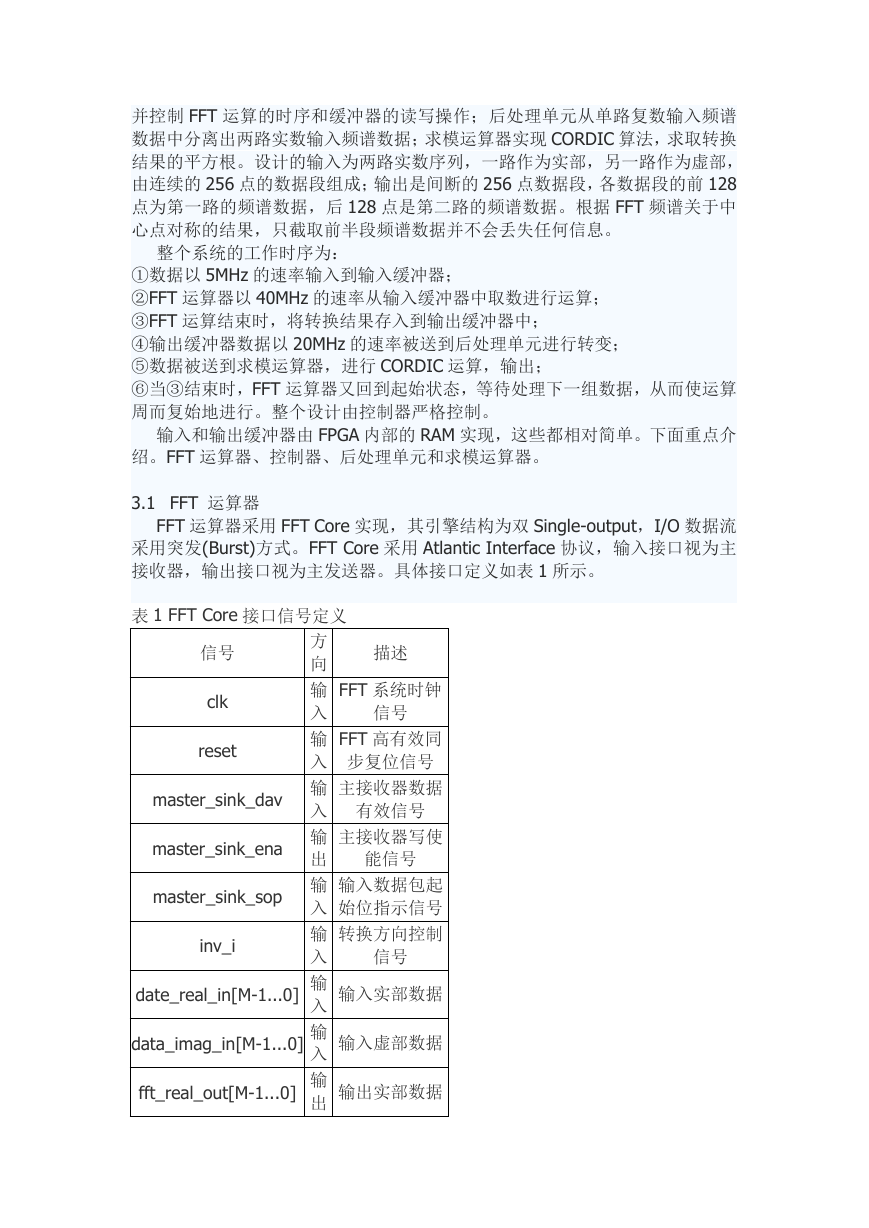

3 硬件设计

图 1 整体原理图

设计的整体原理图如图 1 所示。输入和输出缓冲器分别存储预处理数据和 FFT

转换结果;FFT 运算器负责 FFT 运算;控制器为输入和输出缓冲器提供读写地址,

�

并控制 FFT 运算的时序和缓冲器的读写操作;后处理单元从单路复数输入频谱

数据中分离出两路实数输入频谱数据;求模运算器实现 CORDIC 算法,求取转换

结果的平方根。设计的输入为两路实数序列,一路作为实部,另一路作为虚部,

由连续的 256 点的数据段组成;输出是间断的 256 点数据段,各数据段的前 128

点为第一路的频谱数据,后 128 点是第二路的频谱数据。根据 FFT 频谱关于中

心点对称的结果,只截取前半段频谱数据并不会丢失任何信息。

整个系统的工作时序为:

①数据以 5MHz 的速率输入到输入缓冲器;

②FFT 运算器以 40MHz 的速率从输入缓冲器中取数进行运算;

③FFT 运算结束时,将转换结果存入到输出缓冲器中;

④输出缓冲器数据以 20MHz 的速率被送到后处理单元进行转变;

⑤数据被送到求模运算器,进行 CORDIC 运算,输出;

⑥当③结束时,FFT 运算器又回到起始状态,等待处理下一组数据,从而使运算

周而复始地进行。整个设计由控制器严格控制。

输入和输出缓冲器由 FPGA 内部的 RAM 实现,这些都相对简单。下面重点介

绍。FFT 运算器、控制器、后处理单元和求模运算器。

3.1 FFT 运算器

FFT 运算器采用 FFT Core 实现,其引擎结构为双 Single-output,I/O 数据流

采用突发(Burst)方式。FFT Core 采用 Atlantic Interface 协议,输入接口视为主

接收器,输出接口视为主发送器。具体接口定义如表 1 所示。

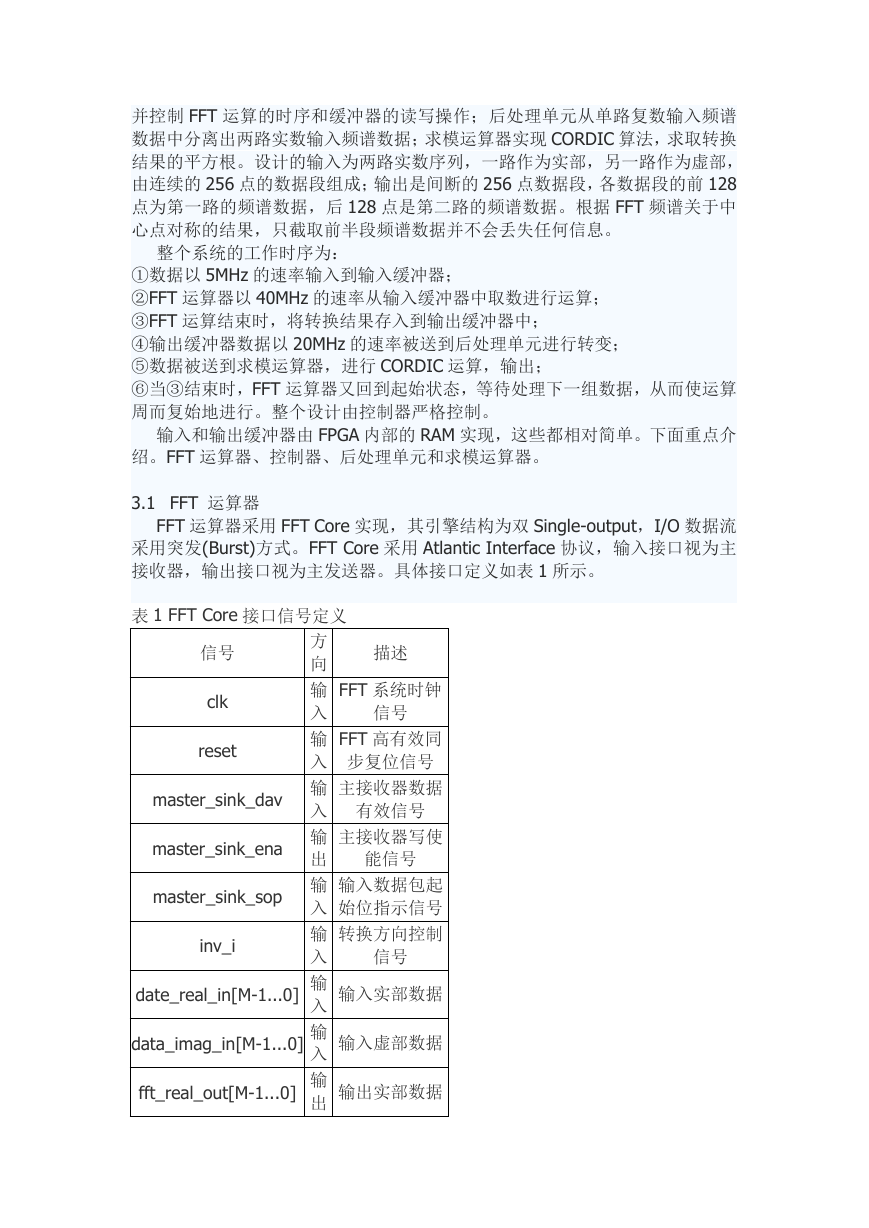

表 1 FFT Core 接口信号定义

信号

clk

reset

master_sink_dav

master_sink_ena

master_sink_sop

inv_i

date_real_in[M-1...0]

data_imag_in[M-1...0]

fft_real_out[M-1...0]

方

向

输

入

输

入

输

入

输

出

输

入

输

入

输

入

输

入

输

出

描述

FFT 系统时钟

信号

FFT 高有效同

步复位信号

主接收器数据

有效信号

主接收器写使

能信号

输入数据包起

始位指示信号

转换方向控制

信号

输入实部数据

输入虚部数据

输出实部数据

�

fft_imag_out[M-1...0]

exponent_out[5...0]

master_source_dav

master_source_cna

master_source_sop

master_source_eop

输

出

输

出

输

入

输

出

输

出

输

出

输出虚部数据

有符号数据块

指数

子接收器接收

有效指示信号

主发送器使能

信号

输出数据包起

始位

输出数据包结

束位

具体的工作流程:系统复位后,数据源将 master_sink_dav 置位,表示有采

样数据等待输入;作为回应,FFT Core 将 master_sink_ena 置位,表示可以接

收输入数据;数据源加载第一个复数数据,同时 master_sink_sop 置位,表示输

入数据块的起始;下一个时钟,master_sink_sop 被清零,输入数据按照自然顺

序被加入。输入数据达到 256 点时,系统自然启动 FFT 运算。通过 inv_i 信号的

置 位 / 清 零 可 以 改 变 单 个 数 据 块 的 FFT 转 换 方 向 , inv_i 信 号 必 须 和

master_sink_sop 信 号 严 格 同 步 。 当 FFT 转 换 结 束 时 , 子 接 收 器 已 经 将

master_source_dav 信号置位,表示子接收器可以接收 FFT 的转换结果;同时,

master_source_ena 信号置位,FFTCore 按照自然顺序输出运算结果;在输出过

程中,master_source_sop 和 master_source_eop 信号被置位,表示输出数据块

的起始和结束。详细的描述参见文献[4]。

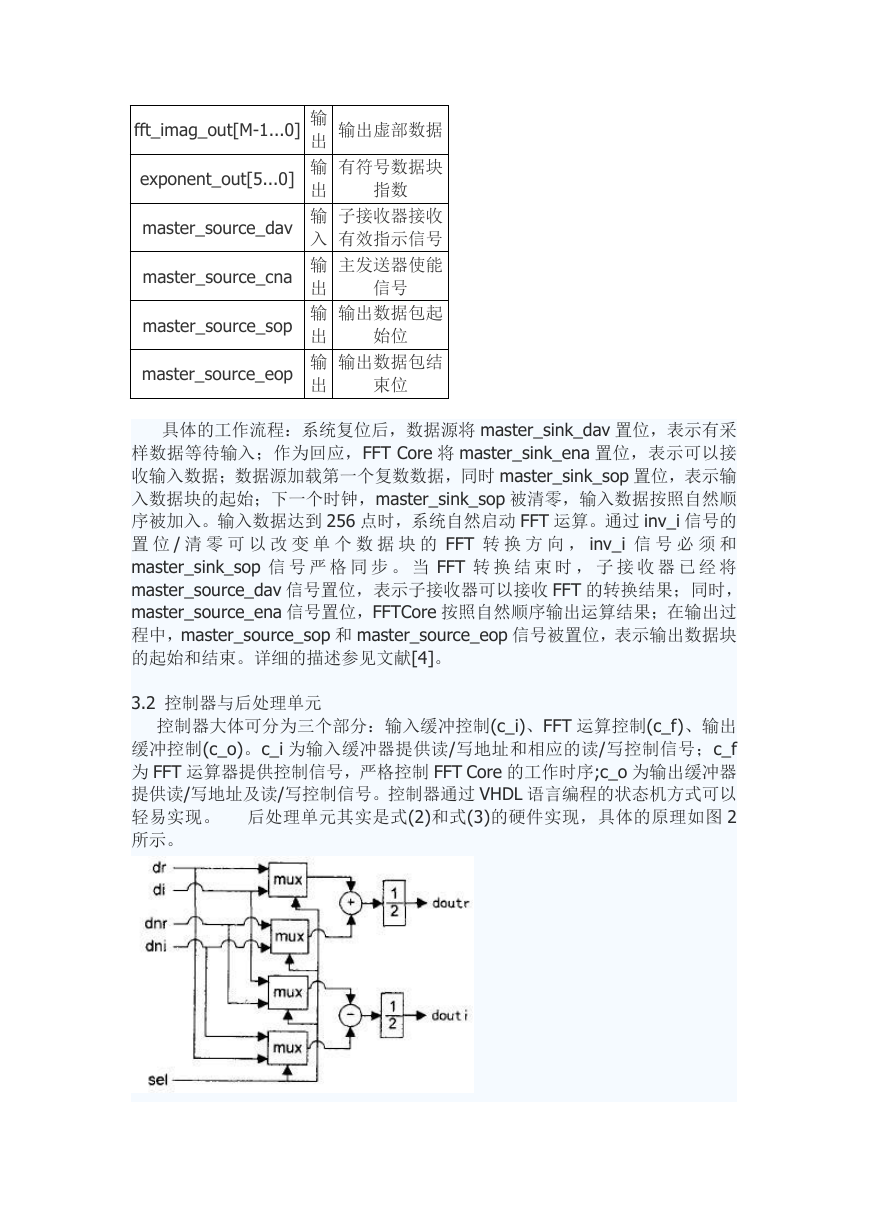

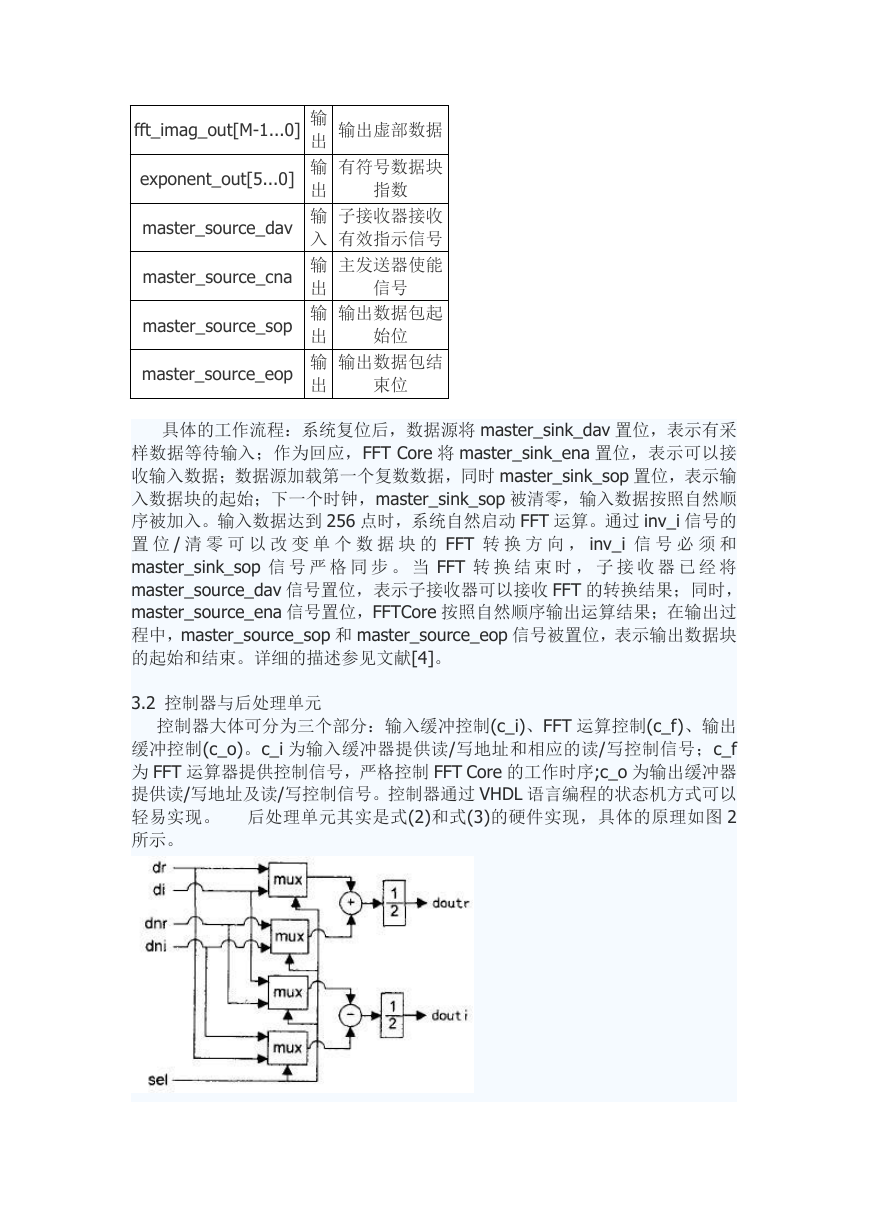

3.2 控制器与后处理单元

控制器大体可分为三个部分:输入缓冲控制(c_i)、FFT 运算控制(c_f)、输出

缓冲控制(c_o)。c_i 为输入缓冲器提供读/写地址和相应的读/写控制信号;c_f

为 FFT 运算器提供控制信号,严格控制 FFT Core 的工作时序;c_o 为输出缓冲器

提供读/写地址及读/写控制信号。控制器通过 VHDL 语言编程的状态机方式可以

轻易实现。 后处理单元其实是式(2)和式(3)的硬件实现,具体的原理如图 2

所示。

�

图 2 后处理单元原理图

图中标识“mux”、“+”、“-”、“1/2”分别表示选择器、加法器、减法器和除法器,

dr、di、dnr、dni 分别与式(1)和式(2)中的 Zr(k)、Zi(k)、Zr(N-k)、Zi(N-k)相对

应。当 sel 等于 0 时,提取第一路实序列的频谱数据 G(k),实现式(1)功能;当

sel 等于 1 时,提取第二路实序列的频谱数据,实现式(2)功能。

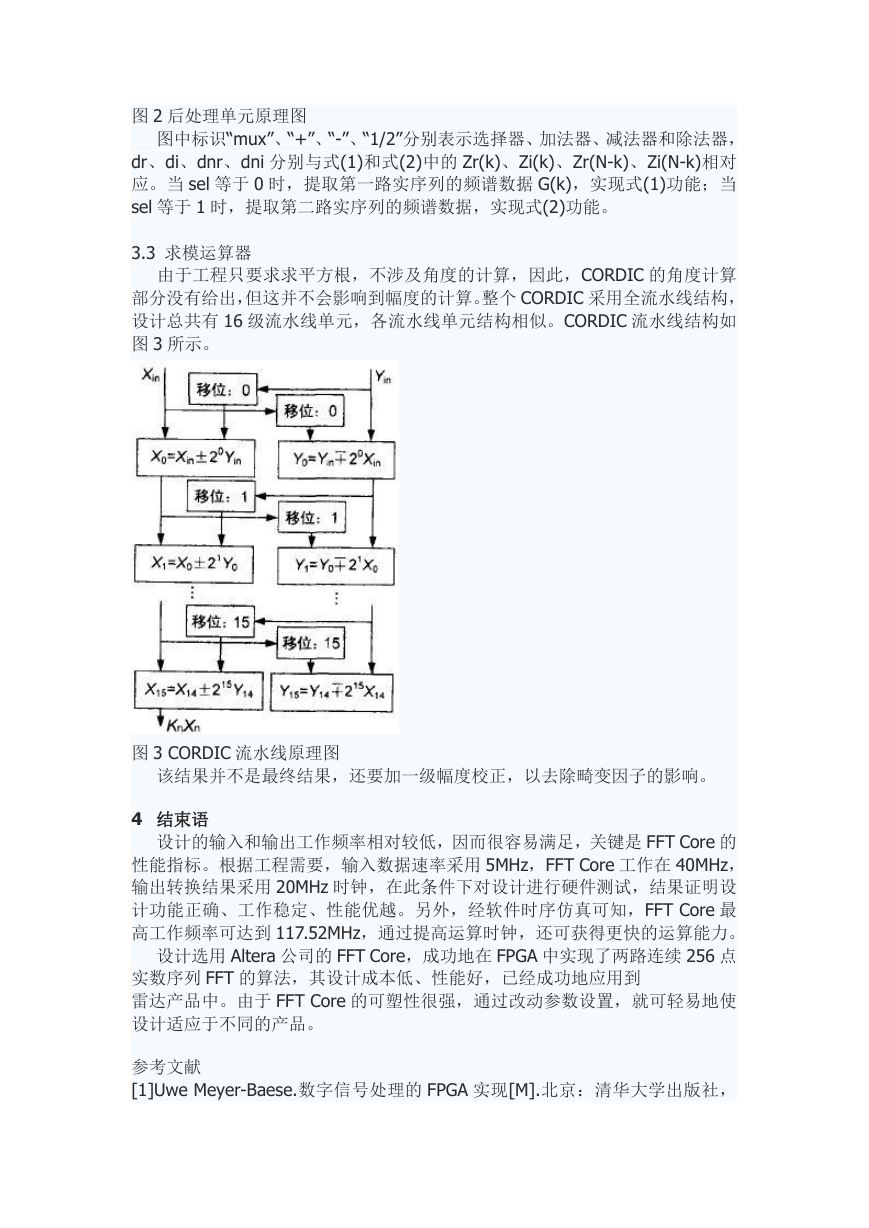

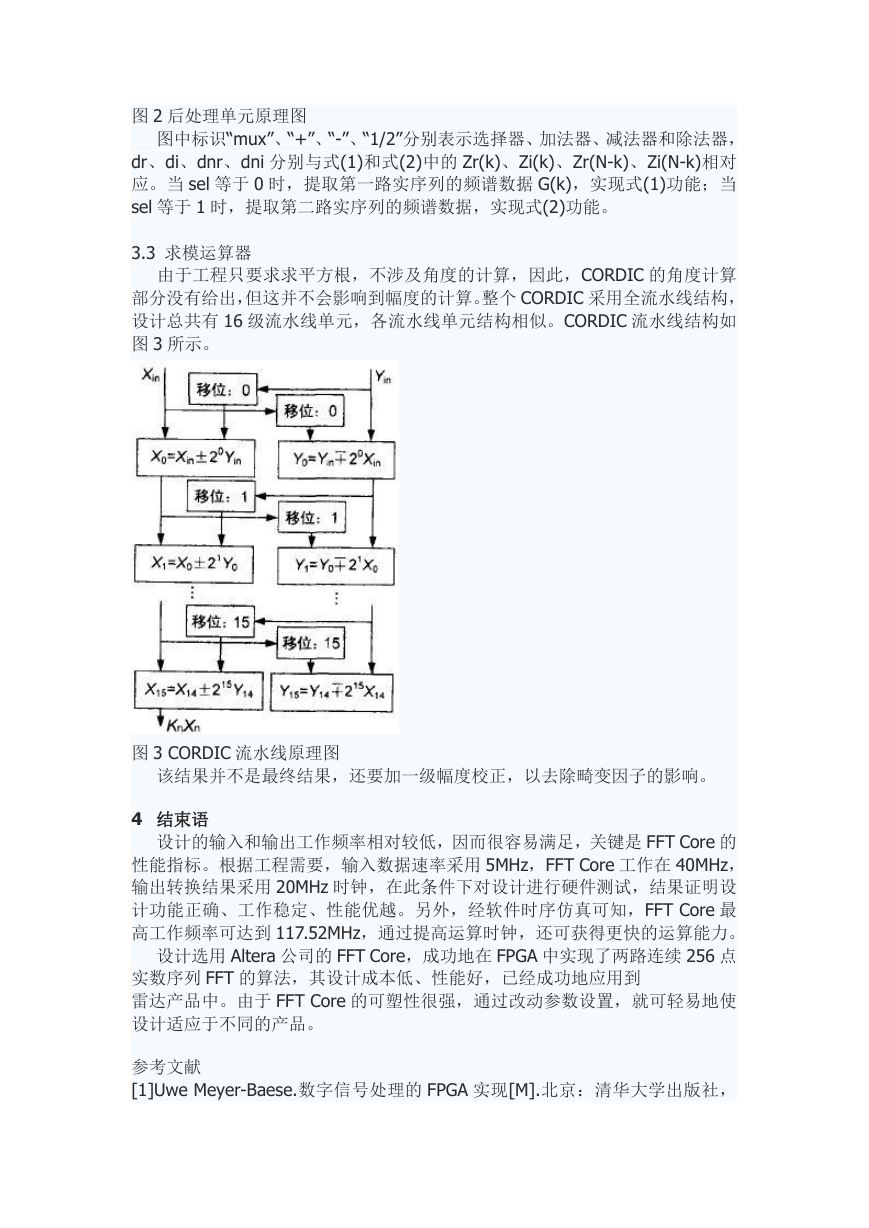

3.3 求模运算器

由于工程只要求求平方根,不涉及角度的计算,因此,CORDIC 的角度计算

部分没有给出,但这并不会影响到幅度的计算。整个 CORDIC 采用全流水线结构,

设计总共有 16 级流水线单元,各流水线单元结构相似。CORDIC 流水线结构如

图 3 所示。

图 3 CORDIC 流水线原理图

该结果并不是最终结果,还要加一级幅度校正,以去除畸变因子的影响。

4 结束语

设计的输入和输出工作频率相对较低,因而很容易满足,关键是 FFT Core 的

性能指标。根据工程需要,输入数据速率采用 5MHz,FFT Core 工作在 40MHz,

输出转换结果采用 20MHz 时钟,在此条件下对设计进行硬件测试,结果证明设

计功能正确、工作稳定、性能优越。另外,经软件时序仿真可知,FFT Core 最

高工作频率可达到 117.52MHz,通过提高运算时钟,还可获得更快的运算能力。

设计选用 Altera 公司的 FFT Core,成功地在 FPGA 中实现了两路连续 256 点

实数序列 FFT 的算法,其设计成本低、性能好,已经成功地应用到

雷达产品中。由于 FFT Core 的可塑性很强,通过改动参数设置,就可轻易地使

设计适应于不同的产品。

参考文献

[1]Uwe Meyer-Baese.数字信号处理的 FPGA 实现[M].北京:清华大学出版社,

�

2003.

[2]侯朝焕,阎世尊,蒋银林.实用 FFT 信号处理技术[M].北京:海洋出版社,1990.

[3]谈宜育,卞文兵,李元等.一种基于 CORDIC 算法的 R-θ变换 ASIC[J].微电子

学,2000,30(3):166~167.

[4]李滔,韩月秋.基于流水线 CORDIC 算法的三角函数发生器.系统工程与电子技

术[J],2000,22(4):85-87.

西安电子科技大学通信工程学院 罗雪苟 詹阳

引言

DFT(Discrete Fourier Transformation)是数字信号分析与处理如图形、语音及图像等领域

的重要变换工具,直

接计算 DFT 的计算量与变换区间长度 N 的平方成正比。当 N 较大时,因计算量太大,直接

用 DFT 算法进行谱分析和信号的实时处理是不切实际的。快速傅立叶变换(Fast Fourier

Transformation,简称 FFT)使 DFT 运算效率提高 1~2 个数量级。其原因是当 N 较大时,对

DFT 进行了基 4 和基 2 分解运算。FFT 算法除了必需的数据存储器 ram 和旋转因子 rom 外,

仍需较复杂的运算和控制电路单元,即使现在,实现长点数的 FFT 仍然是很困难。本文提出

的 FFT 实现算法是基于 FPGA 之上的,算法完成对一个序列的 FFT 计算,完全由脉冲触发,

外部只输入一脉冲头和输入数据,便可以得到该脉冲头作为起始标志的 N 点 FFT 输出结果。

由于使用了双 ram,该算法是流型(Pipelined)的,可以连续计算 N 点复数输入 FFT,即输入

可以是分段 N 点连续复数数据流。采用 DIF(Decimation In Frequency)-FFT 和 DIT(Decimation

In Time)-FFT 对于算法本身来说是无关紧要的,因为两种情况下只是存储器的读写地址有所

变动而已,不影响算法的结构和流程,也不会对算法复杂度有何影响。算法实现的可以是基

2/4 混合基 FFT,也可以是纯基 4FFT 和纯基 2FFT 运算。

傅立叶变换和逆变换

对于变换长度为 N 的序列 x(n)其傅立叶变换可以表示如下:

N

nk

X(k)=DFT[x(n)]= Σ x(n)W

n=0

式(1)

�

其中,W=exp(-2π/N)。

当点数 N 较大时,必须对式(1)进行基 4/基 2 分解,以短点数实现长点数的变换。而 IDFT

的实现在 DFT 的基础上就显得较为简单了:

式(2)

由式(2)可以看出,在 FFT 运算模块的基础上,只需将输入序列进行取共轭后再

进行 FFT 运算,输出结果再取一次共轭便实现了对输入序列的 IDFT 运算,因子

1/N 对于不同的数据表示格式具体实现时的处理方式是不一样的。IDFT 在 FFT

的基础上输入和输出均有一次共轭操作,但它们共用一个内核,仍然是十分方便

的。

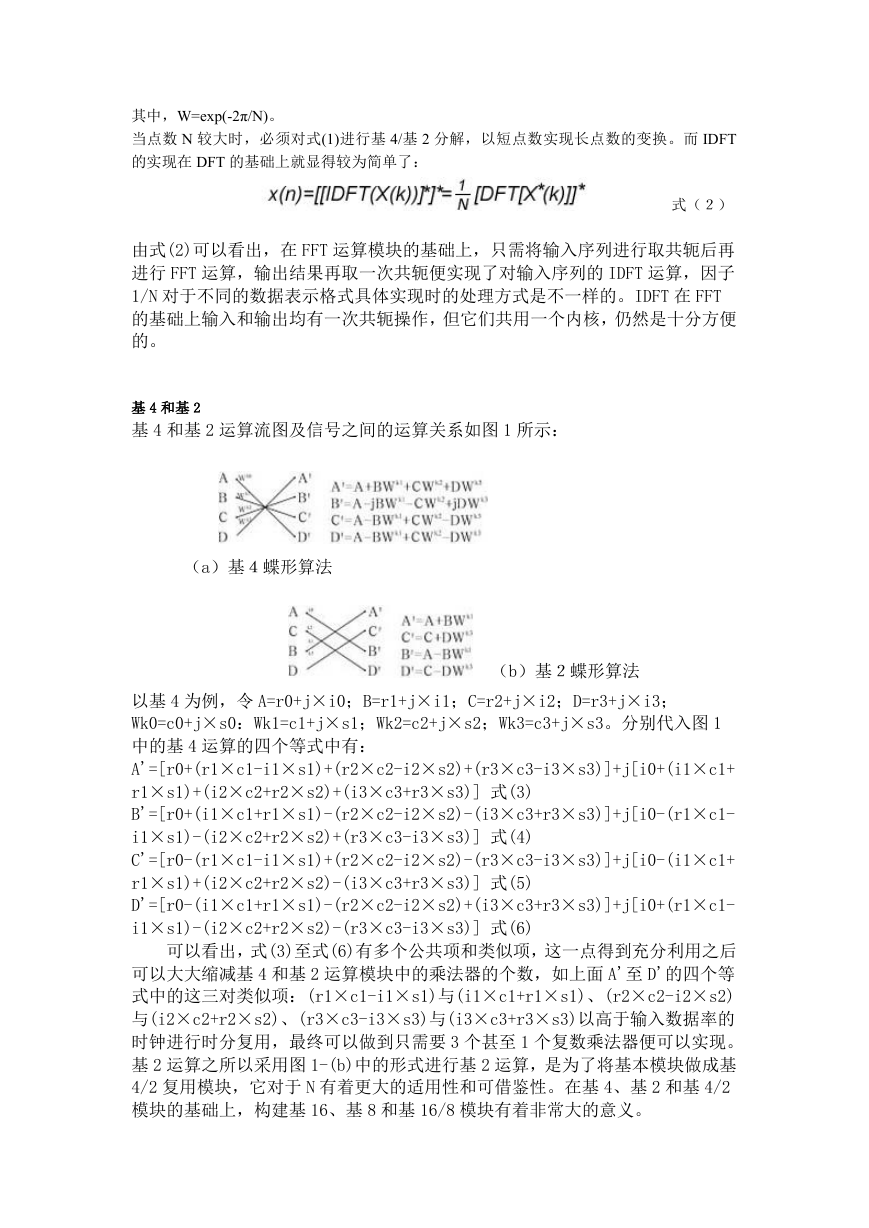

基 4 和基 2

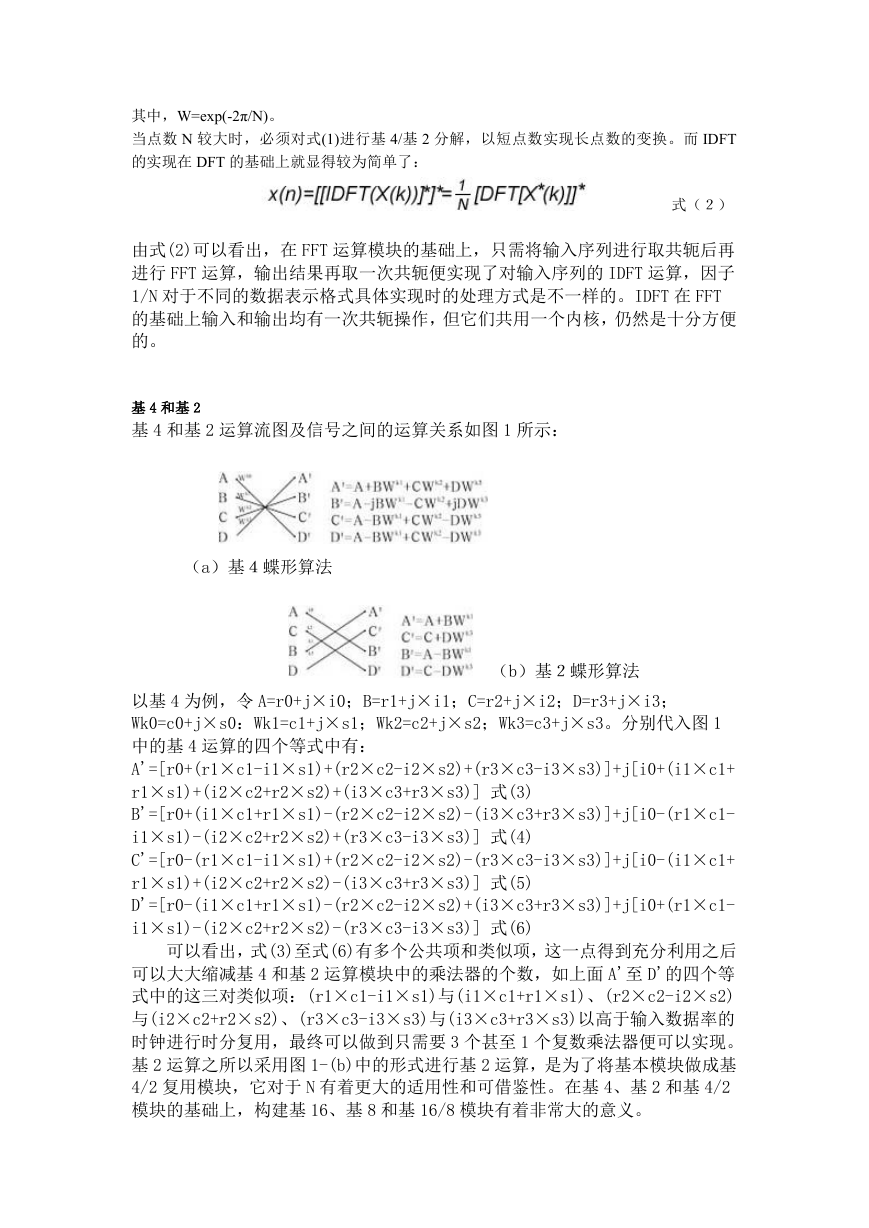

基 4 和基 2 运算流图及信号之间的运算关系如图 1 所示:

(a)基4蝶形算法

(b)基2蝶形算法

以基 4 为例,令 A=r0+j×i0;B=r1+j×i1;C=r2+j×i2;D=r3+j×i3;

Wk0=c0+j×s0:Wk1=c1+j×s1;Wk2=c2+j×s2;Wk3=c3+j×s3。分别代入图 1

中的基 4 运算的四个等式中有:

A'=[r0+(r1×c1-i1×s1)+(r2×c2-i2×s2)+(r3×c3-i3×s3)]+j[i0+(i1×c1+

r1×s1)+(i2×c2+r2×s2)+(i3×c3+r3×s3)] 式(3)

B'=[r0+(i1×c1+r1×s1)-(r2×c2-i2×s2)-(i3×c3+r3×s3)]+j[i0-(r1×c1-

i1×s1)-(i2×c2+r2×s2)+(r3×c3-i3×s3)] 式(4)

C'=[r0-(r1×c1-i1×s1)+(r2×c2-i2×s2)-(r3×c3-i3×s3)]+j[i0-(i1×c1+

r1×s1)+(i2×c2+r2×s2)-(i3×c3+r3×s3)] 式(5)

D'=[r0-(i1×c1+r1×s1)-(r2×c2-i2×s2)+(i3×c3+r3×s3)]+j[i0+(r1×c1-

i1×s1)-(i2×c2+r2×s2)-(r3×c3-i3×s3)] 式(6)

可以看出,式(3)至式(6)有多个公共项和类似项,这一点得到充分利用之后

可以大大缩减基 4 和基 2 运算模块中的乘法器的个数,如上面 A'至 D'的四个等

式中的这三对类似项:(r1×c1-i1×s1)与(i1×c1+r1×s1)、(r2×c2-i2×s2)

与(i2×c2+r2×s2)、(r3×c3-i3×s3)与(i3×c3+r3×s3)以高于输入数据率的

时钟进行时分复用,最终可以做到只需要 3 个甚至 1 个复数乘法器便可以实现。

基 2 运算之所以采用图 1-(b)中的形式进行基 2 运算,是为了将基本模块做成基

4/2 复用模块,它对于 N 有着更大的适用性和可借鉴性。在基 4、基 2 和基 4/2

模块的基础上,构建基 16、基 8 和基 16/8 模块有着非常大的意义。

�

算法实现

傅立叶变换实现时首先进行基 2、基 4 分解,一般来说,如果算法使用基 4

实现,虽然使用的资源多了一些,但速度上的好处足以弥补。如果资源充足,使

用基 16、基 8 或基 16/8 复用模块,速度可以大大提高。一般 FFT 实现简单框图

如图 2 所示。

在图 2 中,运算模块即为基 2/4/8/16 模块或它们的复用模块,Rom 表中存

储的是 N 点旋转因子表。控制模块产生所有的控制信号,存储器 1 和 2 的读写地

址、写使能、运算模块的启动信号及因子表的读地址等信号。当然对于运算模块

为基 16/8 复用模块时,控制模块就需要产生模式选择信号,如对于运算模块是

基 4/2 模块时,该信号就决定了内部运算模块是进行基 4 运算还是基 2 运算。存

储器 1 作为当前输入标志对应输入 N 点数据的缓冲器,存储器 2 作为中间结果存

储器,用于存储运算模块计算出的各 Pass 的结果。在图中的各种地址、使能和

数据的紧密配合下,经过一定延时后输出计算结果及其对应指示标志。图 2 只是

一定点或浮点的 FFT 实现模块,如果是块浮点运算,则必须加入一个数据因子控

制器,控制每遍运算过程中的数据大小,并根据各个 Pass 的乘性因子之和的大

小,对最终输出进行大小控制,以保证每段 FFT 运算输出增益一致。

外部输入为 N 点数据段流和启动信号(N 点之间如无间隔,则每 N 数据点输

入一脉冲信号),一方面,外部数据存入存储器 1 中,同时通过控制模块的控制,

读出存储器 1 中的前段 N 点数据和 Rom 表中的因子及相关控制信号送入运算核心

模块进行各个 Pass 的运算,每个 Pass 的输出都存入存储器 2 中,最后一个 Pass

的计算结果存入存储器 2 中,并在下一个启动头到来后,输出计算结果。对图 2

的实现,除去运算模块,关键是各个 Pass 数据因子读写地址及控制信号的配合。

速度、资源和精度

假定输入数据的速率为 fin,则每数据的持续时间 T=1/fin,运算模块的计

算时钟频率为 fa,对于 N(N=2p,p 即为 Pass 数目)点 FFT 计算时延与 Pass 数目

直接相关。如果使用基 2 运算不考虑控制开销,纯粹的计算时延为

td=p×N×T×fin/fa。显然在 fa>p× fin 时,在 N 点内可完成 FFT 运算。否则

不能完成,即不能实现流型的变换。这在 N 很大且输入数据速率较高时以 FPGA

实现几乎是不可能的,而且内部计算时钟过高容易导致电路的工作不稳定。设基

2 时的最小可流型工作运算频率为 fa0,则使用基 4 实现流型的变换,计算时钟

fa= fa0 就可以。而使用基 8 时计算时钟 fa= fa0 便可完成,基 16 时为 fa0 的

1/4。上面所讨论的是纯基运算,当 N 不为 4 的幂次方时(如 N=2048=16×16×8,

运算模块为基 16/8 复用模块),而又希望使用较低倍的时钟完成运算时,图 2

中的运算模块必然包括基 4/2 复用模块(即基 16/8 复用模块),这也就是前面提

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc