研 究 生 课 程 论 文

课程名称 基于 FPGA 的任意数值分频器设计

授课学期 2012 学年至 2013 学年

第

二

学期

学

专

学

姓

院

业

号

名

电子工程学院

电子与通信工程

2011011583

郭飞

任 课 教 师

交 稿 日 期

成

绩

阅读教师签名

日

期

摘要

�

在复杂的数字逻辑电路中,经常会用到不同的时钟信号。本文主要介绍了在

QuartusII 开发软件下得用 Verilog 硬件描述语言来设计分频器。在进行分频器设

计时,采用的是一种逐层深入的设计理念,由易到难、由浅入深。可实现 2-256 之间

的任意奇数、偶数、半整数分频。此外,本文还介绍了 Altera 公司的 EP1K100QC208-3

型 FPGA,使得分频器的设计显得更加实际化,从而也体现了一种实践求真知的求学

理念。

关键词: Verilog HDL; FPGA;数字逻辑电路设计; VHDL

Abstract

�

logic circuit,

In the complex numeral

the different clock signal can be used

frequently. This article mainly introduced under the QuartusII development software to

descript the frequency divider with the Verilog hardware description language. When

carries on the frequency divider designs, used one kind of design idea with the level

thorough, from the simple to the difficult , from the shallow to the deep. May realize

2-256 between free odd number, the even number, the half Integer frequency division. In

addition, this article also introduced Altera Corporation's EP1K100QC208-3 FPGA, it

causes the frequency divider’s design more actually, thus also manifested one practice

to ask the true knowledge to study idea.

Keywords: Verilog HDL ; FPGA; Numeral logic circuit design ;VHDL

引言

�

计算机技术和微电子工艺的发展,使得现代数字系统的设计和应用进入了新的

阶段。电子设计自动化(EDA)技术在数字系统设计中起的作用越来越重要,新的工

具的设计方法不断推出,可编程逻辑器件不断增加新的模块,工能越来越强,硬件

设计语言也顺应形势,推出新的标准,更加好用,更加便捷[1]。

本文主要以 FPGA 和 Verilog HDL 硬件描述语言对分频器的设计为主线。

QuartusII 软年工具也在设计中发挥了重要作用,它为分频器的设计提代了平

台和工具,它将设计者的设计思想自动、高效地转化为物理电路或网表结构,并以

直观、便捷的形式提供了仿真模拟手段[2]。

本文共 5 部分,第 1 部分对 EDA 技术及其发展趋势进行综述,并着重介绍了 FPGA

器件。第 2 部分介绍的是偶数分频器的原理及设计方法。第 3 部分是对第 2 部分的

延深与扩充,它主要介绍的是奇数分频。第四部分介绍的是小数分频。第 5 部分针

对 Altera 公司的 EP1K100QC208-3 型 FPGA 在 QuartusII 中的应用进行了介绍。

分频器的设计与 EDA 技术是不断发展变化的,要掌握分频器设计和 EDA 技术的

精髓,需要设计者在不断实践的过程中不懈的摸索和积累,逐步提高自己的设计水

平。本文在设计中有不少的缺限,希望诗刊给予批评指正。

1 FPGA 与硬件描述语言简介

数字系统的设计和实现离不开 CPLD/FPGA 器件,因为很多数字系统是基于

CPLD/FPGA 器件实现的,本文的设计实现基于 Altera 公司的 EP1K100QC208-3, 该芯

片属于 ACEX 1K 系列。

ACEX 1K 系列器件是 Altera 公司近期推出的新型 CPLD 产品。该器件基于

SRAM,结合查找表(LUT)和嵌入式阵列块(EAB)提供了高密度结构,可提供 10000

到 100000 可用门,每个嵌入式阵列块增加到 16 位宽可实现双端口,RAM 位增加到

49125 个。其多电压引脚可以驱动 2.5V、3.3V、5.0V 器件,也可以被这些电压所

驱动;双向 I/O 引脚执行速度可达 250MHz。该器件还应用 Altera 专利技术进行了

重要的生产改进,进一步降低了器件的成本,提高了产品的性能价格比。因此,ACEX

1K 器件可用来实现许多逻辑复杂、信息量大的系统。但是在器件操作过程中,ACEX

1K 系列器件的配置数据存储在 SRAM 单元中,由于 SRAM 的易失性,配置数据在每

�

次上电时必须被重新载入 SRAM[3]。

在数字系统设计中,一个明显的特征就是越来越多的采用硬件描述语言来进行

设计。硬件描述语言 HDL 是一种用形式化方法描述数字电路和系统的语言。利用这

种语言,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的

设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设

计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,

经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路 ASIC 或现场可

编程门阵列 FPGA 自动布局布线工具,把网表转换为要实现的具体电路布线结构[4]。

目前,硬件描述语言可谓是百花齐放,有 VHDL、Superlog、Verilog、SystemC、

Cynlib C++、C Level 等等。虽然各种语言各有所长,但业界对到底使用哪一种语

言进行设计,却莫衷一是,难有定论。本文选用 Verilog HDL 语言进行分频器描述。

Verilog HDL 语言是在 C 语言的基础上发展而来的硬件描述语言,具有简捷、高效、

易学、功能强的特点,拥有广泛的应用群体[5]。

2 偶数分频器的设计

2.1 分频器的基本原理

在数字电路的设计中,分频器是一种应用十分广泛的基本电路,它的具体操作

功能就是对较高的信号进行分频操作,目的是为了得到所需的较低频率的信号。

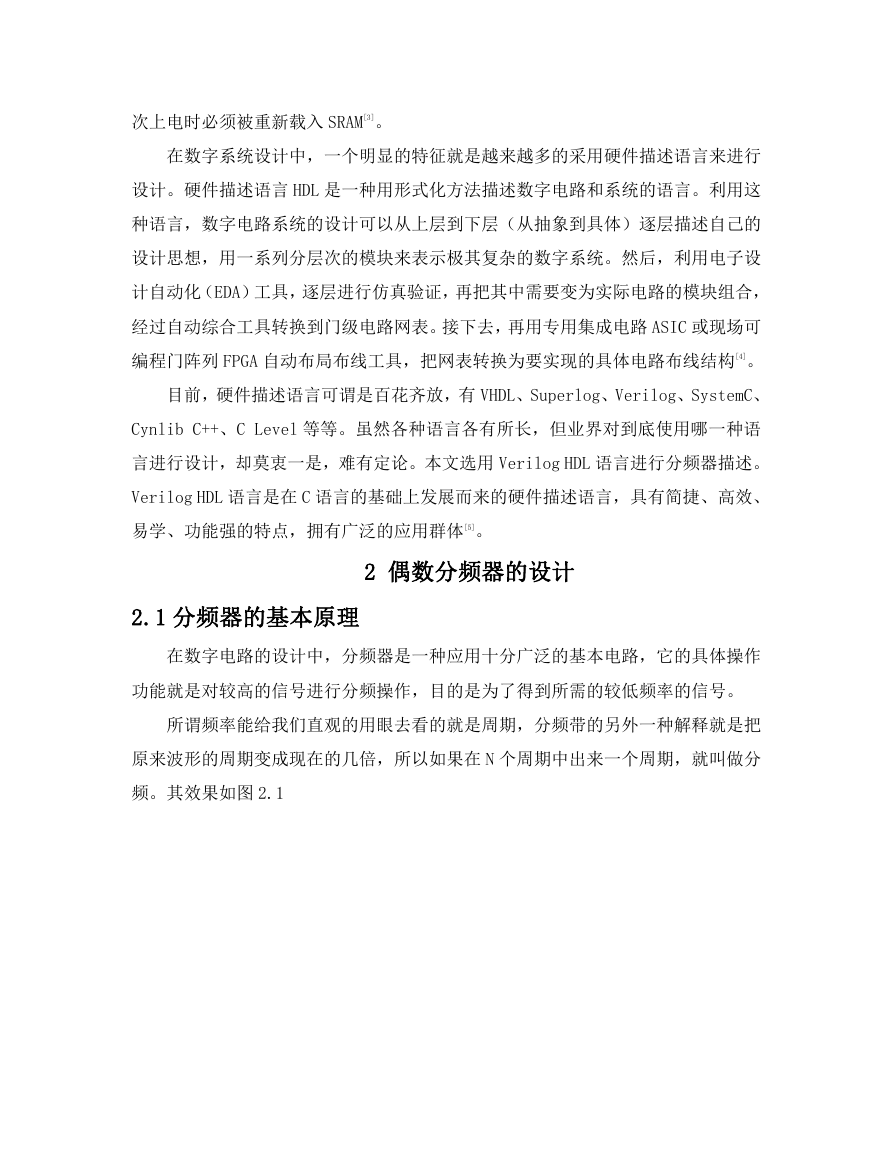

所谓频率能给我们直观的用眼去看的就是周期,分频带的另外一种解释就是把

原来波形的周期变成现在的几倍,所以如果在 N 个周期中出来一个周期,就叫做分

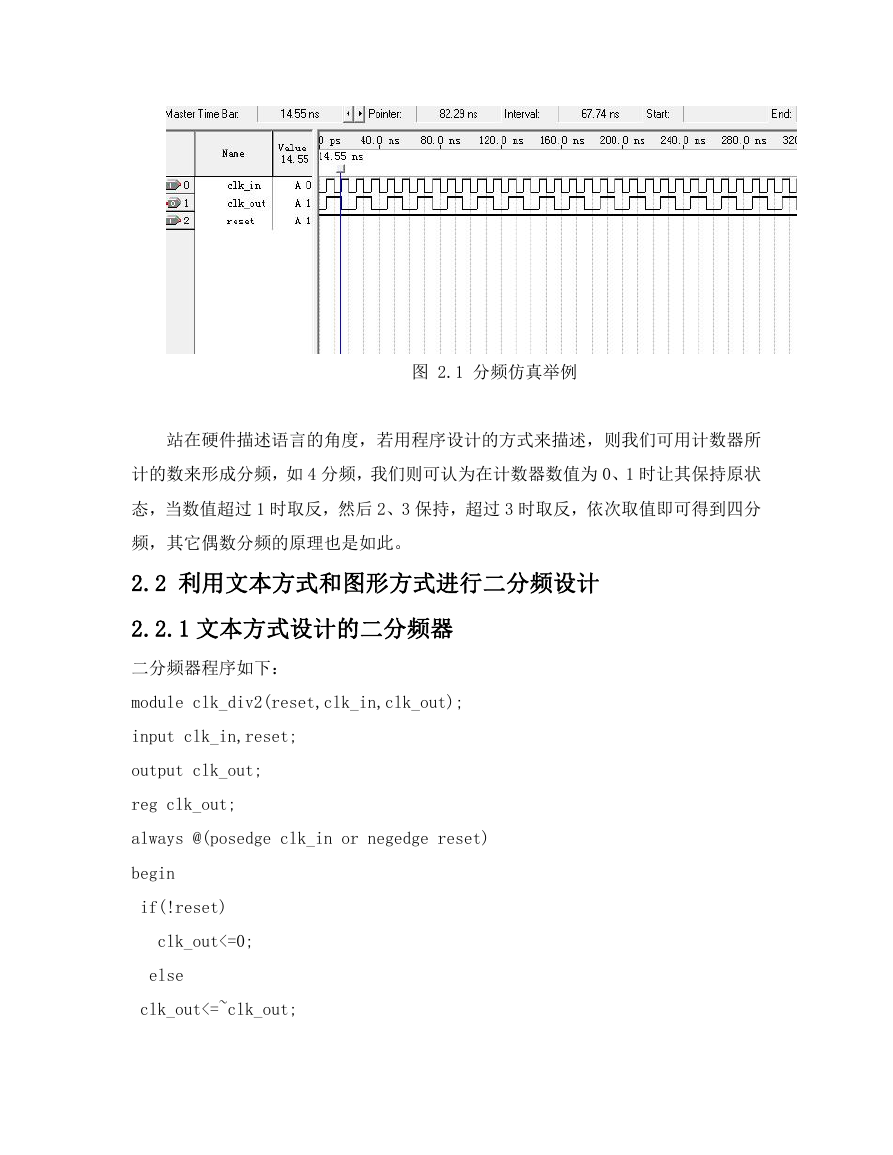

频。其效果如图 2.1

�

图 2.1 分频仿真举例

站在硬件描述语言的角度,若用程序设计的方式来描述,则我们可用计数器所

计的数来形成分频,如 4 分频,我们则可认为在计数器数值为 0、1 时让其保持原状

态,当数值超过 1 时取反,然后 2、3 保持,超过 3 时取反,依次取值即可得到四分

频,其它偶数分频的原理也是如此。

2.2 利用文本方式和图形方式进行二分频设计

2.2.1 文本方式设计的二分频器

二分频器程序如下:

module clk_div2(reset,clk_in,clk_out);

input clk_in,reset;

output clk_out;

reg clk_out;

always @(posedge clk_in or negedge reset)

begin

if(!reset)

clk_out<=0;

else

clk_out<=~clk_out;

�

end

endmodule

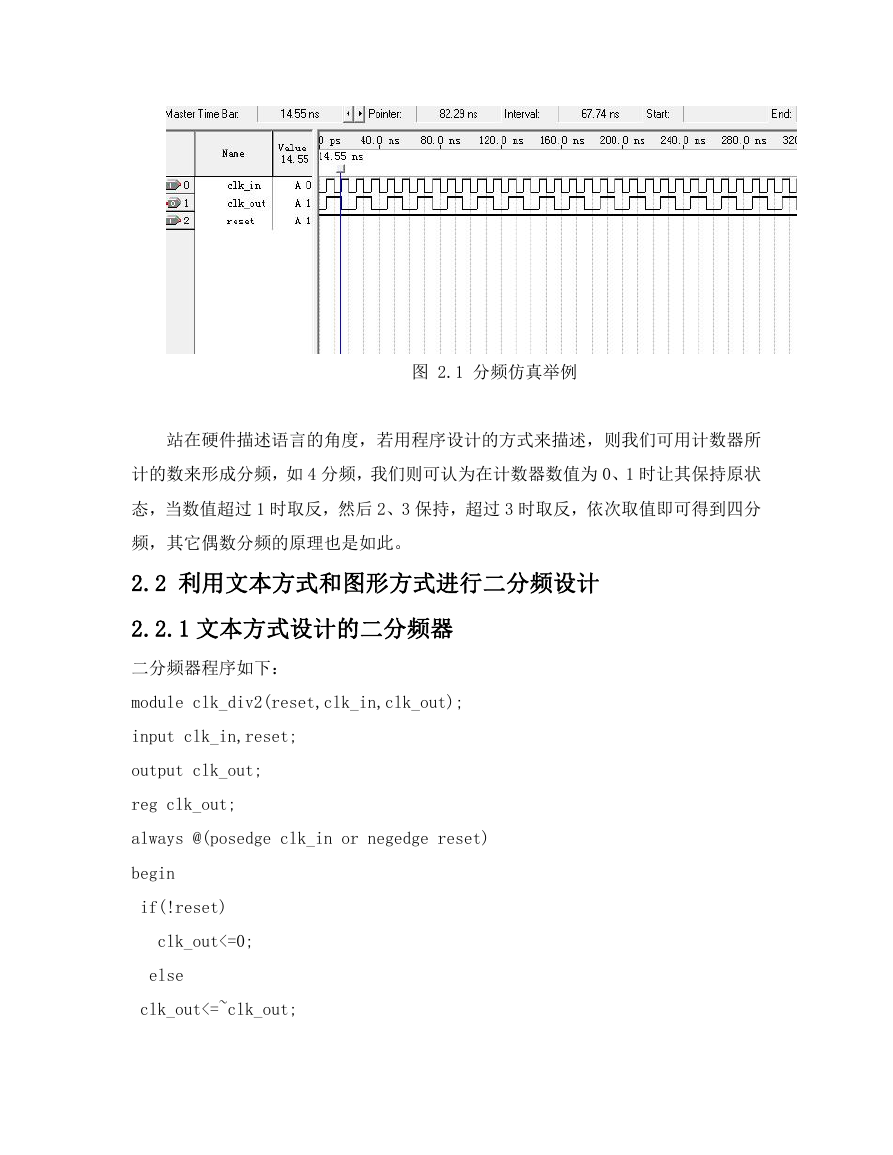

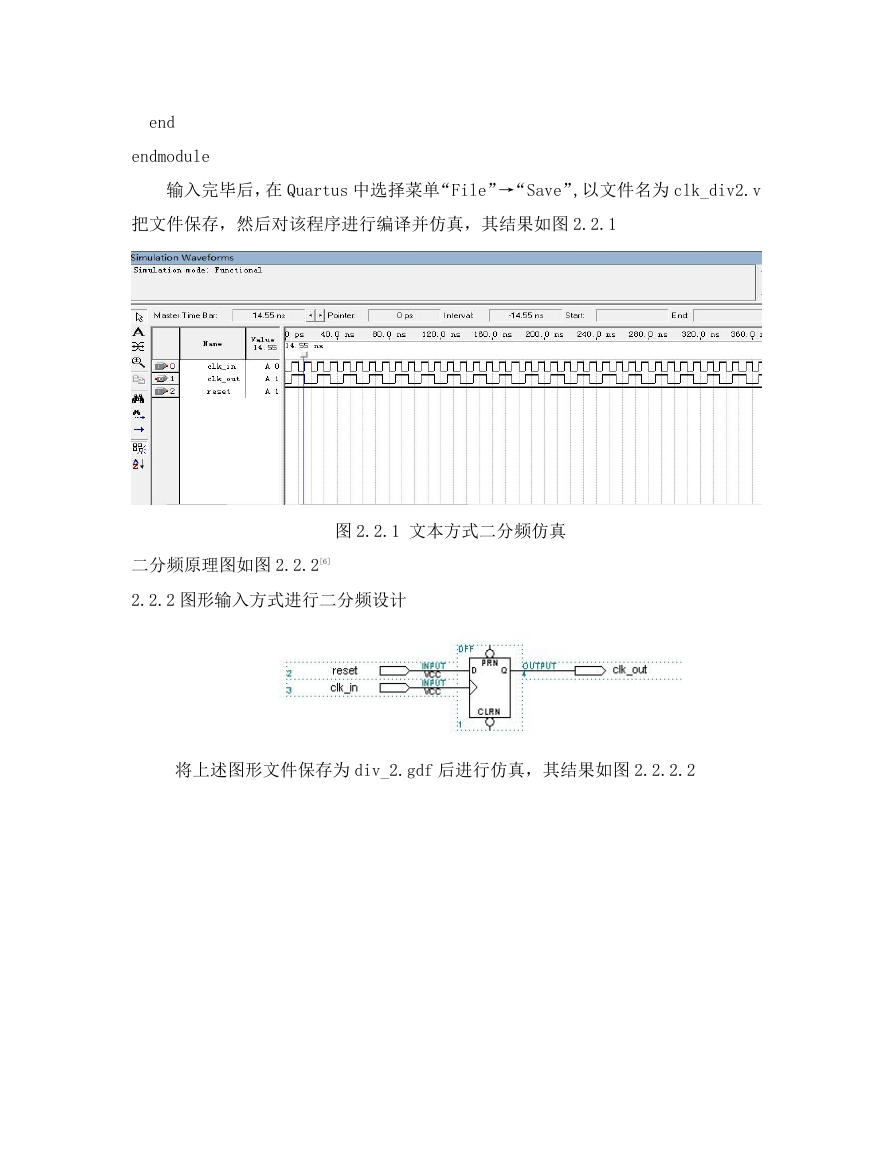

输入完毕后,在 Quartus 中选择菜单“File”→“Save”,以文件名为 clk_div2.v

把文件保存,然后对该程序进行编译并仿真,其结果如图 2.2.1

图 2.2.1 文本方式二分频仿真

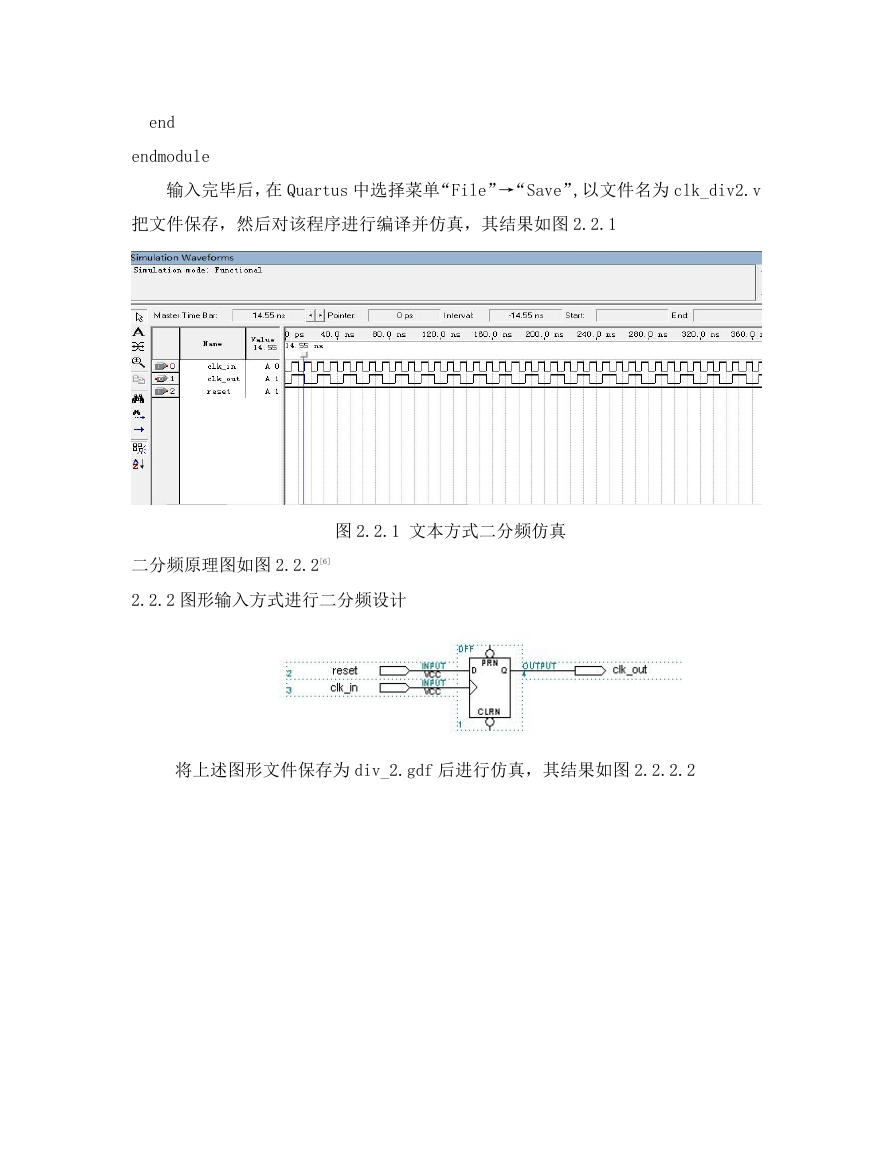

二分频原理图如图 2.2.2[6]

2.2.2 图形输入方式进行二分频设计

图 2.2.2.1 二分频原理图

将上述图形文件保存为 div_2.gdf 后进行仿真,其结果如图 2.2.2.2

�

图 2.2.2.2 图形方式二分频仿真

2.3 十二分频器的设计

为了使大家能更好的理解偶数分频器的设计,下面将以十二分频器设计为例进

行偶数分频器设计的扩展

十二分频器程序:

module clk_div12(reset,clkin,clkout,qout);

input reset,clkin;

output clkout,qout;

reg clkout;

reg[4:0] qout;

always @(posedge clkin)

begin

if(!reset) qout<=0;

else if(qout<11) qout<=qout+1;

else qout<=0;

end

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc