文档中心

文档编号

资源类别: HDL语言

版本

1.0

密级

内部公开

共41页

Verilog HDL入门教程

(仅供内部使用)

拟制:

批准:

批准:

中研基础

日期:

2004.8.3

中研基础

日期:

日期:

yyyy/mm/dd

版权所有 不得复制

�

Verilog HDL 入门教程

绝密

请输入文档编号

修订记录

日期

2004.8.3

修订版本

1.00

描述

初稿完成

作者

2004-08-16

第2页,共41页

版权所有,侵权必究

�

Verilog HDL 入门教程

绝密

请输入文档编号

目 录

1 前言 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 HDL设计方法学简介 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 数字电路设计方法 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 硬件描述语言 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 设计方法学 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Verilog HDL简介 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 历史 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.2 能力 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Verilog HDL 建模概述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 模块 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 简单事例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 模块的结构 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3 模块语法 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 时延 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 三种建模方式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 结构化描述方式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 数据流描述方式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 行为描述方式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 混合设计描述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Verilog HDL 基本语法 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 标识符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 定义 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 关键词 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.3 书写规范建议 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 注释 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 格式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 数字值集合 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 值集合 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 常量 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 数据类型 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 线网类型 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 寄存器类型

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 运算符和表达式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1 算术运算符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.2 关系运算符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.3 逻辑运算符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.4 按位逻辑运算符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.5 条件运算符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.6 连接运算符 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 条件语句 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 case 语句 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 结构建模 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

5

5

6

6

7

7

7

9

9

9

10

11

11

12

12

14

15

16

17

17

17

17

17

17

18

18

18

18

20

20

20

21

21

22

23

24

25

25

25

27

28

2004-08-16

第3页,共41页

版权所有,侵权必究

�

Verilog HDL 入门教程

绝密

请输入文档编号

5.1 模块定义结构 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 模块端口 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 实例化语句 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 结构化建模具体实例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 数据流建模 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 连续赋值语句 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 阻塞赋值语句 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 数据流建模具体实例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 行为建模 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 简介 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 顺序语句块 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 过程赋值语句 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 行为建模具体实例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 其他方面 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9 习题 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 附录A Verilog 保留字 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

28

28

29

31

34

34

34

34

35

35

35

36

37

39

39

40

2004-08-16

第4页,共41页

版权所有,侵权必究

�

Verilog HDL 入门教程

Verilog HDL 入门教程

绝密

请输入文档编号

关键词:

摘 要:本文主要介绍了Verilog HDL 语言的一些基本知识,目的是使初学者能够迅速掌握HDL

设计方法,初步了解并掌握Verilog HDL语言的基本要素,能够读懂简单的设计代码并能

够进行一些简单设计的Verilog HDL建模。

缩略语清单: 对本文所用缩略语进行说明,要求提供每个缩略语的英文全名和中文解释。

参考资料清单: 请在表格中罗列本文档所引用的有关参考文献名称、作者、标题、编号、发布日

期和出版单位等基本信息。

名称

作者

编号

发布日期

查阅地点或渠

参考资料清单

出版单位(若

不为本公司发

布的文献,请

填写此列)

道

苏文彪

2000.7

图书馆

机 械 工 业 出 版

社

Quisck

Reference

Verilog HDL

AMBIT Design

System

for

Verilog HDL 硬

件描述语言

J.Bhasker 著

徐振林 等译

1 前言

当前业界的硬件描述语言中主要有VHDL 和Verilog HDL。公司根据本身ASIC设计现有的特

点、现状,主推Verilog HDL 语言,逐渐淡化VHDL语言,从而统一公司的ASIC/FPGA设计平台,

简化流程。

为使新员工在上岗培训中能迅速掌握ASIC/FPGA 设计的基本技能,中研基础部ASIC设计中心

开发了一系列的培训教材。该套HDL语言培训系列包括如下教程:

《Verilog HDL 入门教程》

《Verilog HDL 代码书写规范》

《Verilog 基本电路设计指导书》

《TestBench 编码技术》

系列教材完成得较匆忙,本身尚有许多不完善的地方,同时,可能还需要其他知识方面的培

训但没有形成培训教材,希望大家在培训过程中,多提宝贵意见,以便我们对它进行修改和完

善。

2 HDL设计方法学简介

2004-08-16

第5页,共41页

版权所有,侵权必究

�

Verilog HDL 入门教程

2.1 数字电路设计方法

绝密

请输入文档编号

当前的数字电路设计从层次上分可分成以下几个层次:

1. 算法级设计:利用高级语言如C语言及其他一些系统分析工具(如MATLAB)对设计从系统

的算法级方式进行描述。算法级不需要包含时序信息。

2. RTL级设计:用数据流在寄存器间传输的模式来对设计进行描述。

3. 门级:用逻辑级的与、或、非门等门级之间的连接对设计进行描述。

4. 开关级:用晶体管和寄存器及他们之间的连线关系来对设计进行描述。

算法级是高级的建模,一般对特大型设计或有较复杂的算法时使用,特别是通讯方面的一些

系统,通过算法级的建模来保证设计的系统性能。在算法级通过后,再把算法级用RTL级进行描

述。门级一般对小型设计可适合。开关级一般是在版图级进行。

2.2 硬件描述语言

在传统的设计方法中,当设计工程师设计一个新的硬件、一个新的数字电路或一个数字逻辑

系统时,他或许在CAE 工作站上做设计,为了能在CAE工作站做设计,设计者必须为设计画一张

线路图,通常地,线路图是由表示信号的线和表示基本设计单元的符号连在一起组成线路图,符

号取自设计者用于构造线路图的零件库。若设计者是用标准逻辑器件(如74系列等)做板极设计

线路图,那么在线路图中,符号取自标准逻辑零件符号库;若设计是进行ASIC设计,则这些符号

取自ASIC库的可用的专用宏单元。这就是传统的原理图设计方法。

对线路图的逻辑优化,设计者或许利用一些EDA工具或者人工地进行逻辑的布尔函数逻辑优

化。为了能够对设计进行验证,设计者必须通过搭个硬件平台(如电路板),对设计进行验证。

随着电子设计技术的飞速发展,设计的集成度、复杂度越来越高,传统的设计方法已满足不

了设计的要求,因此要求能够借助当今先进的EDA工具,使用一种描述语言,对数字电路和数字

逻辑系统能够进行形式化的描述,这就是硬件描述语言。

硬件描述语言HDL(Hardware Description Language )是一种用形式化方法来描述数字电路和

数字逻辑系统的语言。数字逻辑电路设计者可利用这种语言来描述自己的设计思想,然后利用

EDA工具进行仿真,再自动综合到门级电路,最后用ASIC或FPGA实现其功能。举个例子,在传统

的设计方法中,对2输入的与门,我们可能需到标准器件库中调个74系列的器件出来,但在硬件描

述语言中,“& ”就是一个与门的形式描述,“C = A & B”就是一个2输入与门的描述。而“and

”就是一个与门器件。

硬件描述语言发展至今已有二十多年历史,当今业界的标准中(IEEE标准)主要有VHDL和

Verilog HDL 这两种硬件描述语言。

2.3 设计方法学

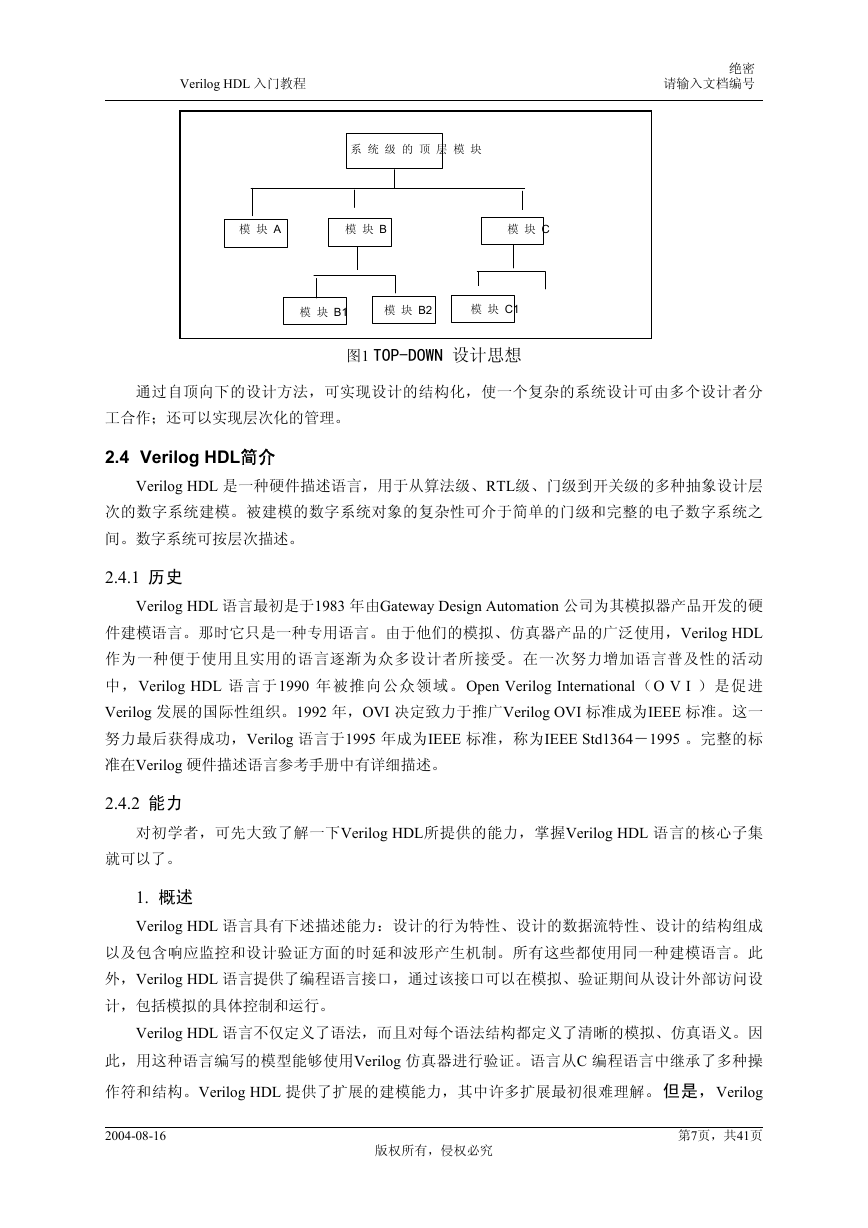

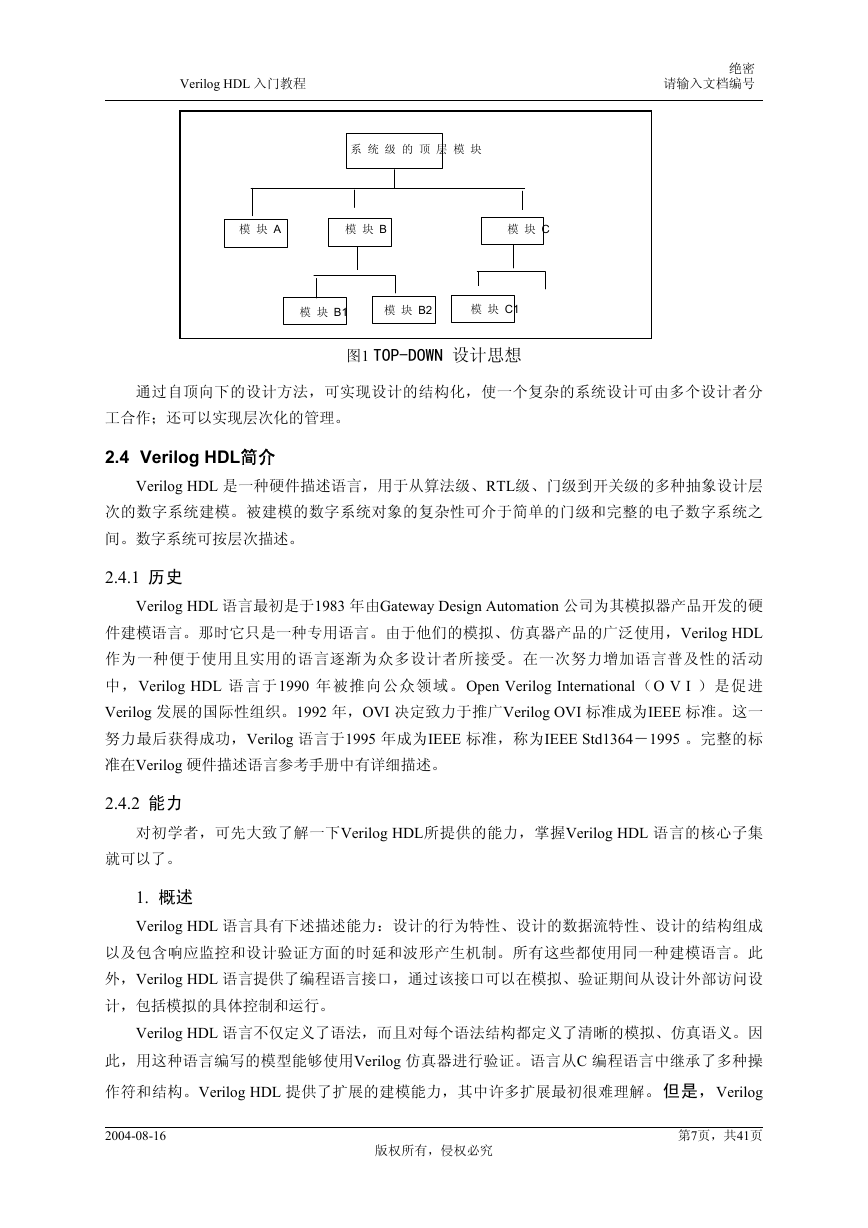

当前的ASIC设计有多种设计方法,但一般地采用自顶向下的设计方法。

随着技术的发展,一个芯片上往往集成了几十万到几百万个器件,传统的自底向上的设计方

法已不太现实。因此,一个设计往往从系统级设计开始,把系统划分成几个大的基本的功能模

块,每个功能模块再按一定的规则分成下一个层次的基本单元,如此一直划分下去。自顶向下的

设计方法可用下面的树状结构表示:

2004-08-16

第6页,共41页

版权所有,侵权必究

�

Verilog HDL 入门教程

绝密

请输入文档编号

系 统 级 的 顶 层 模 块

模 块 A

模 块 B

模 块 C

模 块 B1

模 块 B2

模 块 C1

图1 TOP-DOWN 设计思想

通过自顶向下的设计方法,可实现设计的结构化,使一个复杂的系统设计可由多个设计者分

工合作;还可以实现层次化的管理。

2.4 Verilog HDL简介

Verilog HDL 是一种硬件描述语言,用于从算法级、RTL级、门级到开关级的多种抽象设计层

次的数字系统建模。被建模的数字系统对象的复杂性可介于简单的门级和完整的电子数字系统之

间。数字系统可按层次描述。

2.4.1 历史

Verilog HDL 语言最初是于1983 年由Gateway Design Automation 公司为其模拟器产品开发的硬

件建模语言。那时它只是一种专用语言。由于他们的模拟、仿真器产品的广泛使用,Verilog HDL

作为一种便于使用且实用的语言逐渐为众多设计者所接受。在一次努力增加语言普及性的活动

中,Verilog HDL 语言于1990 年被推向公众领域。Open Verilog International(O V I )是促进

Verilog 发展的国际性组织。1992 年,OVI 决定致力于推广Verilog OVI 标准成为IEEE 标准。这一

努力最后获得成功,Verilog 语言于1995 年成为IEEE 标准,称为IEEE Std1364-1995 。完整的标

准在Verilog 硬件描述语言参考手册中有详细描述。

2.4.2 能力

对初学者,可先大致了解一下Verilog HDL所提供的能力,掌握Verilog HDL 语言的核心子集

就可以了。

1. 概述

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成

以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此

外,Verilog HDL 语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设

计,包括模拟的具体控制和运行。

Verilog HDL 语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因

此,用这种语言编写的模型能够使用Verilog 仿真器进行验证。语言从C 编程语言中继承了多种操

作符和结构。Verilog HDL 提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog

2004-08-16

第7页,共41页

版权所有,侵权必究

�

Verilog HDL 入门教程

绝密

请输入文档编号

HDL 语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件

描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

2. 主要功能list

基本逻辑门,例如and 、or 和nand 等都内置在语言中。

开关级基本结构模型,例如pmos 和nmos 等也被内置在语言中。

可采用三种不同方式或混合方式对设计建模。这些方式包括:行为描述方式—使用过程化

结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描

述建模。

Verilog HDL 中有两类数据类型:线网数据类型和寄存器数据类型。线网类型表示构件间

的物理连线,而寄存器类型表示抽象的数据存储元件。

能够描述层次设计,可使用模块实例结构描述任何层次。

设计的规模可以是任意的;语言不对设计的规模(大小)施加任何限制。

Verilog HDL 不再是某些公司的专有语言而是I E E E 标准。

人和机器都可阅读Verilog 语言,因此它可作为E D A 的工具和设计者之间的交互语言。

设计能够在多个层次上加以描述,从开关级、门级、寄存器传送级(RT L )到算法级。

能够使用内置开关级原语在开关级对设计完整建模。

同一语言可用于生成模拟激励和指定测试的验证约束条件,例如输入值的指定。

Verilog HDL 能够监控模拟验证的执行,即模拟验证执行过程中设计的值能够被监控和显

示。这些值也能够用于与期望值比较,在不匹配的情况下,打印报告消息。

在行为级描述中,Verilog HDL 不仅能够在RT L 级上进行设计描述,而且能够在体系结构

级描述及其算法级行为上进行设计描述。

能够使用门和模块实例化语句在结构级进行结构描述。

对高级编程语言结构,例如条件语句、情况语句和循环语句,语言中都可以使

用。

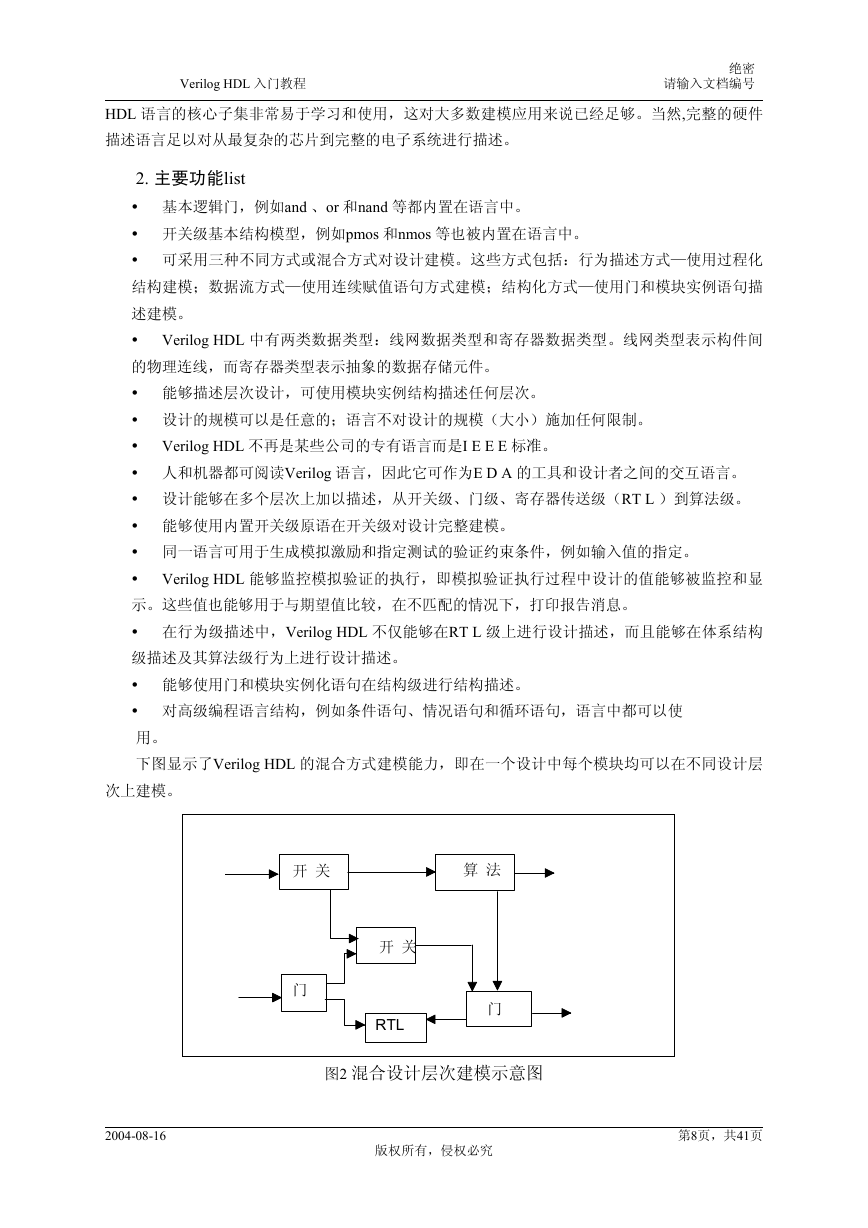

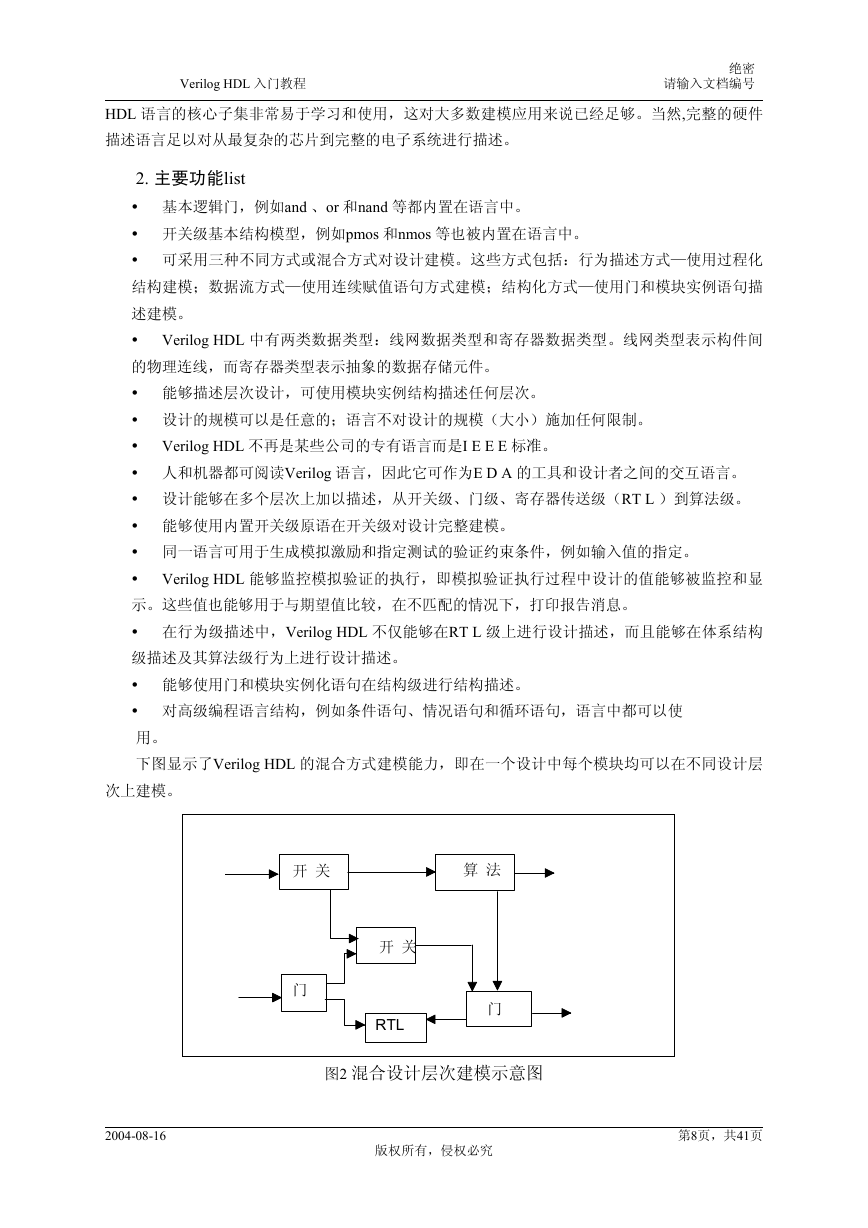

下图显示了Verilog HDL 的混合方式建模能力,即在一个设计中每个模块均可以在不同设计层

次上建模。

开 关

算 法

门

开 关

RTL

门

图2 混合设计层次建模示意图

2004-08-16

第8页,共41页

版权所有,侵权必究

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc