泉 州 师 范 学 院

毕业论文(设计)

题目 基于 FPGA 的电子琴设计

物理与信息工程 学院 电子信息科学与技术 专业 2007 级

学生姓名

吴丽萍

学号

070303051

指导教师

曾永西

职称

讲师

完成日期

2011 年 3 月 30 日

教务处 制

�

基于 FPGA 的电子琴设计

泉州师范学院 电子信息科学与技术专业 070303051 吴丽萍

指导教师 曾永西 讲师

【摘要】介绍了基于 FPGA 的电子琴的工作原理和设计过程。用 Altera 公司的 EP2C8Q208C8N 芯片

为核心器件,通过运用硬件编程语言 VHDL 描述,在 Quartus II 平台上,实现了电子琴的手动弹奏和自

动演奏功能。本系统主要由音频发生模块,键盘控制模块和存储器模块组成。选择手动弹奏模式按键时,

按下音符键后就会选通相应的频率输出;选择自动演奏模式按键时,储存器会将编写好的音乐信息依次取

出,去选通各个对应的频率输出,实现自动演奏。音频发生器由分频器来实现,可产生 16 个频率,这些

频率经放大后驱动喇叭,从而发出声音。

【关键词 】FPGA;Quartus II;VHDL;电子琴; 音符

1

�

目录

第 1 章 引言..................................................................................................................................... .3

1.1 课题分析 .............................................................................................................................. 3

1.2 VHDL 语言和 QUARTUS II 环境简介 ............................................................................. 3

1.2.1 VHDL 简介 ............................................................................................................... 3

1.2.2 Quartus II 简介 ..........................................................................................................3

第 2 章 方案选择及原理分析..........................................................................................................4

2.1 方案比较 ............................................................................................................................. 4

2.2 电子琴设计原理................................................................................................................. 4

2.2.1 分频模块设计方法 ..................................................................................................5

2.2.2 按键模块设计方法...................................................................................................6

2.2.3 顶层模块设计方法...................................................................................................6

2.3 系统设计的主要组成部分 ..................................................................................................6

第 3 章 硬件设计.............................................................................................................................. 6

3.1 现场可编程门阵列 FPGA 简介 ..........................................................................................6

3.2 按键模块及其功能 .............................................................................................................. 7

3.3 显示电路模块及功能 ..........................................................................................................7

第 4 章 软件设计.............................................................................................................................. 7

4.1 系统的流程 .......................................................................................................................... 7

4.2 设计模块 .............................................................................................................................. 7

4.2.1 自动演奏模块........................................................................................................... 9

4.2.2 音阶发生器模块.......................................................................................................9

4.2.3 数控分频模块......................................................................................................... 10

第 5 章 软硬件的系统测试............................................................................................................10

结论.................................................................................................................................................. 10

参考文献.......................................................................................................................................... 11

致谢...................................................................................................................................................11

附录 I 歌谱 ..................................................................................................................................12

附录Ⅱ电路图............................................................................................................................... ...14

附录 III 程序................................................................................................................................ ..14

2

�

第一章 引言

电子琴作为音乐与科技的产物,在电子化和信息化的时代,为音乐的大众化做出了很大

的贡献,歌曲的制作大多数都要由电子琴来完成,然后通过媒介流传开来,电视剧和电影的

插曲、电视节目音效、甚至你的手机铃声,都很可能包含电子琴的身影。

1.1 课题分析

随着电子技术的高速发展,由于 FPGA/CPLD 具有高速、高可靠性、串并行工作方式等

突出优点,所以在电子设计中受到广泛的应用,并且它代表着未来 EDA 设计的方向。

FPGA/CPLD 的设计采用了高级语言,例如 VHDL 语言,AHDL 语言。从而进一步打破了软

硬件之间的界限,加速了产品的开发过程,缩短了设计周期。所以采用 FPGA/CPLD 取代传

统的标准集成电路、接口电路已经成为电子技术发展的必然趋势。

EDA(电子设计自动化) 代表了当今电子设计技术的最新发展方向,它的基本特征是:

设计人员按照“自顶向下”的设计方法,对整个系统进行方案设计和功能划分,系统的关键

电路用一片或几片集成电路(FPGA/CPLD) 实现。

电子琴是数字电路中的一个典型应用。在实际的硬件设计中用到的器件非常多,连线比

较复杂,同时会产生比较大的延时,从而造成测量误差较大,可靠性不好。以 EDA 工具作

为开发手段,运用 VHDL 硬件描述语言将使整个系统大大简化,提高了电子琴整体的性能

和可靠性。

1.2 VHDL 语言和 QUARTUS II 环境简介

1.2.1 VHDL 语言简介

VHDL 是超高速集成电路硬件描述语言,是一种用于电路设计的高级语言。它出现于

80 年代后期,最初是由美国国防部开发出来的,是为了供美军用来提高设计的可靠性和缩

减开发周期的一种使用范围较小的设计语言 。VHDL 主要是应用在数字电路的设计中。目

前,它在中国的应用多数是用在 FPGA/CPLD/EPLD 的设计中,同时也被一些实力较为雄厚

的单位用来设计 ASIC。

VHDL 具有多层次描述系统硬件功能的能力,支持自顶向下和基于库的设计特点。其开

发流程:在顶层用方框图或硬件语言对电路的行为进行描述后,进行系统仿真验证和纠错。

再用逻辑综合优化工具生成具体的门级逻辑电路的网表。然后通过适配器将网表文件配置于

指定的目标器件,产生最终下载文件或配置文件。最后把适配后生成的下载或配置文件通过

编程器或编程电缆下载到具体的 FPGA/CPLD 器件中去,以便进行硬件调试和验证,而实现

可编程的专用集成电路 ASIC 的设计。

VHDL 主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征

的语句外,VHDL 的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

VHDL 系统设计与其他硬件描述语言相比,VHDL 具有更强的行为描述能力,从而决定了他

成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结构,从逻

辑行为上描述和设计大规模电子系统的重要保证。[1]

1.2.2 Quartus II 简介

Quartus II 是 Altera 公司的综合性 PLD 开发软件,支持原理图、VHDL、VerilogHDL

以及 AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合

器以及仿真器,可以完成从设计输入到硬件配置的完整 CPLD 设计流程。

Quartus II 支持 Altera 的 IP 核,包含了 LPM/MegaFunction 宏功能模块库,使用户可以

充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。Maxplus II 作为 Altera 的上

3

�

一代 PLD 设计软件,由于其出色的易用性而得到了广泛的应用。目前 Altera 已经停止了对

Maxplus II 的更新支持,Quartus II 与之相比不仅仅是支持器件类型的丰富和图形界面的改

变。Altera 在 Quartus II 中包含了许多诸如 SignalTap II、Chip Editor 和 RTL Viewer 的设计

辅助工具,集成了 SOPC 和 HardCopy 设计流程,并且继承了 Maxplus II 友好的图形界面及

简便的使用方法。Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能

力和直观易用的接口,越来越受到数字系统设计者的欢迎。[2]

第 2 章 方案选择及原理分析

2.1 方案比较

方案一:采用数字逻辑电路制作,用 IC 拼凑焊接实现。其特点是直接用现成的 IC 组合

而成,简单方便,但本系统需用到许多分频器,这就使得需要用到相当多的 IC,从而造成

了体积过于庞大,而且连线也会比较复杂。

方案二:采用单片机实现,通过软件编程,仿真后将程序用编程器写入到单片机芯片上,

该方案成本低,稳定度也比较好,但外围电路多,特别是播放音乐时需要用到大容量的外部

存储器,这样就增加了编程难度,调试不够直观,也不够灵活方便。

方案三:采用可编程逻辑器件(FPGA)制作,将所有器件集成在一块芯片上,大大减小

了电子琴的体积,用 VHDL 编程实现时更加方便,而且易于进行功能扩展,并可调试仿真,

制作时间大大缩短,因此选用了方案三进行设计。

2.2 电子琴设计原理

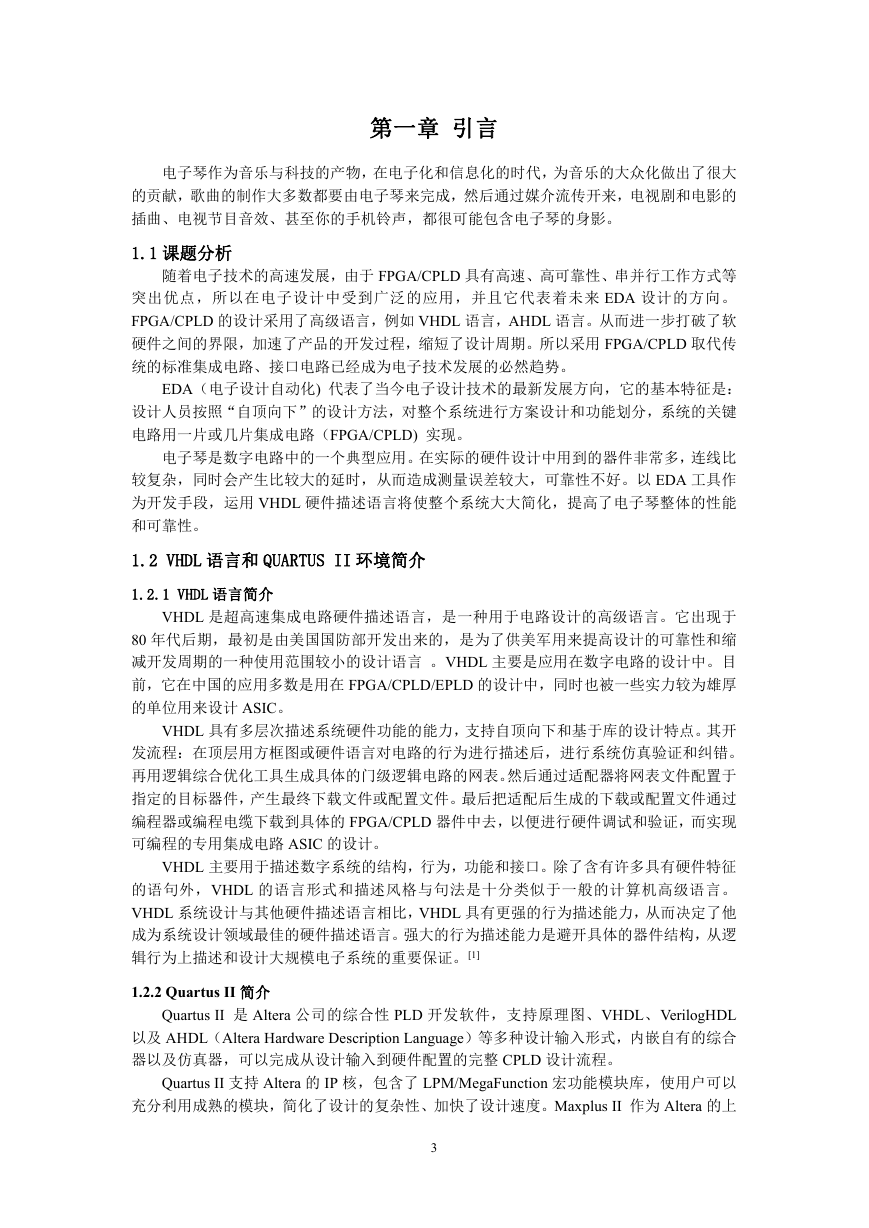

乐曲都是由一连串的音符组成,按照乐曲的乐谱依次输出这些音符所对应的频率,就可

以在扬声器上连续地发出各个音符的音调。为了准确地演奏出一首乐曲,仅仅让扬声器能够

发出声音是远远不够的,还必须准确地控制乐曲的节奏,即每个音符的持续时间。由此可见,

乐曲中每个音符的发音频率以及音符持续的时间是乐曲能够连续演奏的两个关键因素。

乐曲的 12 平均率规定:每 2 个八度音之间的频率要相差 1 倍,比如简谱中的中音 2 与

高音 2。在 2 个八度音之间,又可分为 12 个半音。另外,音符 A(简谱中的低音 5)的频率为

392Hz,音符 E 到 F 之间、B 到 C 之间为半音,其余为全音。由此可以计算出简谱中从低音

l 至高音 1 之间每个音符的频率。简谱音名与频率对应关系如图 2-1 所示:

音名

低音 1

低音 2

低音 3

低音 4

低音 5

低音 6

低音 7

频率/Hz

262

296

330

350

392

440

494

频率/Hz

1047

1175

1319

1397

1568

1760

1976

音名

中音 1

中音 2

中音 3

中音 4

中音 5

中音 6

中音 7

频率/Hz

523

587

659

698

784

880

988

音名

高音 1

高音 2

高音 3

高音 4

高音 5

高音 6

高音 7

表 2-1 简谱音名与频率的对应关系

产生各音符所需的频率使用一分频器来实现,由于各音符对应的频率多为非整数,而分

频系数又不能为小数,所以必须将计算得到的分频数四舍五入取整数。若分频器时钟频率过

低,则由于分频系数过小,四舍五入取整数后的误差较大;若时钟频率过高,虽然误差变小,

但分频数将会变大。在实际的设计中应综合考虑这两方面的因素,在尽量减小频率误差的前

提下取合适的时钟频率。实际上,只要各个音符间的相对频率关系不变,演奏出的乐曲听起

来都不会走调。

4

�

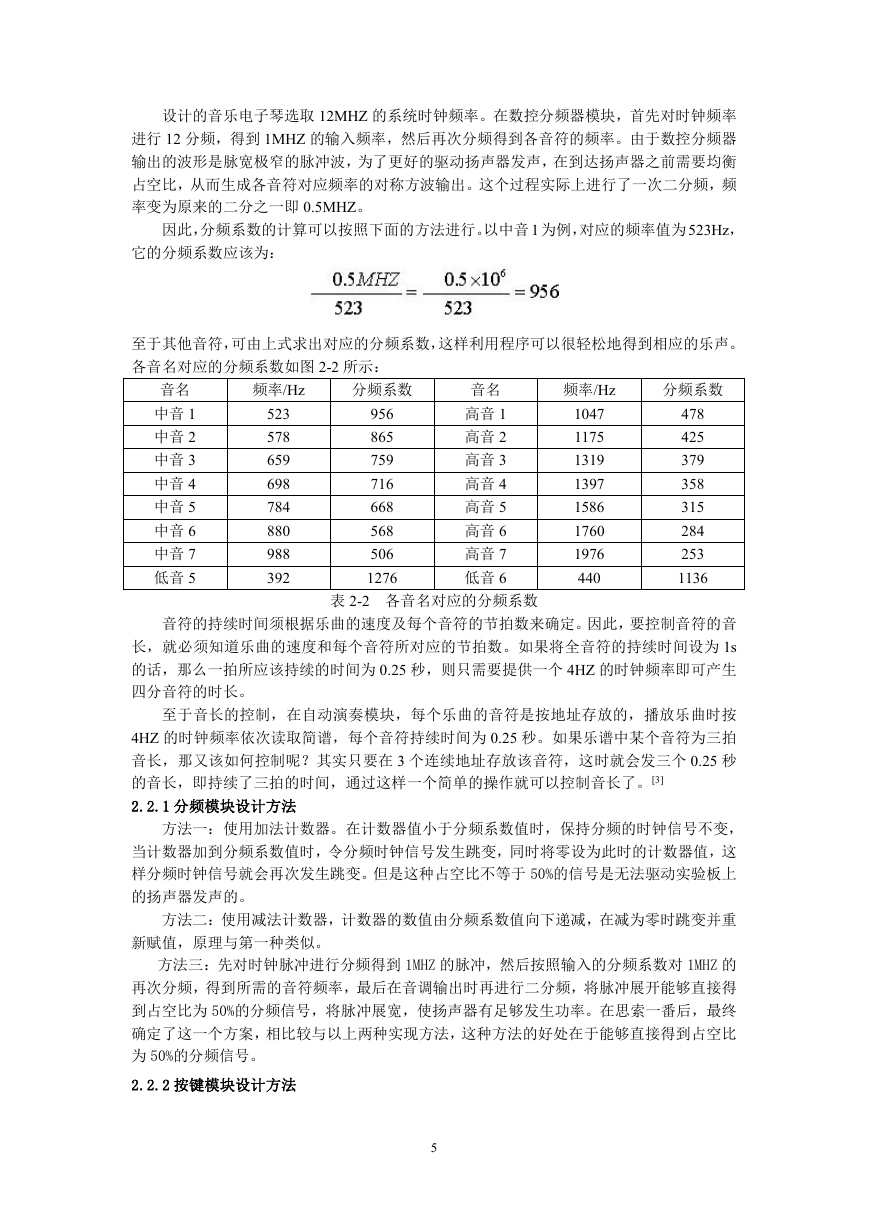

设计的音乐电子琴选取 12MHZ 的系统时钟频率。在数控分频器模块,首先对时钟频率

进行 12 分频,得到 1MHZ 的输入频率,然后再次分频得到各音符的频率。由于数控分频器

输出的波形是脉宽极窄的脉冲波,为了更好的驱动扬声器发声,在到达扬声器之前需要均衡

占空比,从而生成各音符对应频率的对称方波输出。这个过程实际上进行了一次二分频,频

率变为原来的二分之一即 0.5MHZ。

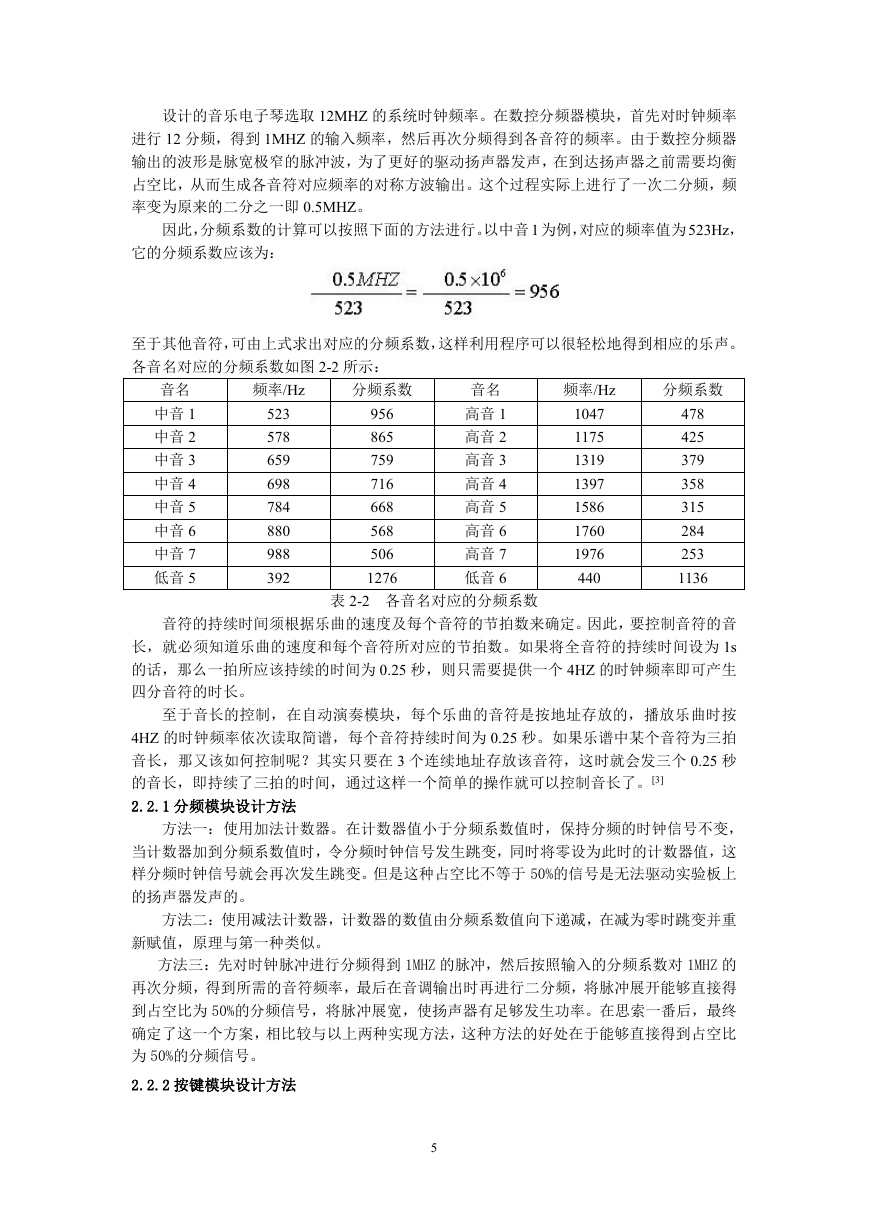

因此,分频系数的计算可以按照下面的方法进行。以中音 1 为例,对应的频率值为 523Hz,

它的分频系数应该为:

至于其他音符,可由上式求出对应的分频系数,这样利用程序可以很轻松地得到相应的乐声。

各音名对应的分频系数如图 2-2 所示:

音名

中音 1

中音 2

中音 3

中音 4

中音 5

中音 6

中音 7

低音 5

频率/Hz

分频系数

523

578

659

698

784

880

988

392

956

865

759

716

668

568

506

1276

音名

高音 1

高音 2

高音 3

高音 4

高音 5

高音 6

高音 7

低音 6

频率/Hz

分频系数

1047

1175

1319

1397

1586

1760

1976

440

478

425

379

358

315

284

253

1136

表 2-2 各音名对应的分频系数

音符的持续时间须根据乐曲的速度及每个音符的节拍数来确定。因此,要控制音符的音

长,就必须知道乐曲的速度和每个音符所对应的节拍数。如果将全音符的持续时间设为 1s

的话,那么一拍所应该持续的时间为 0.25 秒,则只需要提供一个 4HZ 的时钟频率即可产生

四分音符的时长。

至于音长的控制,在自动演奏模块,每个乐曲的音符是按地址存放的,播放乐曲时按

4HZ 的时钟频率依次读取简谱,每个音符持续时间为 0.25 秒。如果乐谱中某个音符为三拍

音长,那又该如何控制呢?其实只要在 3 个连续地址存放该音符,这时就会发三个 0.25 秒

的音长,即持续了三拍的时间,通过这样一个简单的操作就可以控制音长了。[3]

2.2.1 分频模块设计方法

方法一:使用加法计数器。在计数器值小于分频系数值时,保持分频的时钟信号不变,

当计数器加到分频系数值时,令分频时钟信号发生跳变,同时将零设为此时的计数器值,这

样分频时钟信号就会再次发生跳变。但是这种占空比不等于 50%的信号是无法驱动实验板上

的扬声器发声的。

方法二:使用减法计数器,计数器的数值由分频系数值向下递减,在减为零时跳变并重

新赋值,原理与第一种类似。

方法三:先对时钟脉冲进行分频得到 1MHZ 的脉冲,然后按照输入的分频系数对 1MHZ 的

再次分频,得到所需的音符频率,最后在音调输出时再进行二分频,将脉冲展开能够直接得

到占空比为 50%的分频信号,将脉冲展宽,使扬声器有足够发生功率。在思索一番后,最终

确定了这一个方案,相比较与以上两种实现方法,这种方法的好处在于能够直接得到占空比

为 50%的分频信号。

2.2.2 按键模块设计方法

5

�

按键模块在这个系统中的作用是每按下实验板上的一个键,该模块要相应的输出一个分

频系数,用程序将该分频系数送到分频模块后将会产生一个特定频率的信号,传送到实验板

上的扬声器里,并发出不同频率的声音即音符。由于每输入一个信号,就产生一个特定的输

出信号,且每种情况均能罗列,再加上情况总数(电子琴音调个数)不是很大,故我们使

case 语句来实现。

2.2.3 顶层模块设计方法

顶层模块的设计就是要设计一个顶层模块将各模块进行例化连接,再组成一个协同发挥

功能的的整体。我们注意到,分频模块需要一个分频系数,而键入模块将会产生一个分频系

数,因此分频系数在整个系统中将既不输入也不输出,在例化时,我们使用一个信号与之相

连,这样它就能在模块间传递。

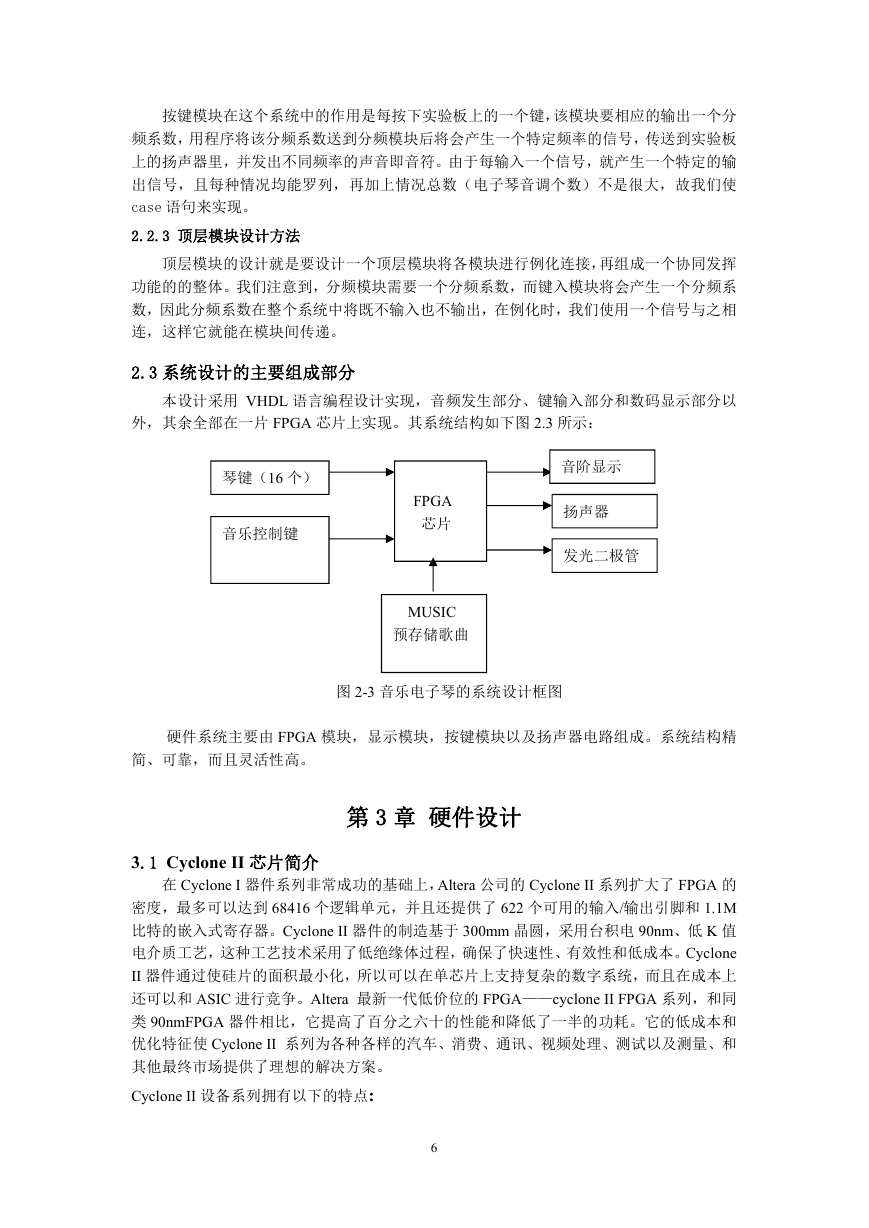

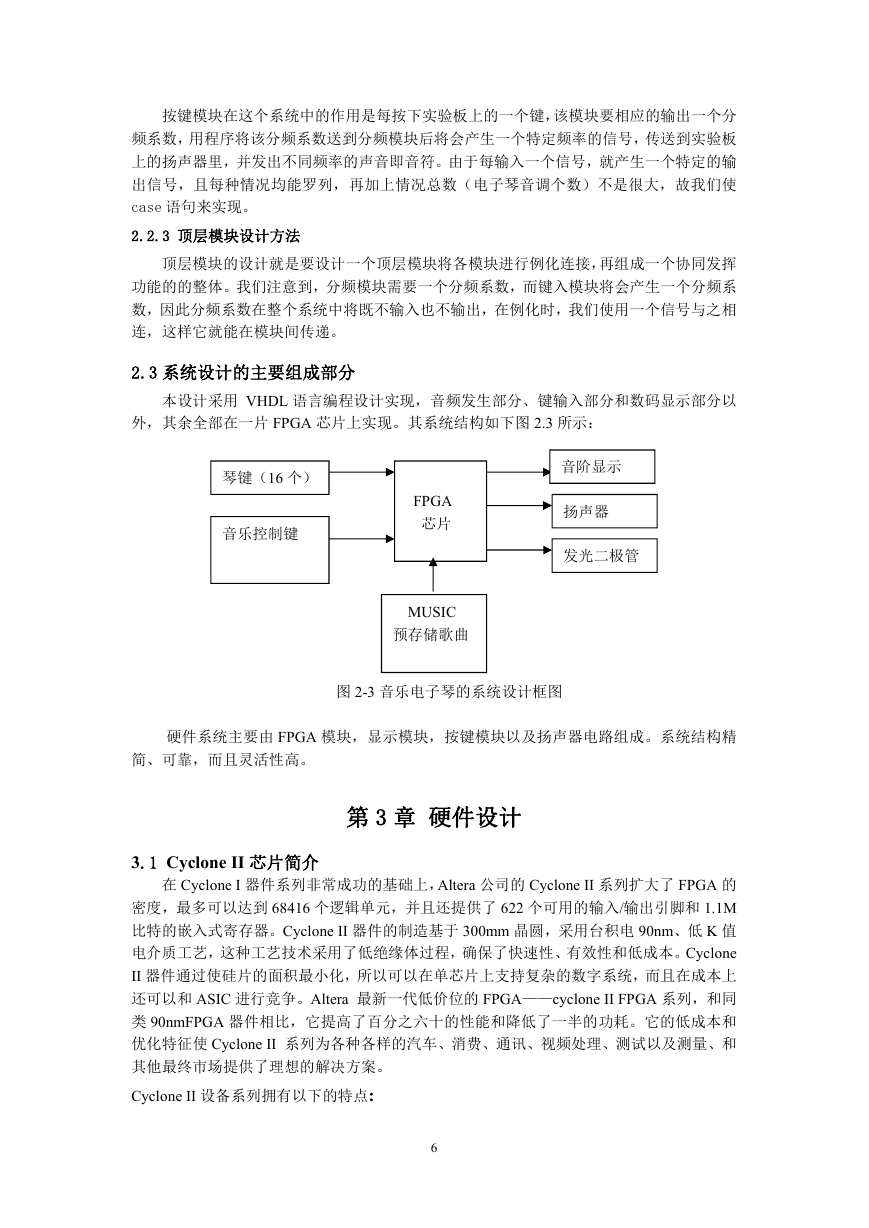

2.3 系统设计的主要组成部分

本设计采用 VHDL 语言编程设计实现,音频发生部分、键输入部分和数码显示部分以

外,其余全部在一片 FPGA 芯片上实现。其系统结构如下图 2.3 所示:

琴键(16 个)

音乐控制键

FPGA

芯片

MUSIC

预存储歌曲

音阶显示

扬声器

发光二极管

图 2-3 音乐电子琴的系统设计框图

硬件系统主要由 FPGA 模块,显示模块,按键模块以及扬声器电路组成。系统结构精

简、可靠,而且灵活性高。

第 3 章 硬件设计

3.1 Cyclone II 芯片简介

在 Cyclone I 器件系列非常成功的基础上,Altera 公司的 Cyclone II 系列扩大了 FPGA 的

密度,最多可以达到 68416 个逻辑单元,并且还提供了 622 个可用的输入/输出引脚和 1.1M

比特的嵌入式寄存器。Cyclone II 器件的制造基于 300mm 晶圆,采用台积电 90nm、低 K 值

电介质工艺,这种工艺技术采用了低绝缘体过程,确保了快速性、有效性和低成本。Cyclone

II 器件通过使硅片的面积最小化,所以可以在单芯片上支持复杂的数字系统,而且在成本上

还可以和 ASIC 进行竞争。Altera 最新一代低价位的 FPGA——cyclone II FPGA 系列,和同

类 90nmFPGA 器件相比,它提高了百分之六十的性能和降低了一半的功耗。它的低成本和

优化特征使 Cyclone II 系列为各种各样的汽车、消费、通讯、视频处理、测试以及测量、和

其他最终市场提供了理想的解决方案。

Cyclone II 设备系列拥有以下的特点:

6

�

●4608 到 68416 LEs 的高密度的结构;

●嵌入式乘法器;

●先进的 I/O 口支持;

●灵活的时钟管理电路;

●设备的配置;[4]

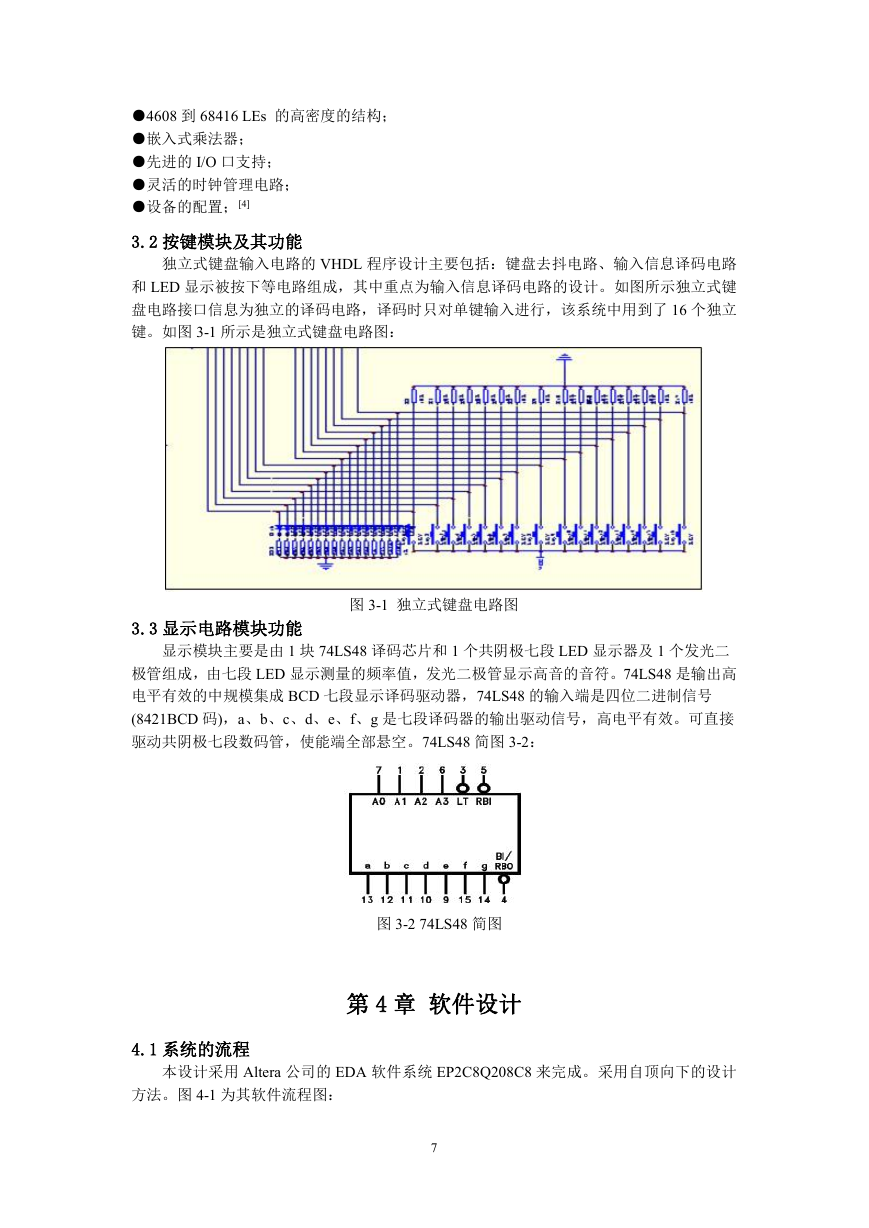

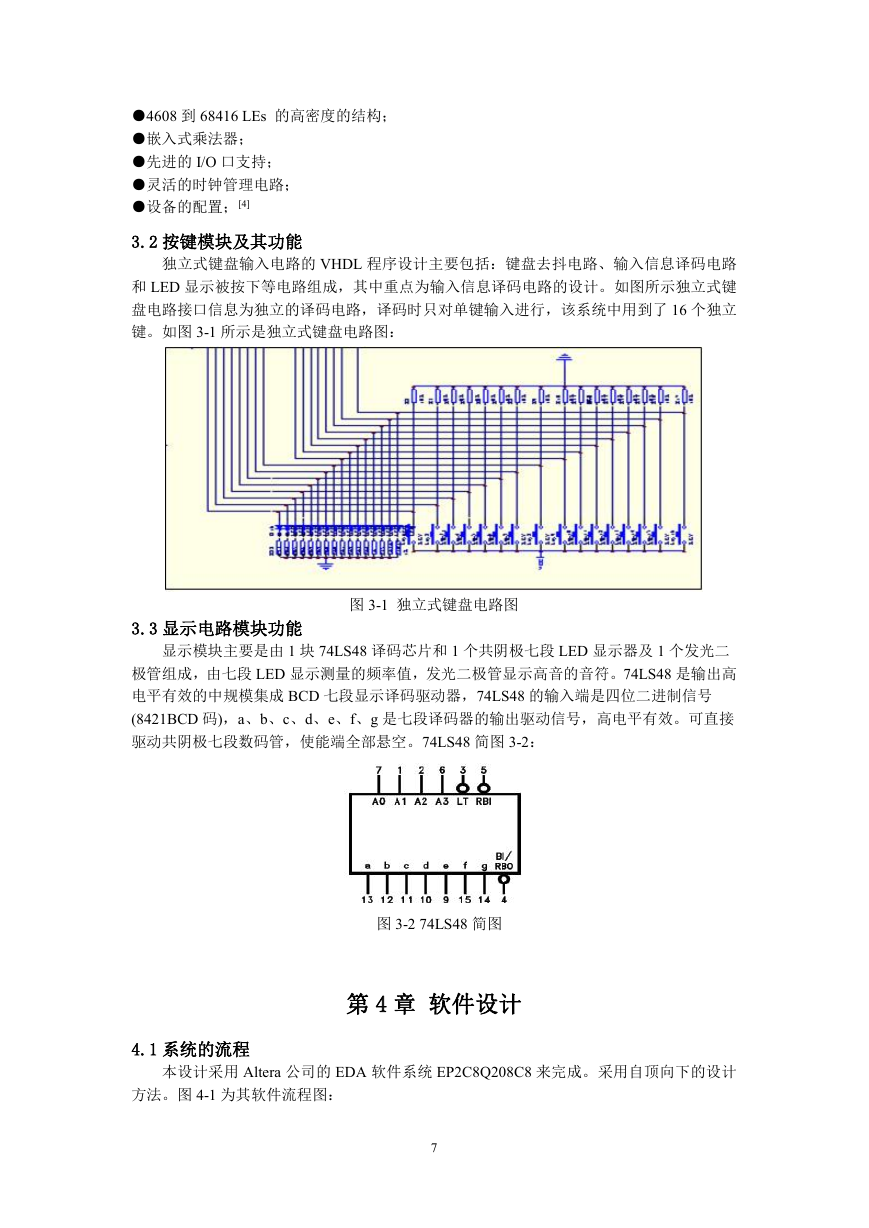

3.2 按键模块及其功能

独立式键盘输入电路的 VHDL 程序设计主要包括:键盘去抖电路、输入信息译码电路

和 LED 显示被按下等电路组成,其中重点为输入信息译码电路的设计。如图所示独立式键

盘电路接口信息为独立的译码电路,译码时只对单键输入进行,该系统中用到了 16 个独立

键。如图 3-1 所示是独立式键盘电路图:

图 3-1 独立式键盘电路图

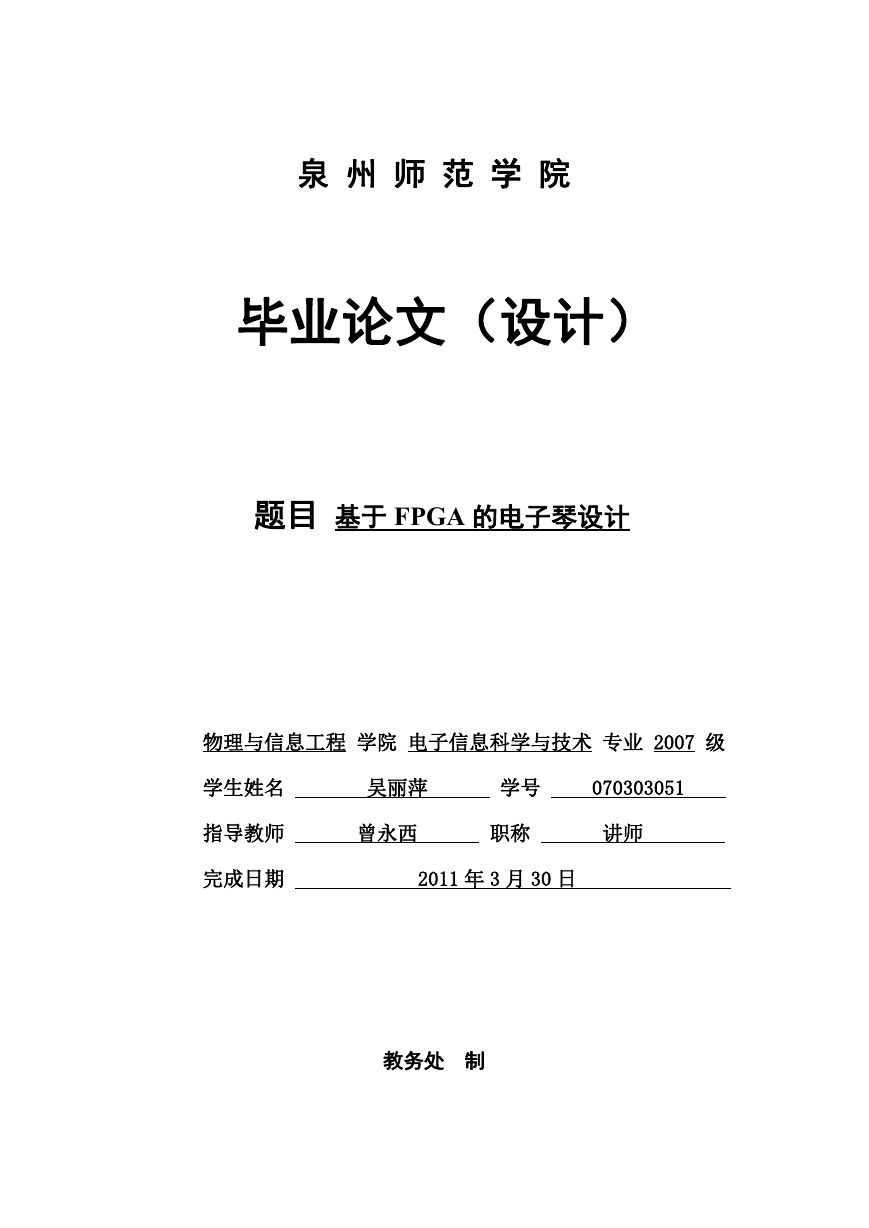

3.3 显示电路模块功能

显示模块主要是由 1 块 74LS48 译码芯片和 1 个共阴极七段 LED 显示器及 1 个发光二

极管组成,由七段 LED 显示测量的频率值,发光二极管显示高音的音符。74LS48 是输出高

电平有效的中规模集成 BCD 七段显示译码驱动器,74LS48 的输入端是四位二进制信号

(8421BCD 码),a、b、c、d、e、f、g 是七段译码器的输出驱动信号,高电平有效。可直接

驱动共阴极七段数码管,使能端全部悬空。74LS48 简图 3-2:

图 3-2 74LS48 简图

第 4 章 软件设计

4.1 系统的流程

本设计采用 Altera 公司的 EDA 软件系统 EP2C8Q208C8 来完成。采用自顶向下的设计

方法。图 4-1 为其软件流程图:

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc