RK3399 Datasheet

Rev 1.6

Rockchip

RK3399

Datasheet

Revision 1.6

Mar. 2017

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 1 -

�

RK3399 Datasheet

Rev 1.6

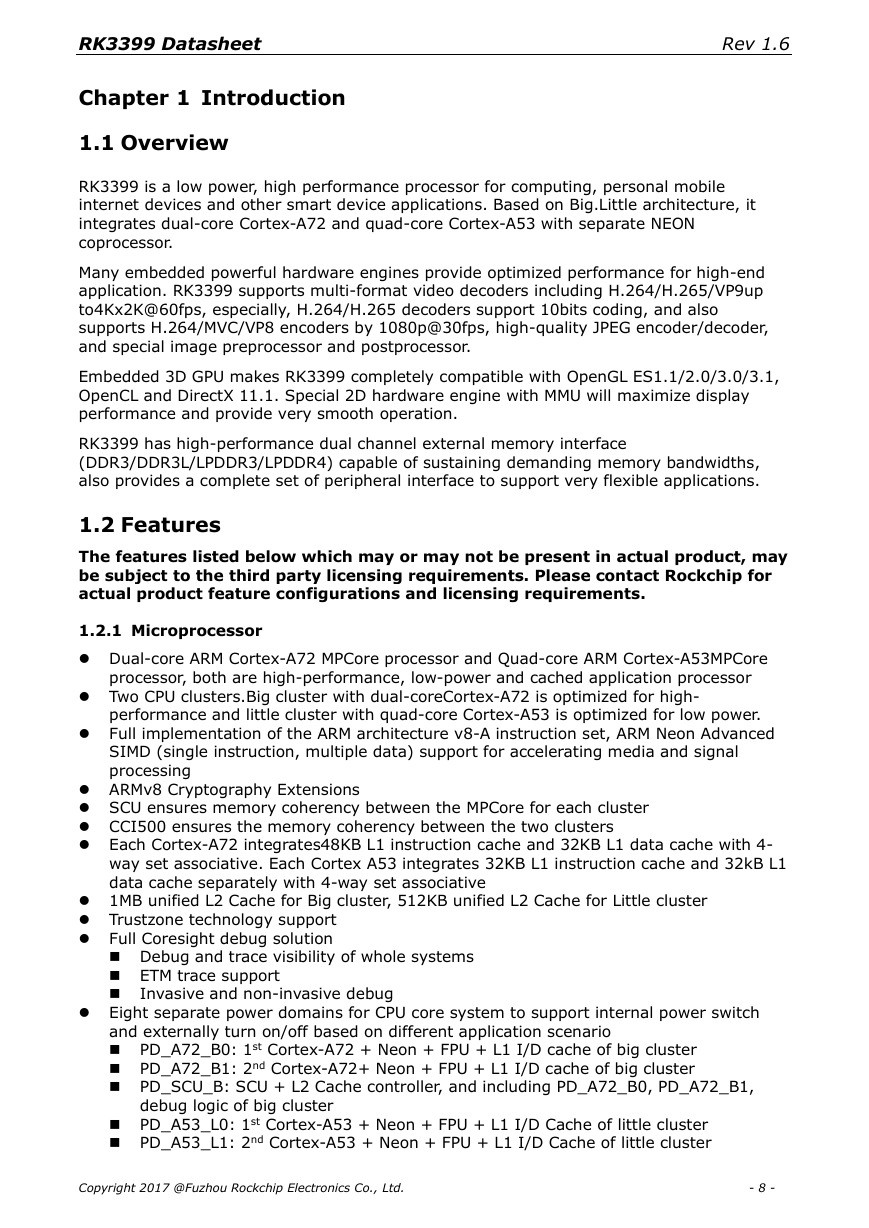

Date

Revision

Description

Revision History

2017-3-1

2016-12-20

1.6

1.5

2016-12-06

1.4

2016-10-30

2016-9-30

1.3

1.2

2016-8-15

1.1

2016-5-04

1.0

Update

Update “Recommended Operating Conditions” for CPU

A72

Removed repeated “EMMC_COREDLL_0V9” in section 3.2

Add ball description for “EMMC_COREDLL_0V9” in section

2.6

Updated ball description for DDR1 in section 2.6

Update the description about video codec

Updated I2C information about Fast-mode plus feature

Updated video codec about H264/H265/VP9

Updated voltage information for power supply

Updated PCIe specification

Updated “Features” section

Initial Release

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 2 -

�

RK3399 Datasheet

Rev 1.6

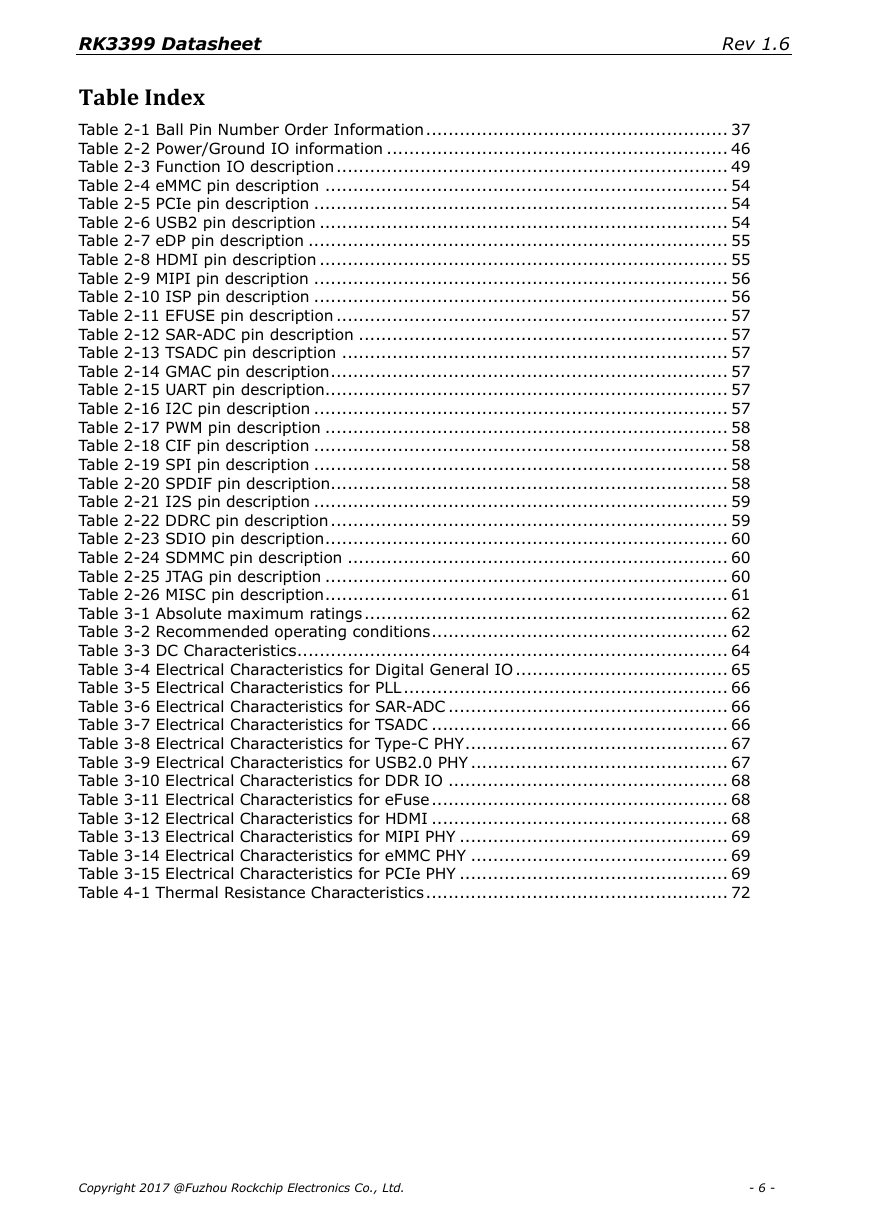

Table of Content

Table of Content .................................................................................................. 3

Figure Index ....................................................................................................... 5

Table Index 6

Chapter 1 Introduction ....................................................................................... 8

1.1 Overview ................................................................................................ 8

1.2 Features ................................................................................................. 8

1.3 Block Diagram ...................................................................................... 26

Chapter 2 Package information ........................................................................... 27

2.1 Ordering information ............................................................................. 27

2.2 Top Marking .......................................................................................... 27

2.3 Dimension ............................................................................................ 27

2.4 Ball Map ............................................................................................... 29

2.5 Ball Pin Number Order ........................................................................... 37

2.6 Power/ground IO descriptions ................................................................. 46

2.7 Function IO description .......................................................................... 49

2.8 IO pin name descriptions ........................................................................ 54

Chapter 3 Electrical Specification ........................................................................ 62

3.1 Absolute Maximum Ratings ..................................................................... 62

3.2 Recommended Operating Conditions ........................................................ 62

3.3 DC Characteristics ................................................................................. 64

3.4 Electrical Characteristics for General IO .................................................... 65

3.5 Electrical Characteristics for PLL .............................................................. 66

3.6 Electrical Characteristics for SAR-ADC ...................................................... 66

3.7 Electrical Characteristics for TSADC ......................................................... 66

3.8 Electrical Characteristics for Type-C PHY ................................................... 67

3.9 Electrical Characteristics for USB2.0 PHY .................................................. 67

3.10 Electrical Characteristics for DDR IO ...................................................... 68

3.11 Electrical Characteristics for eFuse ......................................................... 68

3.12 Electrical Characteristics for HDMI ......................................................... 68

3.13 Electrical Characteristics for MIPI PHY .................................................... 69

3.14 Electrical Characteristics for eMMC PHY .................................................. 69

3.15 Electrical Characteristics for PCIe PHY .................................................... 69

Chapter 4 Thermal Management ......................................................................... 72

4.1 Overview .............................................................................................. 72

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 3 -

�

RK3399 Datasheet

Rev 1.6

4.2 Package Thermal Characteristics ............................................................. 72

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 4 -

�

RK3399 Datasheet

Rev 1.6

Figure Index

Fig. 1-1 Block Diagram ........................................................................................ 26

Fig. 2-1 Top Marking ........................................................................................... 27

Fig. 2-2 Package Top and SideView ....................................................................... 27

Fig. 2-3 Package Bottom View .............................................................................. 28

Fig. 2-4 Package Dimension ................................................................................. 28

Fig. 2-5 Ball Mapping Diagram .............................................................................. 29

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 5 -

�

RK3399 Datasheet

Rev 1.6

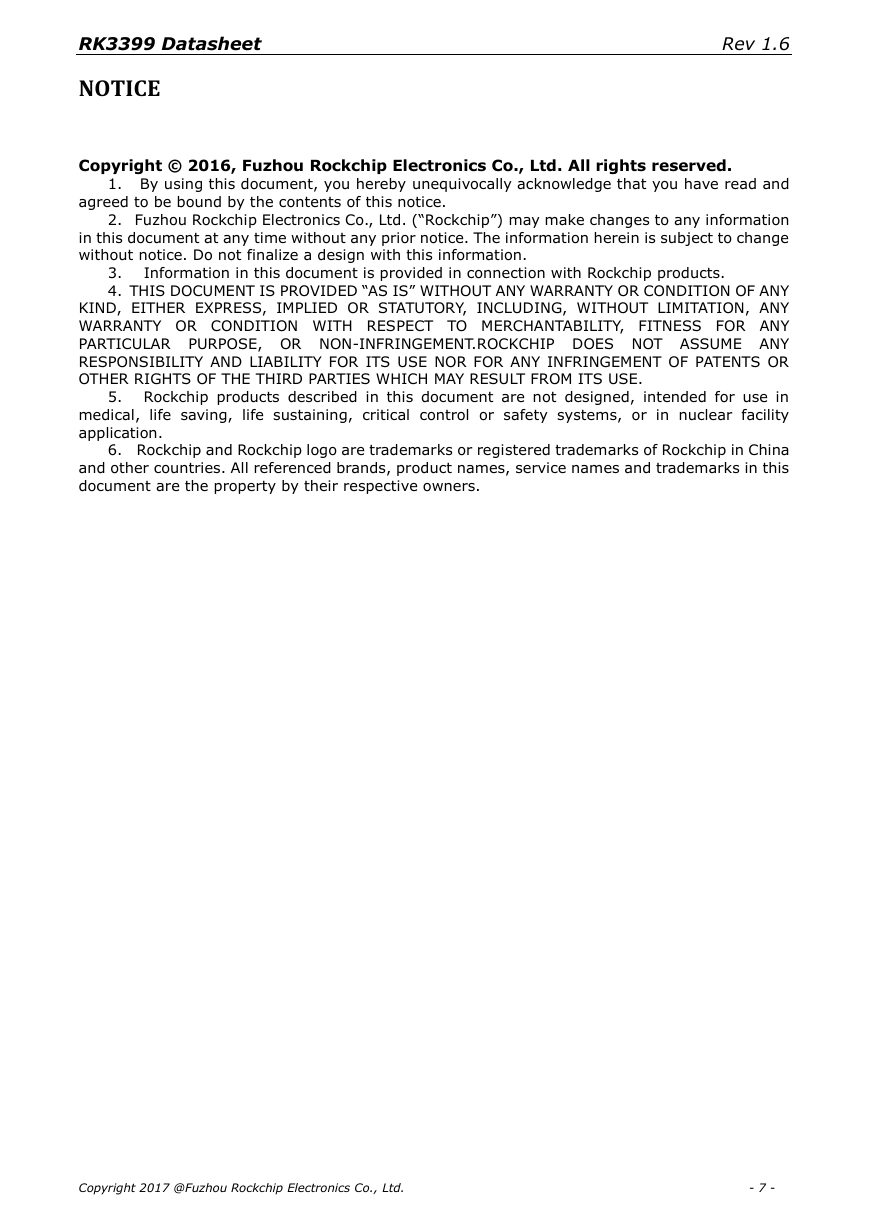

Table Index

Table 2-1 Ball Pin Number Order Information ...................................................... 37

Table 2-2 Power/Ground IO information ............................................................. 46

Table 2-3 Function IO description ...................................................................... 49

Table 2-4 eMMC pin description ........................................................................ 54

Table 2-5 PCIe pin description .......................................................................... 54

Table 2-6 USB2 pin description ......................................................................... 54

Table 2-7 eDP pin description ........................................................................... 55

Table 2-8 HDMI pin description ......................................................................... 55

Table 2-9 MIPI pin description .......................................................................... 56

Table 2-10 ISP pin description .......................................................................... 56

Table 2-11 EFUSE pin description ...................................................................... 57

Table 2-12 SAR-ADC pin description .................................................................. 57

Table 2-13 TSADC pin description ..................................................................... 57

Table 2-14 GMAC pin description ....................................................................... 57

Table 2-15 UART pin description........................................................................ 57

Table 2-16 I2C pin description .......................................................................... 57

Table 2-17 PWM pin description ........................................................................ 58

Table 2-18 CIF pin description .......................................................................... 58

Table 2-19 SPI pin description .......................................................................... 58

Table 2-20 SPDIF pin description ....................................................................... 58

Table 2-21 I2S pin description .......................................................................... 59

Table 2-22 DDRC pin description ....................................................................... 59

Table 2-23 SDIO pin description ........................................................................ 60

Table 2-24 SDMMC pin description .................................................................... 60

Table 2-25 JTAG pin description ........................................................................ 60

Table 2-26 MISC pin description ........................................................................ 61

Table 3-1 Absolute maximum ratings ................................................................. 62

Table 3-2 Recommended operating conditions ..................................................... 62

Table 3-3 DC Characteristics ............................................................................. 64

Table 3-4 Electrical Characteristics for Digital General IO ...................................... 65

Table 3-5 Electrical Characteristics for PLL .......................................................... 66

Table 3-6 Electrical Characteristics for SAR-ADC .................................................. 66

Table 3-7 Electrical Characteristics for TSADC ..................................................... 66

Table 3-8 Electrical Characteristics for Type-C PHY ............................................... 67

Table 3-9 Electrical Characteristics for USB2.0 PHY .............................................. 67

Table 3-10 Electrical Characteristics for DDR IO .................................................. 68

Table 3-11 Electrical Characteristics for eFuse ..................................................... 68

Table 3-12 Electrical Characteristics for HDMI ..................................................... 68

Table 3-13 Electrical Characteristics for MIPI PHY ................................................ 69

Table 3-14 Electrical Characteristics for eMMC PHY .............................................. 69

Table 3-15 Electrical Characteristics for PCIe PHY ................................................ 69

Table 4-1 Thermal Resistance Characteristics ...................................................... 72

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 6 -

�

RK3399 Datasheet

Rev 1.6

NOTICE

Copyright © 2016, Fuzhou Rockchip Electronics Co., Ltd. All rights reserved.

1. By using this document, you hereby unequivocally acknowledge that you have read and

agreed to be bound by the contents of this notice.

2. Fuzhou Rockchip Electronics Co., Ltd. (“Rockchip”) may make changes to any information

in this document at any time without any prior notice. The information herein is subject to change

without notice. Do not finalize a design with this information.

3. Information in this document is provided in connection with Rockchip products.

4. THIS DOCUMENT IS PROVIDED “AS IS” WITHOUT ANY WARRANTY OR CONDITION OF ANY

KIND, EITHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, ANY

WARRANTY OR CONDITION WITH RESPECT TO MERCHANTABILITY, FITNESS FOR ANY

PARTICULAR PURPOSE, OR NON-INFRINGEMENT.ROCKCHIP DOES NOT ASSUME ANY

RESPONSIBILITY AND LIABILITY FOR ITS USE NOR FOR ANY INFRINGEMENT OF PATENTS OR

OTHER RIGHTS OF THE THIRD PARTIES WHICH MAY RESULT FROM ITS USE.

5. Rockchip products described in this document are not designed, intended for use in

medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility

application.

6. Rockchip and Rockchip logo are trademarks or registered trademarks of Rockchip in China

and other countries. All referenced brands, product names, service names and trademarks in this

document are the property by their respective owners.

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 7 -

�

RK3399 Datasheet

Rev 1.6

Chapter 1 Introduction

1.1 Overview

RK3399 is a low power, high performance processor for computing, personal mobile

internet devices and other smart device applications. Based on Big.Little architecture, it

integrates dual-core Cortex-A72 and quad-core Cortex-A53 with separate NEON

coprocessor.

Many embedded powerful hardware engines provide optimized performance for high-end

application. RK3399 supports multi-format video decoders including H.264/H.265/VP9up

to4Kx2K@60fps, especially, H.264/H.265 decoders support 10bits coding, and also

supports H.264/MVC/VP8 encoders by 1080p@30fps, high-quality JPEG encoder/decoder,

and special image preprocessor and postprocessor.

Embedded 3D GPU makes RK3399 completely compatible with OpenGL ES1.1/2.0/3.0/3.1,

OpenCL and DirectX 11.1. Special 2D hardware engine with MMU will maximize display

performance and provide very smooth operation.

RK3399 has high-performance dual channel external memory interface

(DDR3/DDR3L/LPDDR3/LPDDR4) capable of sustaining demanding memory bandwidths,

also provides a complete set of peripheral interface to support very flexible applications.

1.2 Features

The features listed below which may or may not be present in actual product, may

be subject to the third party licensing requirements. Please contact Rockchip for

actual product feature configurations and licensing requirements.

1.2.1 Microprocessor

Dual-core ARM Cortex-A72 MPCore processor and Quad-core ARM Cortex-A53MPCore

processor, both are high-performance, low-power and cached application processor

Two CPU clusters.Big cluster with dual-coreCortex-A72 is optimized for high-

performance and little cluster with quad-core Cortex-A53 is optimized for low power.

Full implementation of the ARM architecture v8-A instruction set, ARM Neon Advanced

SIMD (single instruction, multiple data) support for accelerating media and signal

processing

ARMv8 Cryptography Extensions

SCU ensures memory coherency between the MPCore for each cluster

CCI500 ensures the memory coherency between the two clusters

Each Cortex-A72 integrates48KB L1 instruction cache and 32KB L1 data cache with 4-

way set associative. Each Cortex A53 integrates 32KB L1 instruction cache and 32kB L1

data cache separately with 4-way set associative

1MB unified L2 Cache for Big cluster, 512KB unified L2 Cache for Little cluster

Trustzone technology support

Full Coresight debug solution

Debug and trace visibility of whole systems

ETM trace support

Invasive and non-invasive debug

Eight separate power domains for CPU core system to support internal power switch

and externally turn on/off based on different application scenario

PD_A72_B0: 1st Cortex-A72 + Neon + FPU + L1 I/D cache of big cluster

PD_A72_B1: 2nd Cortex-A72+ Neon + FPU + L1 I/D cache of big cluster

PD_SCU_B: SCU + L2 Cache controller, and including PD_A72_B0, PD_A72_B1,

debug logic of big cluster

PD_A53_L0: 1st Cortex-A53 + Neon + FPU + L1 I/D Cache of little cluster

PD_A53_L1: 2nd Cortex-A53 + Neon + FPU + L1 I/D Cache of little cluster

Copyright 2017 @Fuzhou Rockchip Electronics Co., Ltd. - 8 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc