VCS 篇

基本选项及命令介绍

Vcs 选项里面通过 –v 加库,-f file_list(该文件里面为 rtl 代码或测例),

或直接加.v/.sv 文件时,需要注意,文件内容一定为 module …end 或

program…endprogram 或 package…endpackage 格式,如果是

task ,function,class 则必须包含在上述模块内,如果是以-v 方式加入文件,

无法在 verdi 中 trace 到内部信号

1.编译项+vcs+initreg+random 可以给所有的寄存器和 memory 赋一个随

机的初始值,也可以设置为 0 或 1,指的是变量设置为 reg 类型(wire,bit

等不会被初始化),在编译选项需要加上+vcs+initreg+random,运行选

项加上+vcs+initreg+0/1/random,最后 reg 类型的变量将是运行选项的

值 0/1/random;注意:当使用了上述+vcs+initreg+选项,如果在最开始

又对某个 reg 类型的变量赋一个取反的值,则这时会有一个 0 宽度的脉

宽

2. +vcs+initmen+random(0|1|x) 初始化存储器和多维数组;--用于前仿

真

3.compier 选项先+tc 再加 tb,由于编译的顺序,可以在 tc 中改变 tb 中的

一些 define 或预先 define,所以在 tb 中的 define 要求加上 ifndef 的

判决

4.如何单步运行,定位无限 0 延时的循环:当仿真时间没前进,但Δt 时间

在进行,这一般是存在延时为 0 的循环,则可以通过逐行运行来调试使

用 ctrl+c 停止仿真,在 run,重复该动作,会显示运行的语句,不能+RI

编译后立即运行,要采用 2 步 法,先 complie 然后在 simv。选项要加

-debug_all

5.FSDB 转 VCD 的方法

用法: fsdb2vcd

fsdb_fname [-o vcd_file_name] [options]

参数选择:

木秀于林,冲迎风霜 -- 每天积累一点点

1 / 1226

�

[-bt time[unit]] [-et time[unit]]

[-s [-nocase] {signal_name [-level n] [-verilog|vhdl]}]

[-keep_last_time]

[-map_ns_u [0/x/z]] [-map_ns_y [0/x/z]] [-map_ns_z [0/x/z]]

[-sv] [-v] [-vcs] [-f config_file]

[-bt time[unit]]

指定起始时间,如果不指定,将从 FSDB 的起始时间开始。时间单位可

以是 Ms/Ks

/s/ms/us/ns/ps/fs。如果不指定,将采用 ns。

[-et time[unit]]

指定结束时间,如果不指定,将从 FSDB 的结束时间结束。时间单位可以是

Ms/Ks

/s/ms/us/ns/ps/fs。如果不指定,将采用 ns。

-level n

转换所指定的层次和其向下 n 级层次结构的信号。必须和选项-s 连着使

用

-o

指定输出 VCD 文件的名字

-s

指定需要提取的信号或者层次

例子:

1. 转换所有的信号

%fsdb2vcd verilog.fsdb –o output.vcd

2. 转换指定时间范围和层次的信号

%fsdb2vcd verilog.fsdb –s /system/i_cpu –level 1 –bt 10 –et 1000

更多的解释,请直接在命令行输入 fsdb2vcd,就会有详细参数的解释。

5.截取 FSDB 中一段波形的方法:

fsdbextract

sorce.fsdb -bt (begintime)

-et (endtime) -s

/tb/udut/tp

-level 0 -o destine.fsdb 时间单位为 ns

木秀于林,冲迎风霜 -- 每天积累一点点

2 / 1226

�

6.当开启 -fsdb 命令是,需要设置 debussy 的环境变量,否则会提示

Error-[VPI-LOAD] VPI -load library error 错误

7.DUT_CMP_OPTIONS += +neg_tchk +overlap +sdfverbose -negdelay

–sdfretain

# neg_tchk 负延迟检查;overlap SDF 反标后的精确时序检查;

#sdfverbose 打印出详细的 SDF 反标信息;negdelay 允许 SDF 文件中负延

迟反标

8.DUT_CMP_OPTIONS+=+warn=noTFIPC,noSDFCOM_CFTC,noSDFCOM_NIOD,noS

DFCOM_RCI,noSDFCOM_ANICD,noSDFCOM_PONF,noSDFCOM_CFIIS,noSDFCOM

_MINF,noSDFCOM_IANE,noSDFCOM_TANE,noSDFCOM_SWC

#不报这些 warning。这是 SDF 反标时出现的,一般都不用管,其中

TFIPC,SDFCOM_CFTC 都表示 message ID,

原句为 +warn=no[ID]|all|none

##DUT_CMP_OPTIONS += +notimingcheck+nospecify+delay_mode_zero

# notimingcheck 忽略仿真中的时序检查;把 nospecify 的功能包含进去了,

Specify 都是在 rtl 的 module 中

#nospecify :库中的 cell,会有 specify 语句,指定延时信息的。Nospecify

去除延时信息。注意:如果后仿时有该选项,那么 sdf 文件的反标信息就不

能起作用。

# delay_mode_zero 去除仿真中延迟信息

9.Using Verilog System Tasks(产生波形的那几个函数)

Compilation

This can be done in following two ways:

•% vcs -fsdb [compile_options] verilog_filelist

•For –P tab flow, replace vcsd.tab with novas.tab, where novas.tab

is available in:

/share/PLI/VCS/${PLATFORM}/novas.tab

The following is the use model change:

木秀于林,冲迎风霜 -- 每天积累一点点

3 / 1226

�

% vcs -debug_pp -P $DEBUSSY_LIB/novas.tab $DEBUSSY_LIB/pli.a

[compile_options] verilog_filelist

使用 Verilog 系统函数需要使用 -P 那个包

但这时不能用 -fsdb 选项(2010.07 版本支持)它需要做如下环境变量设置

% setenv DEBUSSY_HOME Debussy_installation

% setenv DEBUSSY_LIB $DEBUSSY_HOME/share/PLI/VCS/LINUX

% setenv LD_LIBRARY_PATH

${DEBUSSY_HOME}/share/PLI/lib/LINUX:$DEBUSSY_LIB

% setenv LM_LICENSE_FILE[Debussy_license]:$LM_LICENSE_FILE

down 波形的步骤:

initial begin

$fdsbDumpfile(file_name); //生成波形的名字

$fsdbDumpvars(0,tb)//down 波形的层次,写了这句话,就会开始 down

波形;

//0 表示当前层及所有子层 ,1 表示当前层 ,2 表示往下一层,3,4..依

此类推.

$fsdbDumpon;

End

Stopping and resuming the dump ($dumpoff/$dumpon)

fsdbDumplimit - 限制 FSDB 文件 size

-- $fsdbDumpvars([], *)

fsdbDumpfile - 指定 FSDB 文件名

-- $fsdbDumpfile(“”)

fsdbDumpvars - Dump 指定的变量

--

fsdbDumpSingle - Dump 指定的信号

fsdbDumpvariable - Dump 指定的 VHDL 变量

木秀于林,冲迎风霜 -- 每天积累一点点

4 / 1226

�

fsdbSwitchDumpFile - 将 dumping 切换到另一个 FSDB 文件

-- $fsdbSwitchDumpFile(“”)

fsdbAutoSwitchDumpfile - 限制文件大小并在数据量过大时自动创建新的

FSDB 文件

-- $fsdbAutoSwitchDumpfile(, “”,< number of file>)

fsdbDumpflush - Force to Dump Result to FSDB file

fsdbDumpMem - Dump 指定的 memory 的内容

-- $fsdbDumpMem(, [, []])

$fsdbDumpon - 打开 FSDB dumping

$fsdbDumpoff - 关闭 FSDB dumping

当 DUT 的某些信号无法显示在 verdi 中时,请注意 fsdb 波形是否配置为最

顶层,即注意是否有 down 此模块的波形

10. sva 在波形上显示的方法:在 tb.v 中 dump 波形地方加上:

$fsdbDumpSVA

11. 如果要增加 assert 语法,需要包含 sva_lib.sv 库

12. 用+incdir 可以改变`include "../../rtl" 语句的相对的路径,但对

于没有用`include,而直接使用../../../rtl/这种做法,则相对的路径

以 compile 所在的目录为基准

13. DUT_CMP_OPTIONS += +neg_tchk +overlap +sdfverbose -negdelay

–sdfretain

# neg_tchk 负延迟检查;overlap SDF 反标后的精确时序检查;

#sdfverbose 打印出详细的 SDF 反标信息;negdelay 允许 SDF 文件中负延迟

反标

14. DUT_CMP_OPTIONS+warn=noTFIPC,noSDFCOM_CFTC,noSDFCOM_NIOD,noS

DFCOM_RCI,noSDFCOM_ANICD,noSDFCOM_PONF,noSDFCOM_CFIIS,noSDFCOM

_MINF,noSDFCOM_IANE,noSDFCOM_TANE,noSDFCOM_SWC#不报这些

warning。这是 SDF 反标时出现的,一般都不用管,其中

木秀于林,冲迎风霜 -- 每天积累一点点

5 / 1226

�

TFIPC,SDFCOM_CFTC 都表示 message ID,原句为

+warn=no[ID]|all|none

15. ##DUT_CMP_OPTIONS += +notimingcheck+nospecify+delay_mode_zero

# notimingcheck 忽略仿真中的时序检查;

#nospecify :库中的 cell,会有 specify 语句,指定延时信息的。Nospecify

去除延时信息。注意:如果后仿时有该选项,那么 sdf 文件的反标信息就不

能起作用。

# delay_mode_zero 去除仿真中延迟信息

路径延时说明

`timescale 1 ns / 1 ns

module design (out,in);

output out;

input in;

wire int1,int2;

assign #4 out=int2;//这个叫 delay_mode_distributed

buf #3 buf2 (int2,int1),

buf1 (int1,in);

//

specify

(in => out) = 7;

//这个叫 delay_mode_path

endspecify

endmodule

从上面模块可以看出 delay_mode_path 为 7ns, delay_mode_distributed 为

4+3+3=10ns,当编译选项有 delay_mode_path,这个模块的延时为 7ns,如果

有 delay_mode_distributed 选项,则这个模块延时为 10ns,如果两个选项都没

有,则 vcs 选用最大的数据

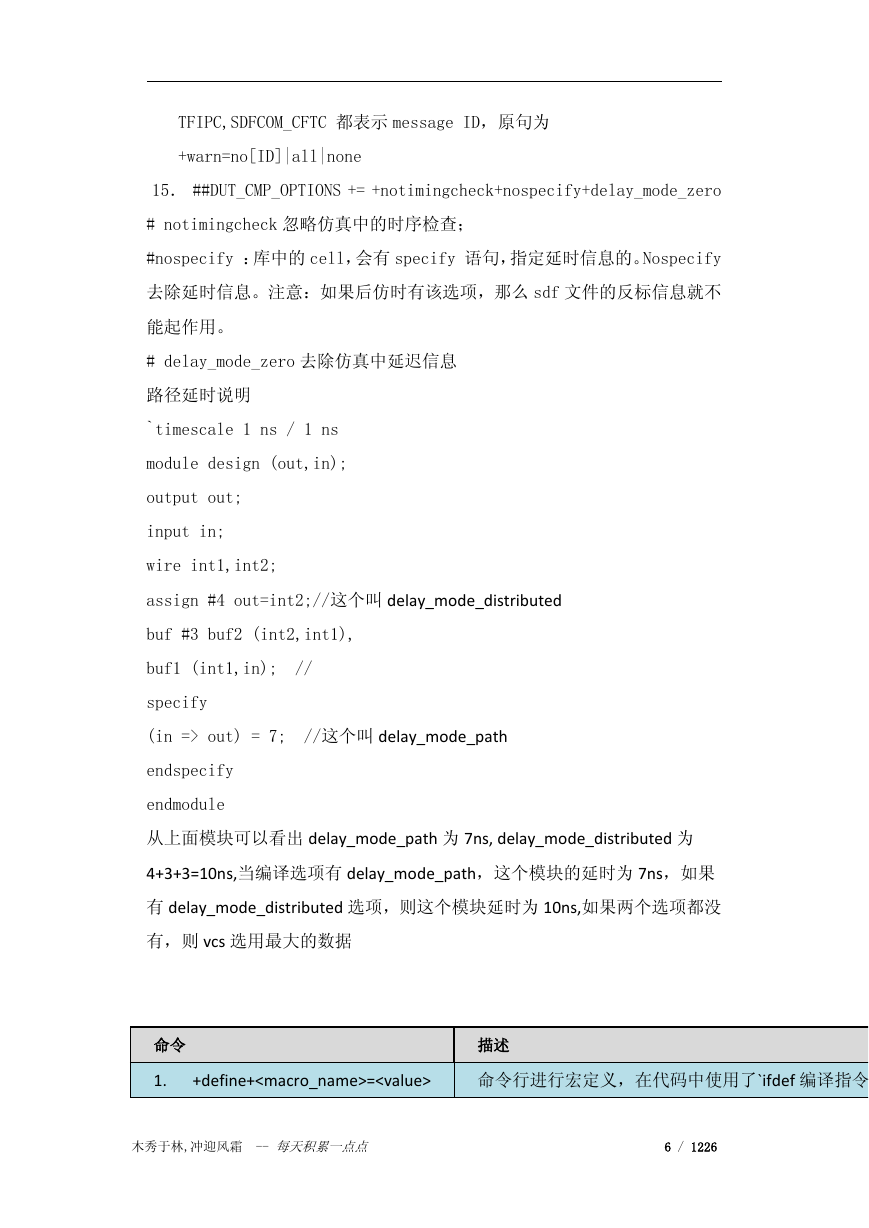

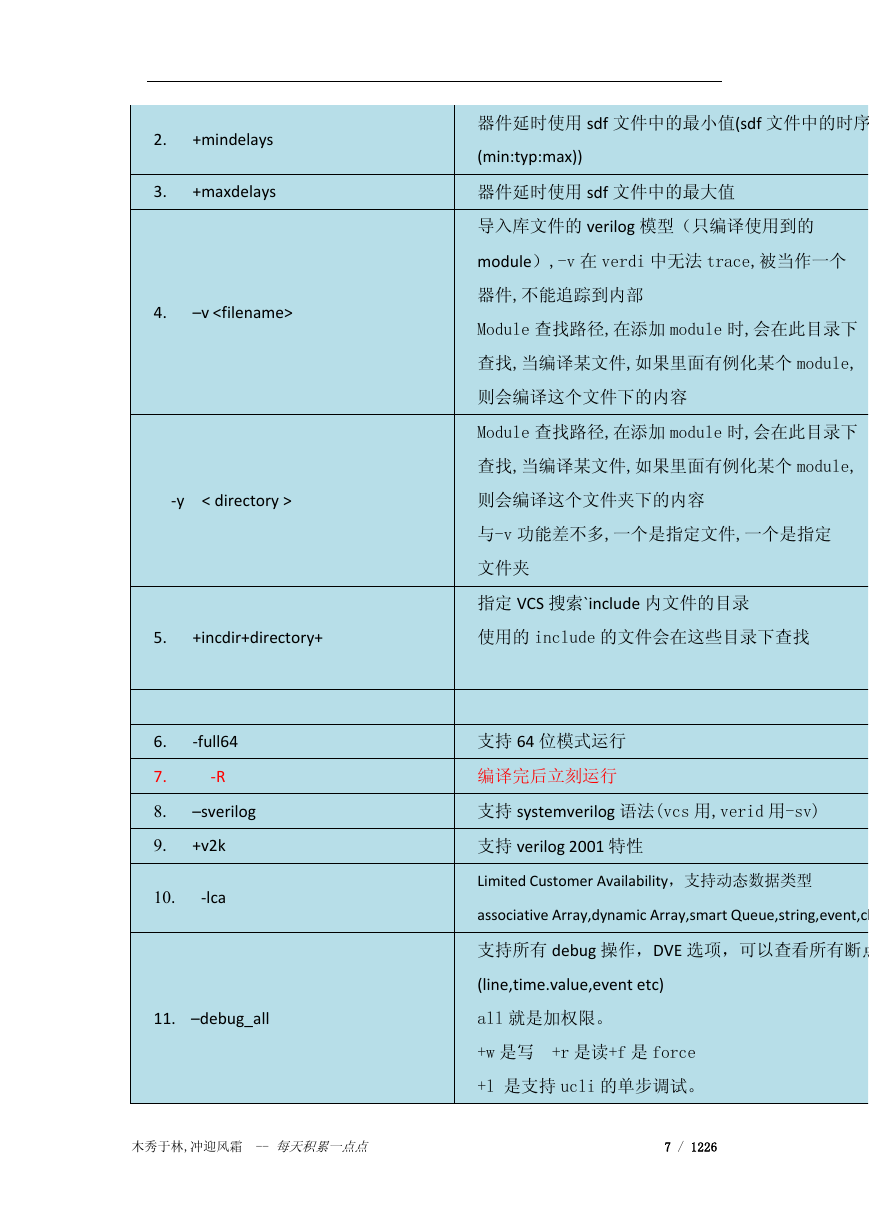

命令

描述

1.

+define+=

命令行进行宏定义,在代码中使用了`ifdef 编译指令

木秀于林,冲迎风霜 -- 每天积累一点点

6 / 1226

�

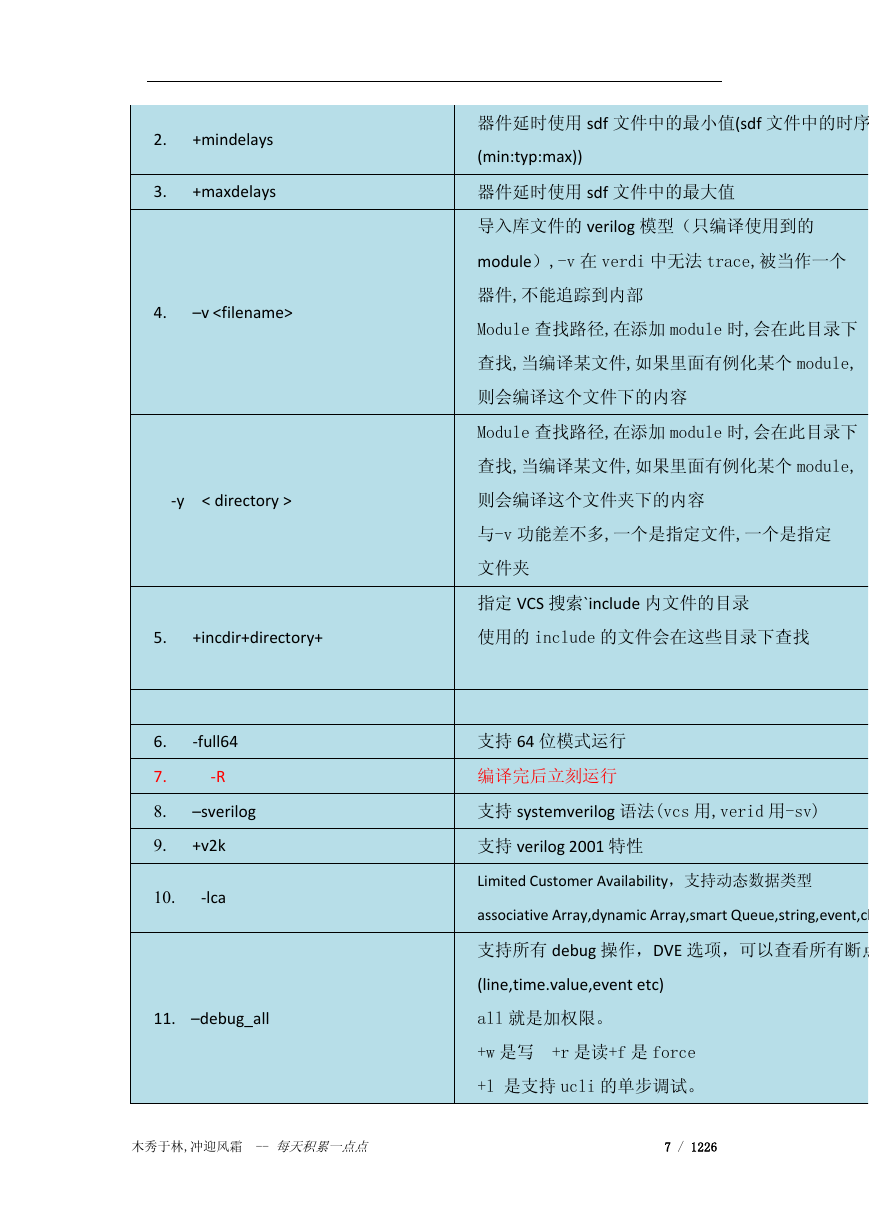

2.

3.

+mindelays

+maxdelays

4.

–v

器件延时使用 sdf 文件中的最小值(sdf 文件中的时序选择格式

(min:typ:max))

器件延时使用 sdf 文件中的最大值

导入库文件的 verilog 模型(只编译使用到的

module),-v 在 verdi 中无法 trace,被当作一个

器件,不能追踪到内部

Module 查找路径,在添加 module 时,会在此目录下

查找,当编译某文件,如果里面有例化某个 module,

则会编译这个文件下的内容

Module 查找路径,在添加 module 时,会在此目录下

查找,当编译某文件,如果里面有例化某个 module,

-y

< directory >

则会编译这个文件夹下的内容

与-v 功能差不多,一个是指定文件,一个是指定

文件夹

指定 VCS 搜索`include 内文件的目录

5.

+incdir+directory+

使用的 include 的文件会在这些目录下查找

6.

7.

8.

9.

-full64

-R

–sverilog

+v2k

10.

-lca

11. –debug_all

支持 64 位模式运行

编译完后立刻运行

支持 systemverilog 语法(vcs 用,verid 用-sv)

支持 verilog 2001 特性

Limited Customer Availability,支持动态数据类型

associative Array,dynamic Array,smart Queue,string,event,class

支持所有 debug 操作,DVE 选项,可以查看所有断点类型

(line,time.value,event etc)

all 就是加权限。

+w 是写 +r 是读+f 是 force

+l 是支持 ucli 的单步调试。

木秀于林,冲迎风霜 -- 每天积累一点点

7 / 1226

�

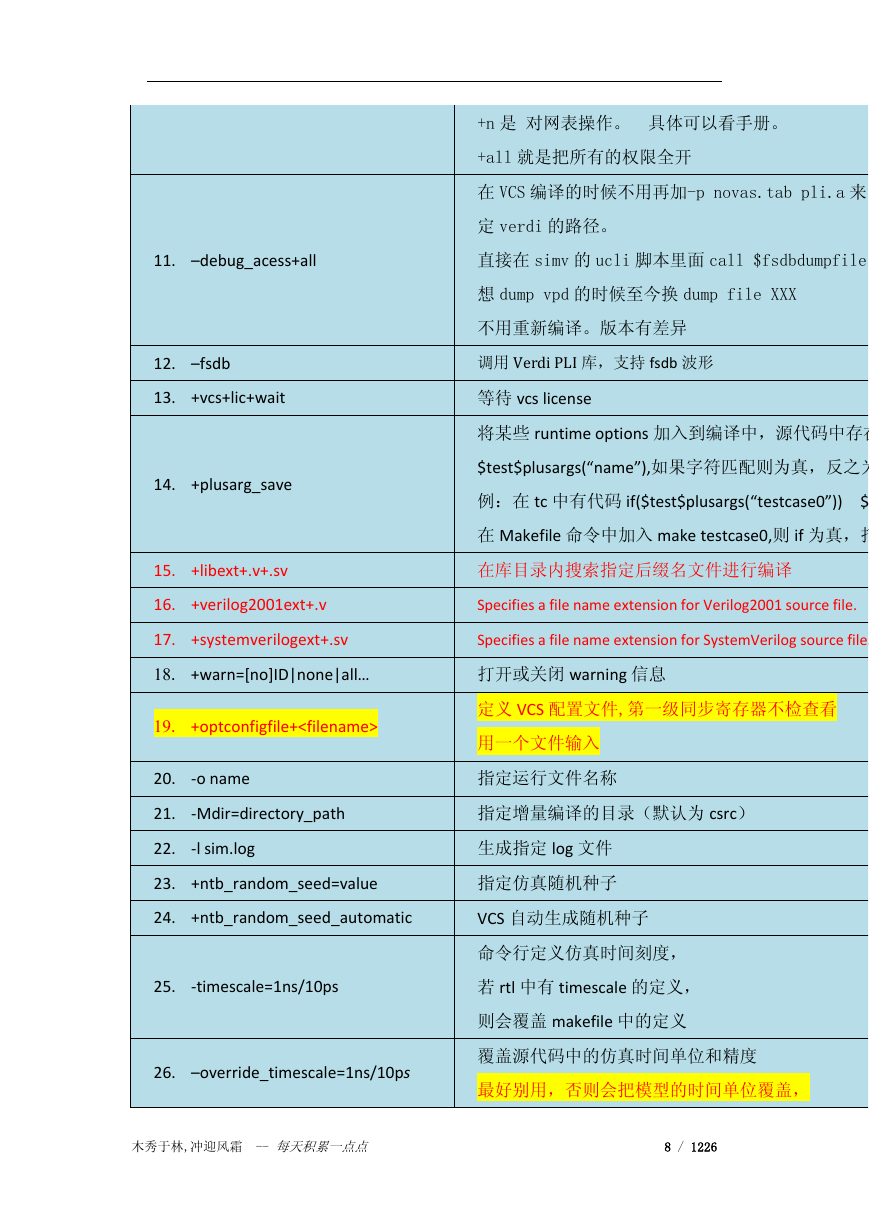

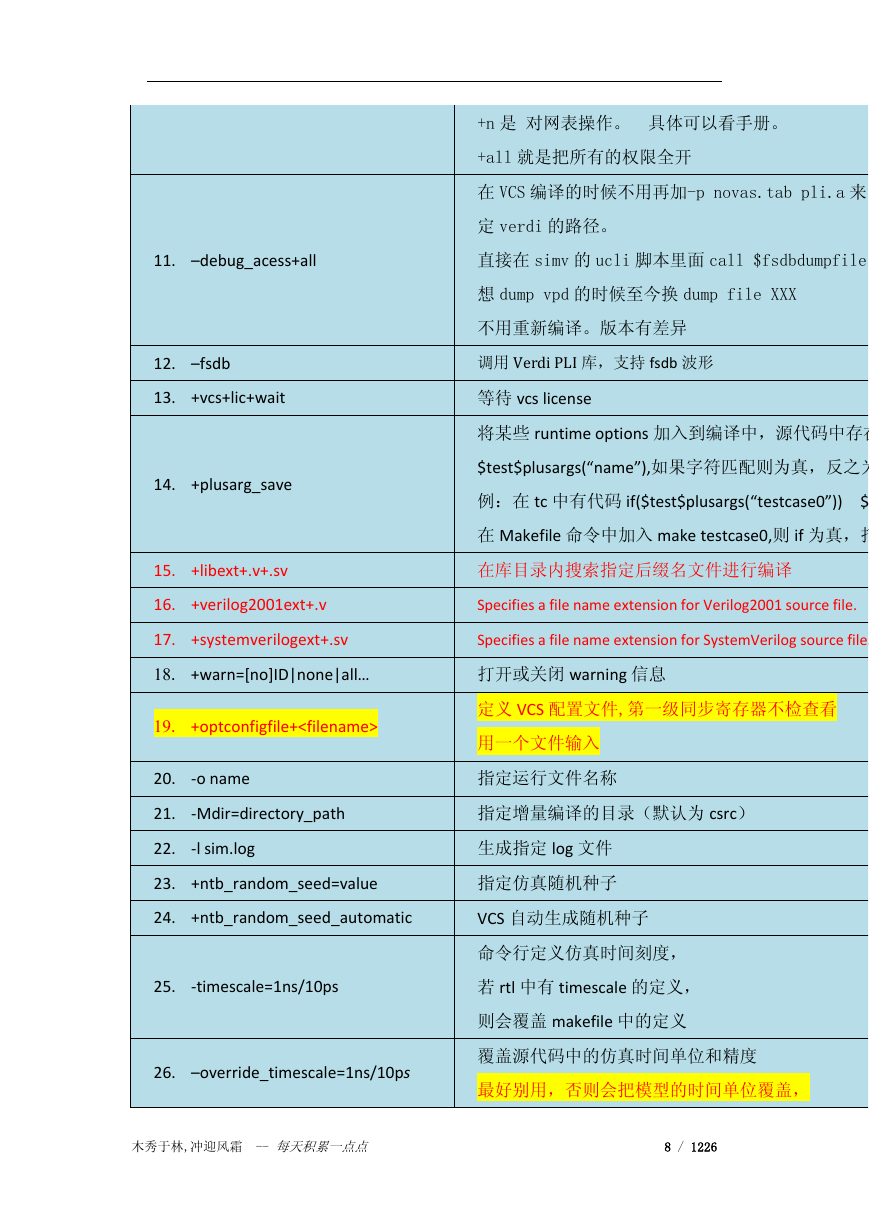

+n 是 对网表操作。 具体可以看手册。

+all 就是把所有的权限全开

在 VCS 编译的时候不用再加-p novas.tab pli.a 来 dump fsdb,指

定 verdi 的路径。

11. –debug_acess+all

直接在 simv 的 ucli 脚本里面 call $fsdbdumpfile

想 dump vpd 的时候至今换 dump file XXX

12. –fsdb

13. +vcs+lic+wait

14. +plusarg_save

不用重新编译。版本有差异

调用VerdiPLI 库,支持 fsdb 波形

等待 vcs license

将某些 runtime options 加入到编译中,源代码中存在系统命令

$test$plusargs(“name”),如果字符匹配则为真,反之为假

例:在 tc 中有代码 if($test$plusargs(“testcase0”)) $display("OK");

在 Makefile 命令中加入 make testcase0,则 if 为真,打印 OK 字符

15. +libext+.v+.sv

16. +verilog2001ext+.v

在库目录内搜索指定后缀名文件进行编译

Specifies a file name extension for Verilog2001 source file.

17. +systemverilogext+.sv

Specifies a file name extension for SystemVerilog source file.

18. +warn=[no]ID|none|all…

打开或关闭 warning 信息

19. +optconfigfile+

20.

-o name

定义 VCS 配置文件,第一级同步寄存器不检查看

用一个文件输入

指定运行文件名称

21.

-Mdir=directory_path

指定增量编译的目录(默认为 csrc)

22.

-l sim.log

生成指定 log 文件

23. +ntb_random_seed=value

指定仿真随机种子

24. +ntb_random_seed_automatic

VCS 自动生成随机种子

25.

-timescale=1ns/10ps

若 rtl 中有 timescale 的定义,

命令行定义仿真时间刻度,

26. –override_timescale=1ns/10ps

则会覆盖 makefile 中的定义

覆盖源代码中的仿真时间单位和精度

最好别用,否则会把模型的时间单位覆盖,

木秀于林,冲迎风霜 -- 每天积累一点点

8 / 1226

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc