第 2 章 思考与习题参考答案

性能指标参数

2-1 简述微处理器的主要性能指标,性能公式(2-1)说明了什么?

答:微处理器的主要性能指标如下表所示

含义

内部处理二进制数的位数

处理器核心工作频率

外部总线的核心频率(基准频率)

前端总线频率

处理器核心工作电压

指管子之间的最小线距

处理器外部地址线条数,决定物理地址空间 2m

处理器外部数据线条数,决定对外访问能力

是否内置协处理器,性能如何

流水线级数

多条指令流水线,含流水线级数

一级/二级/三级高速缓存

单指令处理多个数据的能力

处理器采用的核心架构类型

反应处理器消耗的功率

功耗=动态电容×电压×电压×频率

字长

主频

外频

FSB 频率

工作电压

制造工艺

地址线宽度

数据线宽度

协处理器

流水线技术

超标量结构

L1/L2/L3 Cache

SIMD

核心架构

功耗

示例

8,16,32,64

100MHz,3.2GHz

33MHz,66MHz,100MHz

266MHz,533MHz,800MHz,1330MHz

5V,3V,1.8V,1.2V

0.13μm,90nm,65nm,45nm

20,32,36

8 位,16 位,32 位,64 位

X87

5 级,12 级,14 级,20 级,31 级等

1 个,2 个,3 个,4 个,8 个

8KB,16KB,512KB,4MB

MMX,SSE,SSE2,SSE3,SSSE3,SSE4

P5,P6,NetBurst,Core

50W,25W 等

公式(2-1): 性能=核心频率×每个周期执行指令的条数

说明,微处理器的性能的提高不仅取决于工作频率,还依赖每周期执行指令的条数。新的处理器

代替老的处理器,就是根据这一性能公式来提高它的性能的。即或单独提高频率,或单独增加每周期

执行指令的条数,或既提高频率又增加每周期执行指令的条数。由于核心频率的提高是有限制的,因

此从 Cure 系列开始注重提高每个周期指令执行的条数来提高性能。

思考与习题参考答案

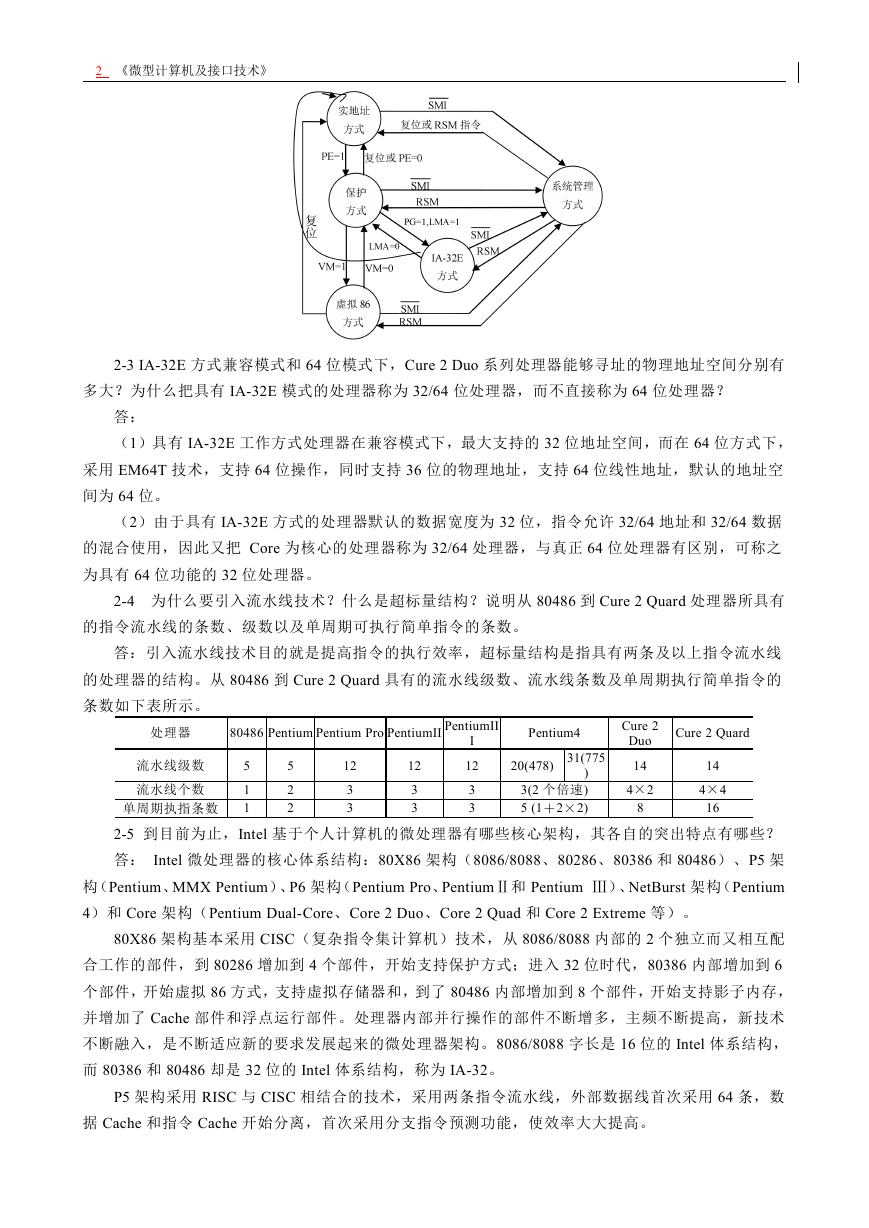

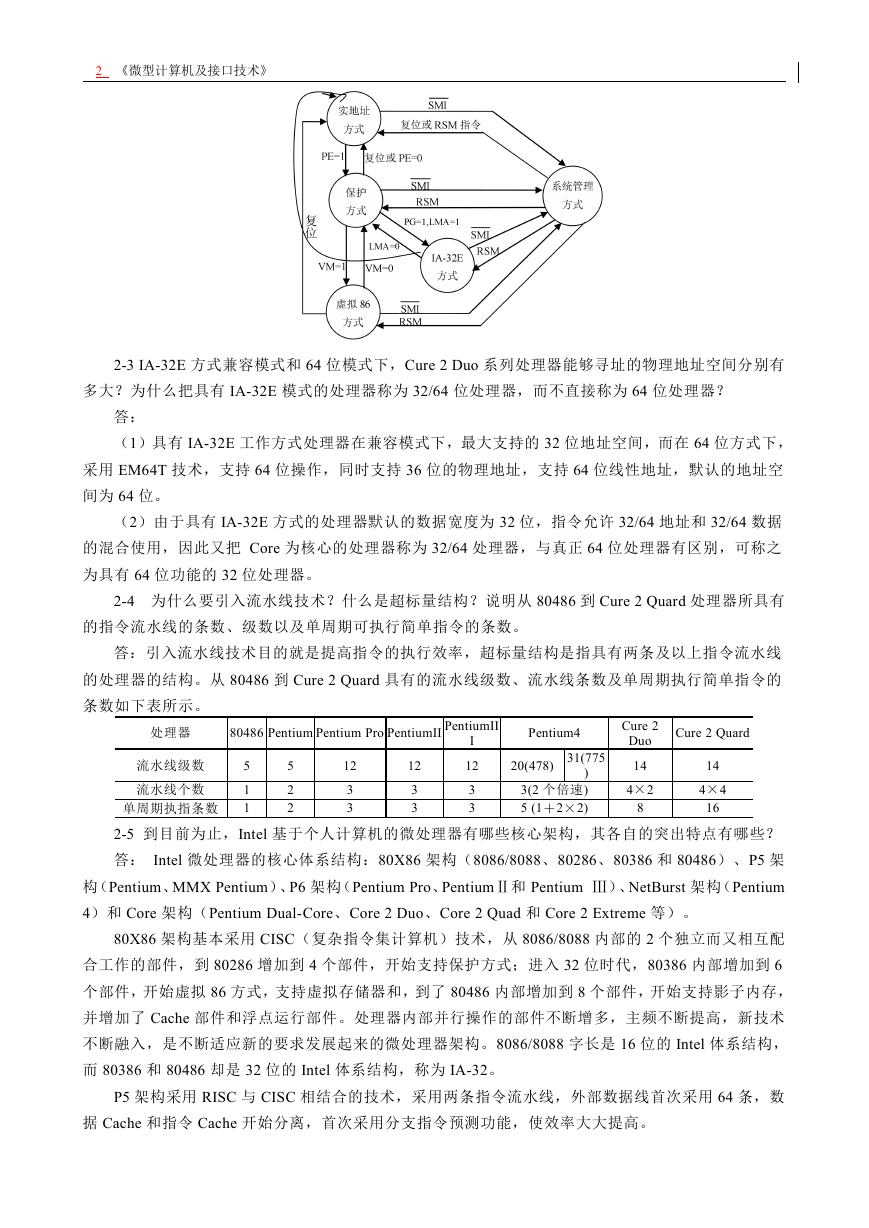

2-2 简述微处理器的工作方式、各工作方式的含义和区别是什么?它们之间是如何切换的?

答:

1.五种工作方式:实地址方式、保护虚地址方式、虚拟 86 方式、系统管理方式以及 IA-32E 方式。

2.含义:

(1)实地址方式是指处理器工作在 8086/8088 编程环境下的工作方式。

(2)保护地址方式,又称保护虚地址方式,简称保护方式,是真正发挥处理器潜能的一种工作方式。

所谓保护是指在执行多任务操作时,对不同任务使用的不同存储空间进行完全隔离,保护每个任务顺

利执行。

(3)虚拟 86 方式是指一个多任务的环境,即模拟多个 8086 的工作方式。在这个方式之下,处理器

被模拟成多个 8086 微处理器同时工作。

(4) 系统管理方式(SMM)是为实现特定功能及系统安全提供的一种工作方式,SMM 的功能主要

包括电源管理以及为操作系统和正在运行的程序提供安全性。SMM 最显著的应用就是电源管理。

以上四种方式是 IA-32 所有处理器所具有的工作方式。

(5)从后期的 P4 到以 Core 为核心的处理器开始支持 64 位扩展技术,引入了 IA-32E 工作方式。在

这种方式下,处理器支持两种模式即兼容的工作方式(兼容 IA-32 处理器的方式)和 64 位工作方式。

在兼容模式下,允许在 64 位操作系统下运行原来的 16 位和 32 位应用程序,采用 EM64T 技术,支持

64 位操作,同时支持 36 位的地址,支持 64 位线性地址,默认的地址空间为 64 位,默认的数据宽度

为 32 位,指令允许 32/64 地址和 32/64 数据的混合使用,因此又把 Core 为核心的处理器称为 32/64

处理器,与真正 64 位处理器有区别,可称之为具有 64 位功能的 32 位处理器。

3.工作方式的相互转换如下图所示。

�

2 《微型计算机及接口技术》

2-3 IA-32E 方式兼容模式和 64 位模式下,Cure 2 Duo 系列处理器能够寻址的物理地址空间分别有

多大?为什么把具有 IA-32E 模式的处理器称为 32/64 位处理器,而不直接称为 64 位处理器?

答:

(1)具有 IA-32E 工作方式处理器在兼容模式下,最大支持的 32 位地址空间,而在 64 位方式下,

采用 EM64T 技术,支持 64 位操作,同时支持 36 位的物理地址,支持 64 位线性地址,默认的地址空

间为 64 位。

(2)由于具有 IA-32E 方式的处理器默认的数据宽度为 32 位,指令允许 32/64 地址和 32/64 数据

的混合使用,因此又把 Core 为核心的处理器称为 32/64 处理器,与真正 64 位处理器有区别,可称之

为具有 64 位功能的 32 位处理器。

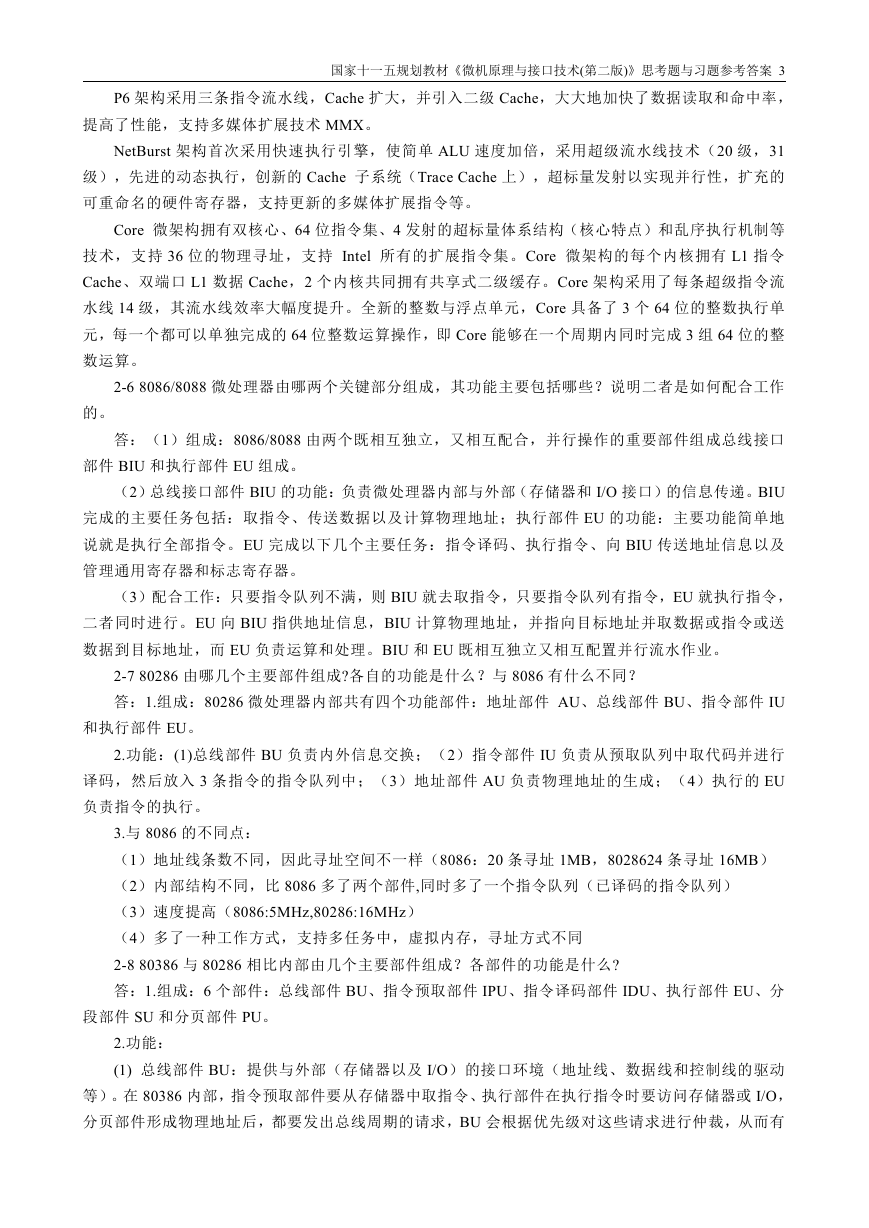

2-4 为什么要引入流水线技术?什么是超标量结构?说明从 80486 到 Cure 2 Quard 处理器所具有

的指令流水线的条数、级数以及单周期可执行简单指令的条数。

答:引入流水线技术目的就是提高指令的执行效率,超标量结构是指具有两条及以上指令流水线

的处理器的结构。从 80486 到 Cure 2 Quard 具有的流水线级数、流水线条数及单周期执行简单指令的

条数如下表所示。

处理器

80486 Pentium Pentium Pro PentiumII PentiumII

Pentium4

Cure 2 Quard

20(478)

31(775

5

2

2

12

3

3

流水线级数

流水线个数

5

1

单周期执指条数 1

2-5 到目前为止,Intel 基于个人计算机的微处理器有哪些核心架构,其各自的突出特点有哪些?

答: Intel 微处理器的核心体系结构:80X86 架构(8086/8088、80286、80386 和 80486)、P5 架

构(Pentium、MMX Pentium)、P6 架构(Pentium Pro、PentiumⅡ和 Pentium Ⅲ)、NetBurst 架构(Pentium

4)和 Core 架构(Pentium Dual-Core、Core 2 Duo、Core 2 Quad 和 Core 2 Extreme 等)。

)

3(2 个倍速)

5 (1+2×2)

14

4×4

16

12

3

3

80X86 架构基本采用 CISC(复杂指令集计算机)技术,从 8086/8088 内部的 2 个独立而又相互配

合工作的部件,到 80286 增加到 4 个部件,开始支持保护方式;进入 32 位时代,80386 内部增加到 6

个部件,开始虚拟 86 方式,支持虚拟存储器和,到了 80486 内部增加到 8 个部件,开始支持影子内存,

并增加了 Cache 部件和浮点运行部件。处理器内部并行操作的部件不断增多,主频不断提高,新技术

不断融入,是不断适应新的要求发展起来的微处理器架构。8086/8088 字长是 16 位的 Intel 体系结构,

而 80386 和 80486 却是 32 位的 Intel 体系结构,称为 IA-32。

P5 架构采用 RISC 与 CISC 相结合的技术,采用两条指令流水线,外部数据线首次采用 64 条,数

据 Cache 和指令 Cache 开始分离,首次采用分支指令预测功能,使效率大大提高。

I

12

3

3

Cure 2

Duo

14

4×2

8

�

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案 3

P6 架构采用三条指令流水线,Cache 扩大,并引入二级 Cache,大大地加快了数据读取和命中率,

提高了性能,支持多媒体扩展技术 MMX。

NetBurst 架构首次采用快速执行引擎,使简单 ALU 速度加倍,采用超级流水线技术(20 级,31

级),先进的动态执行,创新的 Cache 子系统(Trace Cache 上),超标量发射以实现并行性,扩充的

可重命名的硬件寄存器,支持更新的多媒体扩展指令等。

Core 微架构拥有双核心、64 位指令集、4 发射的超标量体系结构(核心特点)和乱序执行机制等

技术,支持 36 位的物理寻址,支持 Intel 所有的扩展指令集。Core 微架构的每个内核拥有 L1 指令

Cache、双端口 L1 数据 Cache,2 个内核共同拥有共享式二级缓存。Core 架构采用了每条超级指令流

水线 14 级,其流水线效率大幅度提升。全新的整数与浮点单元,Core 具备了 3 个 64 位的整数执行单

元,每一个都可以单独完成的 64 位整数运算操作,即 Core 能够在一个周期内同时完成 3 组 64 位的整

数运算。

2-6 8086/8088 微处理器由哪两个关键部分组成,其功能主要包括哪些?说明二者是如何配合工作

的。

答:(1)组成:8086/8088 由两个既相互独立,又相互配合,并行操作的重要部件组成总线接口

部件 BIU 和执行部件 EU 组成。

(2)总线接口部件 BIU 的功能:负责微处理器内部与外部(存储器和 I/O 接口)的信息传递。BIU

完成的主要任务包括:取指令、传送数据以及计算物理地址;执行部件 EU 的功能:主要功能简单地

说就是执行全部指令。EU 完成以下几个主要任务:指令译码、执行指令、向 BIU 传送地址信息以及

管理通用寄存器和标志寄存器。

(3)配合工作:只要指令队列不满,则 BIU 就去取指令,只要指令队列有指令,EU 就执行指令,

二者同时进行。EU 向 BIU 指供地址信息,BIU 计算物理地址,并指向目标地址并取数据或指令或送

数据到目标地址,而 EU 负责运算和处理。BIU 和 EU 既相互独立又相互配置并行流水作业。

2-7 80286 由哪几个主要部件组成?各自的功能是什么?与 8086 有什么不同?

答:1.组成:80286 微处理器内部共有四个功能部件:地址部件 AU、总线部件 BU、指令部件 IU

和执行部件 EU。

2.功能:(1)总线部件 BU 负责内外信息交换;(2)指令部件 IU 负责从预取队列中取代码并进行

译码,然后放入 3 条指令的指令队列中;(3)地址部件 AU 负责物理地址的生成;(4)执行的 EU

负责指令的执行。

3.与 8086 的不同点:

(1)地址线条数不同,因此寻址空间不一样(8086:20 条寻址 1MB,8028624 条寻址 16MB)

(2)内部结构不同,比 8086 多了两个部件,同时多了一个指令队列(已译码的指令队列)

(3)速度提高(8086:5MHz,80286:16MHz)

(4)多了一种工作方式,支持多任务中,虚拟内存,寻址方式不同

2-8 80386 与 80286 相比内部由几个主要部件组成?各部件的功能是什么?

答:1.组成:6 个部件:总线部件 BU、指令预取部件 IPU、指令译码部件 IDU、执行部件 EU、分

段部件 SU 和分页部件 PU。

2.功能:

(1) 总线部件 BU:提供与外部(存储器以及 I/O)的接口环境(地址线、数据线和控制线的驱动

等)。在 80386 内部,指令预取部件要从存储器中取指令、执行部件在执行指令时要访问存储器或 I/O,

分页部件形成物理地址后,都要发出总线周期的请求,BU 会根据优先级对这些请求进行仲裁,从而有

�

4 《微型计算机及接口技术》

序地服务于多个请求,并产生相应的总线操作所需要的信号,包括地址信号、读/写控制信号等。BU

还提供了与协处理器如 80387 或 80287 的接口。

(2)指令预取部件 IPU 通过 BU 按顺序向存储器取指令并放到 16 个字节的预取指令队中,为指

令译码部件提供有效的指令。

(3)指令译码部件 IDU 从预取指令队列中取出原代码后进行译码,并将译码好的指令存放在 3

条指令的队列中,送给执行部件。

(4)执行部件 EU 包括 ALU 以及 64 位的桶形移位寄存器和 8 个 32 位的通用寄存器及保护检测

电路等,EU 从 IDU 中取出已译码的指令后,立即通过控制电路产生各种控制信号送到内部各个部件,

从而执行了该指令。在执行指令的过程中,向分段部件发出逻辑地址信息,并通过 BU 与外部交换数

据。

(5)分段部件 SU 将 EU 送来的两路 32 位有效地址(包括逻辑地址 48 位:16 位选择子和 32 位段

内偏移地址)通过描述符的数据结构形成 32 位的线性地址。

(6)分页部件 PU 接收到线性地址后,通过两次页转换将其变换为实际的 32 位物理地址。

2-9 简述 P5 架构的 Pentium 处理器的结构特点。

答:(1) 与 80X86 系列微处理器兼容

(2) RISC 型超标量结构:两条指令流水线(U+V)

(3) 高性能的浮点运算器

(4) 双重分离式高速缓存:将指令高速缓存与数据高速缓存分离,各自拥有独立的 8KB 高速缓存,

使其能全速执行,减少等待及传送数据时间。

(5) 增强了错误检测与报告功能:内部增强了错误检测与报告功能,特别引进了在片功能冗余检测

(FRC),并采用了一种能降低出错的六晶体管存储单元。

(6) 64 位数据总线:使用 64 位的数据总线(80386/80486 为 32 位)。

(7) 分支指令预测:处理器内部采用了分支预测的技术,大大提高了流水线执行效率。

(8) 常用指令固化及微代码改进

(9) 系统管理方式:在实地址方式、保护方式、虚拟 86 方式的基础上,增加了 SMM(系统管理

方式)。

2-10 Pentium 处理器的U和V两条指令流水线的功能是什么?主频为 100MHz 的 Pentium 处理器,

最快执行两条指令的时间为多少 ns?

答:(1)U 流水线主要用于执行复杂指令,而 V 流水线只能执行简单指令。

(2)最快执行两条指令的时间是一个时钟周期,100MHz 主频其一个时钟周期为 1/100 (us)=10ns。

2-11 简述 Pentium 处理器的 BTB 的功能。

答:BTB(分支目标缓冲器)可对分支指令进行预测,目的是提高流水线执行效率。在 Pentium

微处理器中,使用了 BTB 预测分支指令,这样可在分支指令进入指令流水线之前预先安排指令的顺序,

而不致使指令流水线的执行产生停滞或混乱。

2-12 简述 P6 架构的处理器的主要特点,基于该架构的 PentiumII 和 PentiumIII 特点如何?

答:1.架构的主要特点如下:

(1)三条超标量指令流水线,每条 12 级超流水线(细分也可认为 14 级),使一个时钟周期内可

同时执行三条简单指令。

(2) 5 个并行处理单元:两个整数运算部件,一个装入,一个存储,1 个浮点运算部件(FPU)。

(3)8KB 两路相关指令高速缓存,8KB 四路相关数据高速缓存。

�

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案 5

(4)专用全速总线上的二级高速缓存与微处理器紧密相联。

(5)事务处理 I/O 总线和非封锁高速缓存分级结构。

(6)错序执行,动态分支预测和推理执行。

2. Pentium II 处理器的显著特点有:

(1)双重独立总线(DIB)体系结构

能同时使用具有纠错功能的 64 位系统总线和具有可选纠错功能的 64 位 Cache 总线。

(2)多重跳转分支预测

通过多条分支预测程序执行,加快了工作向处理器的流动。

(3)数据流分析

分析并重排指令,使指令以优化的顺序执行,与原始程序的顺序无关。

(4)指令推测执行

通过预先查看程序计数器 PC 并执行那些将要执行的指令,提高了速率。

(5)采用 Intel MMX 技术

包括了 57 条增强的 MMX 指令技术,可处理视频、声频及图像数据。

Penitum Ⅲ与 Pentium Ⅱ相比,主要参数特点如下:

(1)主频 450MH 以上到 1.1GHz

(2)总线频率 100MHz/133MHz

(3)新增加 70 条 SSE 指令

(4)2.0V 供电,0.25 到 0.18 微米工艺制造

(5)32KB 的 L1 以主频速度工作,512KB 的 L2 以主频一半速度工作

2-15 Pentium 4 处理器,一个时钟周期内可执行多少条简单?如果 3.0GHz 的 Pentium 4 执行 9 条简

单指令,最快需要多长时间执行完?

答:P4 内部有一个复杂指令流水线和两个快速流水线,快速流水线倍速工作,因此每个时钟可执

行 5 条简单指令。3GHz 对应的周期为 1/3ns,9*1/3=3ns 即 9 条指令最短可在 3ns 内执行完毕。

2-17 一个典型的 Cure 2 Duo 处理器一个时钟可以执行多少条简单指令?2.0GHz 的 Cure 2 Duo 处

理器在 1ns 内最快能执行多少条简单指令?

答:由于 Cure 2 Duo 是典型的双核处理器,每个内核有 4 个译码器和相关执行单元,即有 4 条指

令流水线,因此,单一时钟可执行简单指令 4×2=8 条;时钟频率 2GHz 即时钟周期为 0.5ns,即要 0.5ns

内可执行简单指令 8 条,1ns/0.5ns×8=16 条,即 2GHz 的 Cure 2 Duo 可在 1ns 内指行 16 条简单指令。

2-18 总结一下 8086/8088 到 Cure 2 Duo 处理器外部地址线、数据线条数、通用寄存器的位数以及

所处的工作方式。各自的位长以及所能寻址的物理地址空间有多大?

答:从 8086 到 Cure 2 Duo 的相关参数如下表所示表。

�

6 《微型计算机及接口技术》

2-20 通过复位后寄存器的特点,说明各处理器复位后程序第一条指令存放的地址。

答:复位后 16 位处理器 8086/8088 以及 80286 系统复位后内部除 CS=FFFFH 外,其余各寄存器全

为 0,段的起始地址为段寄存器的内容左移 4 位,因此复位后第一条指令的地址 FFFF0H(CS×16+IP)。

IA-32 处理器复位后内部地址相关寄存器的状态为:EIP=0000FFF0H,CS=F000H,CS.BASE(代码

段 基 地 址 ) = FFFF0000H , SS = DS =ES =FS = GS = 0000H , 其 它 段 的 段 基 地 址 均 为 0 , GDTR =

00000000FFFFH,IDTR=00000000FFFFH。即 GDTR 和 IDTR 描述的基地址全为 0,界限均为 FFFFH。

LDTR=0,对应的基地址为 0,界限为 FFFFH,

IA-32 处理器复位后的第一条指令的地址为=段基地址+偏移地址=FFFF0000 + FFF0H =

FFFFFFF0H。

即 8086~80286 复位地址 FFFF0H,80386~Cure 2 Duo 复位地址为 FFFFFFF0H。

2-22 IA-32 处理器的 CR0、CR2、CR3 和 CR4 的名称及功能是什么?CR0 中与寻址有关的控制位

有哪些?CR4 中对于具有 36 条地址线的处理器有哪里相关控制位?

答:(1)控制寄存器名称及功能如下表所示

标识

名称

CR0 机器状态寄存器

CR2 页故障地址寄存器

功能

存放处理器的状态和控制位,决定处理器的工作模式

保存着发生页故障,产生异常中断之前所访问的最后一个页的线性地

址。

CR3 页目录表基址寄存器

保存着页目录表的物理基地址及两个属性

CR4 扩展控制寄存器 CR4(从 Pentium 开始)

包括了几个结构的扩展并指示对特殊处理器性能的支持,36 位物理地

址及不同而大小的支持等

(2)CR0 与寻址有关的主要控制位有 CR0.0(PE)保护允许,CR0.31(PG)分页允许

CR4 中与 36 位地址相关的控制位有:CR4.5(PAE)页地址扩展,对于基于 36 位地址的处理器,

PAE=1 允许使用 36 位地址,访问 64GB 的存储空间,PAE=0 只有访问使用 32 位地址线,寻址 4GB;

CR4.7(PGE)页全局允许,针对基于 36 条地址线的处理器(P6 开始引入)的页全局允许,PGE=1

允许全局页特征,PGE=0 禁止全局页特征;

2-26 已经从内存 1FF00000 开始存放 12H, 34H, 56H, 78H, 90H, ABH, CDH, EFH, 11H, 22H, 33H,

44H, 55H, 66H, 77H, 88H,99H,00H,AAH,BBH,CCH,DDH,EEH,FFH,试说明从 1FF00000H 开始取一个

双四字的值,从 1FF00008H 开始取双字的值,以及从 1F00010H 开始取四字和一个字的值。

解:从 1FF00000H 开始的双四字的值=8877665544332211EFCDAB9078563412H

从 1FF00008H 开始的双字的值=44332211H

从 1FF00010H 开始的四字的值=FFEEDDCCBBAA0099H

从 1FF00010H 开始的一个字的值=0099H

2-28 对于 8086 最小模式填写下列表格

DT / R M / IO

0

0

1

1

0

1

0

1

RD

0

0

1

1

WR

1

1

0

0

指令示例

IN AL,DX

对应的操作

读 I/O 接口

MOV AL,[SI]

读存储器

写 I/O 接口 OUT DX,AL

写存储器 MOV [DI],AL

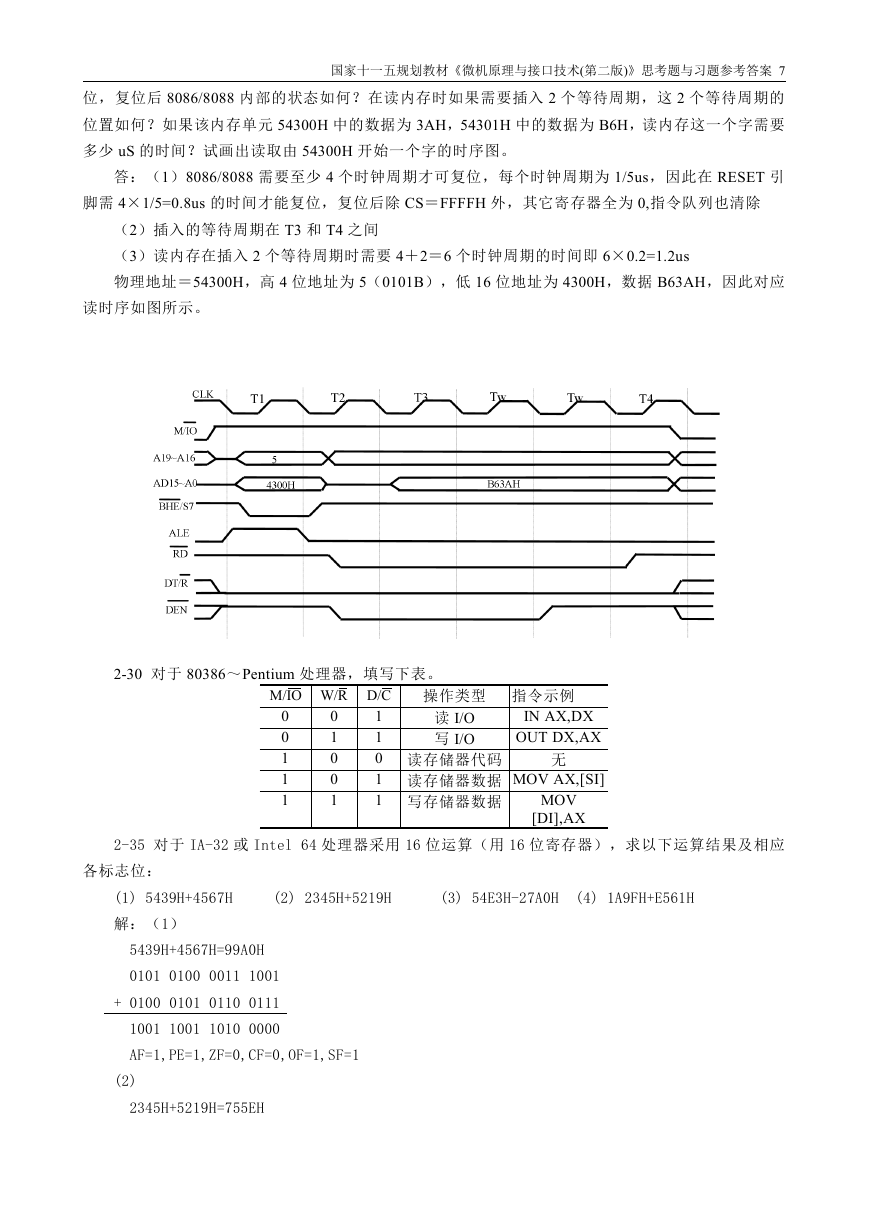

2-29 8086/8088 的外部时钟接 5MHz,试问在 RESET 引脚需要多少 uS 时间的高电平,系统才能复

�

国家十一五规划教材《微机原理与接口技术(第二版)》思考题与习题参考答案 7

位,复位后 8086/8088 内部的状态如何?在读内存时如果需要插入 2 个等待周期,这 2 个等待周期的

位置如何?如果该内存单元 54300H 中的数据为 3AH,54301H 中的数据为 B6H,读内存这一个字需要

多少 uS 的时间?试画出读取由 54300H 开始一个字的时序图。

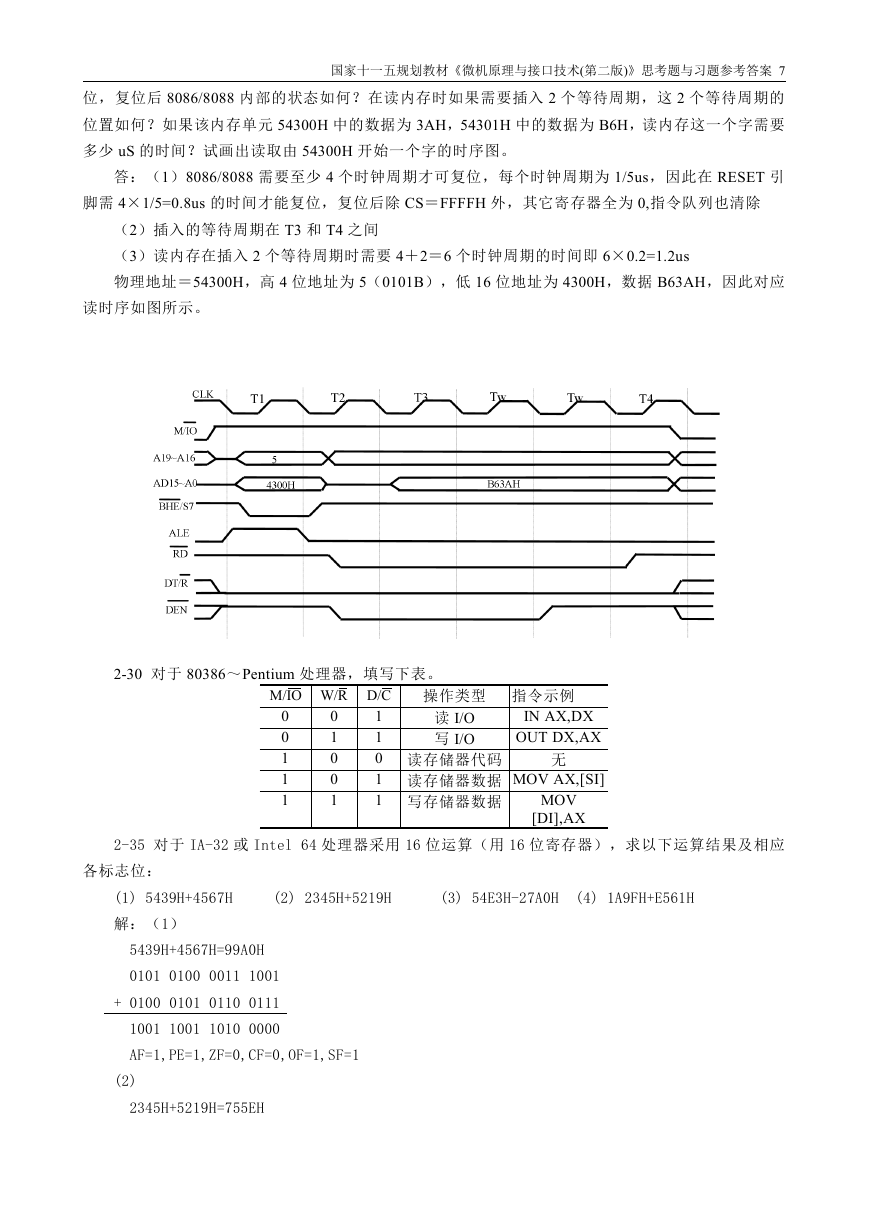

答:(1)8086/8088 需要至少 4 个时钟周期才可复位,每个时钟周期为 1/5us,因此在 RESET 引

脚需 4×1/5=0.8us 的时间才能复位,复位后除 CS=FFFFH 外,其它寄存器全为 0,指令队列也清除

(2)插入的等待周期在 T3 和 T4 之间

(3)读内存在插入 2 个等待周期时需要 4+2=6 个时钟周期的时间即 6×0.2=1.2us

物理地址=54300H,高 4 位地址为 5(0101B),低 16 位地址为 4300H,数据 B63AH,因此对应

读时序如图所示。

2-30 对于 80386~Pentium 处理器,填写下表。

操作类型 指令示例

M/IO W/R D/C

1

1

0 读存储器代码

1 读存储器数据 MOV AX,[SI]

1 写存储器数据

IN AX,DX

OUT DX,AX

读 I/O

写 I/O

0

0

1

1

1

0

1

0

0

1

无

MOV

[DI],AX

2-35 对于 IA-32 或 Intel 64 处理器采用 16 位运算(用 16 位寄存器),求以下运算结果及相应

各标志位:

(1) 5439H+4567H

(2) 2345H+5219H

(3) 54E3H-27A0H

(4) 1A9FH+E561H

解:(1)

5439H+4567H=99A0H

0101 0100 0011 1001

+ 0100 0101 0110 0111

1001 1001 1010 0000

AF=1,PE=1,ZF=0,CF=0,OF=1,SF=1

(2)

2345H+5219H=755EH

�

8 《微型计算机及接口技术》

0010 0011 0100 0101

+ 0101 0010 0001 1001

0111 0101 0101 1110

AF=0,PE=1,ZF=0,CF=0,OF=0,SF=0

(3)法 1 直接相减

54E3H-27A0H=2D43H

0101 0100 1110 0011

- 0010 0111 1010 0000

0010 1101 0100 0011

AF=0,PE=0,ZF=0,CF=0,OF=0,SF=0

法 2 变减为加

54E3H-27A0H=54E3+D860H=2D43H

0101 0100 1110 0011

+ 1101 1000 0110 0000

1 0010 1101 0100 0011

AF=0,PE=0,ZF=0,CF=1,OF=0,SF=0

(4)

1A9FH+E561=0000H

0001 1010 1001 1111

+ 1110 0101 0110 0001

1 0000 0000 0000 0000

AF=1,PE=1,ZF=1,CF=1,OF=0,SF=0

2-36 8086/8088,80386,80486,Pentium,Pentium Pro,Pentium II,Pentium III,Pentium 4,Cure 2

内部通用寄存器的位数、段寄存器的位数、外部地址线和数据线的条数分别为多少?求其寻址范围及带

符号数表示范围。

答:相应参数见下表所示。

2-40 简述段基址、偏移地址、逻辑地址和物理地址的含义及其相互关系。

答:段基址是该段物理地址的起始地址或首地址,偏移地址指的是离段基的偏移量,将存放在段

寄存器中的内容与偏移地址合称为逻辑地址,通常用段寄存器内容:偏移地址表示逻辑地址。在实地址

方式下,逻辑地址包含了段地址(20 位段起始物理地址的高 16 位)和偏移地址,在保护方式下逻辑

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc