课 程 设 计 报 告

学生姓名:

学 院:

班 级:

题 目:

学 号:

电气工程学院

数字电子钟的设计

指导教师:

职称:

教师

2013 年 3 月 15 日

�

一. 设计要求

1、硬件电路设计,包括 TMS320LF2407 基本电路、数码显示电路和基本按键,需

要用 protel 软件完成原理图;

2、软件设计,主要指应用片上定时器作为时钟源编写数字钟程序,数字电子钟

功能要求能调小时、分钟、秒钟,还有随时暂停的功能等,在实验箱上运行调试

成功并能用数码管显示;

3、课程设计报告,包括总体设计方案、硬件电路设计和软件设计的具体说明。

二. 设计方案论证

1、数字时钟选择方案

方案一:本方案采用 Dallas 公司的专用时钟芯片 DS12887A。该芯片内部采

用石英晶体振荡器,其芯片精度不大于 10ms/年,且具有完备的时钟闹钟功能,

因此,可直接对其以用于显示或设置,使得软件编程相对简单。为保证时钟在电

网电压不足或突然掉电等突发情况下仍能正常工作,芯片内部包含锂电池。当电

网电压不足或突然掉电时,系统自动转换到内部锂电池供电系统。而且即使系统

不上电,程序不执行时,锂电池也能保证芯片的正常运行,以备随时提供正确的

时间。

方案二:本方案完全用软件实现数字时钟。原理:利用定时器与软件结合实

现 1 秒定时中断,每产生一次中断,存储器内相应的秒值加 1;若秒值达到 60,

则将其清零,并将相应的分值加 1;若分值达到 60,则清零,并将时值加 1;若

时值达到 24,则清零。该方案具有硬件电路简单的特点。而且,由于是软件实

现,缺点:当 DSP 芯片不上电,程序不执行时,时钟将不工作。

基于硬件电路的考虑,本设计采用方案二完成数字时钟的功能简单方便,容

易操作实现。

2、数码管显示方案

方案一:静态显示。所谓静态显示,就是当显示器显示某一字符时,相应的

发光二极管恒定的导通或截止。该方式每一位都需要一个 8 位输出口控制。静

态显示时较小的电流能获得较高的亮度,且字符不闪烁。但当所显示的位数较多

时,静态显示所需的 I/O 口太多,造成了资源的浪费。

方案二:动态显示。所谓动态显示就是一位一位的轮流点亮各个位,对于显

示器的每一位来说,每隔一段时间点亮一次。利用人的视觉暂留功能可以看到整

个显示,但必须保证扫描速度足够快,字符才不闪烁。显示器的亮度既与导通电

流有关,也于点亮时间与间隔时间的比例有关。调整参数可以实现较高稳定度的

显示。动态显示节省了 I/O 口,降低了能耗。

- 2 -

�

从节省 I/O 口和降低能耗出发,本设计采用方案二,采用数码管动态显示。

三. 设计原理及框图

1、设计原理

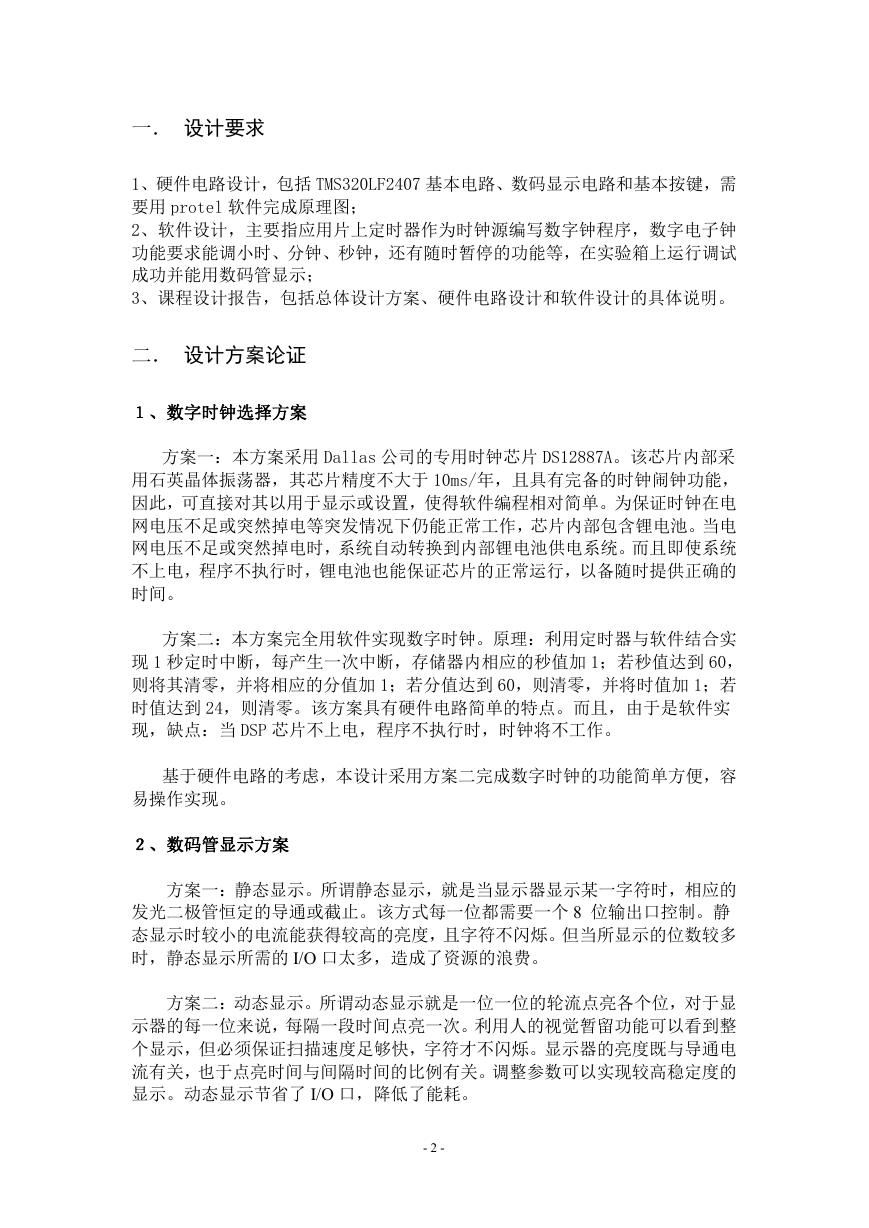

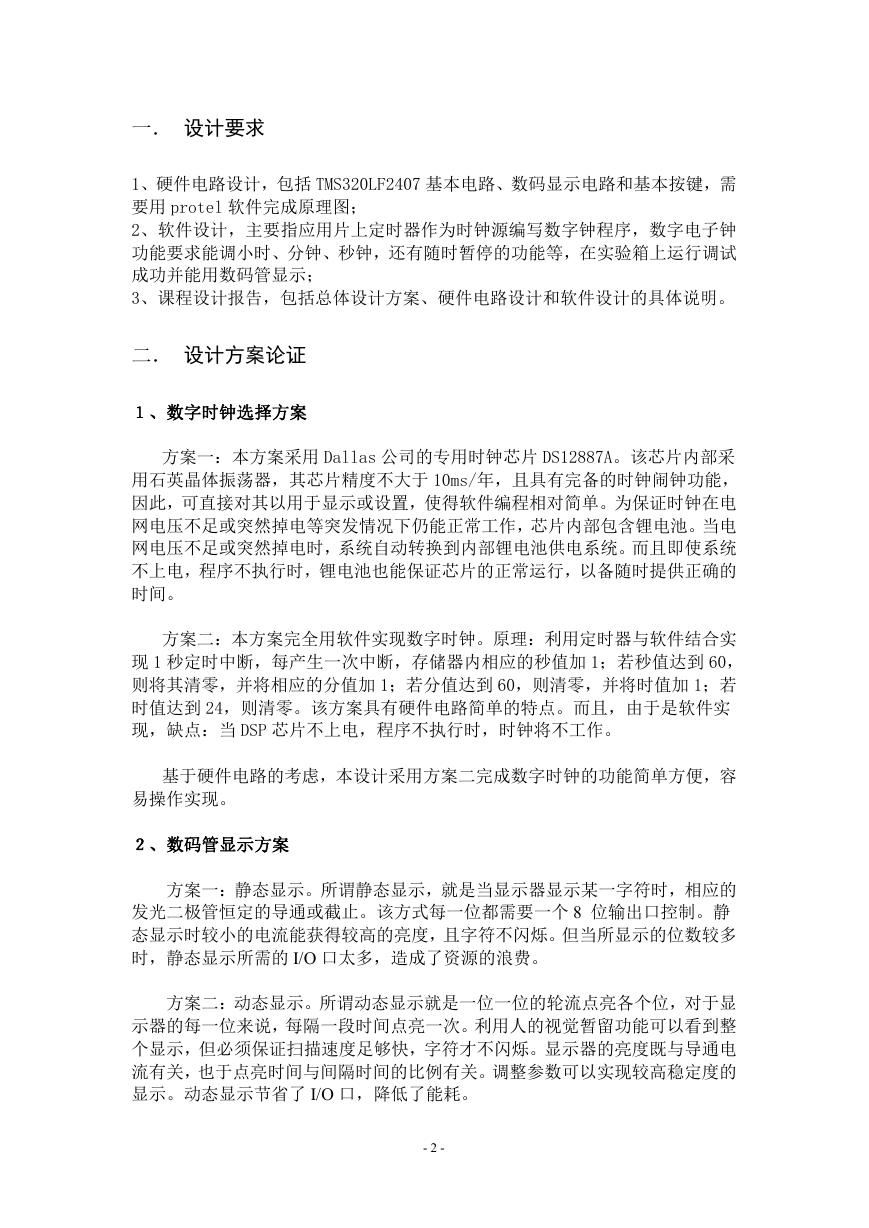

DSP2407 最小系统是整个芯片能正常运行的最基本要求,首先由 DSP 最小系

统的设计包括电源转换电路、锁相环电路、JTAG 接口电路、复位电路等。然后

利用 TMS320LF2407 芯片制作简易电子时钟,利用芯片上的定时器编写1ms

的时间子程序,继而写出主函数程序。总的模块由六个 LED 数码管显示、四个

按键调试时间、数码管驱动模块 74HC273 及数码管位选模块 74HC138 构成。

数 码 管 驱

动电路

芯片

TMS320LF2407

数 码 管 显

示电路

数 码 管 位 选

电路

2、框图

PLL 锁 相 环

电路

复位电路

按 键 控 制

电路

电 压 转 换

模块

四. 器件说明

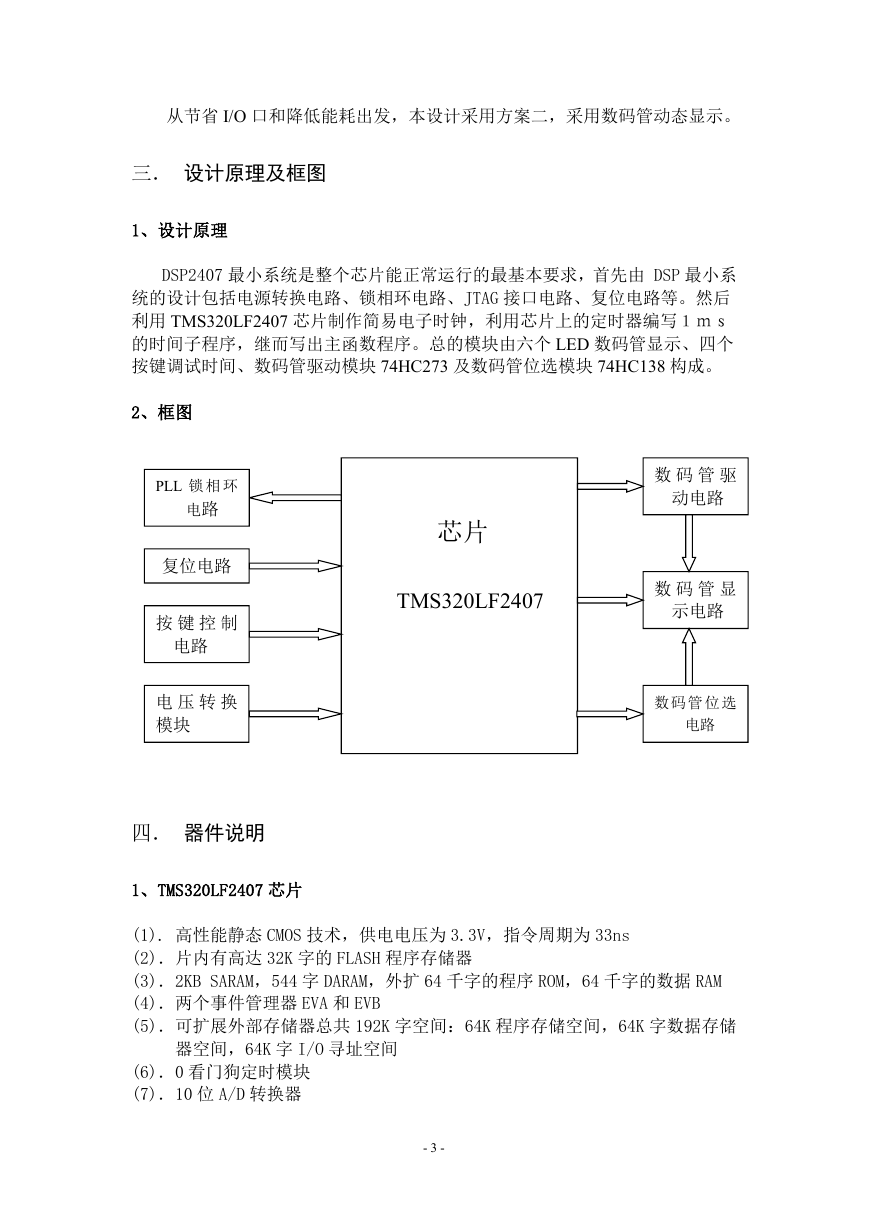

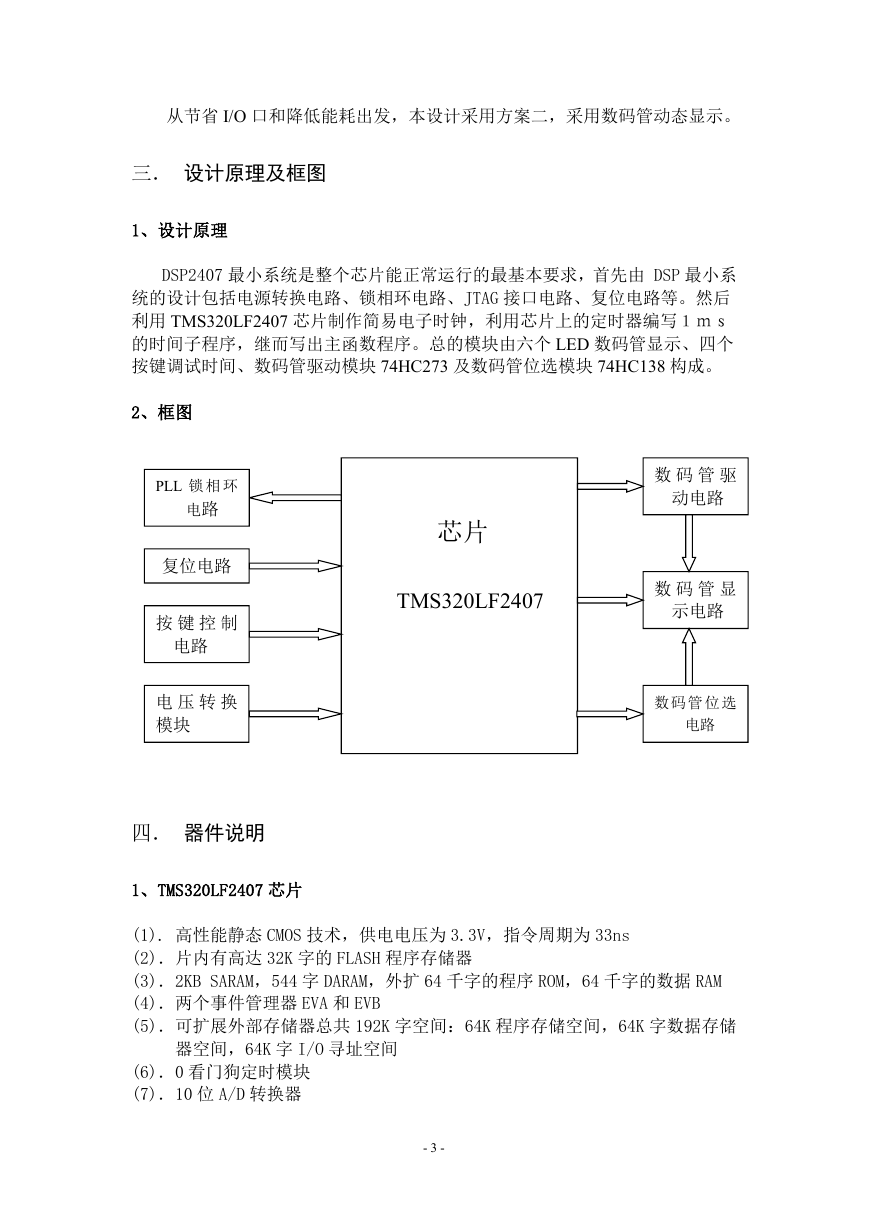

1、TMS320LF2407 芯片

(1). 高性能静态 CMOS 技术,供电电压为 3.3V,指令周期为 33ns

(2).片内有高达 32K 字的 FLASH 程序存储器

(3).2KB SARAM,544 字 DARAM,外扩 64 千字的程序 ROM,64 千字的数据 RAM

(4).两个事件管理器 EVA 和 EVB

(5).可扩展外部存储器总共 192K 字空间:64K 程序存储空间,64K 字数据存储

器空间,64K 字 I/O 寻址空间

(6).0 看门狗定时模块

(7).10 位 A/D 转换器

- 3 -

�

(8).控制局域网络 CAN 模块

(9).串行通信接口 SCI 模块

(10).16 位串行外设 SPI 接口模块

(11).基于锁相环 PLL 的时钟发生器

(12).高达 40 个可单独编程或复用的通用 I/O 引脚

(13).5 个外部中断

(14).电源管理包括 3 种低功耗模式,能独立地将外设器件转入低功耗工作模式

图 1.1 TMS320LF2407

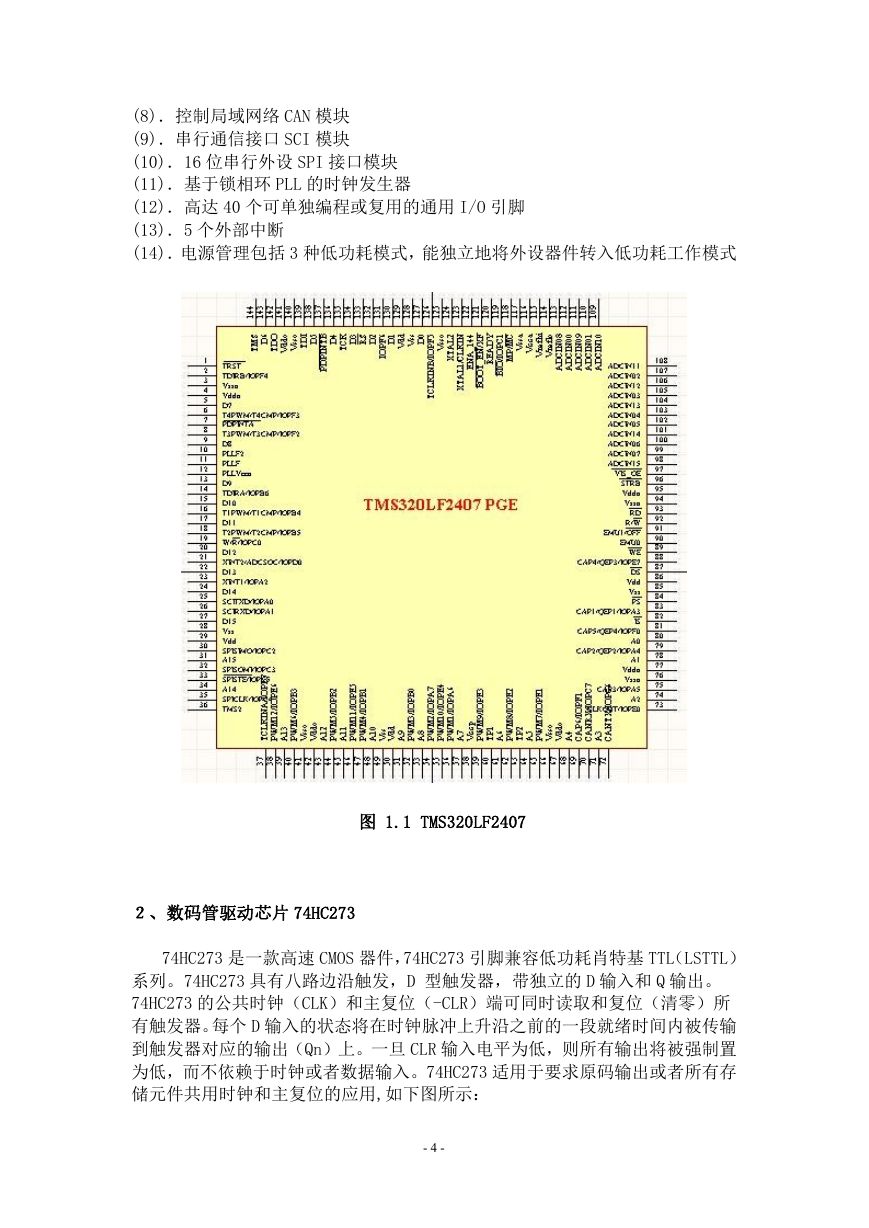

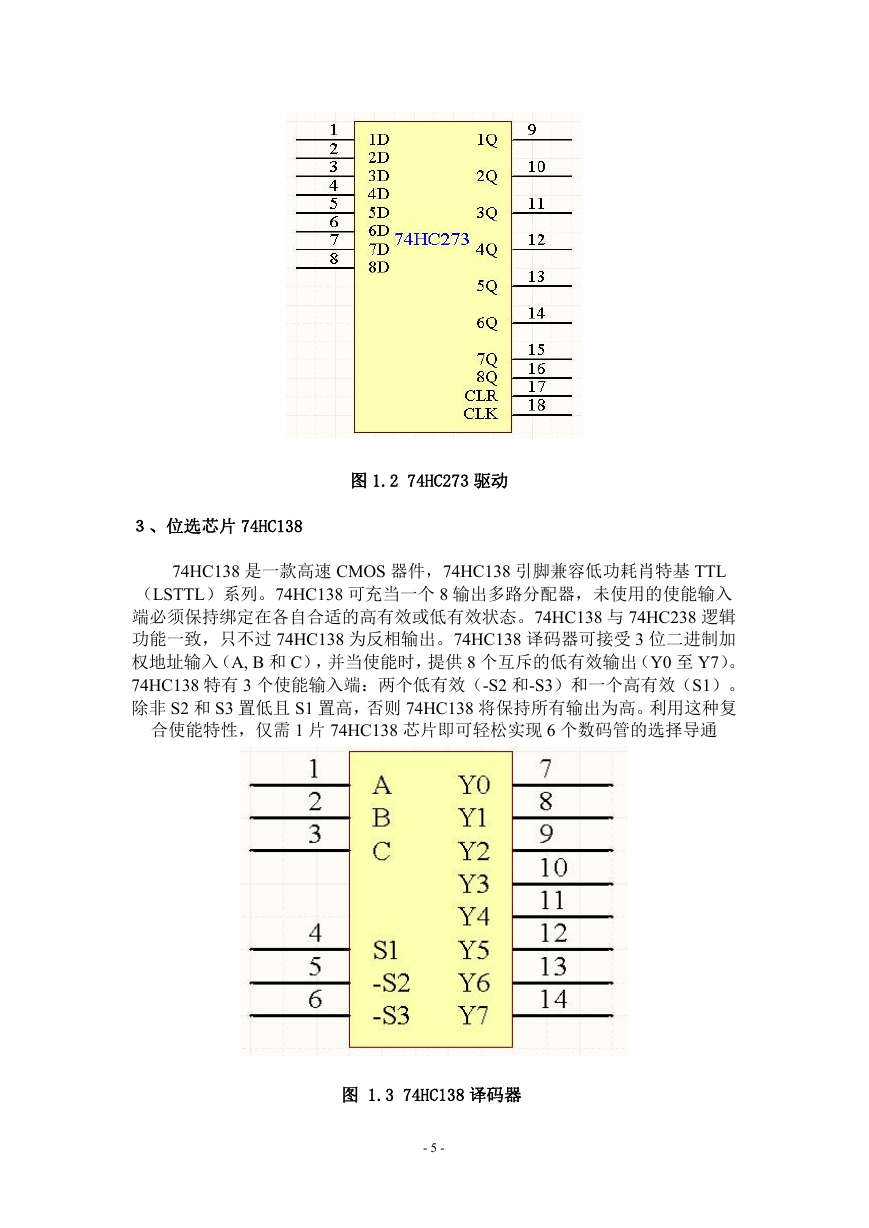

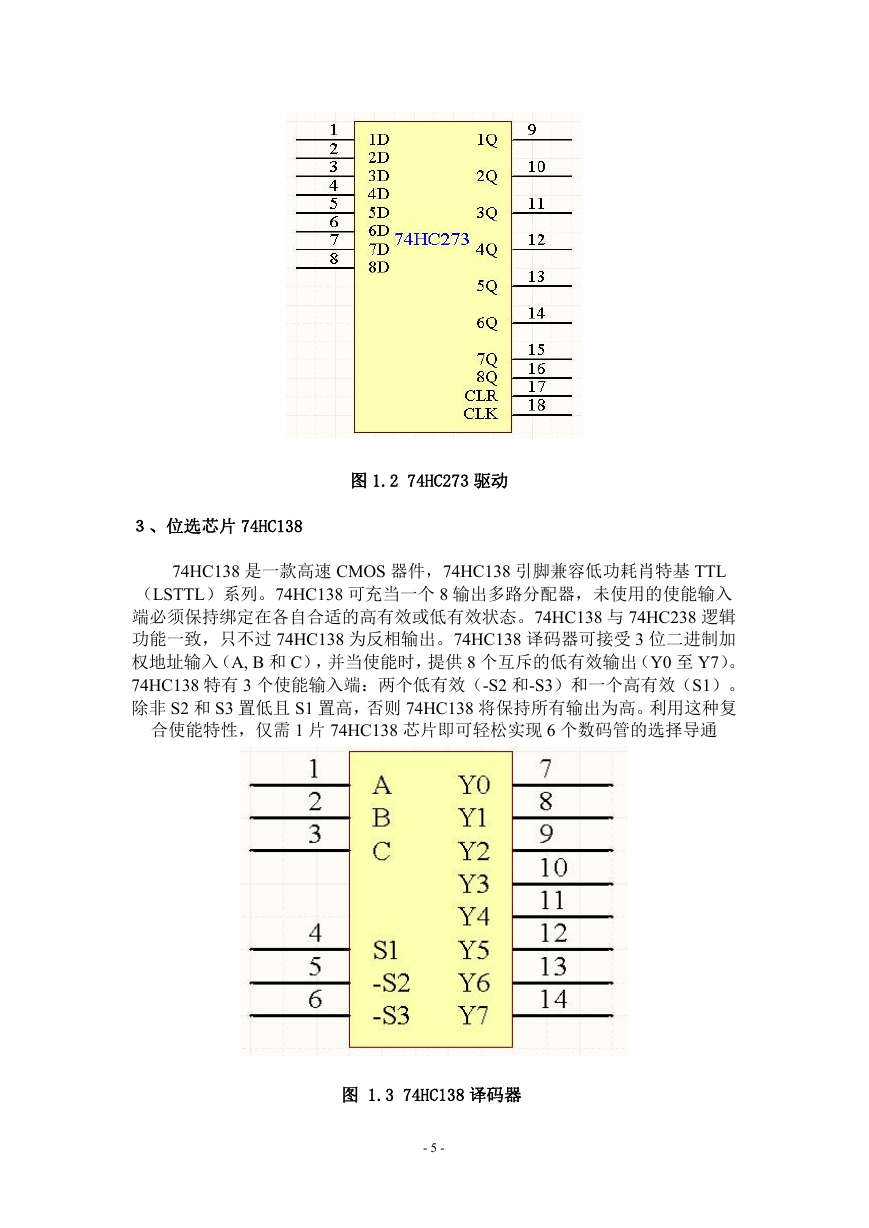

2、数码管驱动芯片 74HC273

74HC273 是一款高速 CMOS 器件,74HC273 引脚兼容低功耗肖特基 TTL(LSTTL)

系列。74HC273 具有八路边沿触发,D 型触发器,带独立的 D 输入和 Q 输出。

74HC273 的公共时钟(CLK)和主复位(-CLR)端可同时读取和复位(清零)所

有触发器。每个 D 输入的状态将在时钟脉冲上升沿之前的一段就绪时间内被传输

到触发器对应的输出(Qn)上。一旦 CLR 输入电平为低,则所有输出将被强制置

为低,而不依赖于时钟或者数据输入。74HC273 适用于要求原码输出或者所有存

储元件共用时钟和主复位的应用,如下图所示:

- 4 -

�

图 1.2 74HC273 驱动

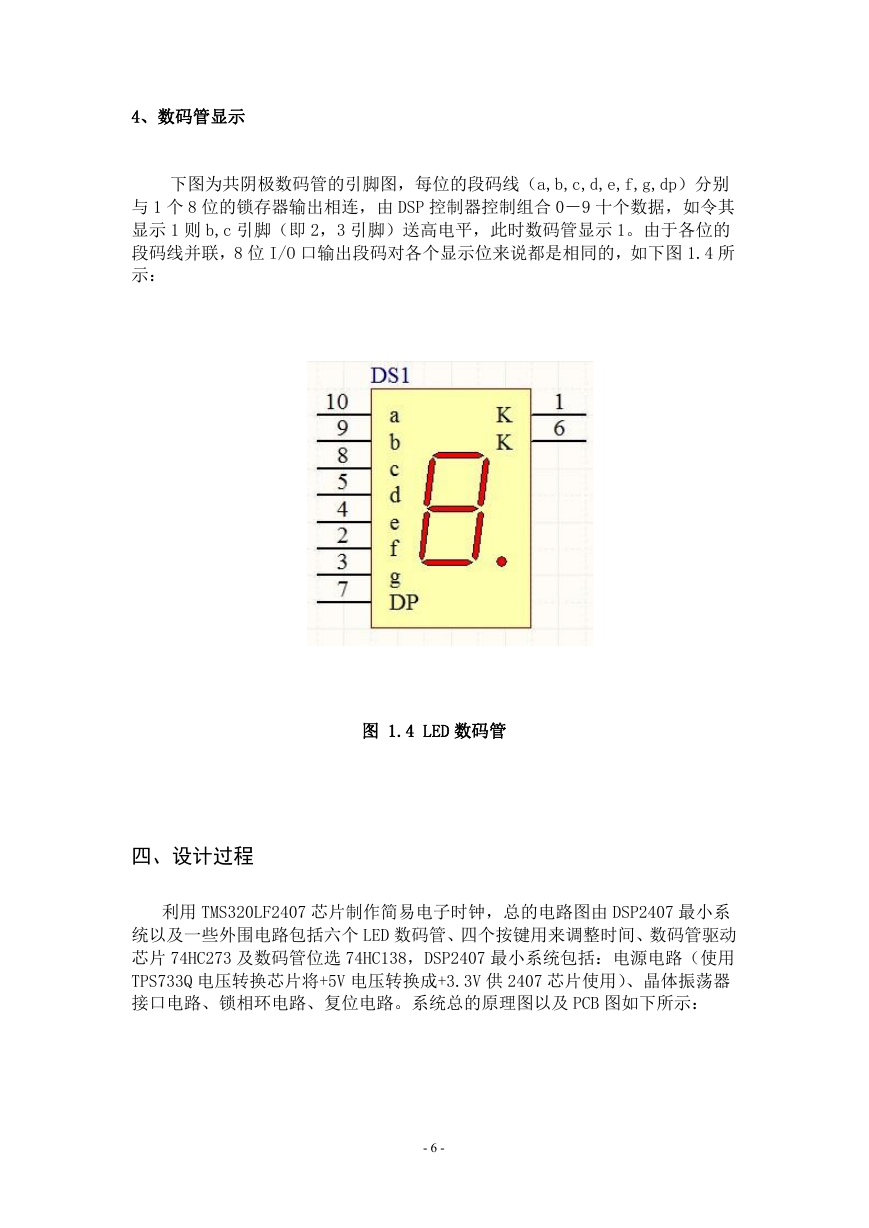

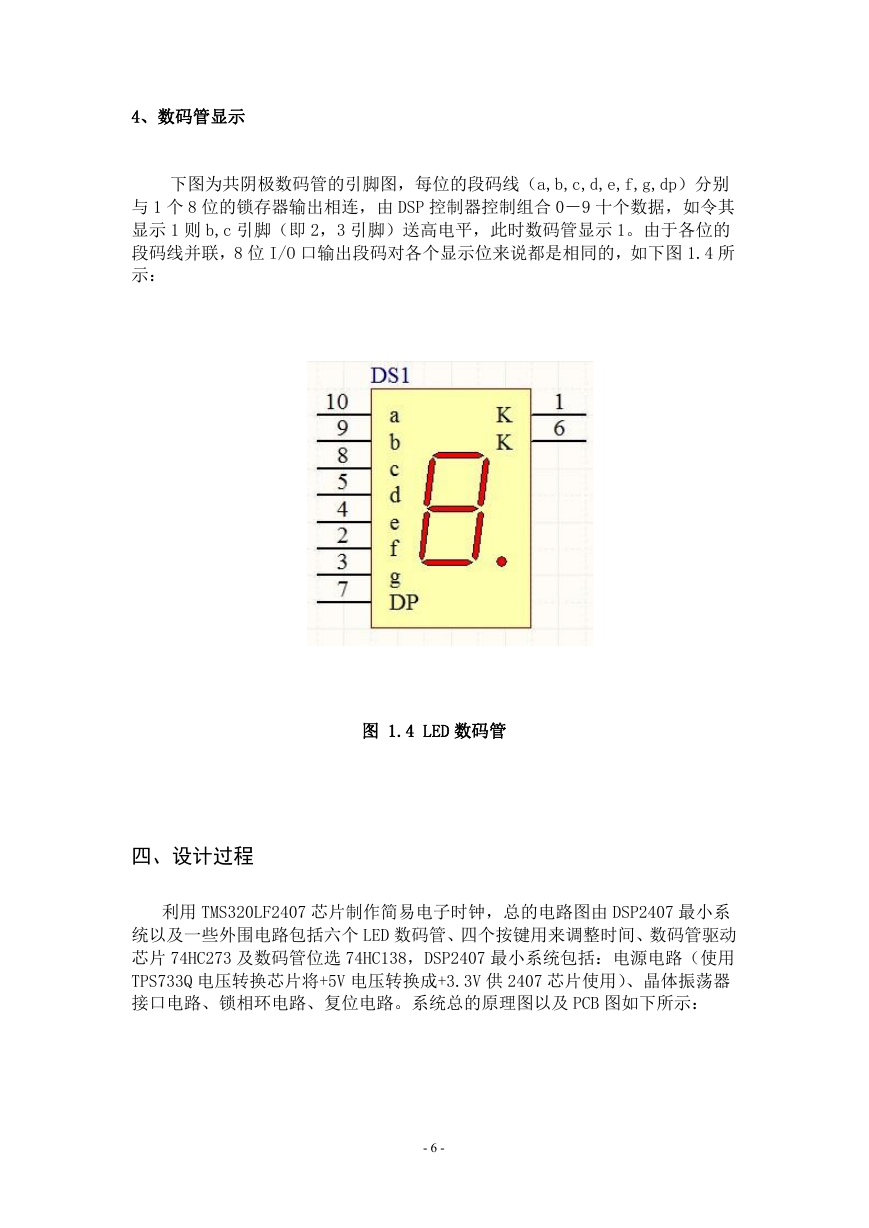

3、位选芯片 74HC138

74HC138 是一款高速 CMOS 器件,74HC138 引脚兼容低功耗肖特基 TTL

(LSTTL)系列。74HC138 可充当一个 8 输出多路分配器,未使用的使能输入

端必须保持绑定在各自合适的高有效或低有效状态。74HC138 与 74HC238 逻辑

功能一致,只不过 74HC138 为反相输出。74HC138 译码器可接受 3 位二进制加

权地址输入(A, B 和 C),并当使能时,提供 8 个互斥的低有效输出(Y0 至 Y7)。

74HC138 特有 3 个使能输入端:两个低有效(-S2 和-S3)和一个高有效(S1)。

除非 S2 和 S3 置低且 S1 置高,否则 74HC138 将保持所有输出为高。利用这种复

合使能特性,仅需 1 片 74HC138 芯片即可轻松实现 6 个数码管的选择导通

图 1.3 74HC138 译码器

- 5 -

�

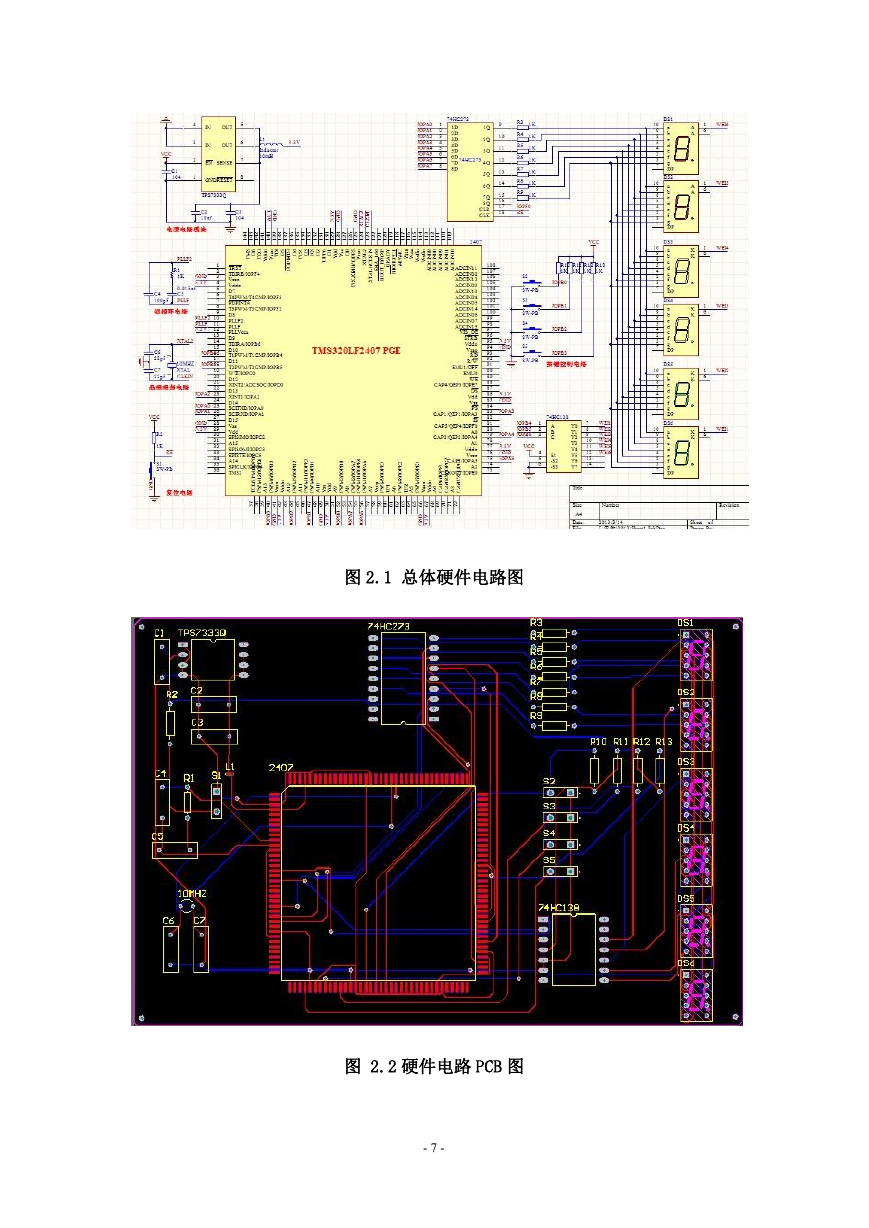

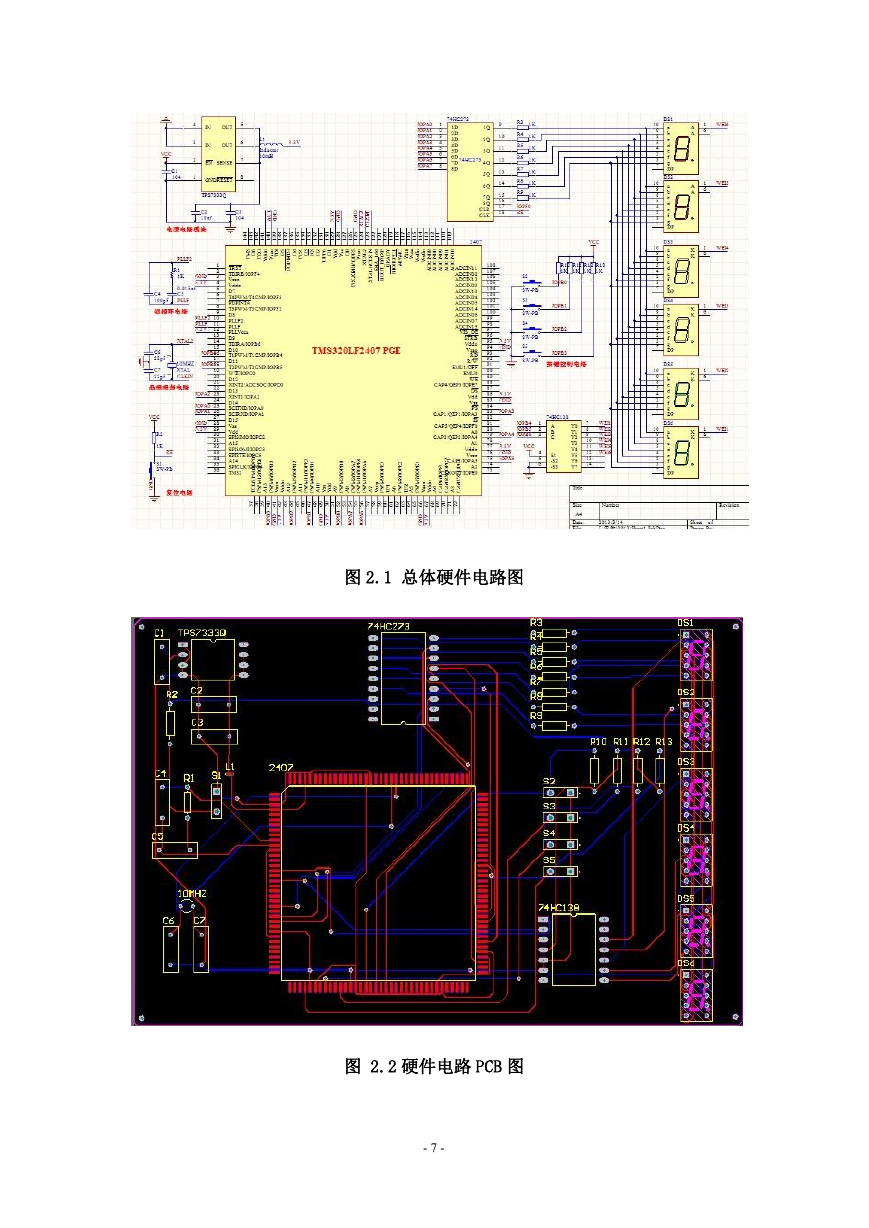

4、数码管显示

下图为共阴极数码管的引脚图,每位的段码线(a,b,c,d,e,f,g,dp)分别

与 1 个 8 位的锁存器输出相连,由 DSP 控制器控制组合 0-9 十个数据,如令其

显示 1 则 b,c 引脚(即 2,3 引脚)送高电平,此时数码管显示 1。由于各位的

段码线并联,8 位 I/O 口输出段码对各个显示位来说都是相同的,如下图 1.4 所

示:

图 1.4 LED 数码管

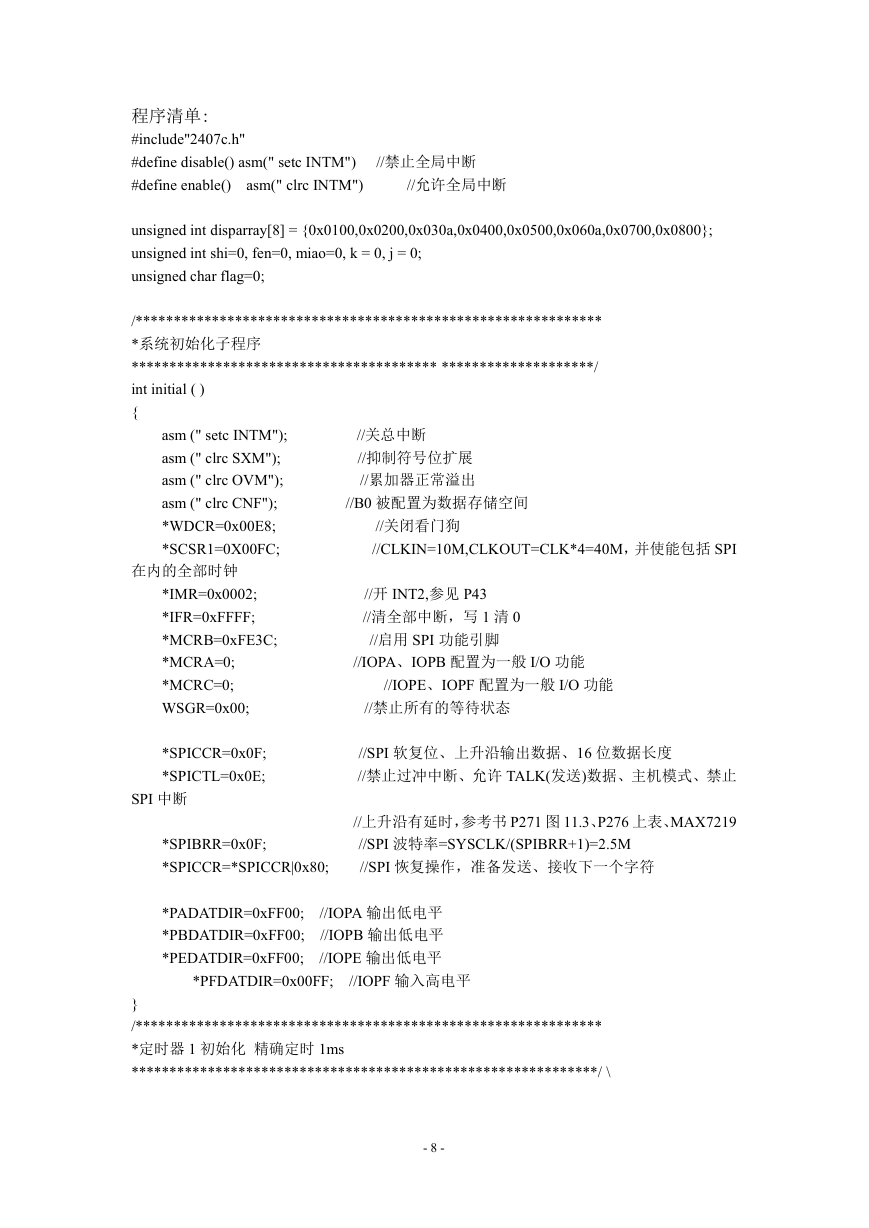

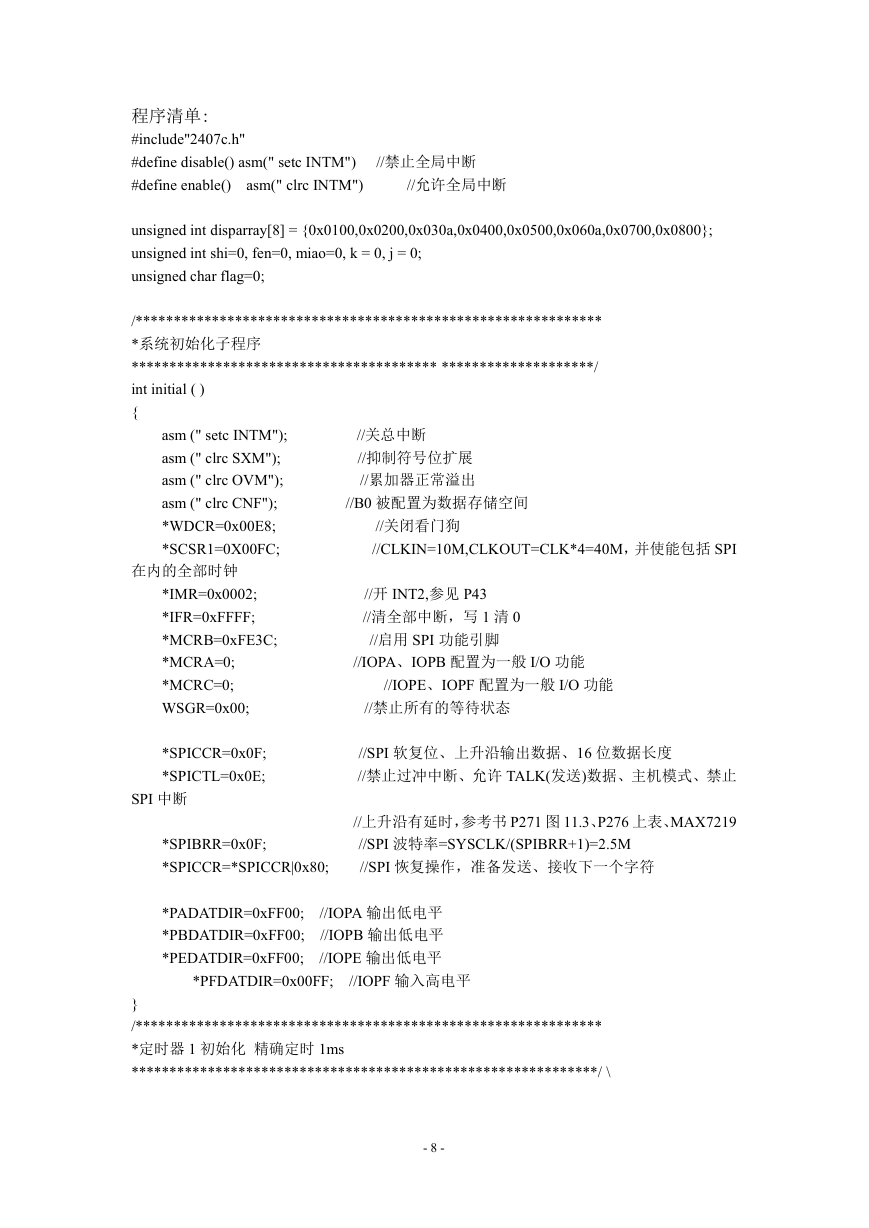

四、设计过程

利用 TMS320LF2407 芯片制作简易电子时钟,总的电路图由 DSP2407 最小系

统以及一些外围电路包括六个 LED 数码管、四个按键用来调整时间、数码管驱动

芯片 74HC273 及数码管位选 74HC138,DSP2407 最小系统包括:电源电路(使用

TPS733Q 电压转换芯片将+5V 电压转换成+3.3V 供 2407 芯片使用)、晶体振荡器

接口电路、锁相环电路、复位电路。系统总的原理图以及 PCB 图如下所示:

- 6 -

�

图 2.1 总体硬件电路图

图 2.2 硬件电路 PCB 图

- 7 -

�

程序清单:

#include"2407c.h"

#define disable() asm(" setc INTM")

#define enable()

asm(" clrc INTM")

//禁止全局中断

//允许全局中断

unsigned int disparray[8] = {0x0100,0x0200,0x030a,0x0400,0x0500,0x060a,0x0700,0x0800};

unsigned int shi=0, fen=0, miao=0, k = 0, j = 0;

unsigned char flag=0;

/*************************************************************

*系统初始化子程序

**************************************** ********************/

int initial ( )

{

asm (" setc INTM");

asm (" clrc SXM");

asm (" clrc OVM");

asm (" clrc CNF");

*WDCR=0x00E8;

*SCSR1=0X00FC;

在内的全部时钟

*IMR=0x0002;

*IFR=0xFFFF;

*MCRB=0xFE3C;

*MCRA=0;

*MCRC=0;

WSGR=0x00;

*SPICCR=0x0F;

*SPICTL=0x0E;

SPI 中断

//关总中断

//抑制符号位扩展

//累加器正常溢出

//B0 被配置为数据存储空间

//关闭看门狗

//CLKIN=10M,CLKOUT=CLK*4=40M,并使能包括 SPI

//开 INT2,参见 P43

//清全部中断,写 1 清 0

//启用 SPI 功能引脚

//IOPA、IOPB 配置为一般 I/O 功能

//IOPE、IOPF 配置为一般 I/O 功能

//禁止所有的等待状态

//SPI 软复位、上升沿输出数据、16 位数据长度

//禁止过冲中断、允许 TALK(发送)数据、主机模式、禁止

*SPIBRR=0x0F;

*SPICCR=*SPICCR|0x80;

//上升沿有延时,参考书 P271 图 11.3、P276 上表、MAX7219

//SPI 波特率=SYSCLK/(SPIBRR+1)=2.5M

//SPI 恢复操作,准备发送、接收下一个字符

*PADATDIR=0xFF00;

*PBDATDIR=0xFF00;

*PEDATDIR=0xFF00;

//IOPA 输出低电平

//IOPB 输出低电平

//IOPE 输出低电平

*PFDATDIR=0x00FF;

//IOPF 输入高电平

}

/*************************************************************

*定时器 1 初始化 精确定时 1ms

*************************************************************/ \

- 8 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc