Qualcomm Technologies, Inc.

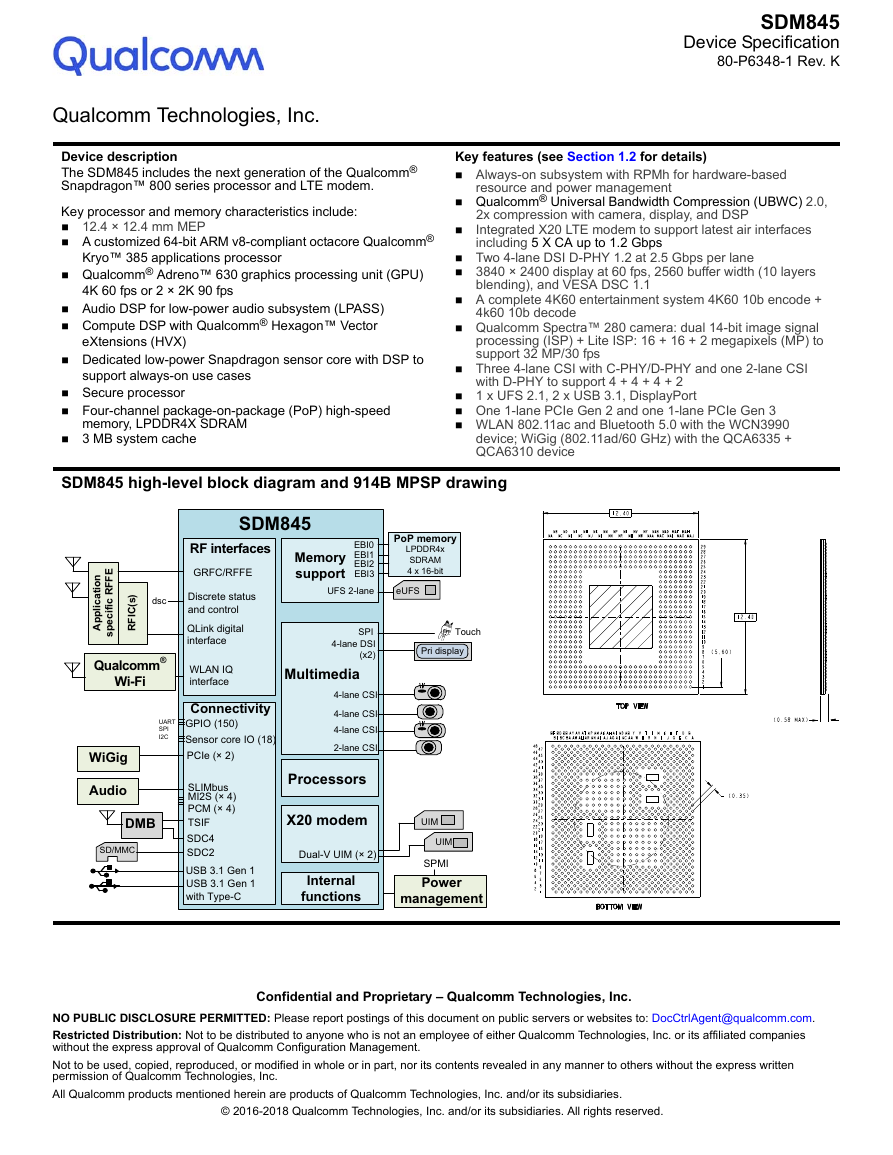

SDM845

Device Specification

80-P6348-1 Rev. K

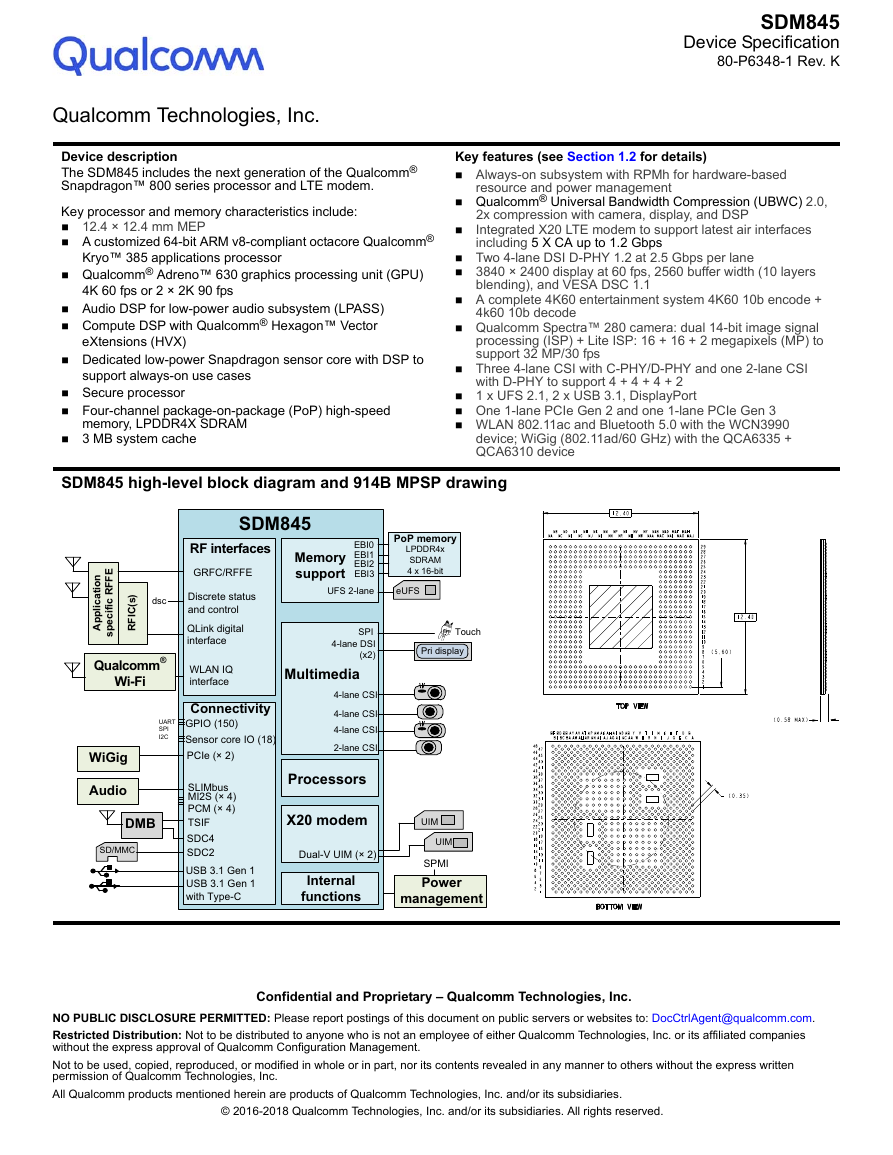

Device description

The SDM845 includes the next generation of the Qualcomm®

Snapdragon™ 800 series processor and LTE modem.

Key processor and memory characteristics include:

12.4 × 12.4 mm MEP

A customized 64-bit ARM v8-compliant octacore Qualcomm®

Kryo™ 385 applications processor

Qualcomm® Adreno™ 630 graphics processing unit (GPU)

4K 60 fps or 2 × 2K 90 fps

Audio DSP for low-power audio subsystem (LPASS)

Compute DSP with Qualcomm® Hexagon™ Vector

eXtensions (HVX)

Dedicated low-power Snapdragon sensor core with DSP to

support always-on use cases

Secure processor

Four-channel package-on-package (PoP) high-speed

memory, LPDDR4X SDRAM

3 MB system cache

Key features (see Section 1.2 for details)

Always-on subsystem with RPMh for hardware-based

Qualcomm® Universal Bandwidth Compression (UBWC) 2.0,

resource and power management

2x compression with camera, display, and DSP

Integrated X20 LTE modem to support latest air interfaces

including 5 X CA up to 1.2 Gbps

Two 4-lane DSI D-PHY 1.2 at 2.5 Gbps per lane

3840 × 2400 display at 60 fps, 2560 buffer width (10 layers

blending), and VESA DSC 1.1

A complete 4K60 entertainment system 4K60 10b encode +

4k60 10b decode

Qualcomm Spectra™ 280 camera: dual 14-bit image signal

processing (ISP) + Lite ISP: 16 + 16 + 2 megapixels (MP) to

support 32 MP/30 fps

Three 4-lane CSI with C-PHY/D-PHY and one 2-lane CSI

with D-PHY to support 4 + 4 + 4 + 2

1 x UFS 2.1, 2 x USB 3.1, DisplayPort

One 1-lane PCIe Gen 2 and one 1-lane PCIe Gen 3

WLAN 802.11ac and Bluetooth 5.0 with the WCN3990

device; WiGig (802.11ad/60 GHz) with the QCA6335 +

QCA6310 device

SDM845 high-level block diagram and 914B MPSP drawing

SDM845

Memory

support

EBI0

EBI1

EBI2

EBI3

UFS 2-lane

PoP memory

LPDDR4x

SDRAM

4 x 16-bit

eUFS

n

o

i

t

a

c

i

l

p

p

A

E

F

F

R

c

i

f

i

c

e

p

s

dsc

)

s

(

C

F

R

I

Qualcomm®

Wi-Fi

UART

SPI

I2C

WiGig

Audio

DMB

SD/MMC

RF interfaces

GRFC/RFFE

Discrete status

and control

QLink digital

interface

WLAN IQ

interface

Connectivity

GPIO (150)

Sensor core IO (18)

PCIe (× 2)

SLIMbus

MI2S (× 4)

PCM (× 4)

TSIF

SDC4

SDC2

USB 3.1 Gen 1

USB 3.1 Gen 1

with Type-C

SPI

4-lane DSI

(x2)

Touch

Pri display

Multimedia

4-lane CSI

4-lane CSI

4-lane CSI

2-lane CSI

Processors

X20 modem

Dual-V UIM (× 2)

Internal

functions

UIM

UIM

SPMI

Power

management

Confidential and Proprietary – Qualcomm Technologies, Inc.

NO PUBLIC DISCLOSURE PERMITTED: Please report postings of this document on public servers or websites to: DocCtrlAgent@qualcomm.com.

Restricted Distribution: Not to be distributed to anyone who is not an employee of either Qualcomm Technologies, Inc. or its affiliated companies

without the express approval of Qualcomm Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others without the express written

permission of Qualcomm Technologies, Inc.

All Qualcomm products mentioned herein are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

© 2016-2018 Qualcomm Technologies, Inc. and/or its subsidiaries. All rights reserved.

�

Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1

2 Pin definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4 Mechanical information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5 Carrier, handling, and storage information . . . . . . . . . . . . . . . . . . . . . . . . . 75

6 PCB mounting guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7 Part reliability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

8 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

2

�

1 Introduction

Document updates

See the Revision history for details on the changes included in this revision.

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3

�

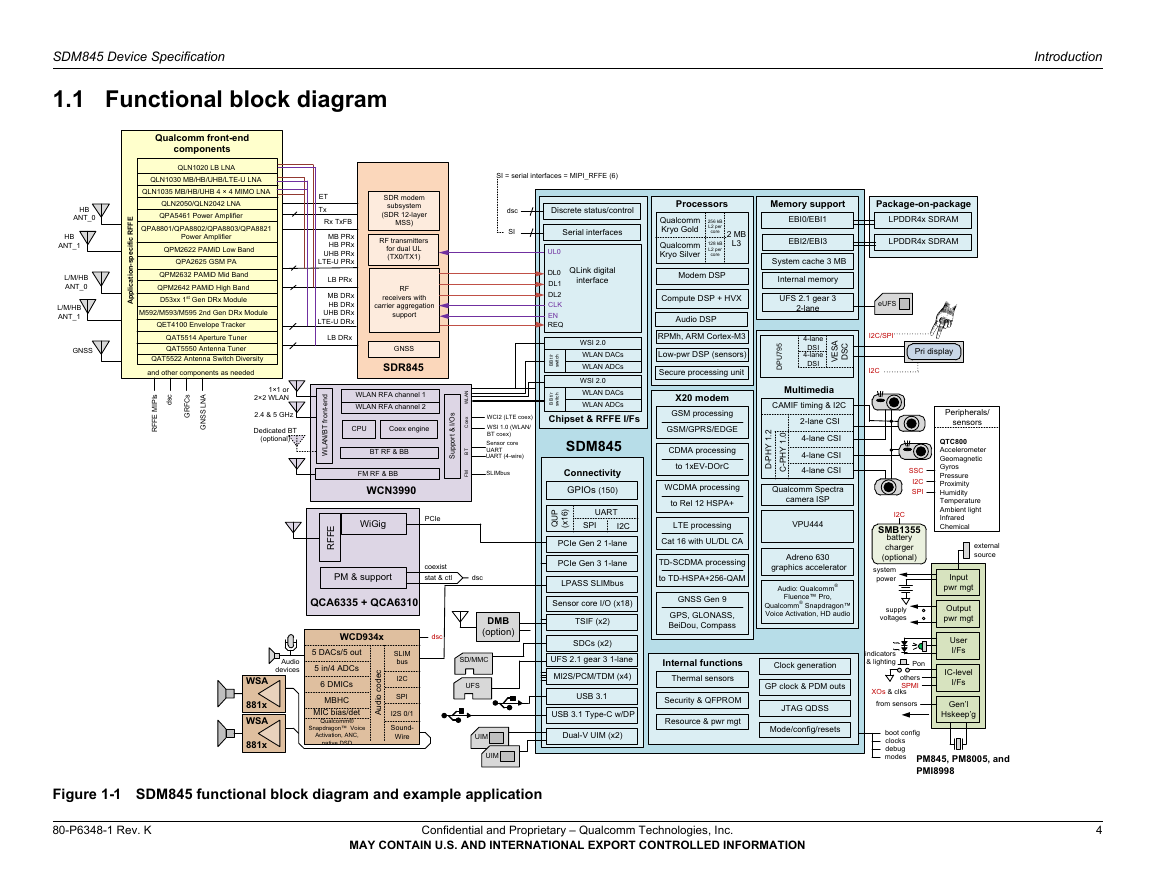

SDM845 Device Specification

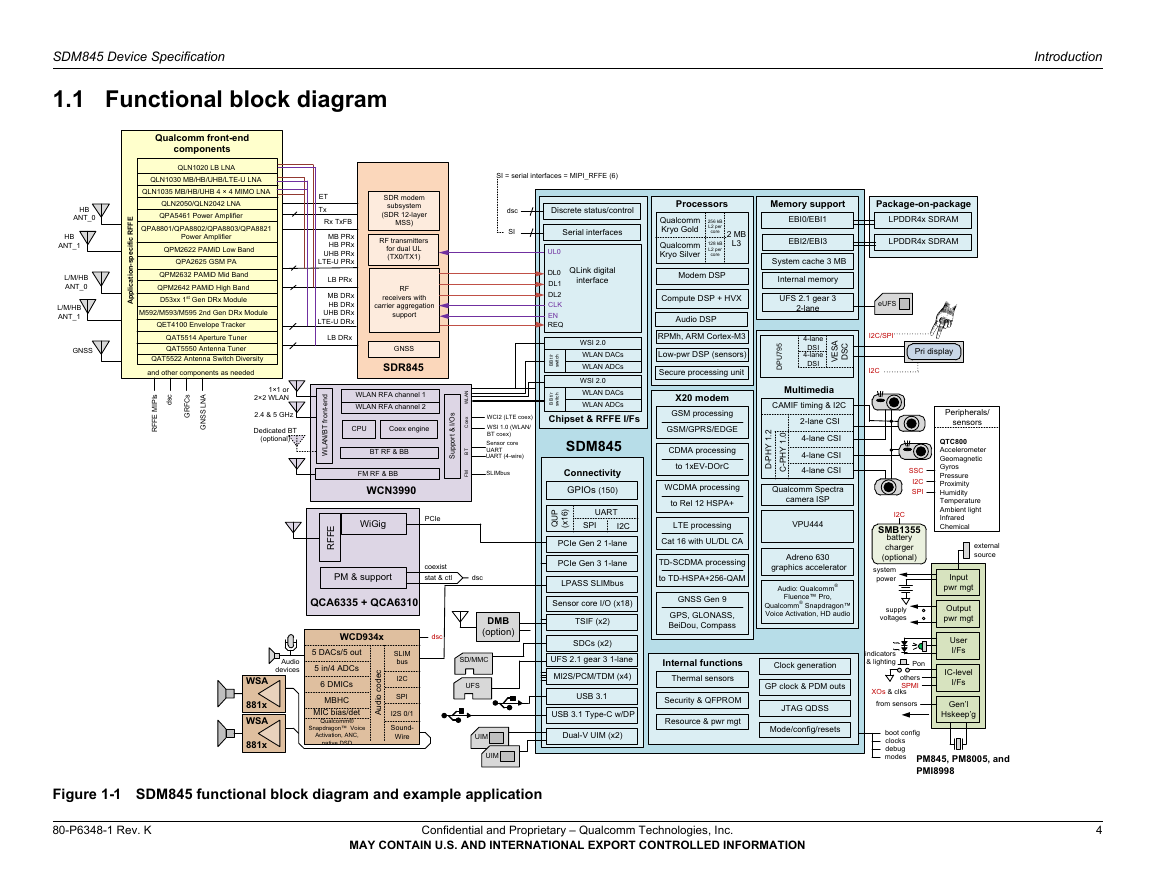

1.1 Functional block diagram

Introduction

HB

ANT_0

HB

ANT_1

L/M/HB

ANT_0

L/M/HB

ANT_1

GNSS

Qualcomm front-end

components

QLN1020 LB LNA

QLN1030 MB/HB/UHB/LTE-U LNA

QLN1035 MB/HB/UHB 4 × 4 MIMO LNA

QLN2050/QLN2042 LNA

QPA5461 Power Amplifier

QPA8801/QPA8802/QPA8803/QPA8821

Power Amplifier

QPM2622 PAMiD Low Band

QPA2625 GSM PA

QPM2632 PAMiD Mid Band

QPM2642 PAMiD High Band

D53xx 1st Gen DRx Module

M592/M593/M595 2nd Gen DRx Module

QET4100 Envelope Tracker

QAT5514 Aperture Tuner

QAT5550 Antenna Tuner

QAT5522 Antenna Switch Diversity

and other components as needed

E

F

F

R

c

i

f

i

c

e

p

s

-

n

o

i

t

a

c

i

l

p

p

A

I

s

I

P

M

E

F

F

R

c

s

d

s

C

F

R

G

A

N

L

S

S

N

G

1×1 or

2×2 WLAN

2.4 & 5 GHz

Dedicated BT

(optional)

SDR modem

subsystem

(SDR 12-layer

MSS)

RF transmitters

for dual UL

(TX0/TX1)

RF

receivers with

carrier aggregation

support

ET

Tx

Rx TxFB

MB PRx

HB PRx

UHB PRx

LTE-U PRx

LB PRx

MB DRx

HB DRx

UHB DRx

LTE-U DRx

LB DRx

SI = serial interfaces = MIPI_RFFE (6)

dsc

SI

Discrete status/control

Serial interfaces

QLink digital

interface

UL0

DL0

DL1

DL2

CLK

EN

REQ

WCI2 (LTE coex)

WSI 1.0 (WLAN/

BT coex)

Sensor core

UART

UART (4-wire)

SLIMbus

GNSS

SDR845

WLAN RFA channel 1

WLAN RFA channel 2

CPU

Coex engine

BT RF & BB

FM RF & BB

WCN3990

s

O

/

I

&

t

r

o

p

p

u

S

N

A

L

W

x

e

o

C

T

B

M

F

WiGig

PCIe

d

n

e

-

t

n

o

r

f

/

T

B

N

A

L

W

E

F

F

R

PM & support

coexist

stat & ctl

dsc

QCA6335 + QCA6310

WCD934x

dsc

Audio

devices

5 DACs/5 out

5 in/4 ADCs

6 DMICs

MBHC

MIC bias/det

Qualcomm®

Snapdragon™ Voice

Activation, ANC,

native DSD

c

e

d

o

c

i

o

d

u

A

SLIM

bus

I2C

SPI

I2S 0/1

Sound-

Wire

WSA

881x

WSA

881x

DMB

(option)

SD/MMC

UFS

UIM

UIM

WSI 2.0

WLAN DACs

WLAN ADCs

WSI 2.0

WLAN DACs

WLAN ADCs

r

/

t

B

B

h

c

t

i

w

s

r

/

t

B

B

h

c

t

i

w

s

Chipset & RFFE I/Fs

SDM845

Connectivity

GPIOs (150)

P

U

Q

)

6

1

x

(

UART

SPI

I2C

PCIe Gen 2 1-lane

PCIe Gen 3 1-lane

LPASS SLIMbus

Sensor core I/O (x18)

TSIF (x2)

SDCs (x2)

UFS 2.1 gear 3 1-lane

MI2S/PCM/TDM (x4)

USB 3.1

USB 3.1 Type-C w/DP

Dual-V UIM (x2)

Processors

Memory support

Package-on-package

Qualcomm

Kryo Gold

Qualcomm

Kryo Silver

256 kB

L2 per

core

128 kB

L2 per

core

2 MB

L3

Modem DSP

Compute DSP + HVX

Audio DSP

RPMh, ARM Cortex-M3

Low-pwr DSP (sensors)

Secure processing unit

X20 modem

GSM processing

GSM/GPRS/EDGE

CDMA processing

to 1xEV-DOrC

WCDMA processing

to Rel 12 HSPA+

LTE processing

Cat 16 with UL/DL CA

TD-SCDMA processing

to TD-HSPA+256-QAM

GNSS Gen 9

GPS, GLONASS,

BeiDou, Compass

EBI0/EBI1

EBI2/EBI3

System cache 3 MB

Internal memory

UFS 2.1 gear 3

2-lane

4-lane

DSI

4-lane

DSI

A

S

E

V

C

S

D

5

9

7

U

P

D

Multimedia

CAMIF timing & I2C

2

.

1

Y

H

P

D

-

0

.

1

Y

H

P

C

-

2-lane CSI

4-lane CSI

4-lane CSI

4-lane CSI

Qualcomm Spectra

camera ISP

VPU444

Adreno 630

graphics accelerator

Audio: Qualcomm®

Fluence™ Pro,

Qualcomm® Snapdragon™

Voice Activation, HD audio

Internal functions

Thermal sensors

Security & QFPROM

Resource & pwr mgt

Clock generation

GP clock & PDM outs

JTAG QDSS

Mode/config/resets

LPDDR4x SDRAM

LPDDR4x SDRAM

eUFS

I2C/SPI

I2C

Pri display

Peripherals/

sensors

QTC800

Accelerometer

Geomagnetic

Gyros

Pressure

Proximity

Humidity

Temperature

Ambient light

Infrared

Chemical

external

source

Input

pwr mgt

Output

pwr mgt

User

I/Fs

IC-level

I/Fs

Gen’l

Hskeep’g

SSC

I2C

SPI

I2C

SMB1355

battery

charger

(optional)

system

power

supply

voltages

indicators

& lighting

Pon

others

SPMI

XOs & clks

from sensors

boot config

clocks

debug

modes

PM845, PM8005, and

PMI8998

Figure 1-1 SDM845 functional block diagram and example application

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

4

�

SDM845 Device Specification

Introduction

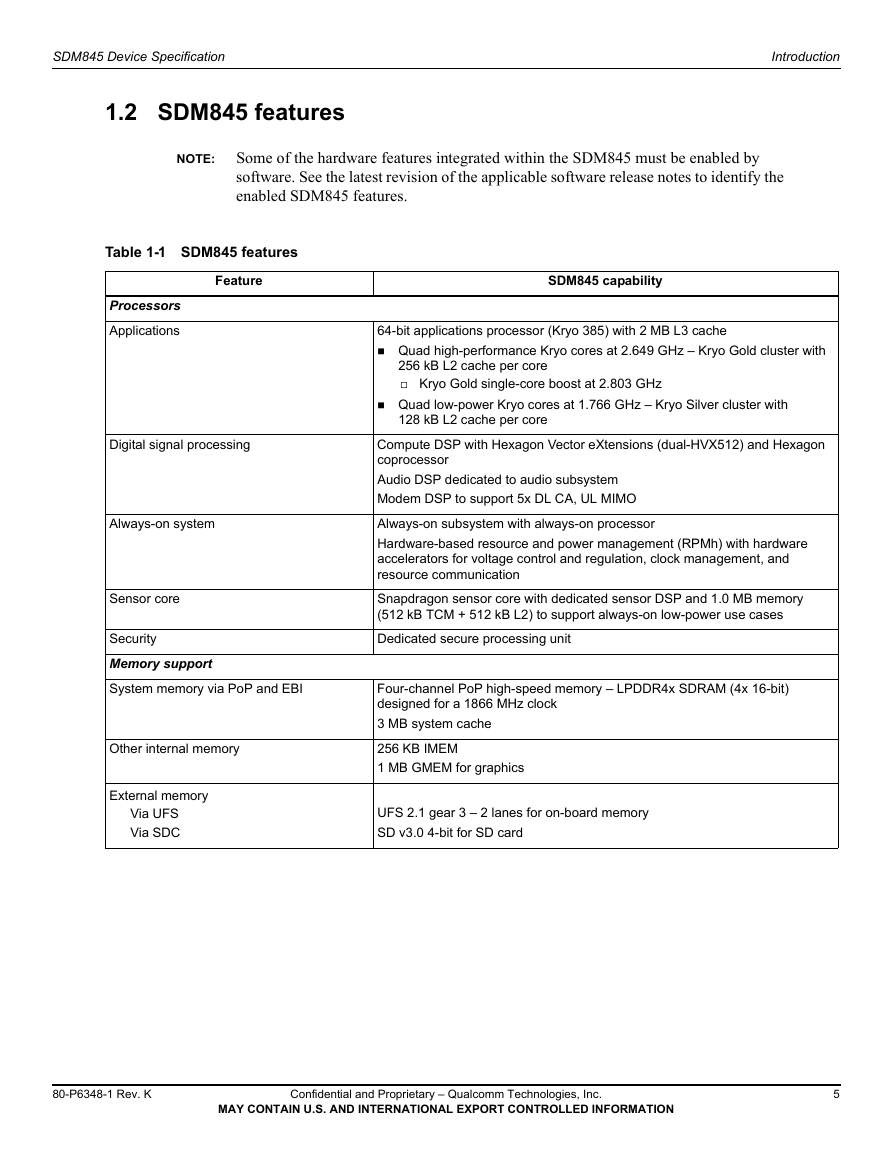

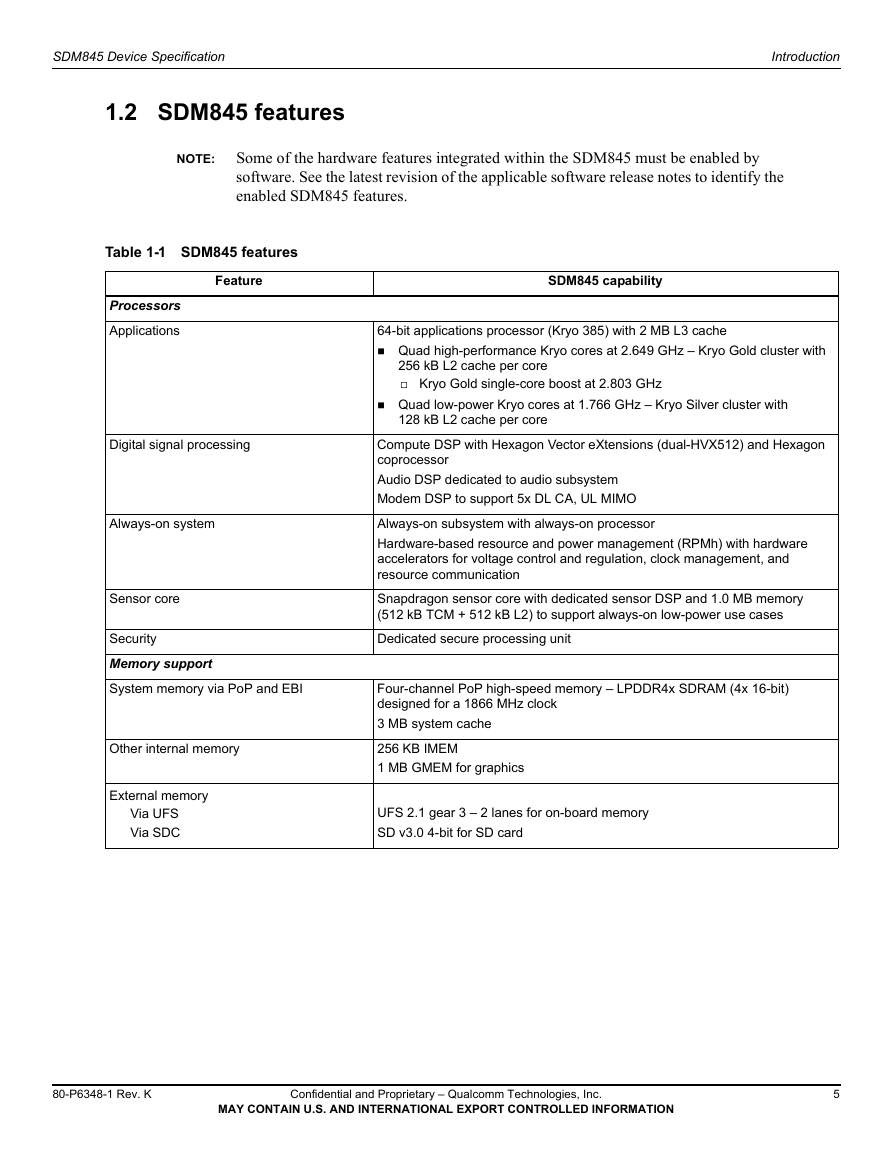

1.2 SDM845 features

NOTE:

Some of the hardware features integrated within the SDM845 must be enabled by

software. See the latest revision of the applicable software release notes to identify the

enabled SDM845 features.

Table 1-1 SDM845 features

Feature

Processors

Applications

Digital signal processing

Always-on system

Sensor core

Security

Memory support

System memory via PoP and EBI

Other internal memory

External memory

Via UFS

Via SDC

SDM845 capability

64-bit applications processor (Kryo 385) with 2 MB L3 cache

Quad high-performance Kryo cores at 2.649 GHz – Kryo Gold cluster with

256 kB L2 cache per core

Kryo Gold single-core boost at 2.803 GHz

Quad low-power Kryo cores at 1.766 GHz – Kryo Silver cluster with

128 kB L2 cache per core

Compute DSP with Hexagon Vector eXtensions (dual-HVX512) and Hexagon

coprocessor

Audio DSP dedicated to audio subsystem

Modem DSP to support 5x DL CA, UL MIMO

Always-on subsystem with always-on processor

Hardware-based resource and power management (RPMh) with hardware

accelerators for voltage control and regulation, clock management, and

resource communication

Snapdragon sensor core with dedicated sensor DSP and 1.0 MB memory

(512 kB TCM + 512 kB L2) to support always-on low-power use cases

Dedicated secure processing unit

Four-channel PoP high-speed memory – LPDDR4x SDRAM (4x 16-bit)

designed for a 1866 MHz clock

3 MB system cache

256 KB IMEM

1 MB GMEM for graphics

UFS 2.1 gear 3 – 2 lanes for on-board memory

SD v3.0 4-bit for SD card

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

5

�

SDM845 Device Specification

Introduction

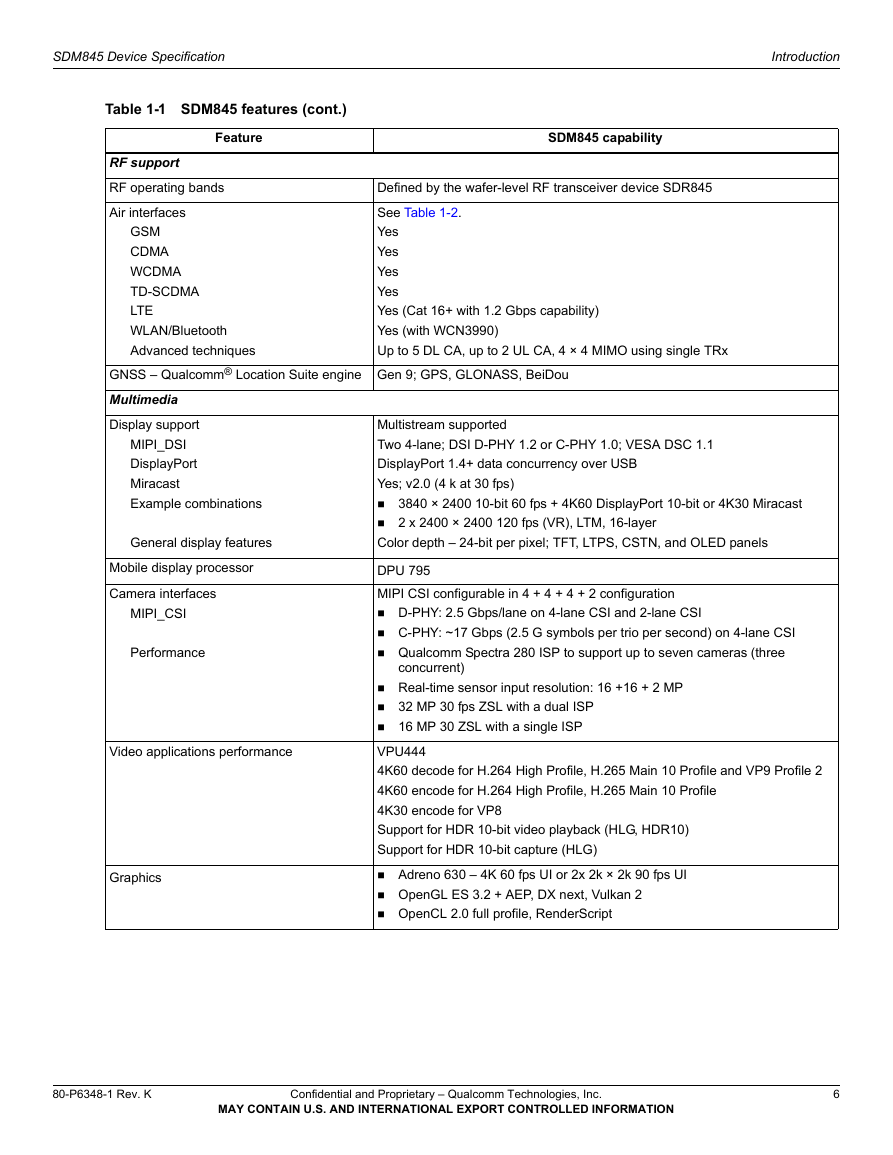

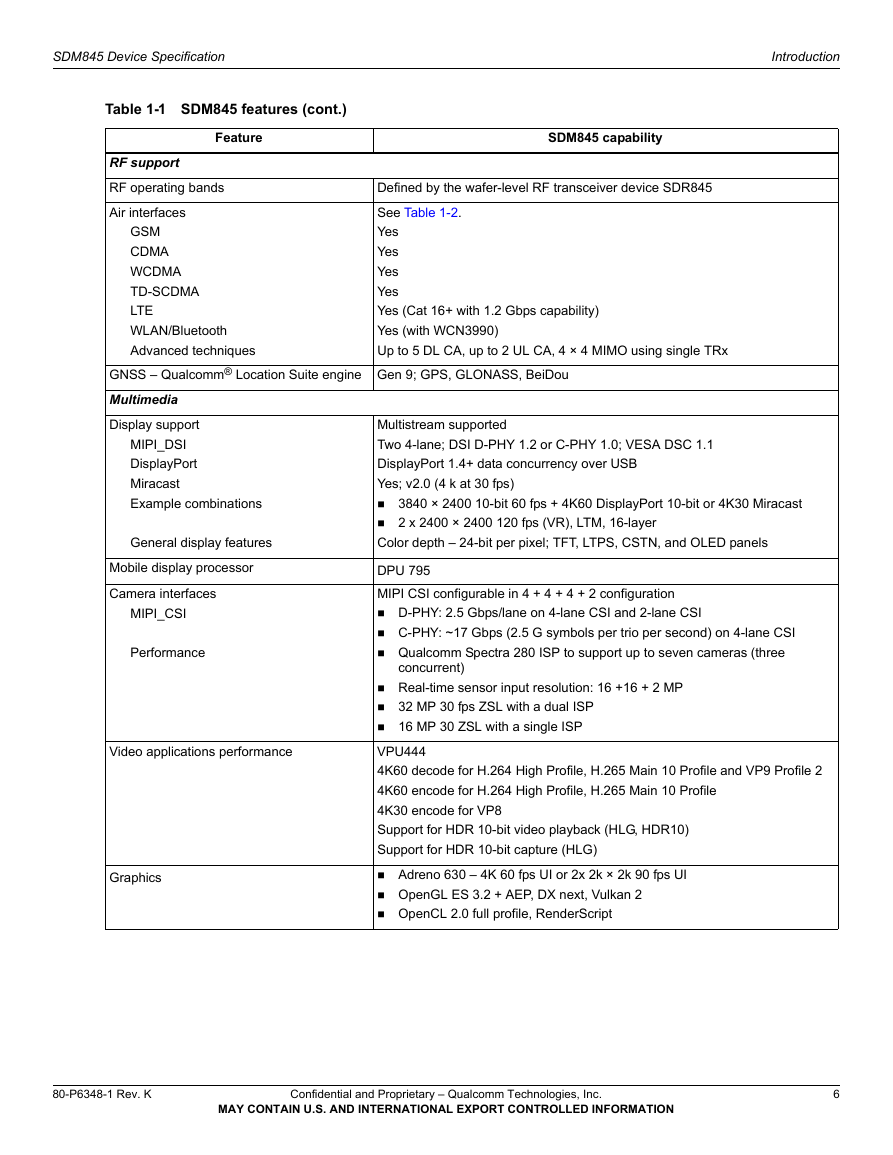

Table 1-1 SDM845 features (cont.)

Feature

RF support

RF operating bands

Air interfaces

GSM

CDMA

WCDMA

TD-SCDMA

LTE

WLAN/Bluetooth

Advanced techniques

SDM845 capability

Defined by the wafer-level RF transceiver device SDR845

See Table 1-2.

Yes

Yes

Yes

Yes

Yes (Cat 16+ with 1.2 Gbps capability)

Yes (with WCN3990)

Up to 5 DL CA, up to 2 UL CA, 4 × 4 MIMO using single TRx

GNSS – Qualcomm® Location Suite engine Gen 9; GPS, GLONASS, BeiDou

Multimedia

Display support

MIPI_DSI

DisplayPort

Miracast

Example combinations

General display features

Mobile display processor

Camera interfaces

MIPI_CSI

Performance

Video applications performance

Graphics

Multistream supported

Two 4-lane; DSI D-PHY 1.2 or C-PHY 1.0; VESA DSC 1.1

DisplayPort 1.4+ data concurrency over USB

Yes; v2.0 (4 k at 30 fps)

3840 × 2400 10-bit 60 fps + 4K60 DisplayPort 10-bit or 4K30 Miracast

2 x 2400 × 2400 120 fps (VR), LTM, 16-layer

Color depth – 24-bit per pixel; TFT, LTPS, CSTN, and OLED panels

DPU 795

MIPI CSI configurable in 4 + 4 + 4 + 2 configuration

D-PHY: 2.5 Gbps/lane on 4-lane CSI and 2-lane CSI

C-PHY: ~17 Gbps (2.5 G symbols per trio per second) on 4-lane CSI

Qualcomm Spectra 280 ISP to support up to seven cameras (three

concurrent)

Real-time sensor input resolution: 16 +16 + 2 MP

32 MP 30 fps ZSL with a dual ISP

16 MP 30 ZSL with a single ISP

VPU444

4K60 decode for H.264 High Profile, H.265 Main 10 Profile and VP9 Profile 2

4K60 encode for H.264 High Profile, H.265 Main 10 Profile

4K30 encode for VP8

Support for HDR 10-bit video playback (HLG, HDR10)

Support for HDR 10-bit capture (HLG)

Adreno 630 – 4K 60 fps UI or 2x 2k × 2k 90 fps UI

OpenGL ES 3.2 + AEP, DX next, Vulkan 2

OpenCL 2.0 full profile, RenderScript

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

6

�

SDM845 Device Specification

Introduction

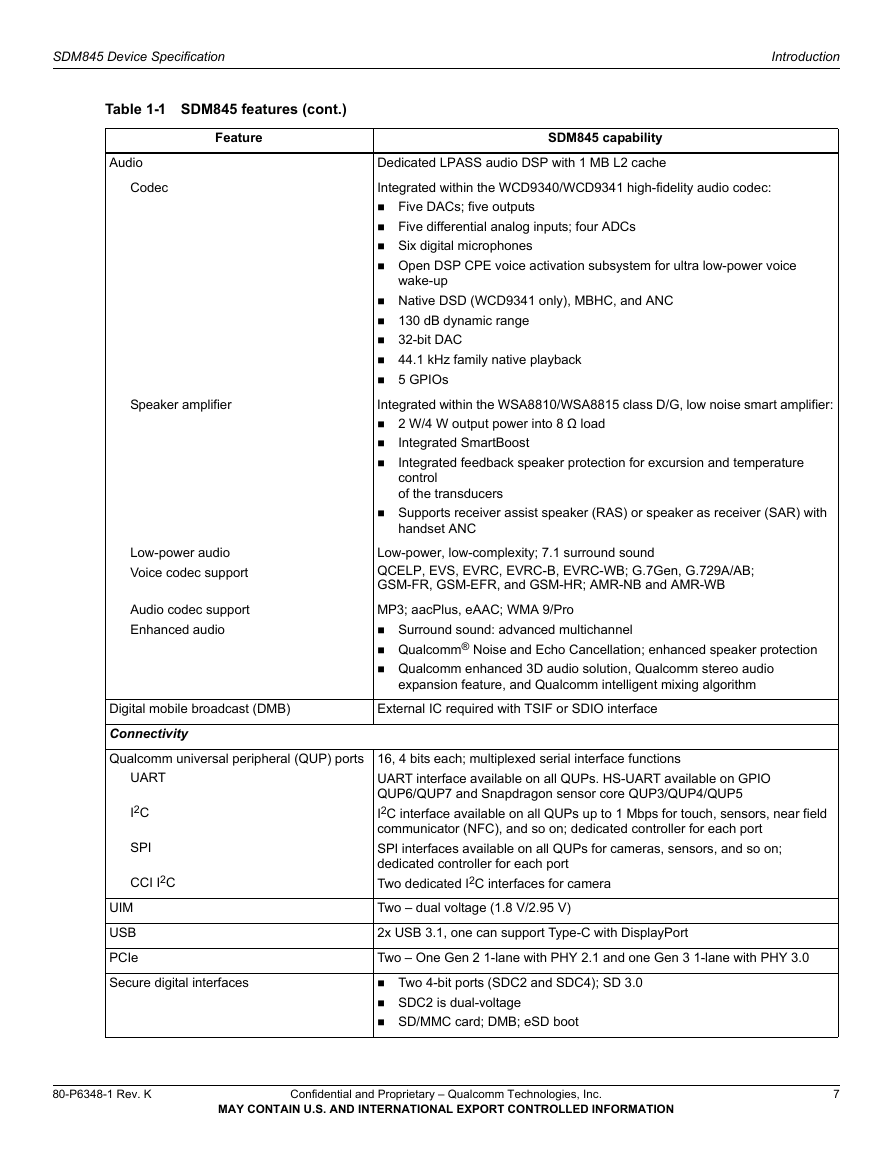

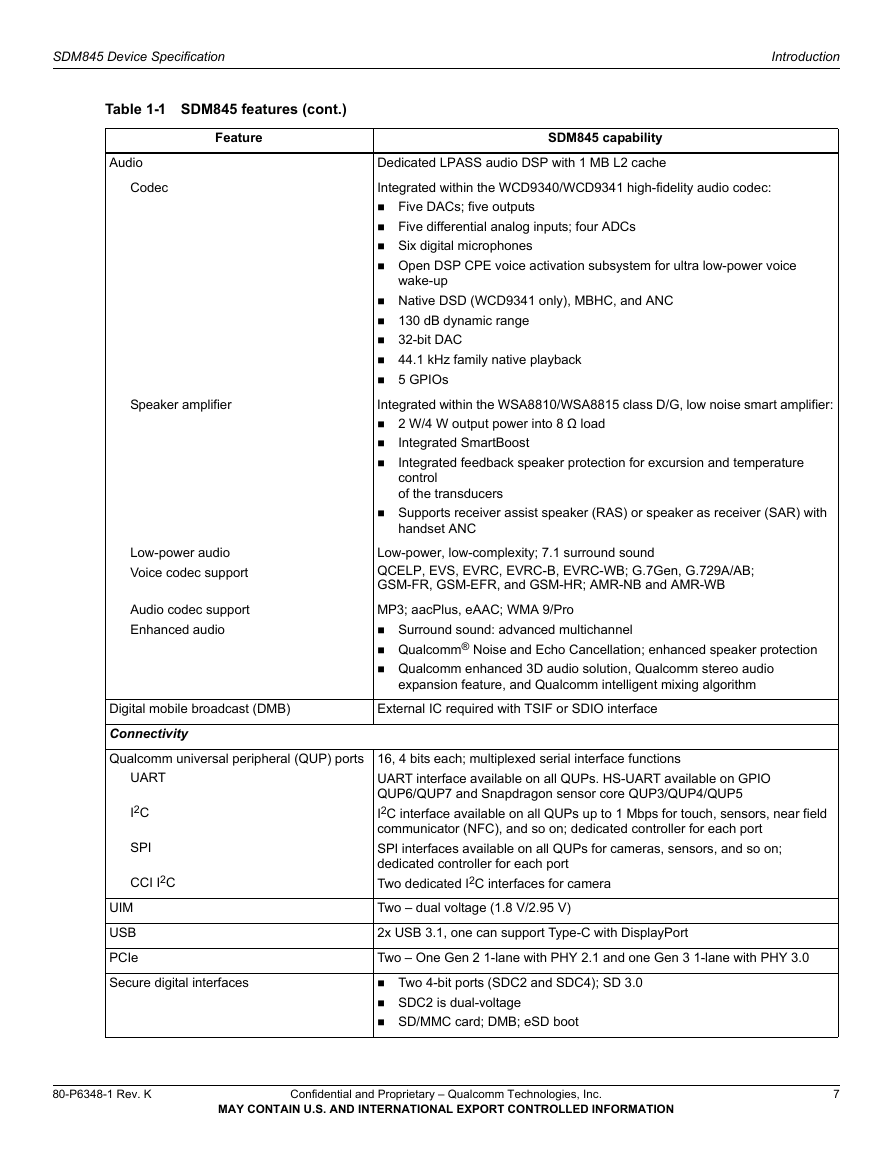

Table 1-1 SDM845 features (cont.)

Feature

Audio

Codec

Speaker amplifier

Low-power audio

Voice codec support

Audio codec support

Enhanced audio

Digital mobile broadcast (DMB)

Connectivity

Qualcomm universal peripheral (QUP) ports

UART

I2C

SPI

CCI I2C

UIM

USB

PCIe

Secure digital interfaces

SDM845 capability

Dedicated LPASS audio DSP with 1 MB L2 cache

Integrated within the WCD9340/WCD9341 high-fidelity audio codec:

Five DACs; five outputs

Five differential analog inputs; four ADCs

Six digital microphones

Open DSP CPE voice activation subsystem for ultra low-power voice

wake-up

Native DSD (WCD9341 only), MBHC, and ANC

130 dB dynamic range

32-bit DAC

44.1 kHz family native playback

5 GPIOs

Integrated within the WSA8810/WSA8815 class D/G, low noise smart amplifier:

2 W/4 W output power into 8 Ω load

Integrated SmartBoost

Integrated feedback speaker protection for excursion and temperature

control

of the transducers

Supports receiver assist speaker (RAS) or speaker as receiver (SAR) with

handset ANC

Low-power, low-complexity; 7.1 surround sound

QCELP, EVS, EVRC, EVRC-B, EVRC-WB; G.7Gen, G.729A/AB;

GSM-FR, GSM-EFR, and GSM-HR; AMR-NB and AMR-WB

MP3; aacPlus, eAAC; WMA 9/Pro

Surround sound: advanced multichannel

Qualcomm® Noise and Echo Cancellation; enhanced speaker protection

Qualcomm enhanced 3D audio solution, Qualcomm stereo audio

expansion feature, and Qualcomm intelligent mixing algorithm

External IC required with TSIF or SDIO interface

16, 4 bits each; multiplexed serial interface functions

UART interface available on all QUPs. HS-UART available on GPIO

QUP6/QUP7 and Snapdragon sensor core QUP3/QUP4/QUP5

I2C interface available on all QUPs up to 1 Mbps for touch, sensors, near field

communicator (NFC), and so on; dedicated controller for each port

SPI interfaces available on all QUPs for cameras, sensors, and so on;

dedicated controller for each port

Two dedicated I2C interfaces for camera

Two – dual voltage (1.8 V/2.95 V)

2x USB 3.1, one can support Type-C with DisplayPort

Two – One Gen 2 1-lane with PHY 2.1 and one Gen 3 1-lane with PHY 3.0

Two 4-bit ports (SDC2 and SDC4); SD 3.0

SDC2 is dual-voltage

SD/MMC card; DMB; eSD boot

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

7

�

SDM845 Device Specification

Introduction

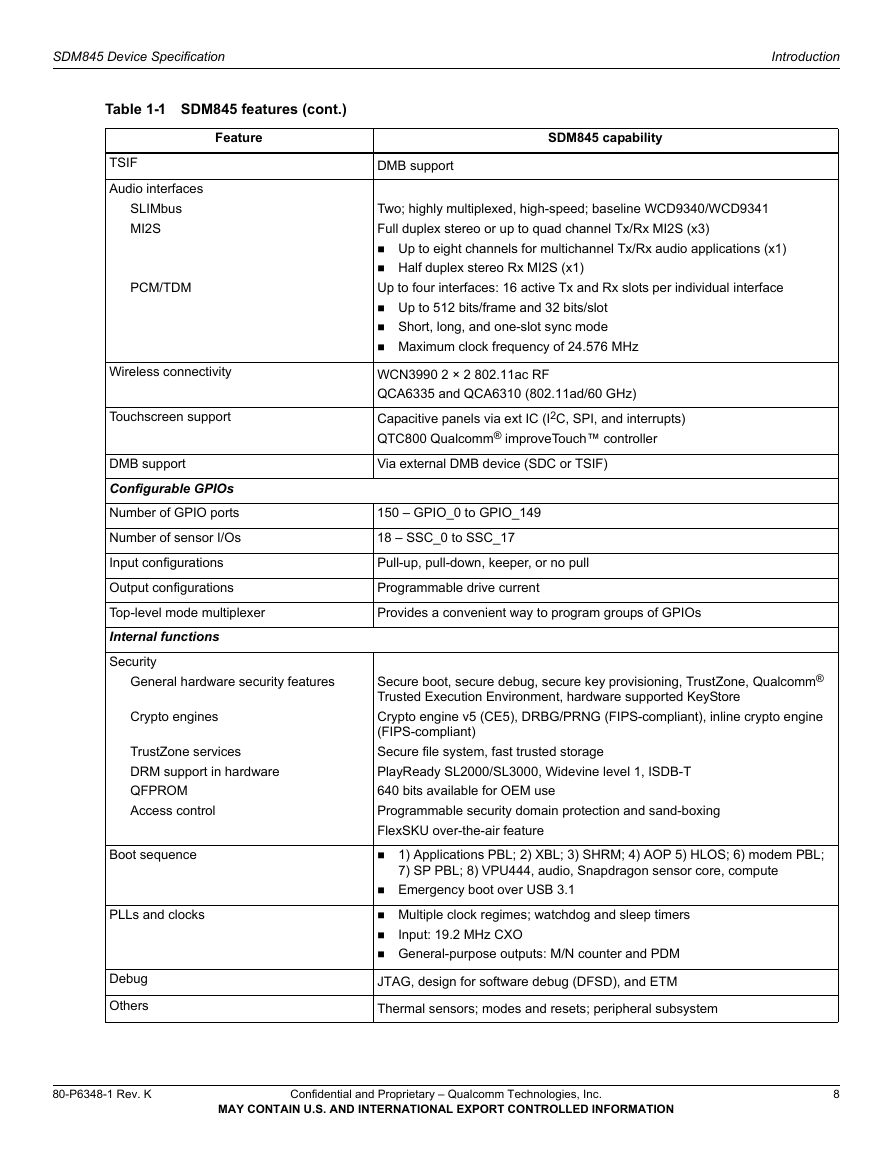

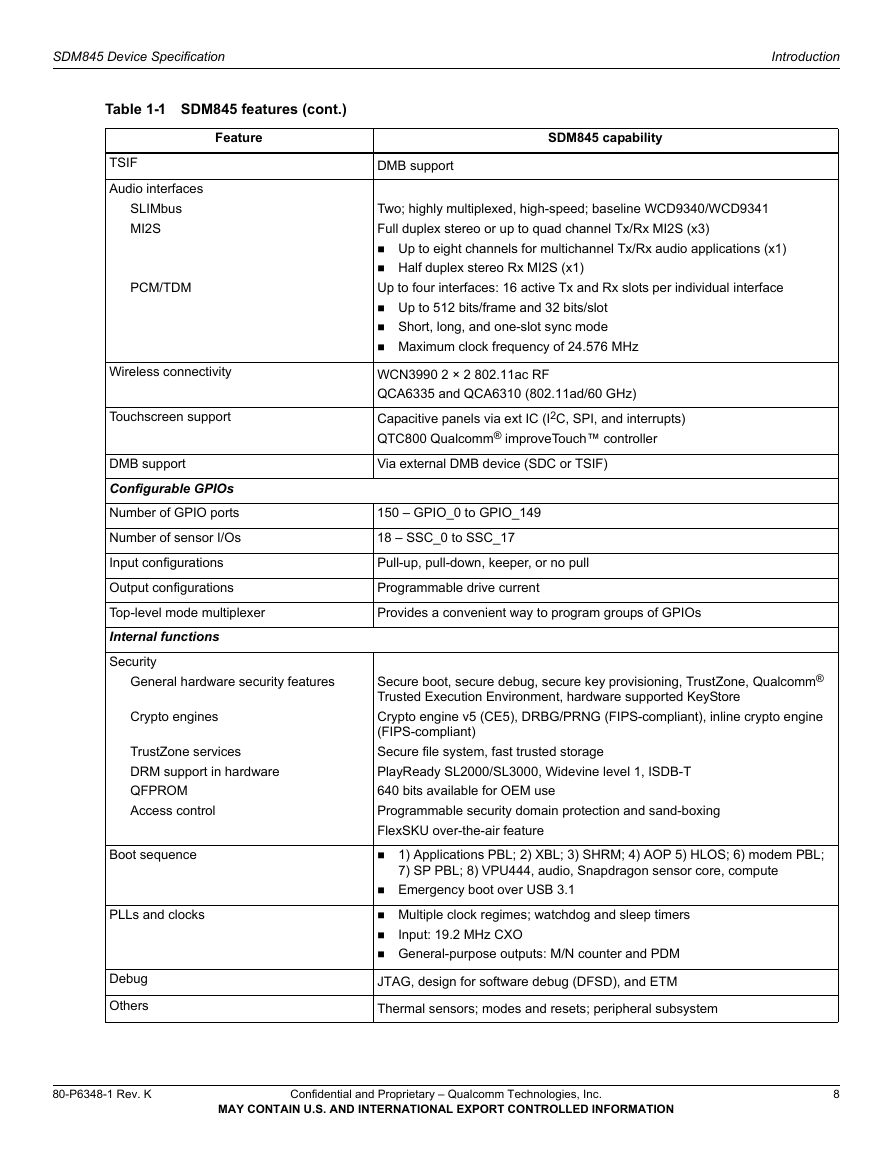

Table 1-1 SDM845 features (cont.)

Feature

SDM845 capability

DMB support

Two; highly multiplexed, high-speed; baseline WCD9340/WCD9341

Full duplex stereo or up to quad channel Tx/Rx MI2S (x3)

Up to eight channels for multichannel Tx/Rx audio applications (x1)

Half duplex stereo Rx MI2S (x1)

Up to four interfaces: 16 active Tx and Rx slots per individual interface

Up to 512 bits/frame and 32 bits/slot

Short, long, and one-slot sync mode

Maximum clock frequency of 24.576 MHz

WCN3990 2 × 2 802.11ac RF

QCA6335 and QCA6310 (802.11ad/60 GHz)

Capacitive panels via ext IC (I2C, SPI, and interrupts)

QTC800 Qualcomm® improveTouch™ controller

Via external DMB device (SDC or TSIF)

150 – GPIO_0 to GPIO_149

18 – SSC_0 to SSC_17

Pull-up, pull-down, keeper, or no pull

Programmable drive current

Provides a convenient way to program groups of GPIOs

Secure boot, secure debug, secure key provisioning, TrustZone, Qualcomm®

Trusted Execution Environment, hardware supported KeyStore

Crypto engine v5 (CE5), DRBG/PRNG (FIPS-compliant), inline crypto engine

(FIPS-compliant)

Secure file system, fast trusted storage

PlayReady SL2000/SL3000, Widevine level 1, ISDB-T

640 bits available for OEM use

Programmable security domain protection and sand-boxing

FlexSKU over-the-air feature

1) Applications PBL; 2) XBL; 3) SHRM; 4) AOP 5) HLOS; 6) modem PBL;

7) SP PBL; 8) VPU444, audio, Snapdragon sensor core, compute

Emergency boot over USB 3.1

Multiple clock regimes; watchdog and sleep timers

Input: 19.2 MHz CXO

General-purpose outputs: M/N counter and PDM

JTAG, design for software debug (DFSD), and ETM

Thermal sensors; modes and resets; peripheral subsystem

TSIF

Audio interfaces

SLIMbus

MI2S

PCM/TDM

Wireless connectivity

Touchscreen support

DMB support

Configurable GPIOs

Number of GPIO ports

Number of sensor I/Os

Input configurations

Output configurations

Top-level mode multiplexer

Internal functions

Security

General hardware security features

Crypto engines

TrustZone services

DRM support in hardware

QFPROM

Access control

Boot sequence

PLLs and clocks

Debug

Others

80-P6348-1 Rev. K

Confidential and Proprietary – Qualcomm Technologies, Inc.

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc