ATA6562/3

具有待机模式的高速CAN 收发器

特性

• 完全符合 ISO 11898-2、ISO 11898-2: 2016 和

SAE J2962-2 标准

• 符合CAN FD 标准

• 最高5 Mbps 的通信速度

• 低电磁辐射(Electromagnetic Emission,EME)

和 高 电 磁 抗 扰 度(Electromagnetic Immunity,

EMI)

• 具有宽共模范围的差分接收器

• ATA6562:静默模式

• 通 过 CAN 总 线 实 现 远 程 唤 醒 功 能 ——

ISO 11898-2: 2016 中指定的唤醒模式(Wake-Up

on Pattern,WUP),3.8 µs活动过滤时间

• 在所有电源条件下的功能行为均可预测:

• 收发器在未通电时脱离总线

• RXD隐性钳位检测

• 总 线 引 脚 具 有 较 高 的 静 电 放 电(Electrostatic

Discharge,ESD)处理能力

• 在汽车环境下对总线引脚进行瞬态保护

• 发送数据(Transmit Data,TXD)显性超时功能

• VCC和VIO引脚欠压检测

• CANH/CANL具有短路和过热保护

• 符合OEM“Hardware Requirements for LIN, CAN

and FlexRay Interfaces in Automotive Applications,

Rev. 1.3”

• 符合AEC-Q100要求

• 可选择两种环境温度等级:

- ATA6562-GAQW1、ATA6563-GAQW1、

ATA6562-GBQW1和ATA6563-GBQW1,最高

Tamb = +125°C

- ATA6562-GAQW0、ATA6563-GAQW0、

ATA6562-GBQW0和ATA6563-GBQW0,最高

Tamb = +150°C

• 封装:具有可润湿侧翼的 SOIC8 和 VDFN8(潮湿

敏感度1级)

应用

汽车、工业、航天、医疗和消费类应用中的经典CAN

和CAN FD 网络。

概述

ATA6562/ATA6563 是一款高速CAN 收发器,可在控制

器局域网(Controller Area Network,CAN)协议控制

器和物理双线CAN总线之间提供接口。

该收发器专为汽车行业的高速(最高5 Mbps)CAN

应 用 而 设 计, 为 具 有 CAN 协 议 控 制 器 的 单 片 机 提

供 差 分 发 送 和 接 收 功 能。它 能 够 改 进 电 磁 兼 容 性

(ElectroMagnetic Compatibility,EMC)和静电放电

(ESD)性能,并且具有以下特性:

• 当电源电压关闭时,CAN总线表现出理想的无源

行为

• 直 接 连 接 到 电 源 电 压 为 3V 至 5V 的 单 片 机

(ATA6563)

ATA6562/ATA6563 具有三种工作模式以及专用故障保

护功能,是所有类型的高速CAN 网络的理想选择,对

于需要低功耗模式(通过CAN 总线唤醒)的节点更是

如此。

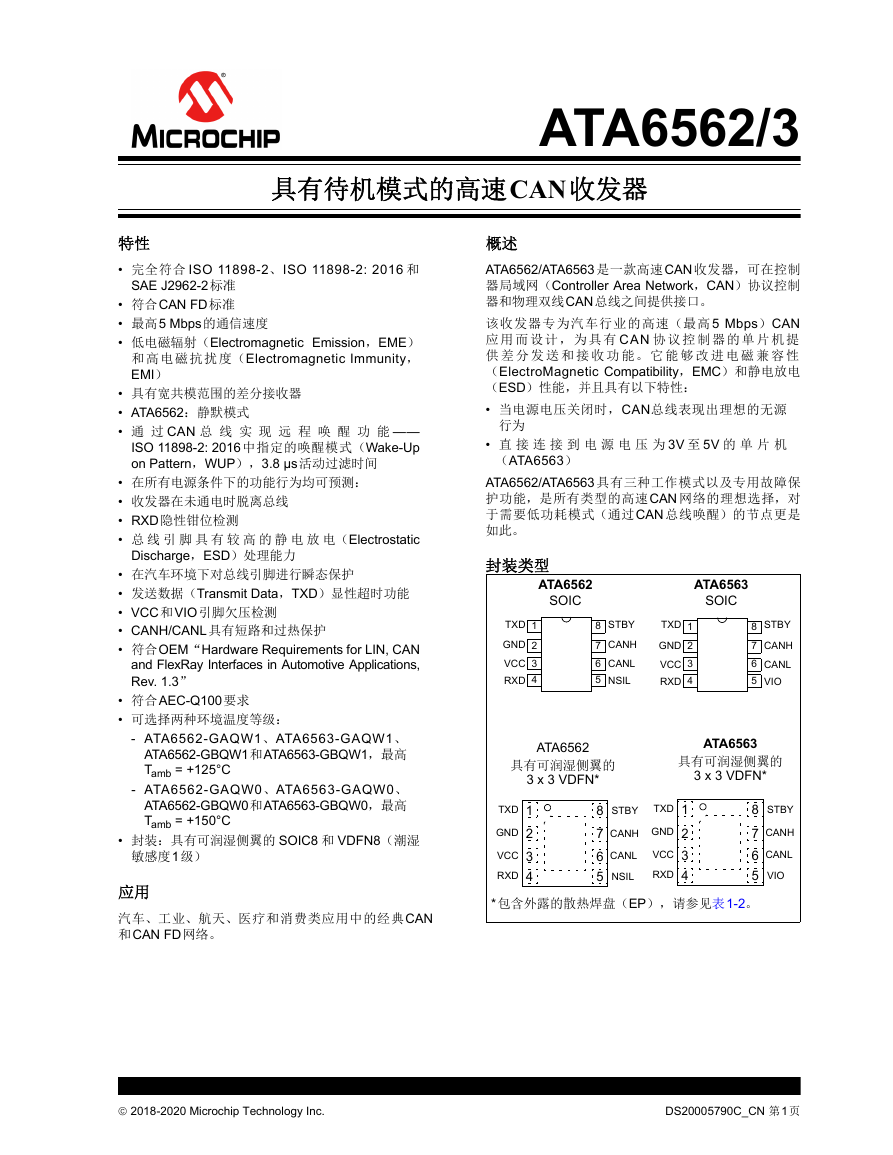

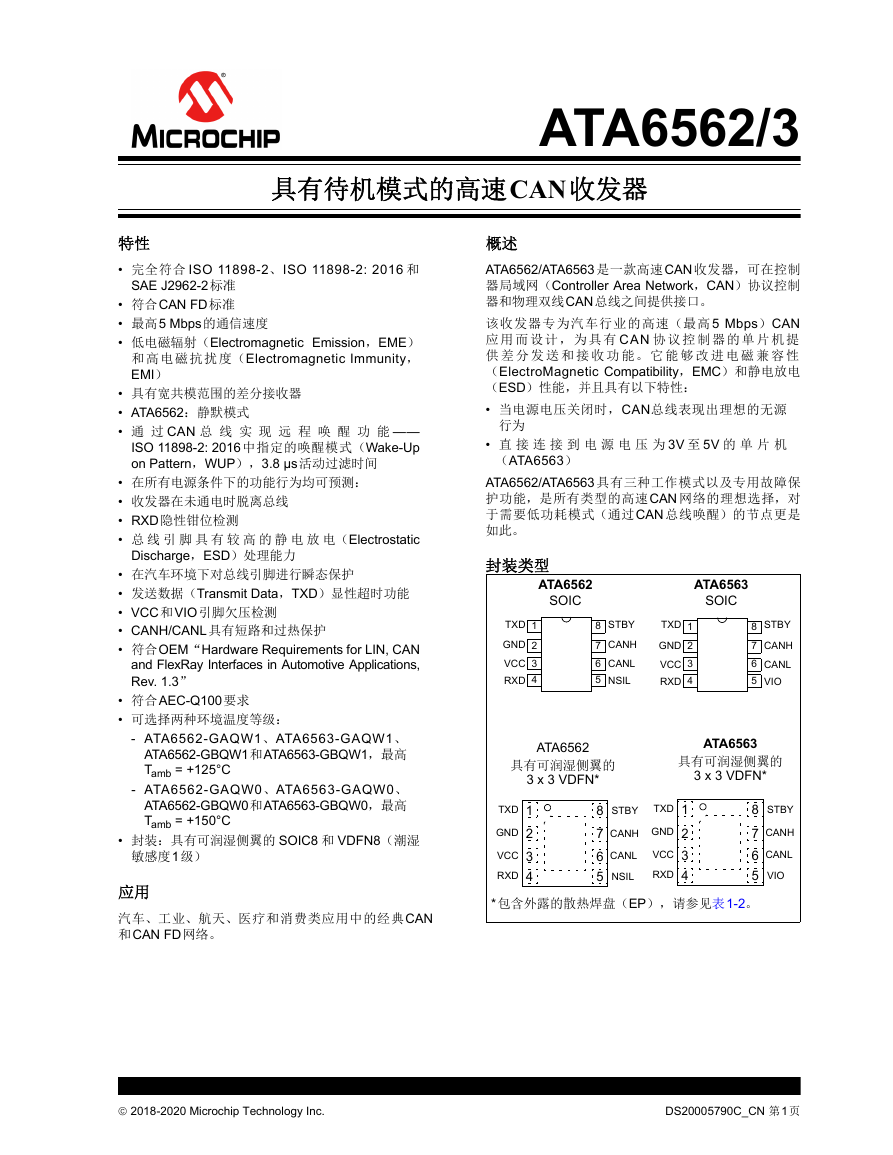

封装类型

ATA6562

SOIC

ATA6563

SOIC

TXD

GND

VCC

RXD

1

2

3

4

STBY

8

CANH

7

6

CANL

5 NSIL

TXD

GND

VCC

RXD

1

2

3

4

STBY

CANH

CANL

8

7

6

5 VIO

ATA6562

具有可润湿侧翼的

3 x 3 VDFN*

ATA6563

具有可润湿侧翼的

3 x 3 VDFN*

TXD 1

2

GND

3

4

VCC

RXD

8

7

6

5

STBY

CANH

CANL

NSIL

TXD 1

2

GND

3

4

VCC

RXD

8

7

6

5

STBY

CANH

CANL

VIO

*包含外露的散热焊盘(EP),请参见表1-2。

2018-2020 Microchip Technology Inc.

DS20005790C_CN 第1 页

�

ATA6562/3

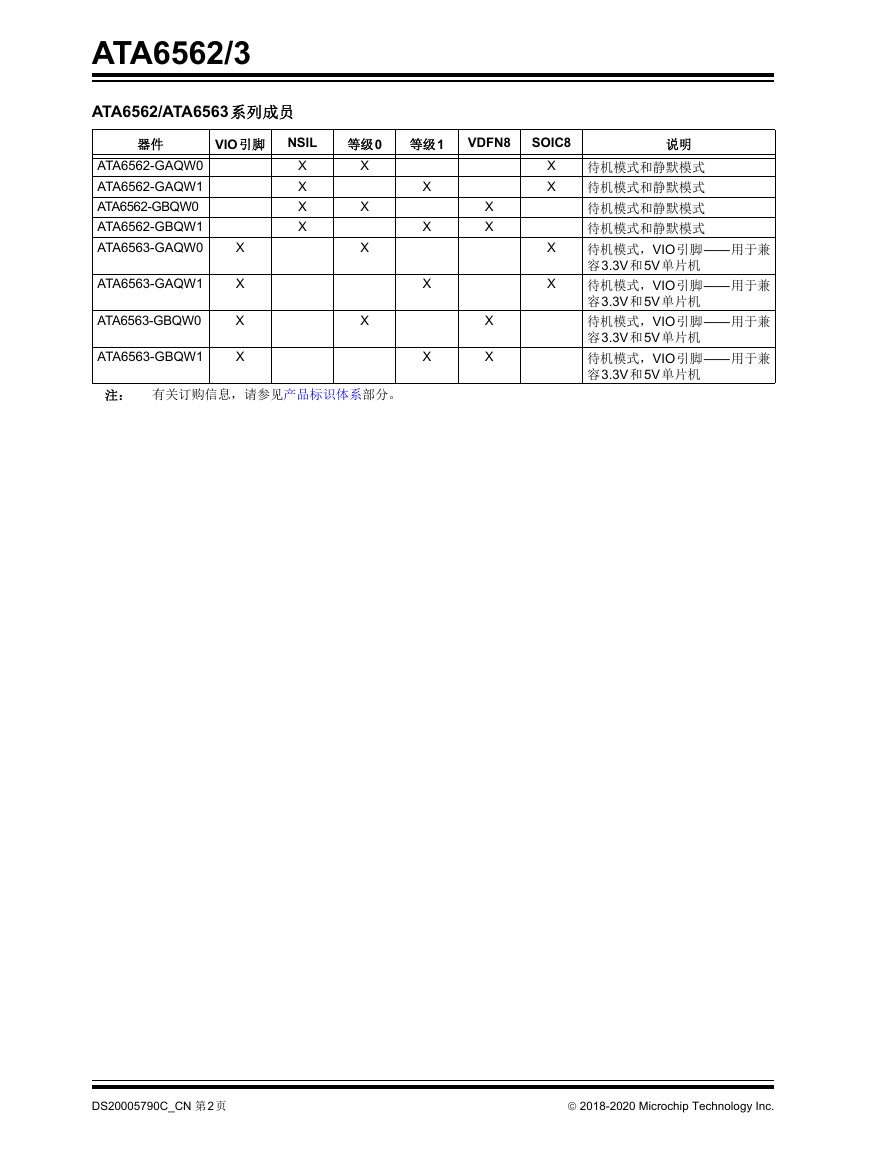

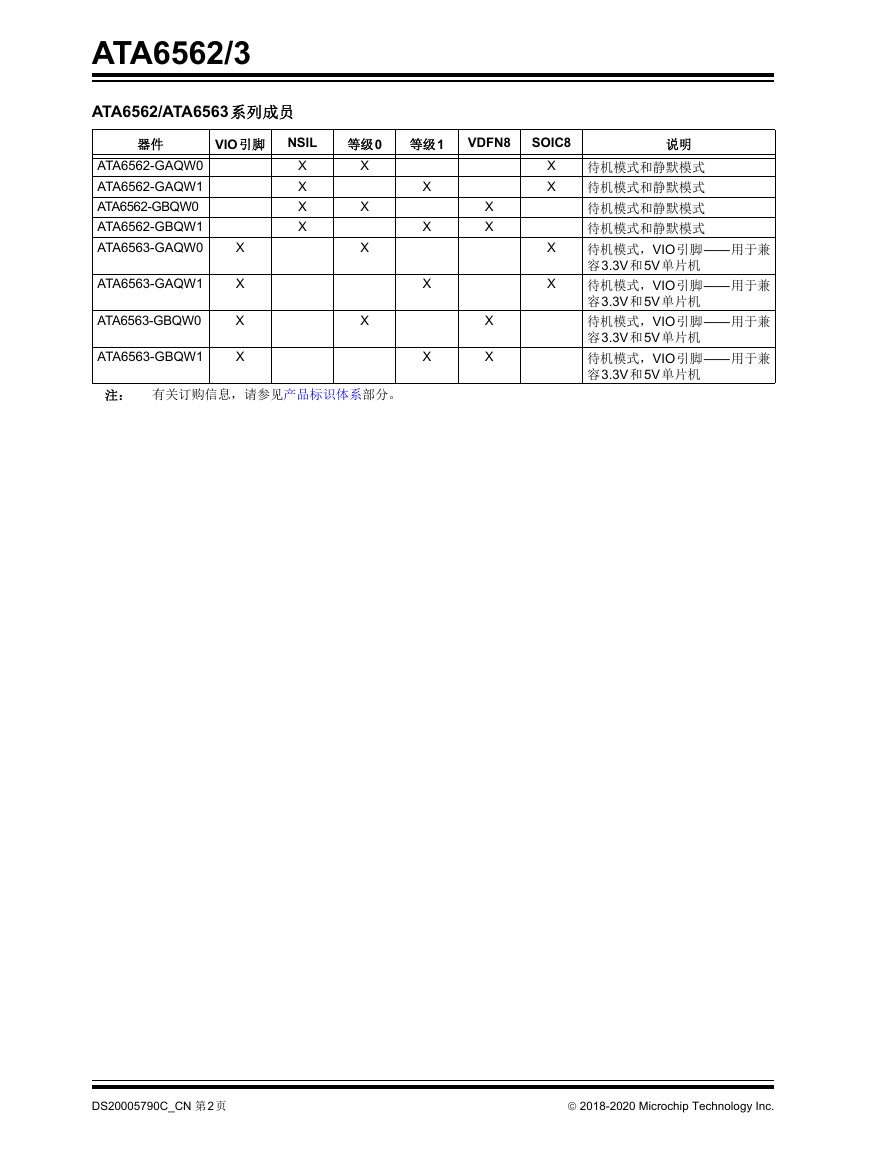

ATA6562/ATA6563 系列成员

器件

VIO 引脚 NSIL

等级0

等级1

VDFN8

SOIC8

说明

ATA6562-GAQW0

ATA6562-GAQW1

ATA6562-GBQW0

ATA6562-GBQW1

ATA6563-GAQW0

ATA6563-GAQW1

ATA6563-GBQW0

ATA6563-GBQW1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

注: 有关订购信息,请参见产品标识体系部分。

X

X

X

X

待机模式和静默模式

待机模式和静默模式

待机模式和静默模式

待机模式和静默模式

待机模式,VIO引脚——用于兼

容3.3V 和5V单片机

待机模式,VIO引脚——用于兼

容3.3V 和5V单片机

待机模式,VIO引脚——用于兼

容3.3V 和5V单片机

待机模式,VIO引脚——用于兼

容3.3V 和5V单片机

DS20005790C_CN 第2 页

2018-2020 Microchip Technology Inc.

�

ATA6562/3

V

5(1)

V

3

VCC

Temperature

温度保护

Protection

TXD

TXD

Time-Out-

超时定时器

Timer

Slope Control

斜率控制和

and

驱动器

Driver

7

6

CANH

CANL

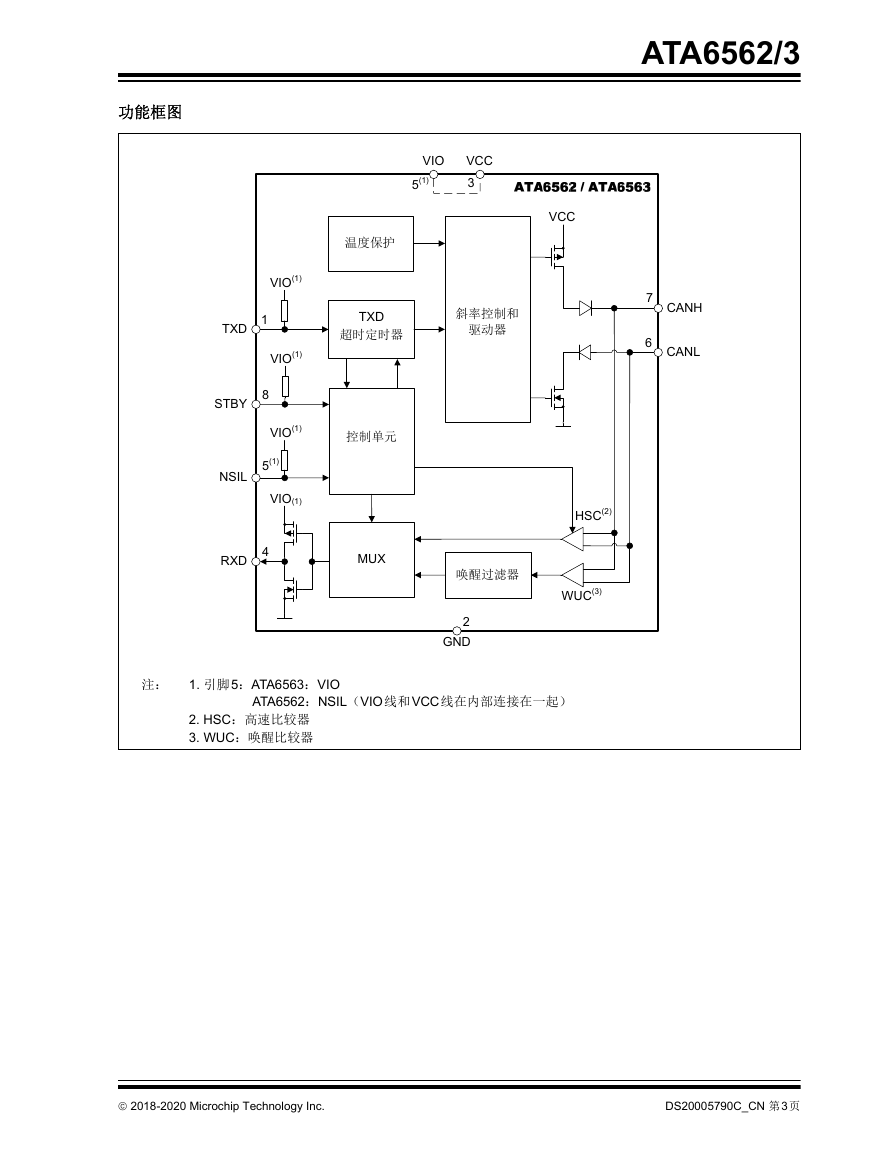

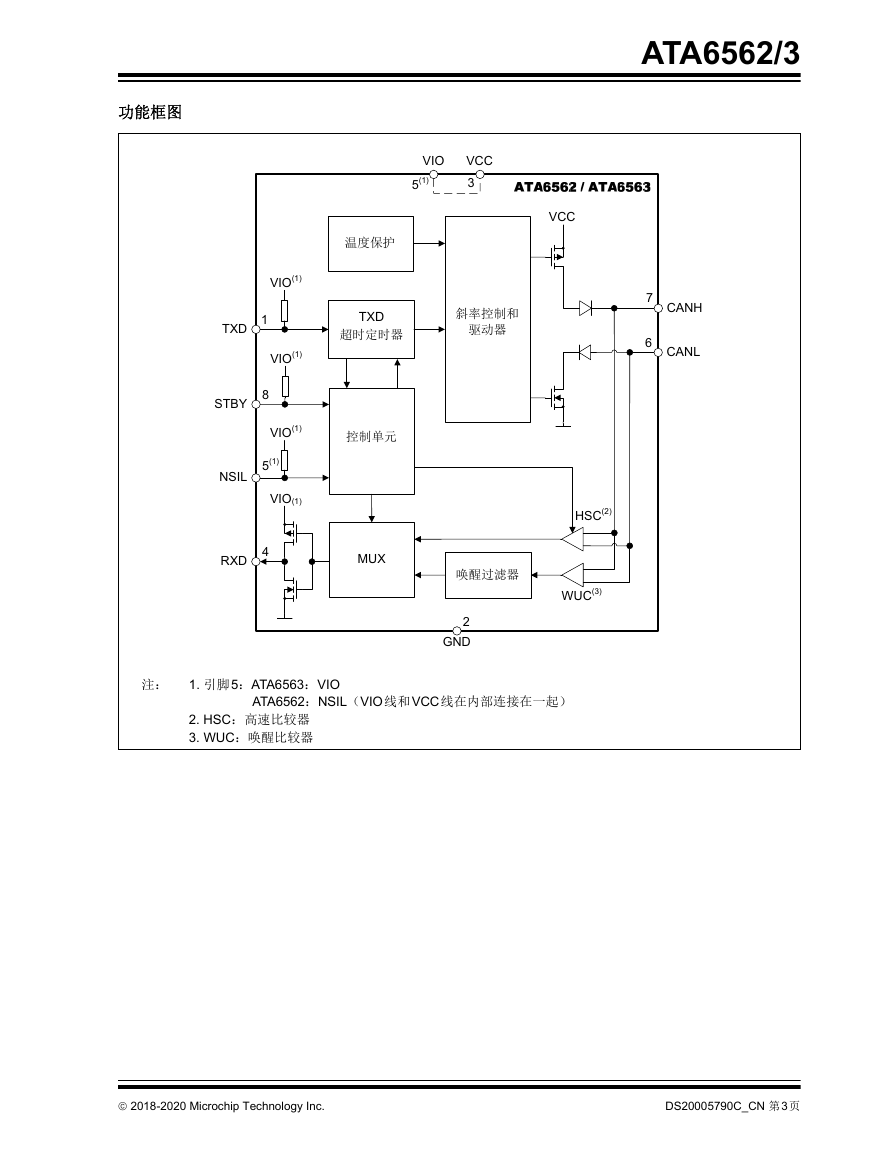

功能框图

VIO(1)

VIO(1)

1

8

TXD

STBY

VIO(1)

控制单元

Control Unit

5(1)

NSIL

VIO(

4

RXD

MUX

HSC(2)

WUC(3)

Wake-up

唤醒过滤器

Filter

2

GND

注: 1. 引脚5:ATA6563:VIO

ATA6562:NSIL(VIO 线和VCC线在内部连接在一起)

2. HSC:高速比较器

3. WUC:唤醒比较器

2018-2020 Microchip Technology Inc.

DS20005790C_CN 第3 页

�

ATA6562/3

1.0 功能说明

ATA6562/ATA6563是一款独立的双路高速CAN收发器,

符合ISO 11898-2、ISO 11898-2: 2016、ISO 11898-5

和SAE J2962-2 CAN 标准。它在待机模式下的电流消

耗极低,并通过 CAN 总线实现唤醒功能。该器件提

供两个版本,这两个版本的惟一差别在于引脚5 的功能

不同:

• ATA6562:引脚5是静默模式NSIL的控制输入,允

许ATA6562 只通过总线接收数据但不发送数据。

输出驱动器级被禁止。VIO线和VCC线在内部连接

在一起,这会将TXD、RXD、STBY和NSIL引脚的

信号电平设置为与5V单片机兼容的电平。

• ATA6563:引脚 5 是 VIO 引脚,应与单片机电源电

压连接。这样就能直接连接到电源电压低至3V的单

片机,并将TXD、RXD 和STBY 引脚的信号电平调

整为单片机的I/O电平。I/O端口由VIO引脚供电。

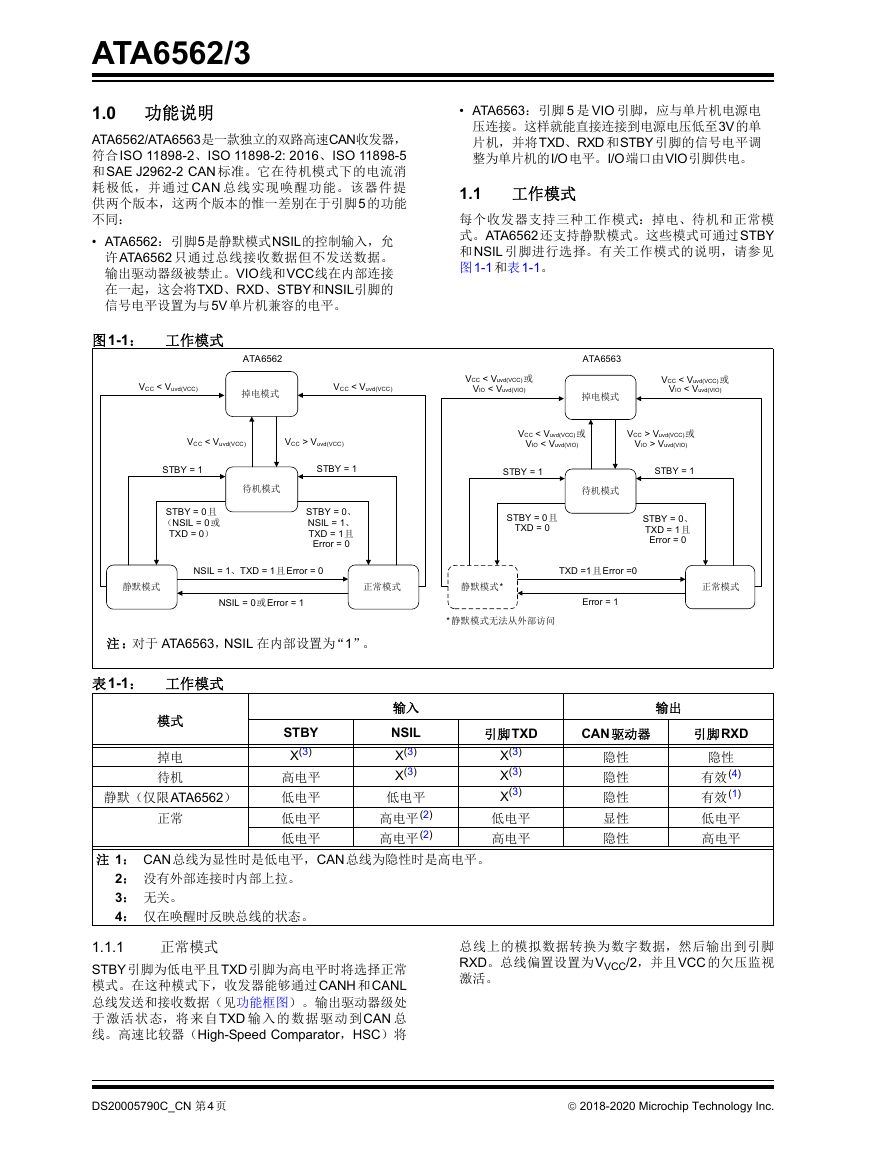

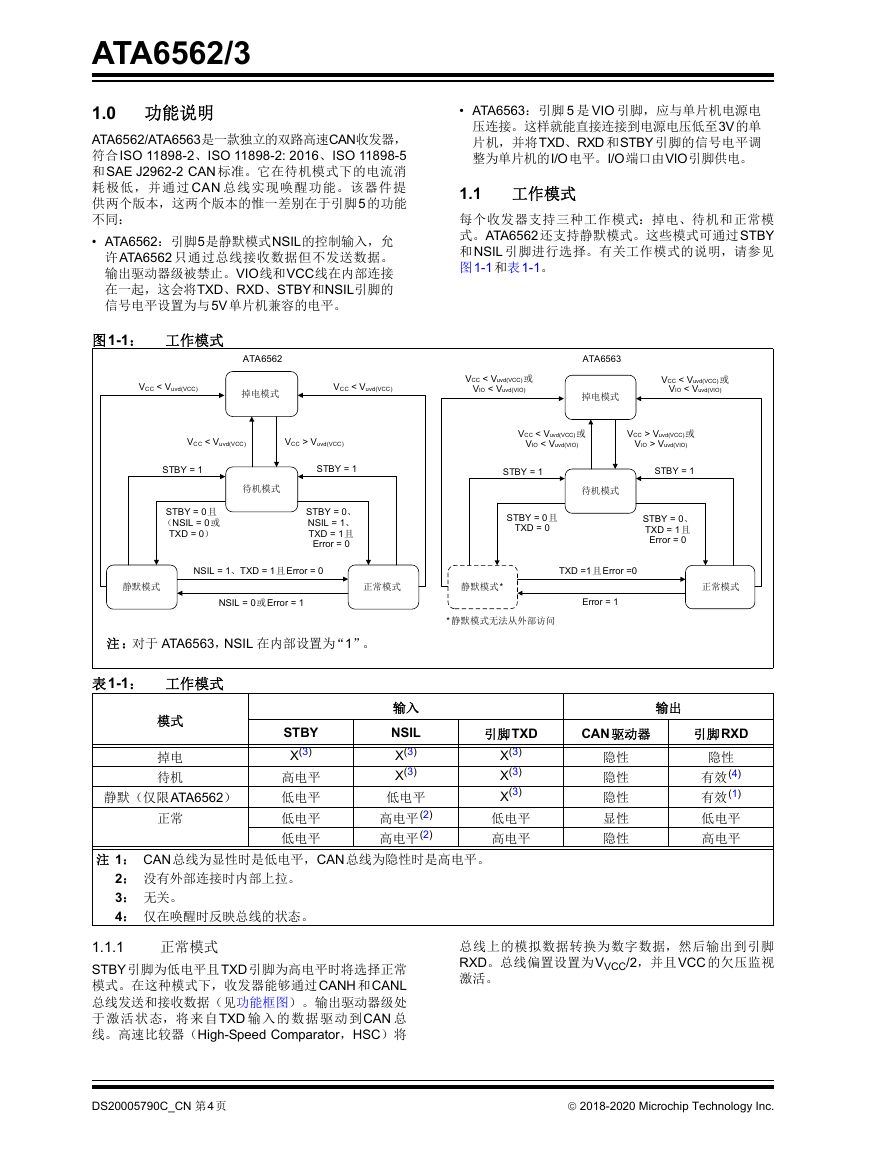

1.1 工作模式

每个收发器支持三种工作模式:掉电、待机和正常模

式。ATA6562 还支持静默模式。这些模式可通过STBY

和NSIL 引脚进行选择。有关工作模式的说明,请参见

图1-1 和表1-1。

图1-1: 工作模式

VCC < Vuvd(VCC)

ATA6562

Unpowered

掉电模式

Mode

VCC < Vuvd(VCC)

VCC < Vuvd(VCC) or

VCC < Vuvd(VCC) 或

VIO < Vuvd(VIO)

VIO < Vuvd(VIO)

ATA6563

Unpowered

掉电模式

Mode

VCC < Vuvd(VCC) or

VCC < Vuvd(VCC) 或

VIO < Vuvd(VIO)

VIO < Vuvd(VIO)

VCC < Vuvd(VCC)

VCC > Vuvd(VCC)

STBY = 1

STBY = 1

Standby

待机模式

Mode

STBY = 0 and

STBY = 0 且

(NSIL = 0 or

(NSIL = 0 或

TXD = 0)

TXD = 0)

STBY = 0 and

STBY = 0、

NSIL = 1、

NSIL = 1 and

TXD = 1 且

TXD = 1 and

Error = 0

Error = 0

VCC < Vuvd(VCC) or

VCC < Vuvd(VCC) 或

VIO < Vuvd(VIO)

VIO < Vuvd(VIO)

VCC > Vuvd(VCC) or

VCC > Vuvd(VCC)或

VIO > Vuvd(VIO)

VIO > Vuvd(VIO)

STBY = 1

STBY = 1

Standby

待机模式

Mode

STBY = 0 且

STBY = 0 and

TXD = 0

TXD = 0

STBY = 0、

STBY = 0 and

TXD = 1 且

TXD = 1 and

Error = 0

Error = 0

Silent

Mode

静默模式

NSIL = 1 and TXD = 1 and Error = 0

NSIL = 1、TXD = 1且Error = 0

NSIL = 0 or Error = 1

NSIL = 0 或Error = 1

Normal

正常模式

Mode

Silent

静默模式*

Mode *

TXD =1 且Error =0

TXD = 1 and Error = 0

Error = 1

Normal

正常模式

Mode

* 静默模式无法从外部访问

* Silent ode is externally not accessible

注 :对于 ATA6563,NSIL 在内部设置为“1”。

表1-1: 工作模式

模式

掉电

待机

静默(仅限ATA6562)

正常

STBY

X(3)

高电平

低电平

低电平

低电平

输入

NSIL

X(3)

X(3)

低电平

高电平(2)

高电平(2)

引脚TXD

CAN驱动器

引脚RXD

输出

X(3)

X(3)

X(3)

低电平

高电平

隐性

隐性

隐性

显性

隐性

隐性

有效(4)

有效(1)

低电平

高电平

注 1: CAN总线为显性时是低电平,CAN总线为隐性时是高电平。

2: 没有外部连接时内部上拉。

3: 无关。

4: 仅在唤醒时反映总线的状态。

正常模式

1.1.1

STBY 引脚为低电平且TXD 引脚为高电平时将选择正常

模式。在这种模式下,收发器能够通过CANH 和CANL

总线发送和接收数据(见功能框图)。输出驱动器级处

于激活状态,将来自TXD 输入的数据驱动到CAN 总

线。高速比较器(High-Speed Comparator,HSC)将

总线上的模拟数据转换为数字数据,然后输出到引脚

RXD。总线偏置设置为VVCC/2,并且VCC 的欠压监视

激活。

DS20005790C_CN 第4 页

2018-2020 Microchip Technology Inc.

�

ATA6562/3

总线上输出信号的斜率得到控制和优化,确保实现最低

的电磁辐射(EME)。

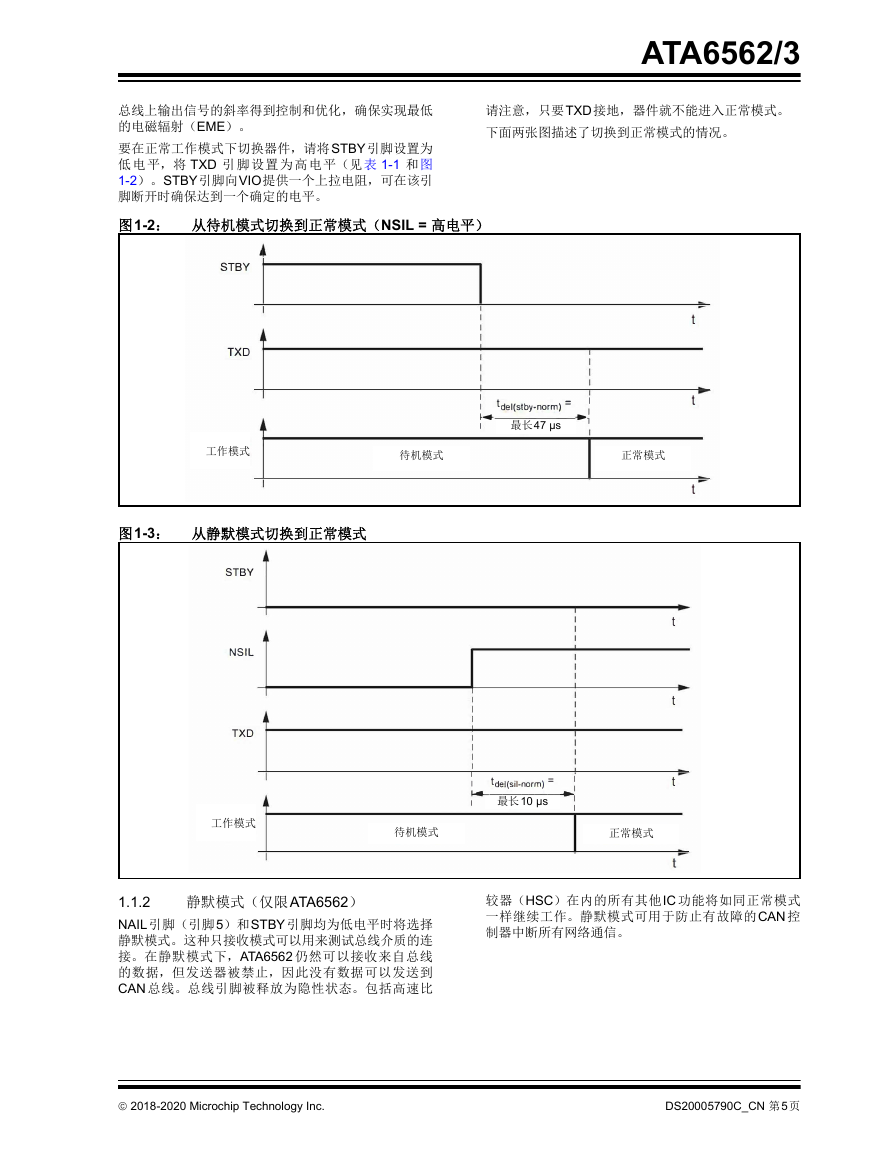

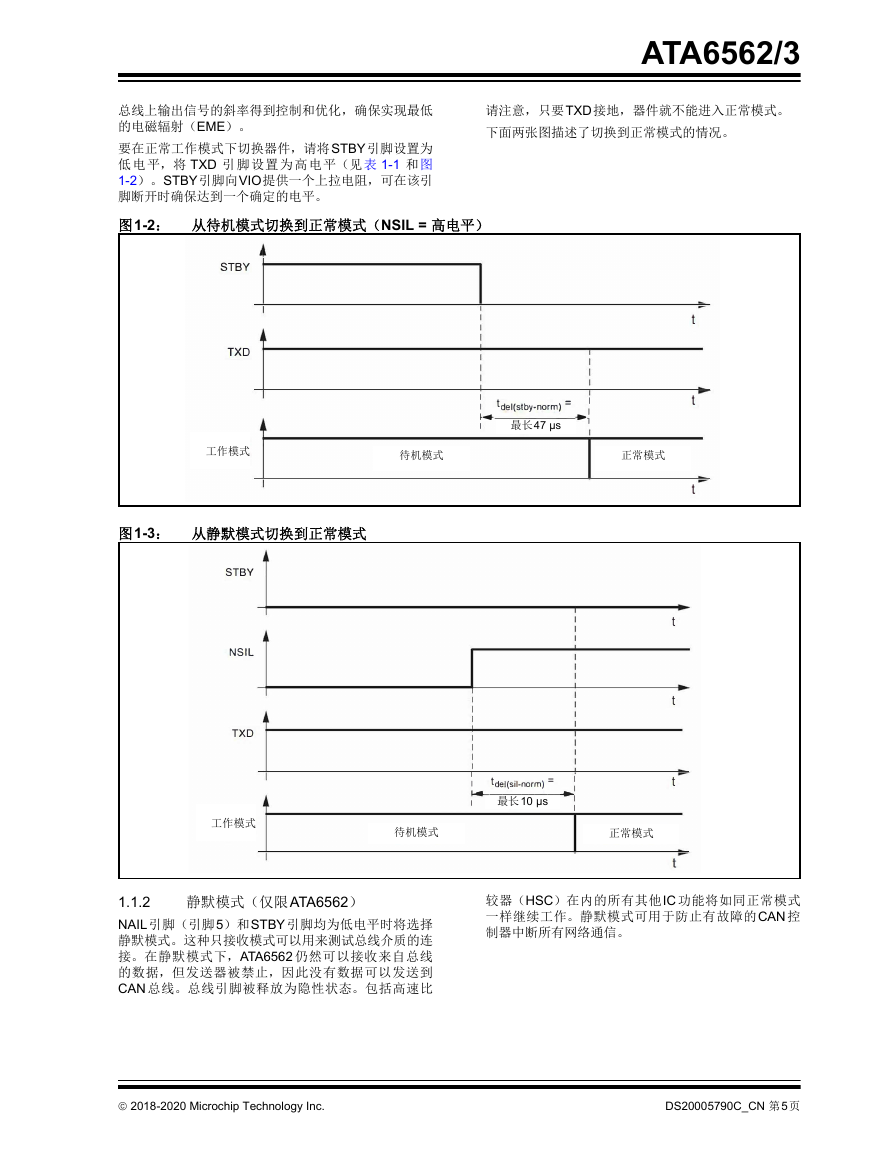

要在正常工作模式下切换器件,请将STBY 引脚设置为

低电平,将 TXD 引脚设置为高电平(见表 1-1 和图

1-2)。STBY引脚向VIO提供一个上拉电阻,可在该引

脚断开时确保达到一个确定的电平。

图1-2: 从待机模式切换到正常模式(NSIL = 高电平)

请注意,只要TXD 接地,器件就不能进入正常模式。

下面两张图描述了切换到正常模式的情况。

工作模式

最长47 μs

待机模式

正常模式

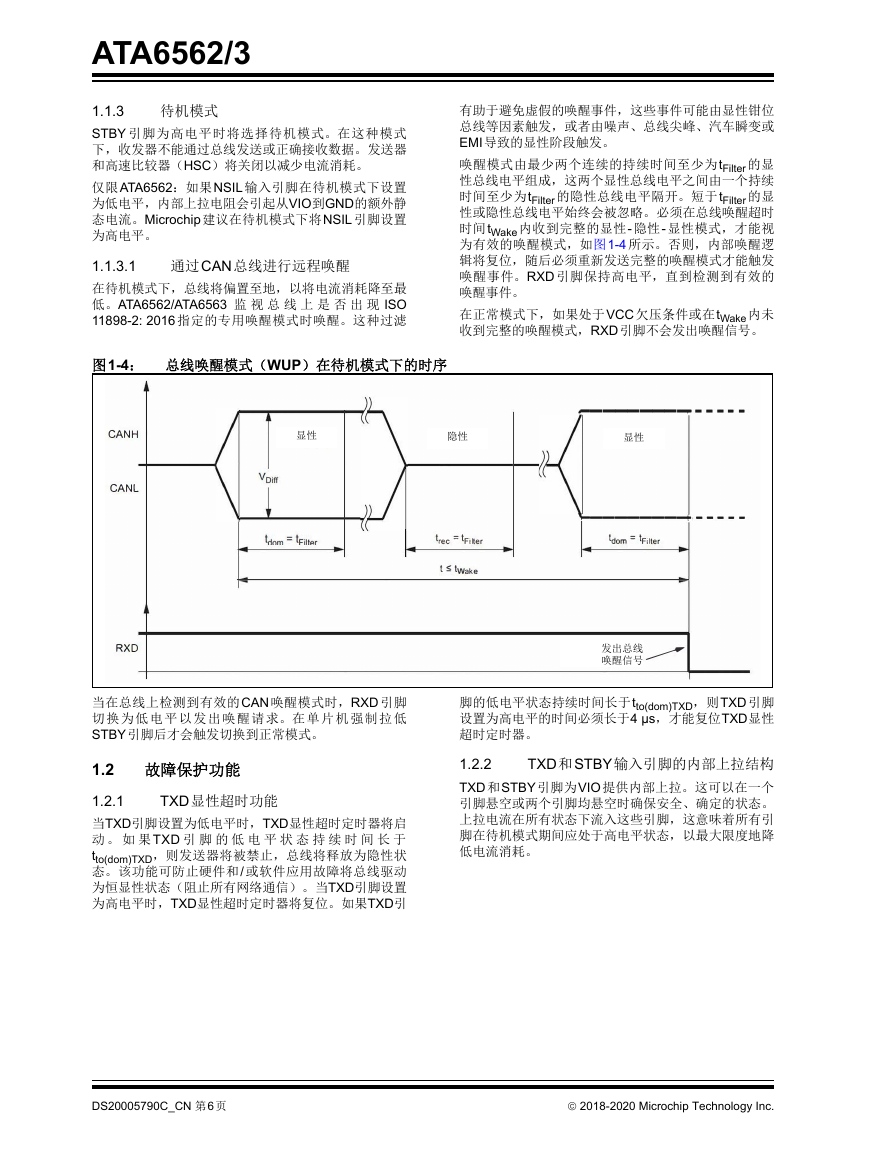

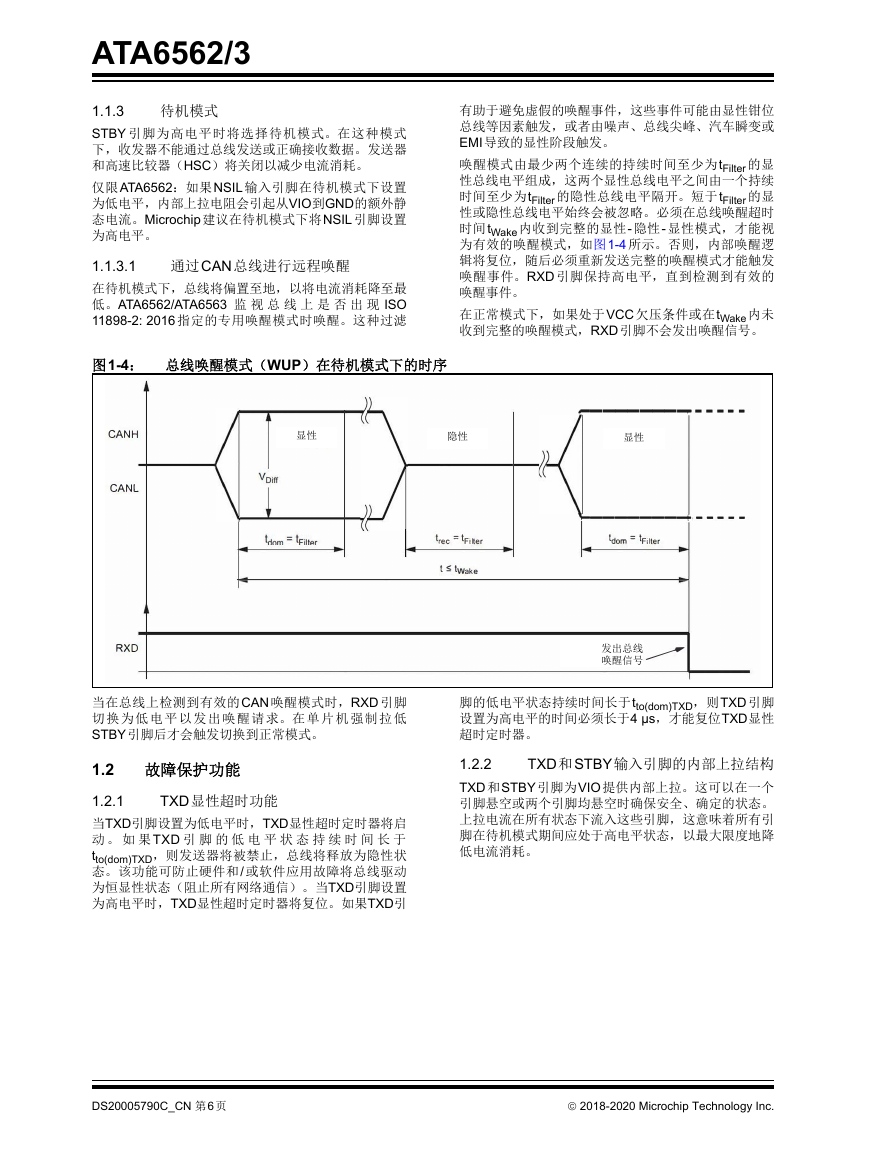

图1-3: 从静默模式切换到正常模式

工作模式

最长10 μs

待机模式

正常模式

静默模式(仅限ATA6562)

1.1.2

NAIL 引脚(引脚5)和STBY 引脚均为低电平时将选择

静默模式。这种只接收模式可以用来测试总线介质的连

接。在静默模式下,ATA6562 仍然可以接收来自总线

的数据,但发送器被禁止,因此没有数据可以发送到

CAN 总线。总线引脚被释放为隐性状态。包括高速比

较器(HSC)在内的所有其他IC 功能将如同正常模式

一样继续工作。静默模式可用于防止有故障的CAN 控

制器中断所有网络通信。

2018-2020 Microchip Technology Inc.

DS20005790C_CN 第5 页

�

ATA6562/3

待机模式

1.1.3

STBY 引脚为高电平时将选择待机模式。在这种模式

下,收发器不能通过总线发送或正确接收数据。发送器

和高速比较器(HSC)将关闭以减少电流消耗。

仅限ATA6562:如果NSIL 输入引脚在待机模式下设置

为低电平,内部上拉电阻会引起从VIO到GND的额外静

态电流。Microchip 建议在待机模式下将NSIL 引脚设置

为高电平。

通过CAN 总线进行远程唤醒

1.1.3.1

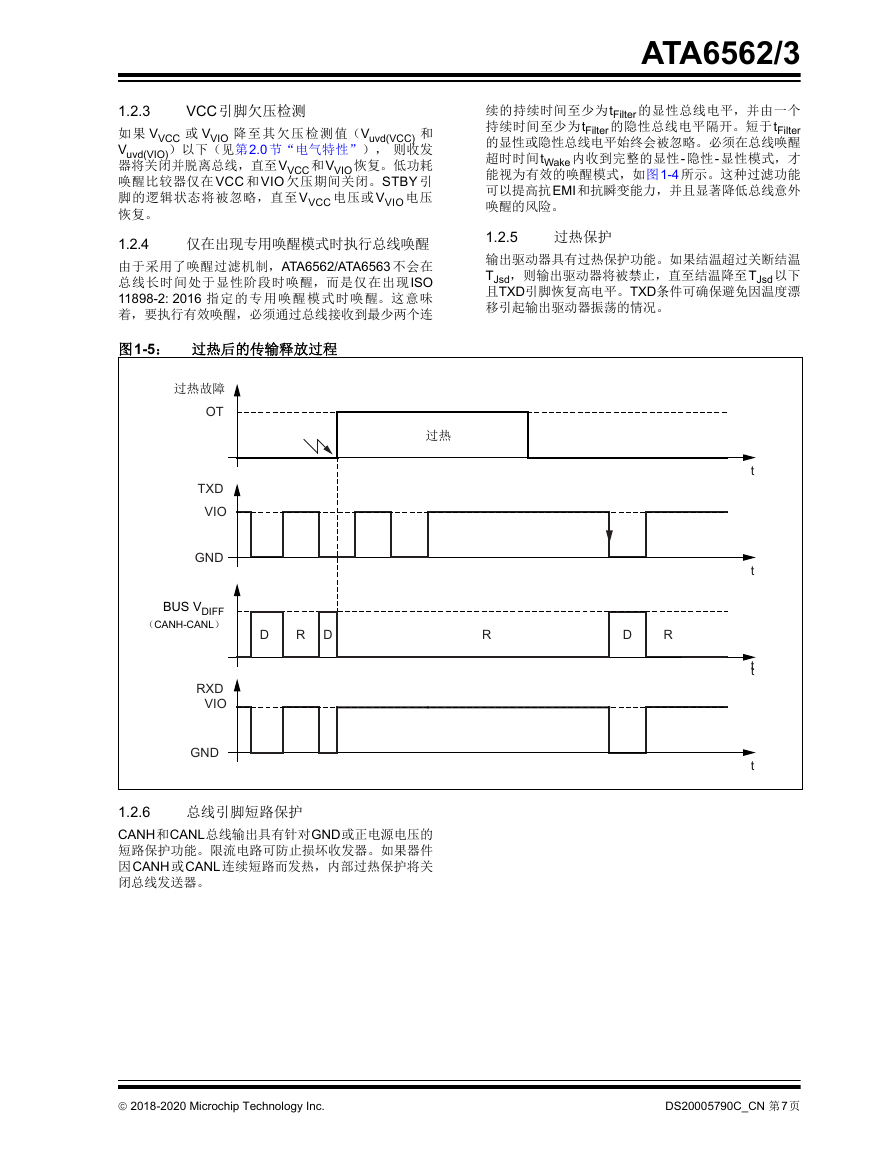

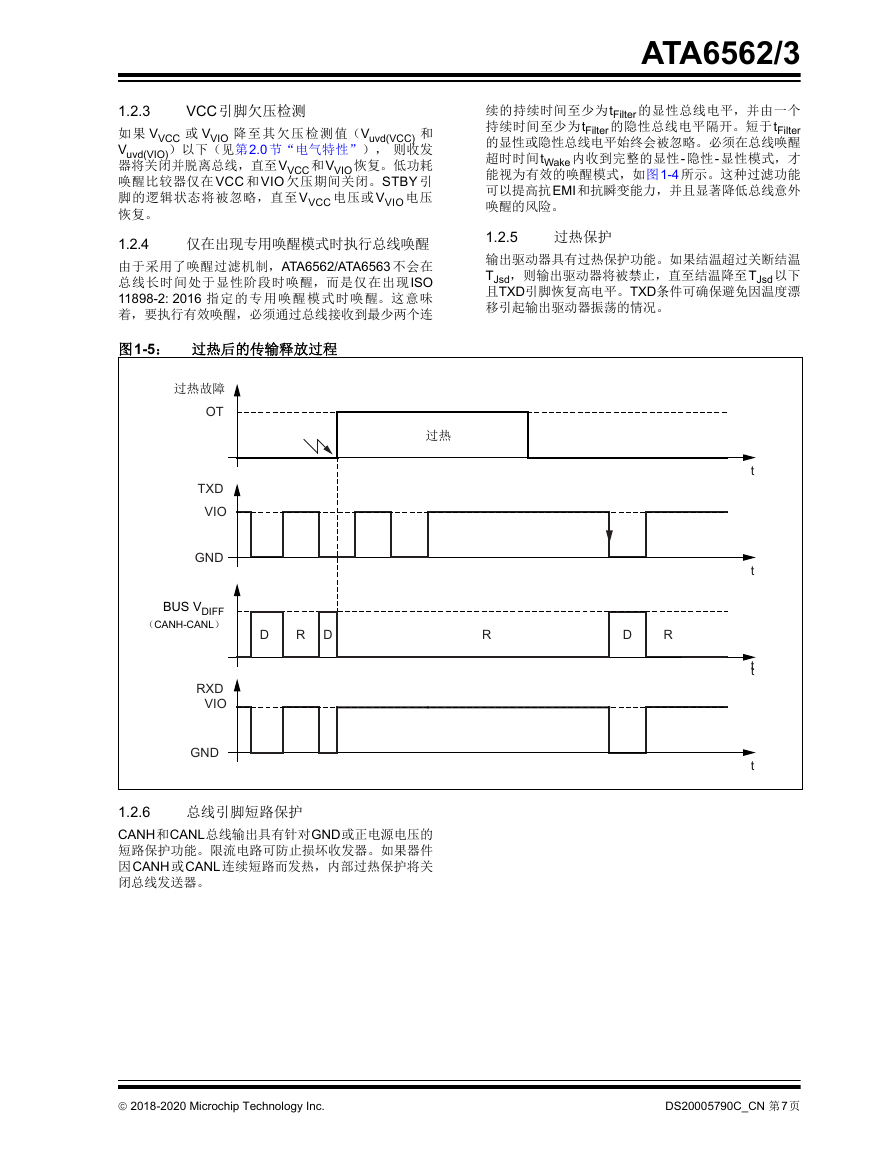

在待机模式下,总线将偏置至地,以将电流消耗降至最

低。ATA6562/ATA6563 监 视 总 线 上 是 否 出 现 ISO

11898-2: 2016 指定的专用唤醒模式时唤醒。这种过滤

图1-4: 总线唤醒模式(WUP)在待机模式下的时序

有助于避免虚假的唤醒事件,这些事件可能由显性钳位

总线等因素触发,或者由噪声、总线尖峰、汽车瞬变或

EMI导致的显性阶段触发。

唤醒模式由最少两个连续的持续时间至少为tFilter 的显

性总线电平组成,这两个显性总线电平之间由一个持续

时间至少为tFilter 的隐性总线电平隔开。短于tFilter 的显

性或隐性总线电平始终会被忽略。必须在总线唤醒超时

时间tWake 内收到完整的显性- 隐性- 显性模式,才能视

为有效的唤醒模式,如图1-4 所示。否则,内部唤醒逻

辑将复位,随后必须重新发送完整的唤醒模式才能触发

唤醒事件。RXD 引脚保持高电平,直到检测到有效的

唤醒事件。

在正常模式下,如果处于VCC 欠压条件或在tWake 内未

收到完整的唤醒模式,RXD引脚不会发出唤醒信号。

显性

隐性

显性

发出总线

唤醒信号

当在总线上检测到有效的CAN 唤醒模式时,RXD 引脚

切 换为 低 电 平 以发 出 唤 醒 请求。在 单 片 机 强 制 拉 低

STBY引脚后才会触发切换到正常模式。

脚的低电平状态持续时间长于tto(dom)TXD,则TXD 引脚

设置为高电平的时间必须长于4 µs,才能复位TXD显性

超时定时器。

TXD 显性超时功能

1.2 故障保护功能

1.2.1

当TXD引脚设置为低电平时,TXD显性超时定时器将启

动 。 如 果TXD 引 脚 的 低 电 平 状 态 持 续 时 间 长 于

tto(dom)TXD,则发送器将被禁止,总线将释放为隐性状

态。该功能可防止硬件和/ 或软件应用故障将总线驱动

为恒显性状态(阻止所有网络通信)。当TXD引脚设置

为高电平时,TXD显性超时定时器将复位。如果TXD引

TXD 和STBY 输入引脚的内部上拉结构

1.2.2

TXD 和STBY 引脚为VIO 提供内部上拉。这可以在一个

引脚悬空或两个引脚均悬空时确保安全、确定的状态。

上拉电流在所有状态下流入这些引脚,这意味着所有引

脚在待机模式期间应处于高电平状态,以最大限度地降

低电流消耗。

DS20005790C_CN 第6 页

2018-2020 Microchip Technology Inc.

�

VCC 引脚欠压检测

1.2.3

如果 VVCC 或 VVIO 降至其欠压检测值(Vuvd(VCC) 和

Vuvd(VIO))以下(见第2.0 节“电气特性”), 则收发

器将关闭并脱离总线,直至VVCC 和VVIO 恢复。低功耗

唤醒比较器仅在VCC 和VIO 欠压期间关闭。STBY 引

脚的逻辑状态将被忽略,直至VVCC 电压或VVIO 电压

恢复。

1.2.4

仅在出现专用唤醒模式时执行总线唤醒

由于采用了唤醒过滤机制,ATA6562/ATA6563 不会在

总线长时间处于显性阶段时唤醒,而是仅在出现ISO

11898-2: 2016 指定的专用唤醒模式时唤醒。这 意 味

着,要执行有效唤醒,必须通过总线接收到最少两个连

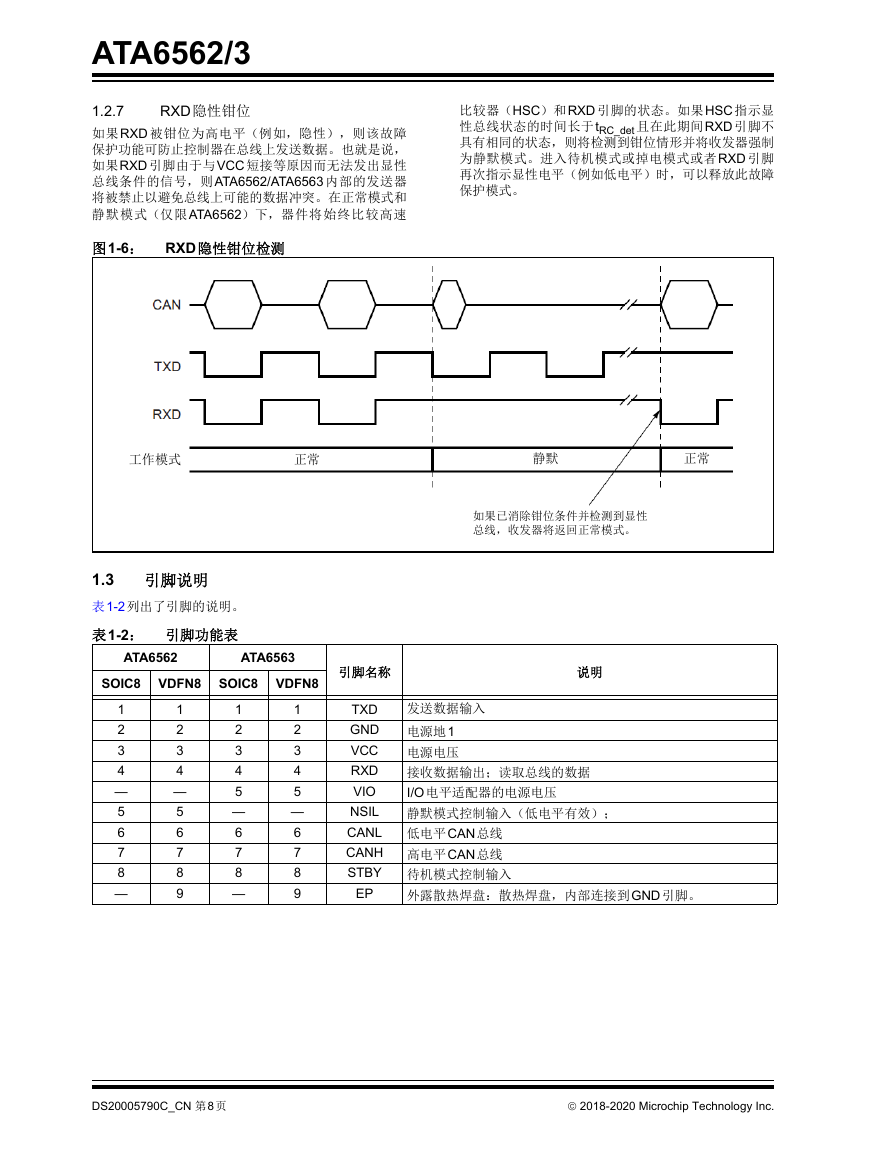

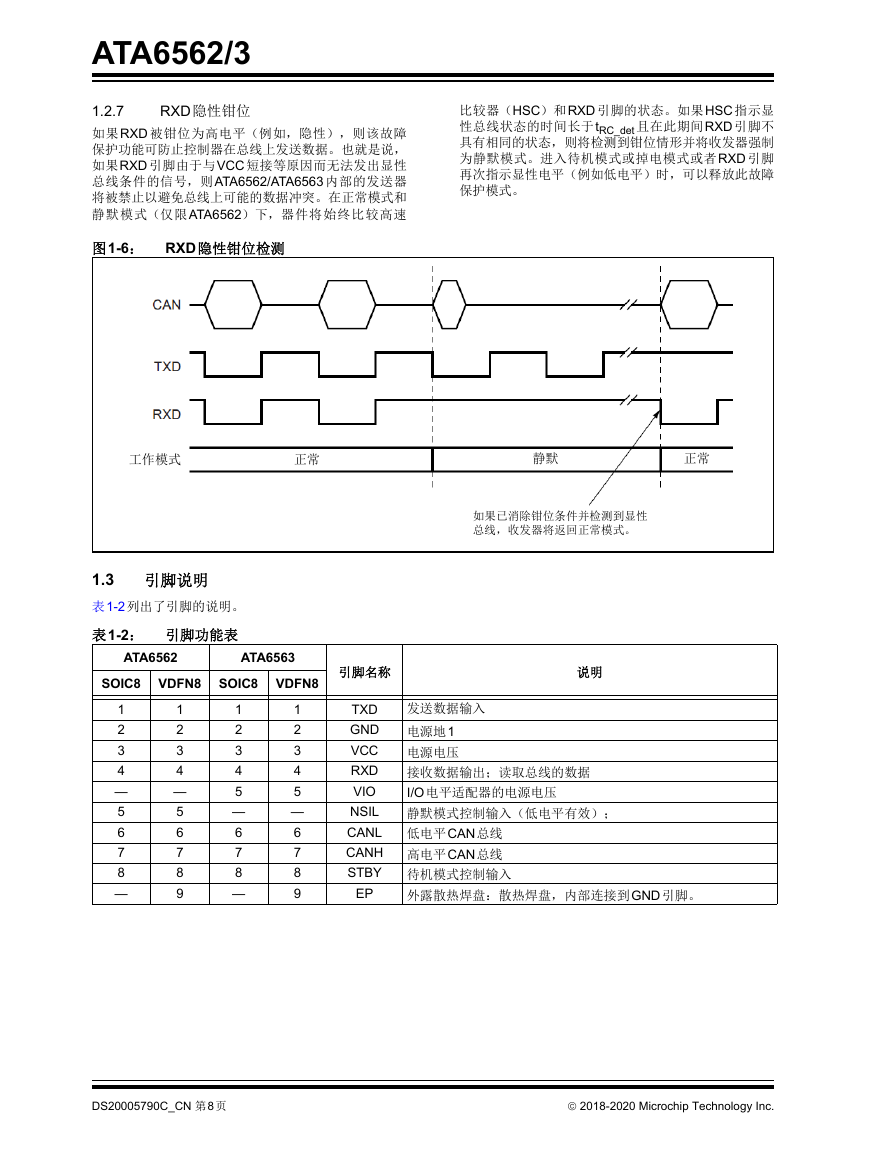

图1-5: 过热后的传输释放过程

ATA6562/3

续的持续时间至少为tFilter 的显性总线电平,并由一个

持续时间至少为tFilter 的隐性总线电平隔开。短于tFilter

的显性或隐性总线电平始终会被忽略。必须在总线唤醒

超时时间tWake 内收到完整的显性- 隐性- 显性模式,才

能视为有效的唤醒模式,如图1-4 所示。这种过滤功能

可以提高抗EMI 和抗瞬变能力,并且显著降低总线意外

唤醒的风险。

过热保护

1.2.5

输出驱动器具有过热保护功能。如果结温超过关断结温

TJsd,则输出驱动器将被禁止,直至结温降至TJsd 以下

且TXD引脚恢复高电平。TXD条件可确保避免因温度漂

移引起输出驱动器振荡的情况。

Failure

Overtemp

过热故障

OT

TXD

VIO

GND

BUS VDIFF

BUS VDIFF

(CANH-CANL)

(CANH-CANL)

RXD

VIO

GND

Overtemperature

过热

D

R D

R

D

R

t

t

t

t

t

总线引脚短路保护

1.2.6

CANH和CANL总线输出具有针对GND或正电源电压的

短路保护功能。限流电路可防止损坏收发器。如果器件

因CANH 或CANL 连续短路而发热,内部过热保护将关

闭总线发送器。

2018-2020 Microchip Technology Inc.

DS20005790C_CN 第7 页

�

ATA6562/3

RXD 隐性钳位

1.2.7

如果RXD 被钳位为高电平(例如,隐性),则该故障

保护功能可防止控制器在总线上发送数据。也就是说,

如果RXD 引脚由于与VCC 短接等原因而无法发出显性

总线条件的信号,则ATA6562/ATA6563 内部的发送器

将被禁止以避免总线上可能的数据冲突。在正常模式和

静默模式(仅限ATA6562)下,器件将始终比较高速

图1-6: RXD 隐性钳位检测

比较器(HSC)和RXD 引脚的状态。如果HSC 指示显

性总线状态的时间长于tRC_det 且在此期间RXD 引脚不

具有相同的状态,则将检测到钳位情形并将收发器强制

为静默模式。进入待机模式或掉电模式或者RXD 引脚

再次指示显性电平(例如低电平)时,可以释放此故障

保护模式。

工作模式

正常

静默

正常

如果已消除钳位条件并检测到显性

总线,收发器将返回正常模式。

1.3 引脚说明

表1-2列出了引脚的说明。

表1-2: 引脚功能表

ATA6562

ATA6563

SOIC8

VDFN8

SOIC8

VDFN8

1

2

3

4

—

5

6

7

8

—

1

2

3

4

—

5

6

7

8

9

1

2

3

4

5

—

6

7

8

—

1

2

3

4

5

—

6

7

8

9

引脚名称

说明

发送数据输入

电源地1

电源电压

TXD

GND

VCC

RXD

VIO

NSIL

CANL 低电平CAN 总线

CANH 高电平CAN 总线

STBY 待机模式控制输入

EP

接收数据输出;读取总线的数据

I/O电平适配器的电源电压

静默模式控制输入(低电平有效);

外露散热焊盘:散热焊盘,内部连接到GND引脚。

DS20005790C_CN 第8 页

2018-2020 Microchip Technology Inc.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc