HyperTransport MegaCore Function

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

MegaCore Version:

Document Date:

9.0

March 2009

�

Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other

words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other

countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending ap-

plications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty,

but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of

any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of

device specifications before relying on any published information and before placing orders for products or services.

UG-MCHYPRTRNS-1.11

�

Contents

Chapter 1. About this MegaCore Function

Release Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Device Family Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

OpenCore Plus Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Chapter 2. Getting Started

Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

MegaCore Function Walkthrough . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Create a New Quartus II Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Launch the MegaWizard Plug-in Manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Step 1: Parameterize . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Step 2: Set Up Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–9

Step 3: Generate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

Simulate the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

Compile the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–13

Program a Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

Set Up Licensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

Append the License to Your license.dat File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

Specify the License File in the Quartus II Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

Example Simulation and Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Example Quartus II Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Example Simulation with Test Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Chapter 3. Specifications

HyperTransport Technology Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

HT Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

HT Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

HyperTransport MegaCore Function Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Physical Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Synchronization and Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Protocol Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Clocking Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

HyperTransport MegaCore Function Parameters and HT Link Performance . . . . . . . . . . . . . . . . . 3–10

Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

CSR Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–31

OpenCore Plus Time-Out Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–40

Appendix A. Parameters

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Parameter Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Device Family and Read Only Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Base Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

Clocking Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

Advanced Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

© March 2009 Altera Corporation

HyperTransport MegaCore Function User Guide

�

iv

Contents

Appendix B. Stratix Device Pin Assignments

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–1

Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B–1

Appendix C. Example Design

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C–1

Additional Information

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2

HyperTransport MegaCore Function User Guide

© March 2009 Altera Corporation

�

1. About this MegaCore Function

Release Information

Table 1–1 provides information about this release of the HyperTransport MegaCore®

function.

Table 1–1. HyperTransport MegaCore Function Release Information

Item

Version

Release Date

Ordering Code

Product ID(s)

Vendor ID(s)

Description

9.0

March 2009

IP-HT

0098

6AF7

Altera® verifies that the current version of the Quartus® II software compiles the

previous version of each MegaCore function. Any exceptions to this verification are

reported in the MegaCore IP Library Release Notes and Errata. Altera does not verify

compilation with MegaCore function versions older than one release.

Device Family Support

MegaCore functions provide either full or preliminary support for target Altera

device families:

■ Full support means the MegaCore function meets all functional and timing

requirements for the device family and may be used in production designs.

■ Preliminary support means the MegaCore function meets all functional

requirements, but may still be undergoing timing analysis for the device family; it

may be used in production designs with caution.

Table 1–2 shows the level of support offered by the HyperTransport MegaCore

function for each of the Altera device families.

Table 1–2. Device Family Support

Device Family

HardCopy® Stratix®

Stratix

Stratix II

Stratix II GX

Stratix GX

Other device families

Support

Full

Full

Full

Preliminary

Full

No support

© March 2009 Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

�

1–2

Introduction

Features

Chapter 1: About this MegaCore Function

Introduction

The HyperTransport MegaCore function implements high-speed packet transfers

between physical (PHY) and link-layer devices, and is fully compliant with the

HyperTransport I/O Link Specification, Revision 1.03. This MegaCore function allows

designers to interface to a wide range of HyperTransport™ technology (HT) enabled

devices quickly and easily, including network processors, coprocessors, video

chipsets, and ASICs.

The HyperTransport MegaCore function has the following features:

■ 8-bit fully integrated HT end-chain interface

■ Packet-based protocol

■ Dual unidirectional point-to-point links

■ Up to 16 Gigabits per second (Gbps) throughput (8 Gbps in each direction)

■

■

200, 300, and 400 MHz DDR links in Stratix and Stratix GX devices

200, 300, 400, and 500 MHz DDR links in Stratix II and Stratix II GX devices

■ Low-swing differential signaling with 100-Ω differential impedance

■ Hardware verified with HyperTransport interfaces on multiple industry standard

processor and bridge devices

■ Fully parameterized MegaCore function allows flexible, easy configuration

■ Fully optimized for the Altera Stratix II, Stratix, Stratix GX, and Stratix II GX

device families

■ Application-side interface uses the Altera AtlanticTM interface standard

■ Manages HT flow control, optimizing performance and ease of use

■ Independent buffering for each HT virtual channel

■ Automatic handling of HT ordering rules

■ Stalling of one virtual channel does not delay other virtual channels (subject to

ordering rules)

■ Flexible parameterized buffer sizes, allowing customization depending on

system requirements

■ User interface has independent interfaces for the HT virtual channels, allowing

independent user logic design

■ Cyclic redundancy code (CRC) generation and checking to preserve data integrity

■ Integrated detection and response to common HT error conditions

■ CRC errors

■ End-chain errors

■ Fully integrated HT configuration space includes all required configuration space

registers and HT capabilities list registers

HyperTransport MegaCore Function User Guide

© March 2009 Altera Corporation

Preliminary

�

Chapter 1: About this MegaCore Function

Performance

1–3

■ 32-bit and 64-bit support across all base address registers (BARs)

■ Automatically handles all CSR space accesses

■ Verilog HDL and VHDL simulation support

OpenCore Plus Evaluation

With the Altera free OpenCore Plus evaluation feature, you can perform the following

actions:

■ Simulate the behavior of a megafunction (Altera MegaCore function or AMPP™

megafunction) within your system

■ Verify the functionality of your design, as well as quickly and easily evaluate its

size and speed

■ Generate time-limited device programming files for designs that include

MegaCore functions

■ Program a device and verify your design in hardware

You only need to purchase a license for the MegaCore function when you are

completely satisfied with its functionality and performance, and want to take your

design to production.

f For more information about OpenCore Plus hardware evaluation using the

HyperTransport MegaCore function, refer to “OpenCore Plus Time-Out Behavior” on

page 3–40 and AN 320: OpenCore Plus Evaluation of Megafunctions.

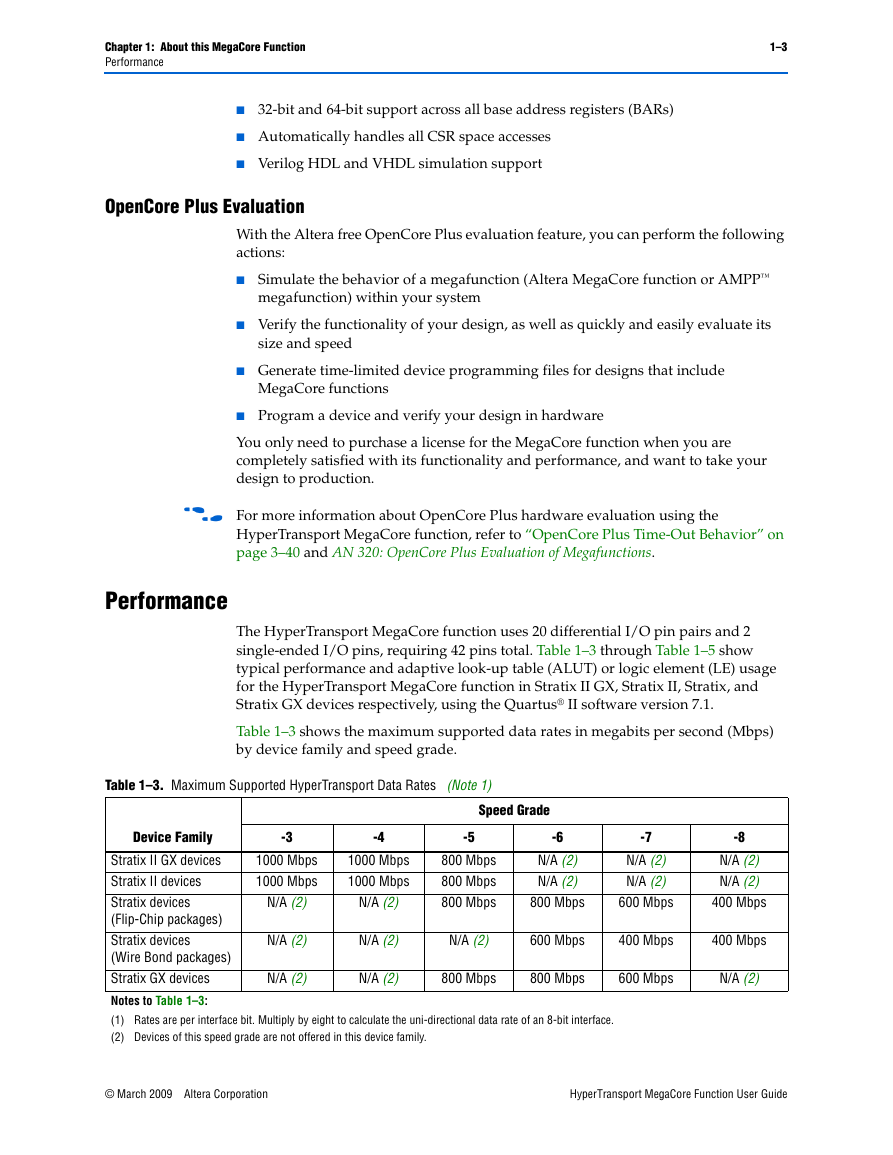

Performance

The HyperTransport MegaCore function uses 20 differential I/O pin pairs and 2

single-ended I/O pins, requiring 42 pins total. Table 1–3 through Table 1–5 show

typical performance and adaptive look-up table (ALUT) or logic element (LE) usage

for the HyperTransport MegaCore function in Stratix II GX, Stratix II, Stratix, and

Stratix GX devices respectively, using the Quartus® II software version 7.1.

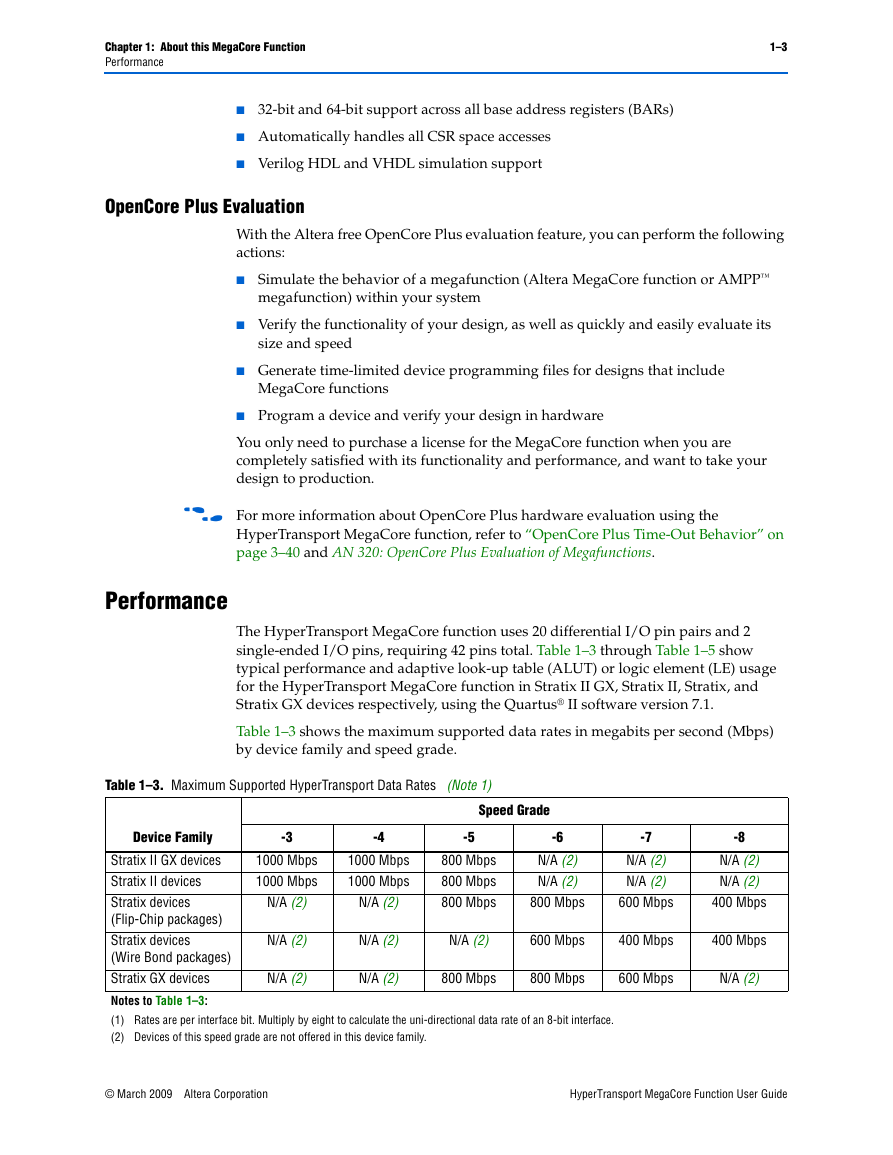

Table 1–3 shows the maximum supported data rates in megabits per second (Mbps)

by device family and speed grade.

Table 1–3. Maximum Supported HyperTransport Data Rates (Note 1)

Speed Grade

-4

-5

-6

-3

1000 Mbps

1000 Mbps

N/A (2)

1000 Mbps

1000 Mbps

N/A (2)

800 Mbps

800 Mbps

800 Mbps

Device Family

Stratix II GX devices

Stratix II devices

Stratix devices

(Flip-Chip packages)

Stratix devices

(Wire Bond packages)

Stratix GX devices

Notes to Table 1–3:

(1) Rates are per interface bit. Multiply by eight to calculate the uni-directional data rate of an 8-bit interface.

(2) Devices of this speed grade are not offered in this device family.

N/A (2)

N/A (2)

800 Mbps

800 Mbps

800 Mbps

N/A (2)

600 Mbps

N/A (2)

N/A (2)

N/A (2)

N/A (2)

-7

N/A (2)

N/A (2)

600 Mbps

-8

N/A (2)

N/A (2)

400 Mbps

400 Mbps

400 Mbps

600 Mbps

N/A (2)

© March 2009 Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

�

1–4

Chapter 1: About this MegaCore Function

Performance

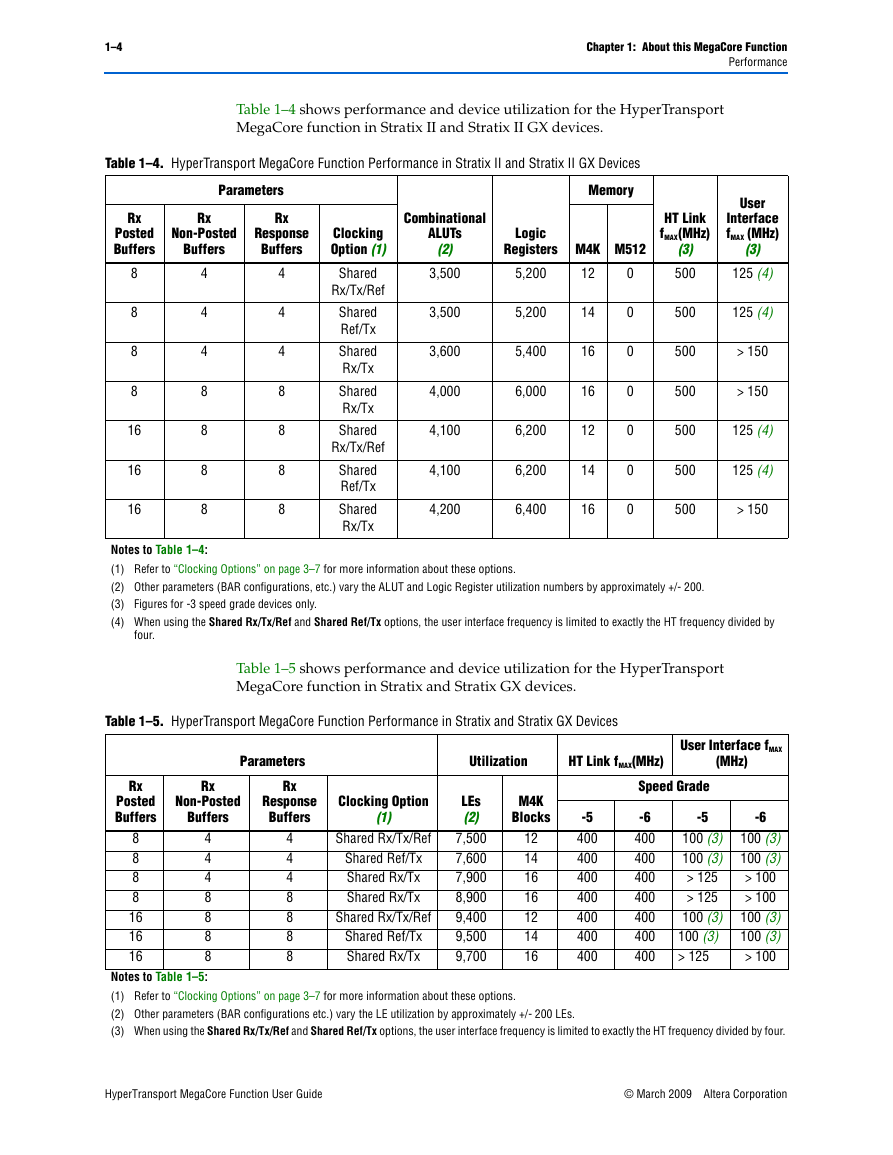

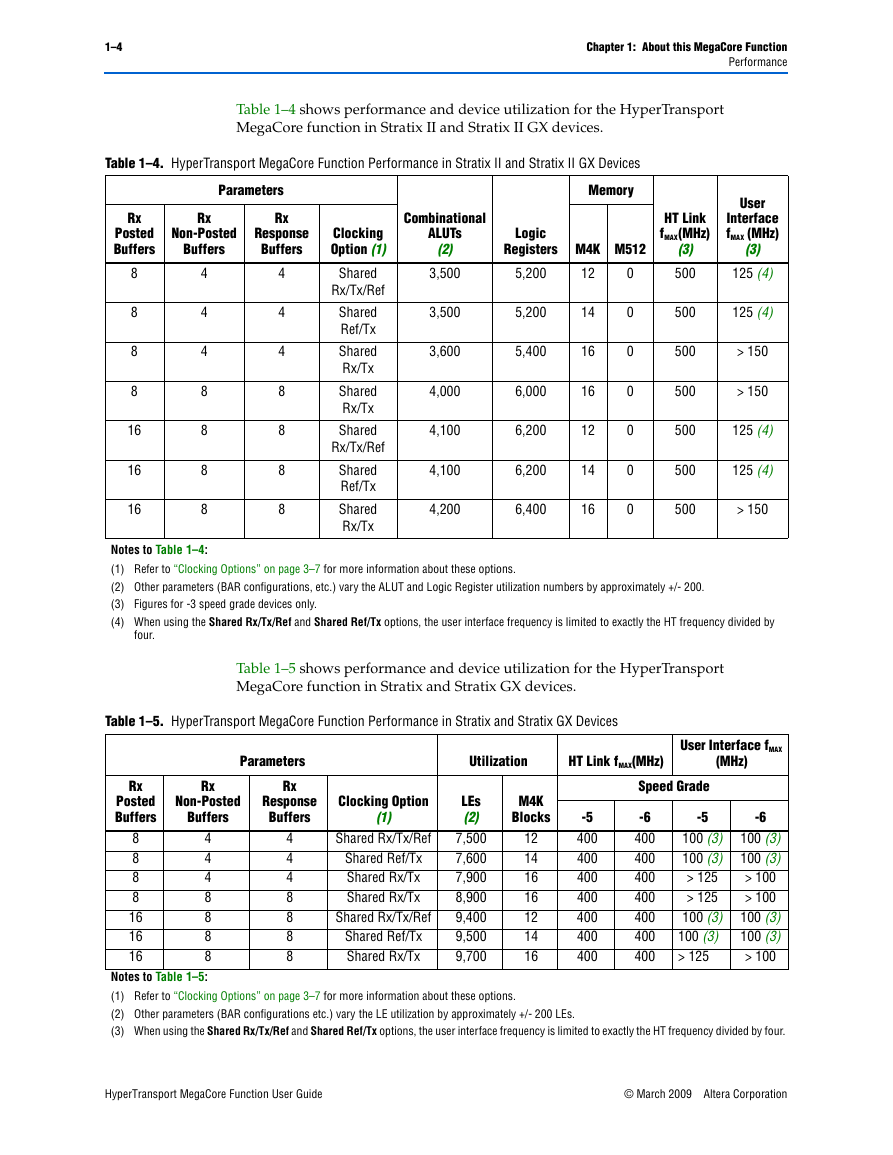

Table 1–4 shows performance and device utilization for the HyperTransport

MegaCore function in Stratix II and Stratix II GX devices.

Table 1–4. HyperTransport MegaCore Function Performance in Stratix II and Stratix II GX Devices

Parameters

Rx

Posted

Buffers

8

8

8

8

16

16

16

Rx

Non-Posted

Buffers

4

4

4

8

8

8

8

Rx

Response

Buffers

4

4

4

8

8

8

8

Clocking

Option (1)

Shared

Rx/Tx/Ref

Shared

Ref/Tx

Shared

Rx/Tx

Shared

Rx/Tx

Shared

Rx/Tx/Ref

Shared

Ref/Tx

Shared

Rx/Tx

Combinational

ALUTs

(2)

3,500

3,500

3,600

4,000

4,100

4,100

4,200

Memory

HT Link

fMAX (MHz)

(3)

500

M4K M512

12

0

14

16

16

12

14

16

0

0

0

0

0

0

500

500

500

500

500

500

Logic

Registers

5,200

5,200

5,400

6,000

6,200

6,200

6,400

User

Interface

fMAX (MHz)

(3)

125 (4)

125 (4)

> 150

> 150

125 (4)

125 (4)

> 150

Notes to Table 1–4:

(1) Refer to “Clocking Options” on page 3–7 for more information about these options.

(2) Other parameters (BAR configurations, etc.) vary the ALUT and Logic Register utilization numbers by approximately +/- 200.

(3) Figures for -3 speed grade devices only.

(4) When using the Shared Rx/Tx/Ref and Shared Ref/Tx options, the user interface frequency is limited to exactly the HT frequency divided by

four.

Table 1–5 shows performance and device utilization for the HyperTransport

MegaCore function in Stratix and Stratix GX devices.

Table 1–5. HyperTransport MegaCore Function Performance in Stratix and Stratix GX Devices

Parameters

Rx

Rx

Non-Posted

Buffers

Response

Buffers

Rx

Posted

Buffers

Utilization

HT Link fMAX(MHz)

User Interface fMAX

(MHz)

Speed Grade

-5

-6

Clocking Option

(1)

Shared Rx/Tx/Ref

M4K

Blocks

4

4

4

8

8

8

8

8

8

8

8

16

16

16

Shared Ref/Tx

Shared Rx/Tx

Shared Rx/Tx

4

4

4

8

8

8

8

Notes to Table 1–5:

(1) Refer to “Clocking Options” on page 3–7 for more information about these options.

(2) Other parameters (BAR configurations etc.) vary the LE utilization by approximately +/- 200 LEs.

(3) When using the Shared Rx/Tx/Ref and Shared Ref/Tx options, the user interface frequency is limited to exactly the HT frequency divided by four.

100 (3)

100 (3)

> 125

> 125

100 (3)

100 (3)

> 125

100 (3)

100 (3)

> 100

> 100

100 (3)

100 (3)

> 100

Shared Ref/Tx

Shared Rx/Tx

12

14

16

16

12

14

16

Shared Rx/Tx/Ref

-5

400

400

400

400

400

400

400

-6

400

400

400

400

400

400

400

LEs

(2)

7,500

7,600

7,900

8,900

9,400

9,500

9,700

HyperTransport MegaCore Function User Guide

© March 2009 Altera Corporation

Preliminary

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc