第二章 计算机体系结构基础

1 在三台不同指令系统的计算机上运行同一程序P时,A机需要执行1. 0× 条指令,B机需要执行2.0×

条指令,C机需要执行条指4.0× 令,但实际执行时间都是10秒,请分别计算这三台机器在实行程

序P时的实际运行速度,以MIPS为单位。这三台计算机在运行程序P时,哪台性能最高?为什么?

解:A 为 10MIPS,B 为 20MIPS,C 为 40MIPS。

三台机器实际性能相同。(题目问的是运行程序 P 时的性能。 )

5 对某处理器进行功耗测试,得到如下数据:时钟不翻转,电压1. 05V时,电流为500mA;时钟频率为

1GHz,电压1.1V时,电流为2500mA。请计算此处理器的静态功耗以及500MHz下的总功耗

解:

1.1V 下静态功耗 1.1×1.1/(1.05/0.5)=0.576W (时钟不翻转的静态功耗按电阻算,

)

1.1V 下 1GHZ 时动态功耗为 1.1×2.5-0.576=2.174W (动态功耗+静态功耗=总功耗,

动 态

静 态

)

总

1.1V 下 0.5GHZ 动态功耗为 2.174*0.5/1=1.087W (动态功耗与翻转率成正比)

1.1V 下 0.5GHZ 总功耗为 1.087+0.576=1.663W

第三章 二进制与逻辑电路

1 定点数的表示,(1):分别给出64位定点原码和补码表示的数的范围;(2):在32位定点补码表示中,

0X80000000表示什么数?

解:

(1) [-(

(2)

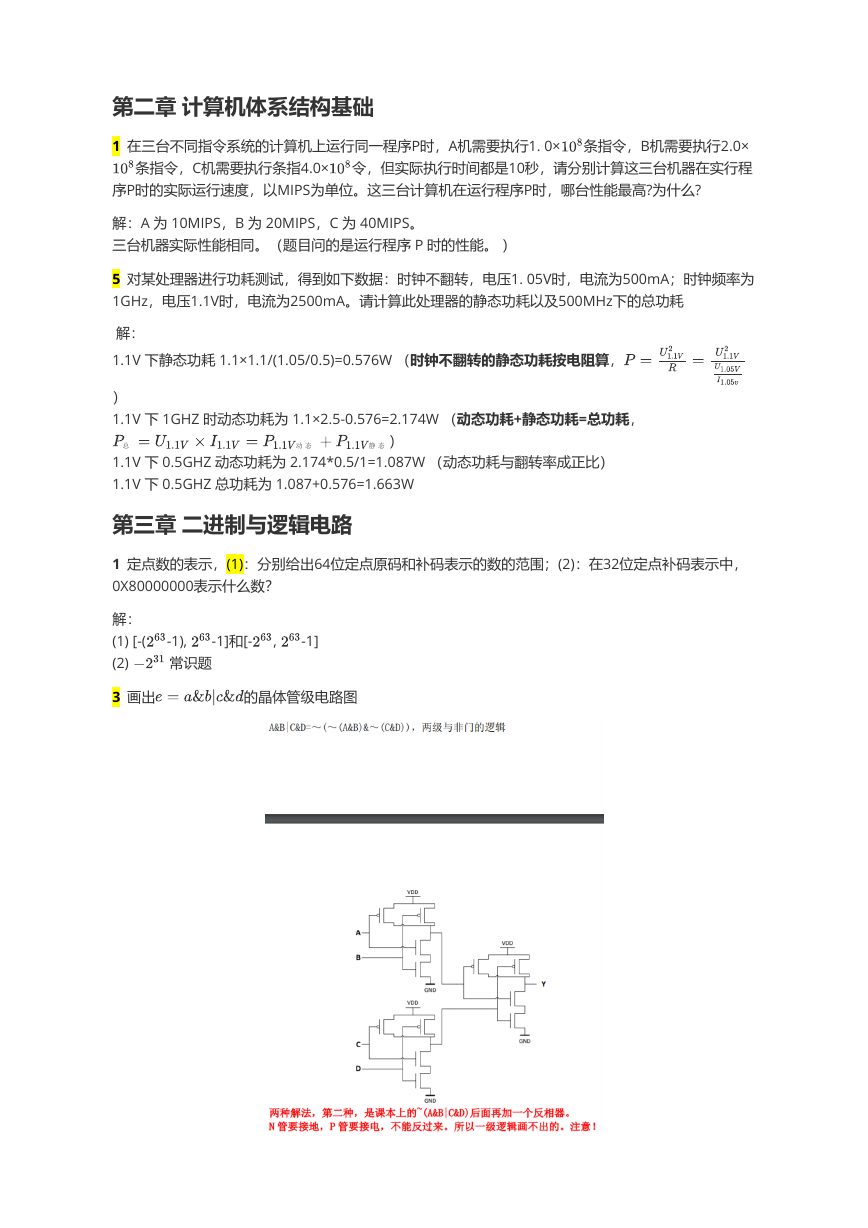

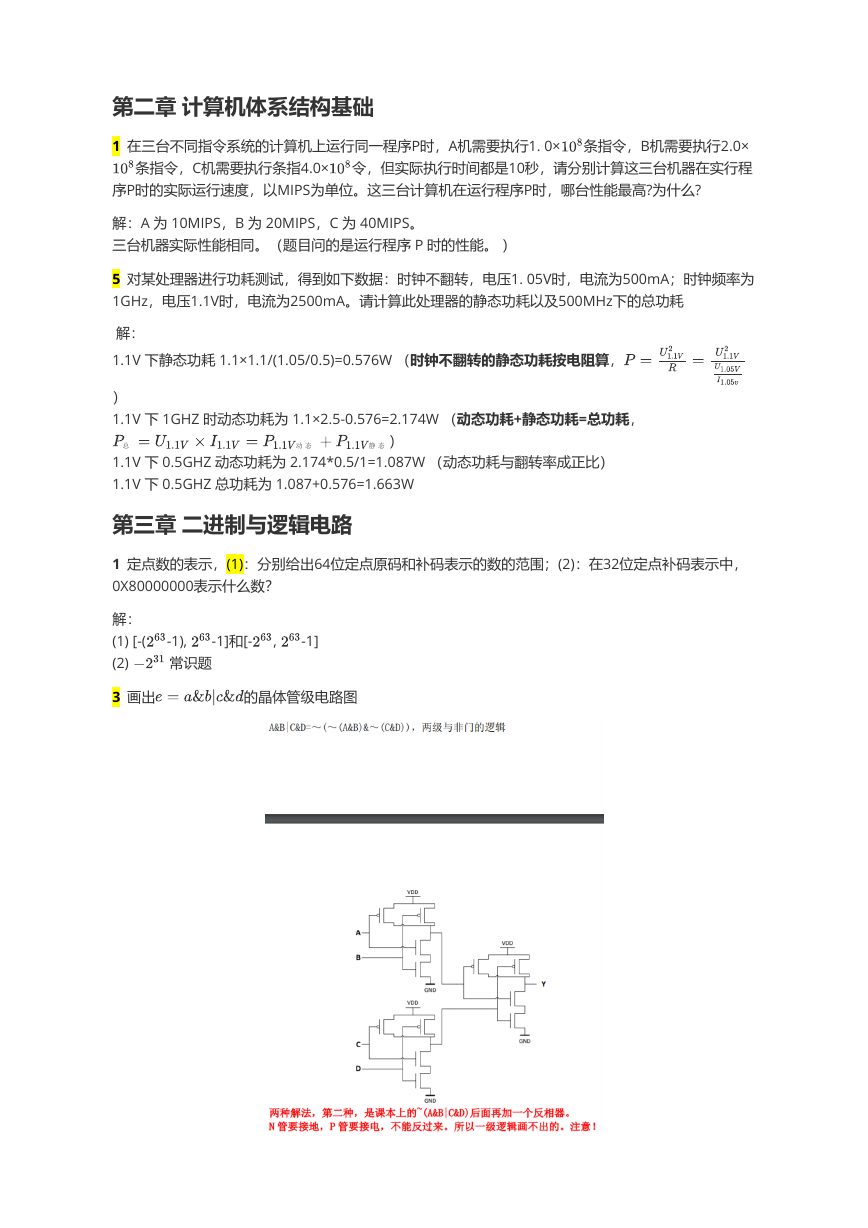

3 画出

-1]和[-

-1),

常识题

,

-1]

的晶体管级电路图

�

4 计算一个FO4的延迟,假设反相器的输入电容为0.0036pF,平均每个负载连线电容为0.0044pF,翻

转延迟为0.023ns,每pF延迟为4.5ns。

解:

FO4 延迟=本征延迟+负载延迟=0.023+4.5·((0.0036+0.0044)·4)=0.167ns

本课对 FO4 定义为 1 个反相器驱动 4 个相同的反相器(器件延迟和线延迟是4份)。 鉴 于 FO4 定 义

存 疑 ( 参 见 wiki ) , 回 答

0.023+4.5·(0.0044+0.0036·4·4)=0.302ns 也算对。

第五章 静态流水线

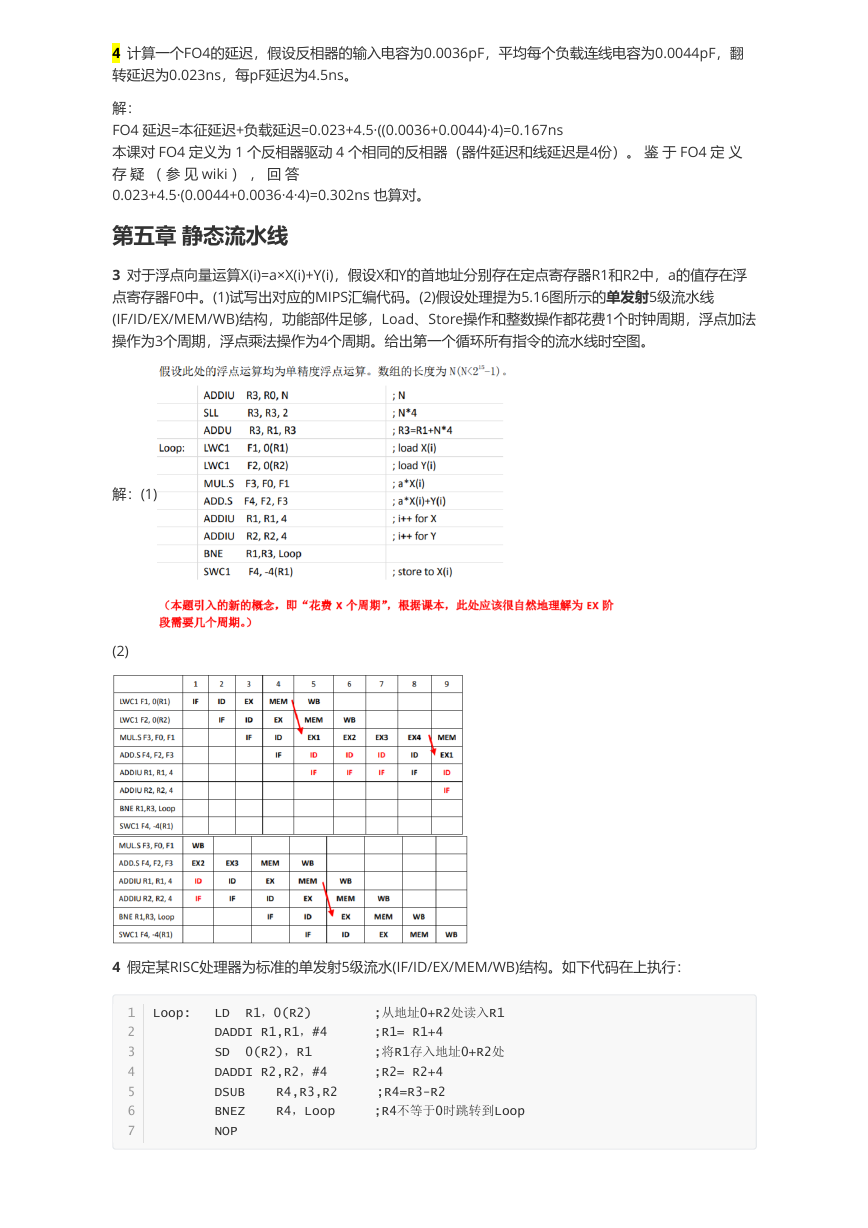

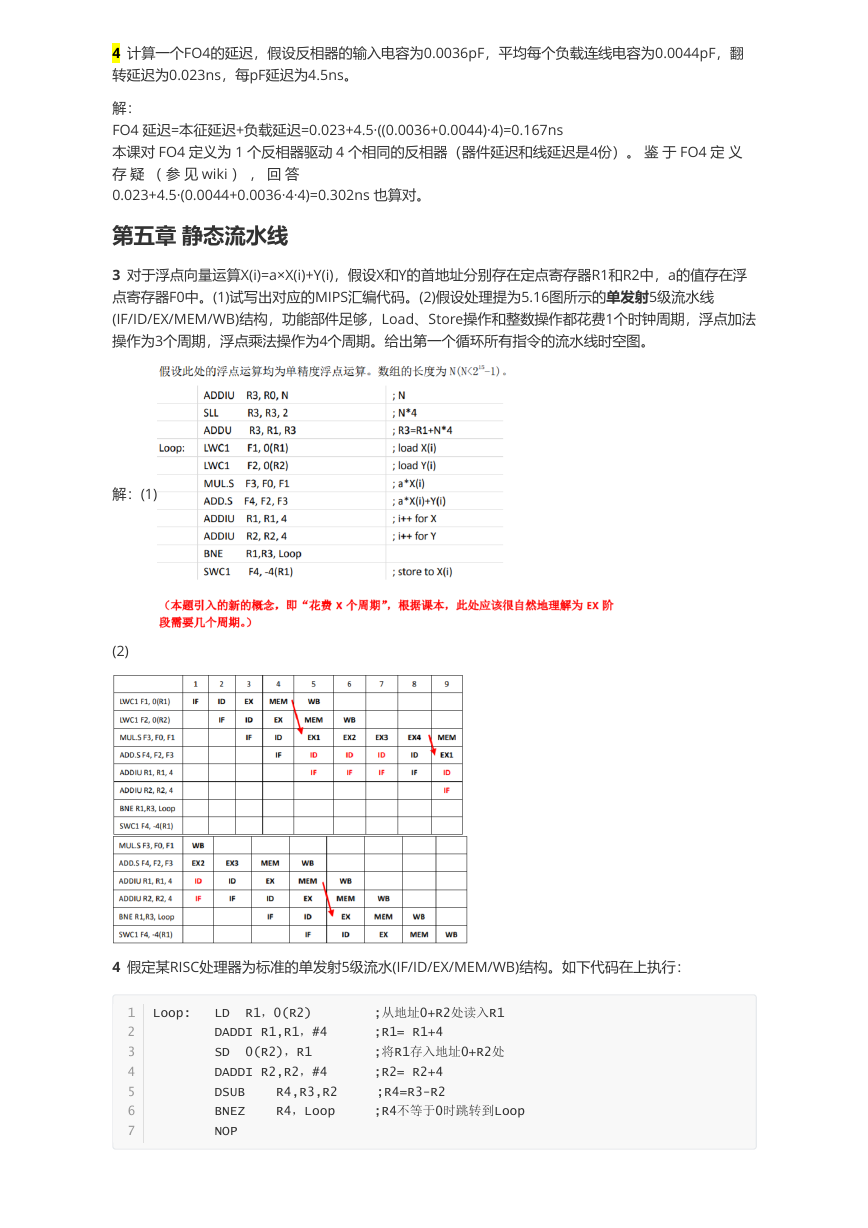

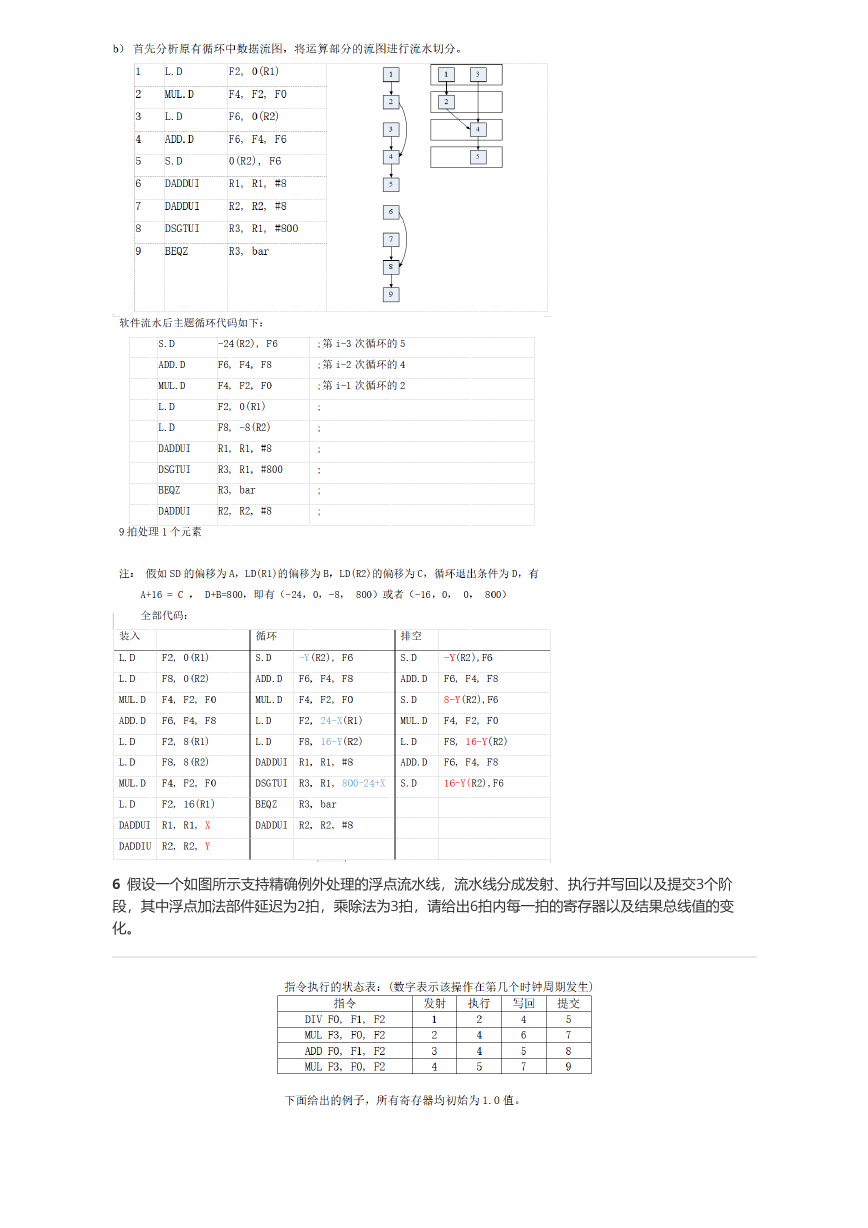

3 对于浮点向量运算X(i)=a×X(i)+Y(i),假设X和Y的首地址分别存在定点寄存器R1和R2中,a的值存在浮

点寄存器F0中。(1)试写出对应的MIPS汇编代码。(2)假设处理提为5.16图所示的单发射5级流水线

(IF/ID/EX/MEM/WB)结构,功能部件足够,Load、Store操作和整数操作都花费1个时钟周期,浮点加法

操作为3个周期,浮点乘法操作为4个周期。给出第一个循环所有指令的流水线时空图。

解:(1)

(2)

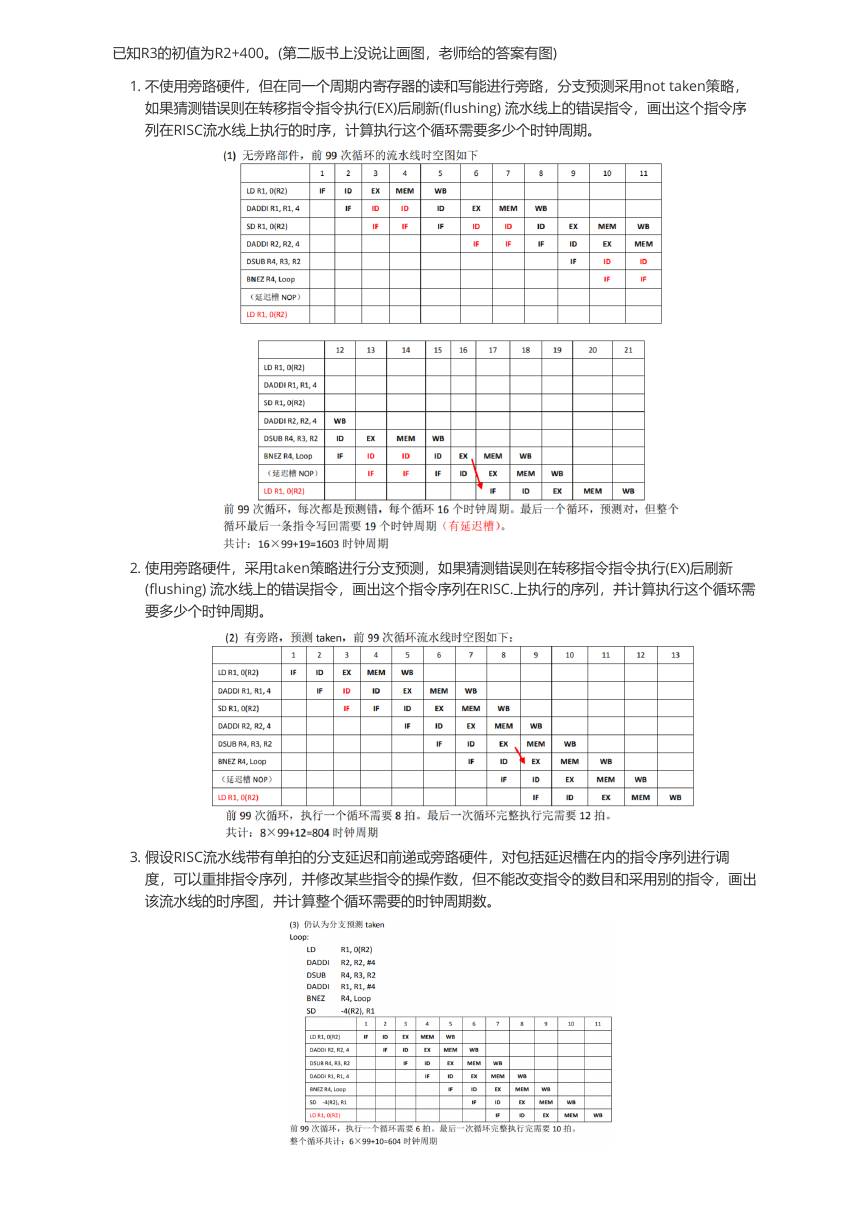

4 假定某RISC处理器为标准的单发射5级流水(IF/ID/EX/MEM/WB)结构。如下代码在上执行:

1

2

3

4

5

6

7

Loop: LD R1,0(R2) ;从地址0+R2处读入R1

DADDI R1,R1,#4 ;R1= R1+4

SD 0(R2),R1 ;将R1存入地址0+R2处

DADDI R2,R2,#4 ;R2= R2+4

DSUB R4,R3,R2 ;R4=R3-R2

BNEZ R4,Loop ;R4不等于0时跳转到Loop

NOP

�

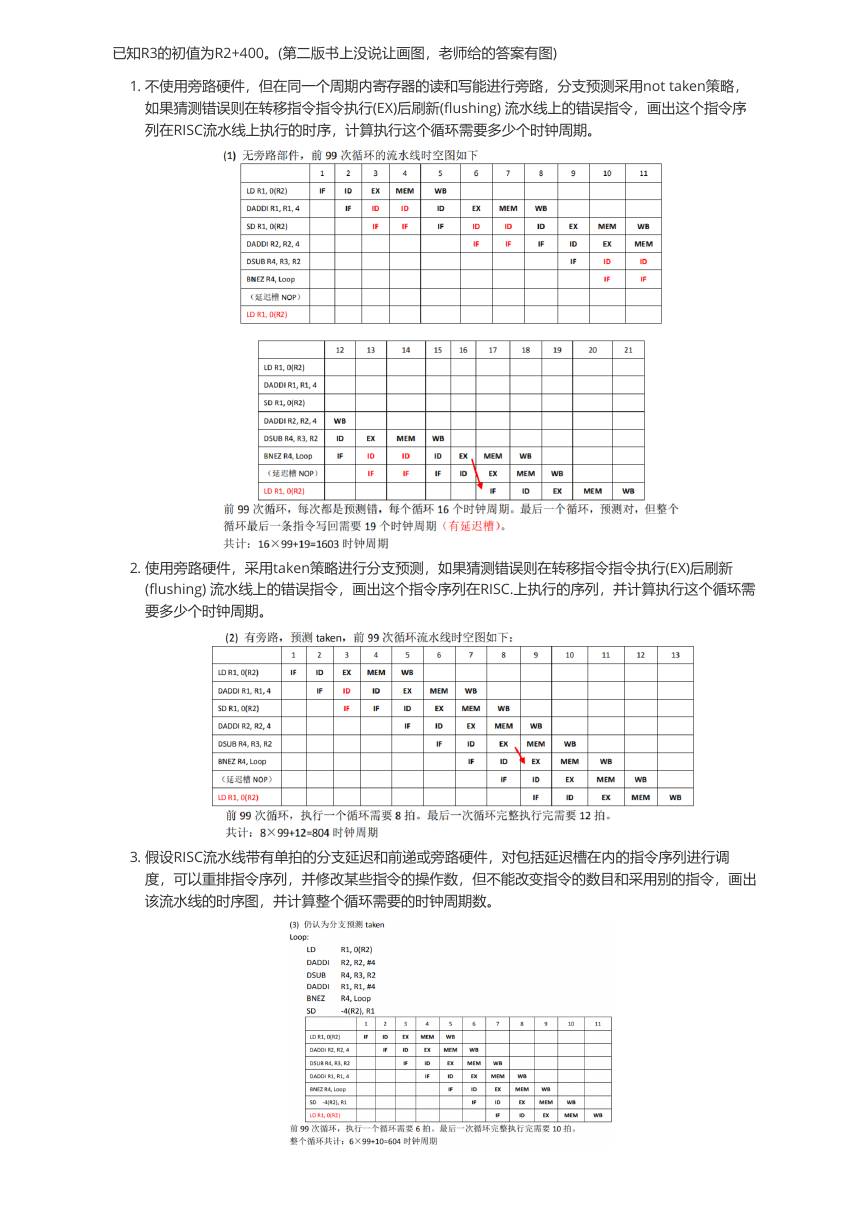

已知R3的初值为R2+400。(第二版书上没说让画图,老师给的答案有图)

1. 不使用旁路硬件,但在同一个周期内寄存器的读和写能进行旁路,分支预测采用not taken策略,

如果猜测错误则在转移指令指令执行(EX)后刷新(flushing) 流水线上的错误指令,画出这个指令序

列在RISC流水线上执行的时序,计算执行这个循环需要多少个时钟周期。

2. 使用旁路硬件,采用taken策略进行分支预测,如果猜测错误则在转移指令指令执行(EX)后刷新

(flushing) 流水线上的错误指令,画出这个指令序列在RISC.上执行的序列,并计算执行这个循环需

要多少个时钟周期。

3. 假设RISC流水线带有单拍的分支延迟和前递或旁路硬件,对包括延迟槽在内的指令序列进行调

度,可以重排指令序列,并修改某些指令的操作数,但不能改变指令的数目和采用别的指令,画出

该流水线的时序图,并计算整个循环需要的时钟周期数。

�

第六章 动态流水线

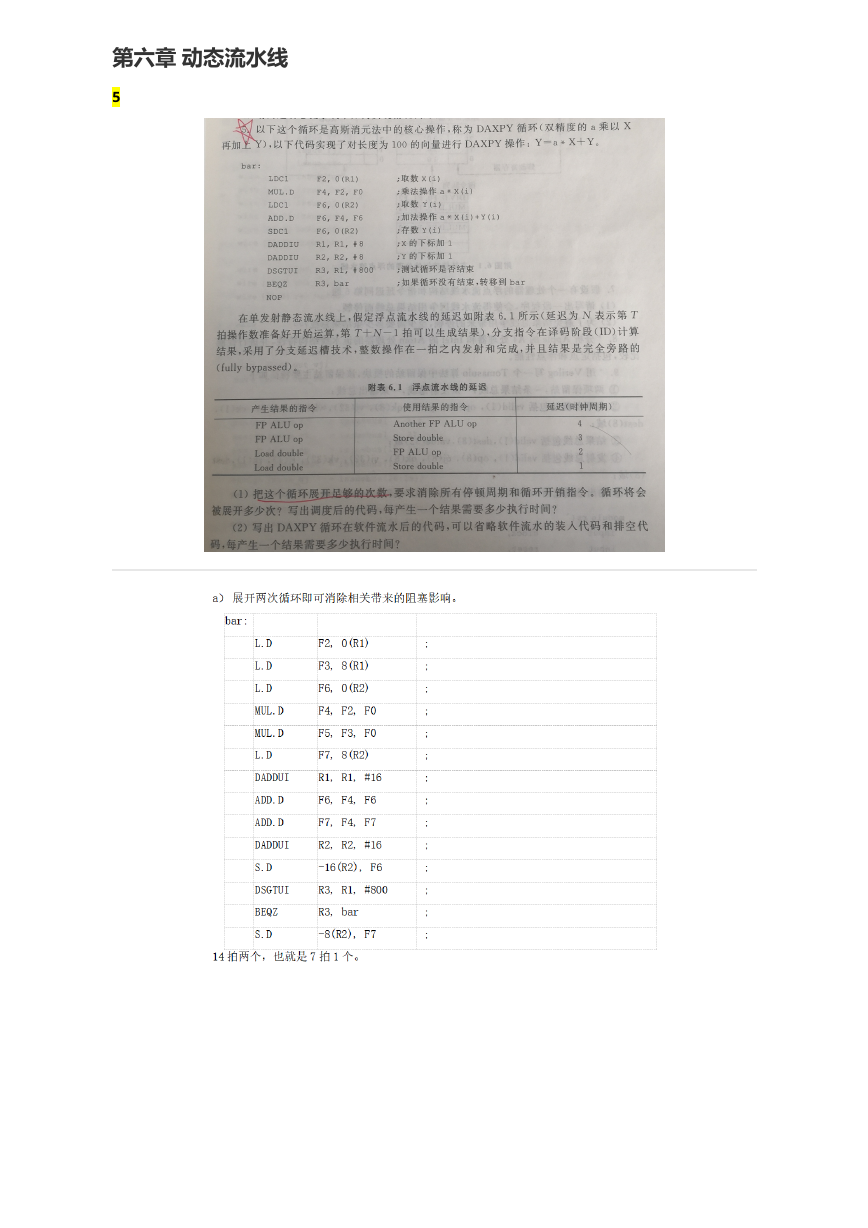

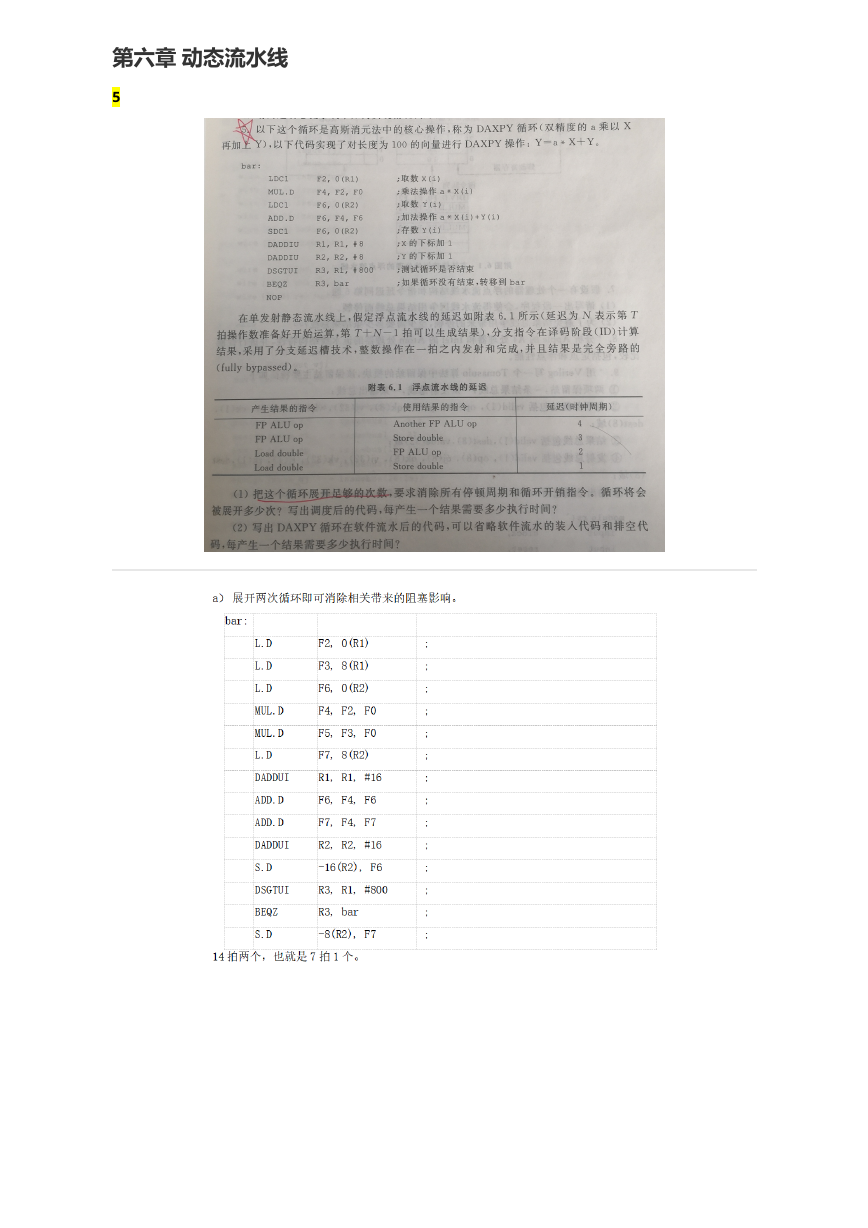

5

�

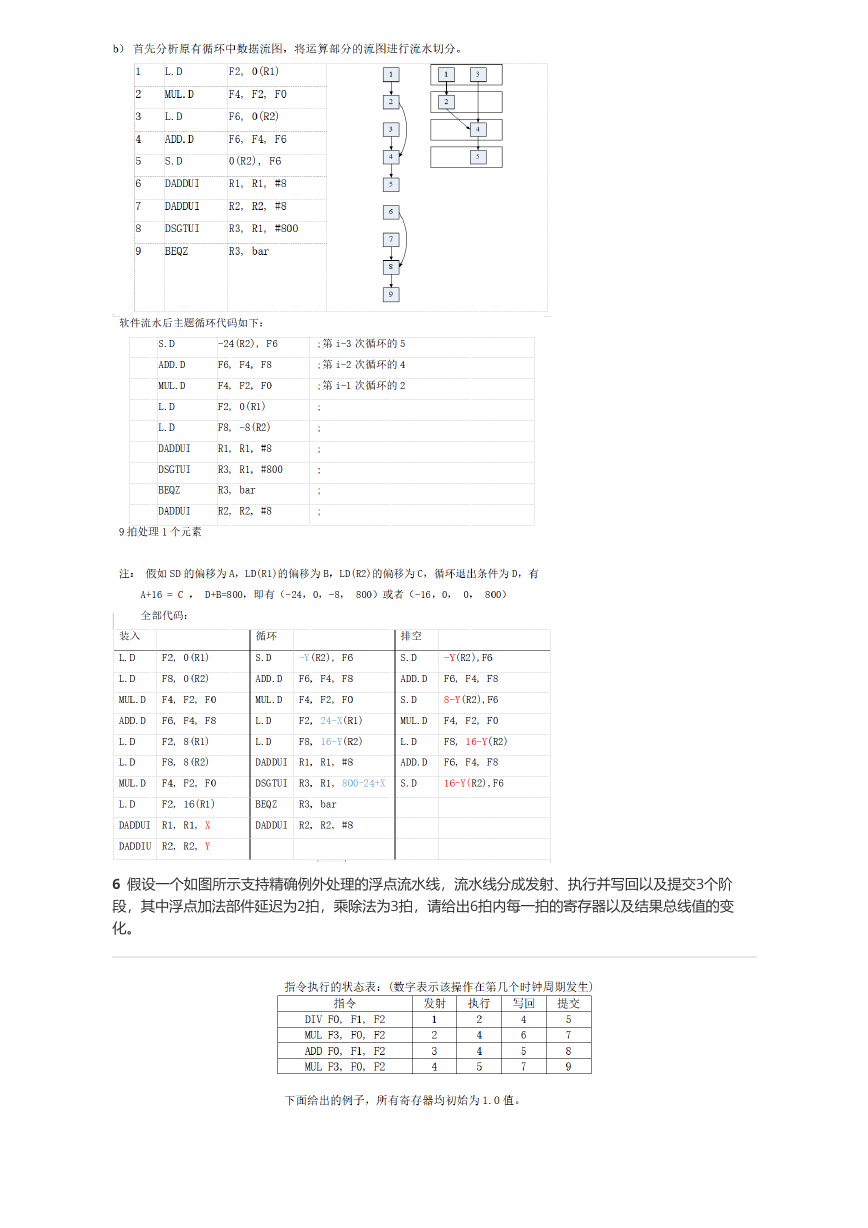

6 假设一个如图所示支持精确例外处理的浮点流水线,流水线分成发射、执行并写回以及提交3个阶

段,其中浮点加法部件延迟为2拍,乘除法为3拍,请给出6拍内每一拍的寄存器以及结果总线值的变

化。

�

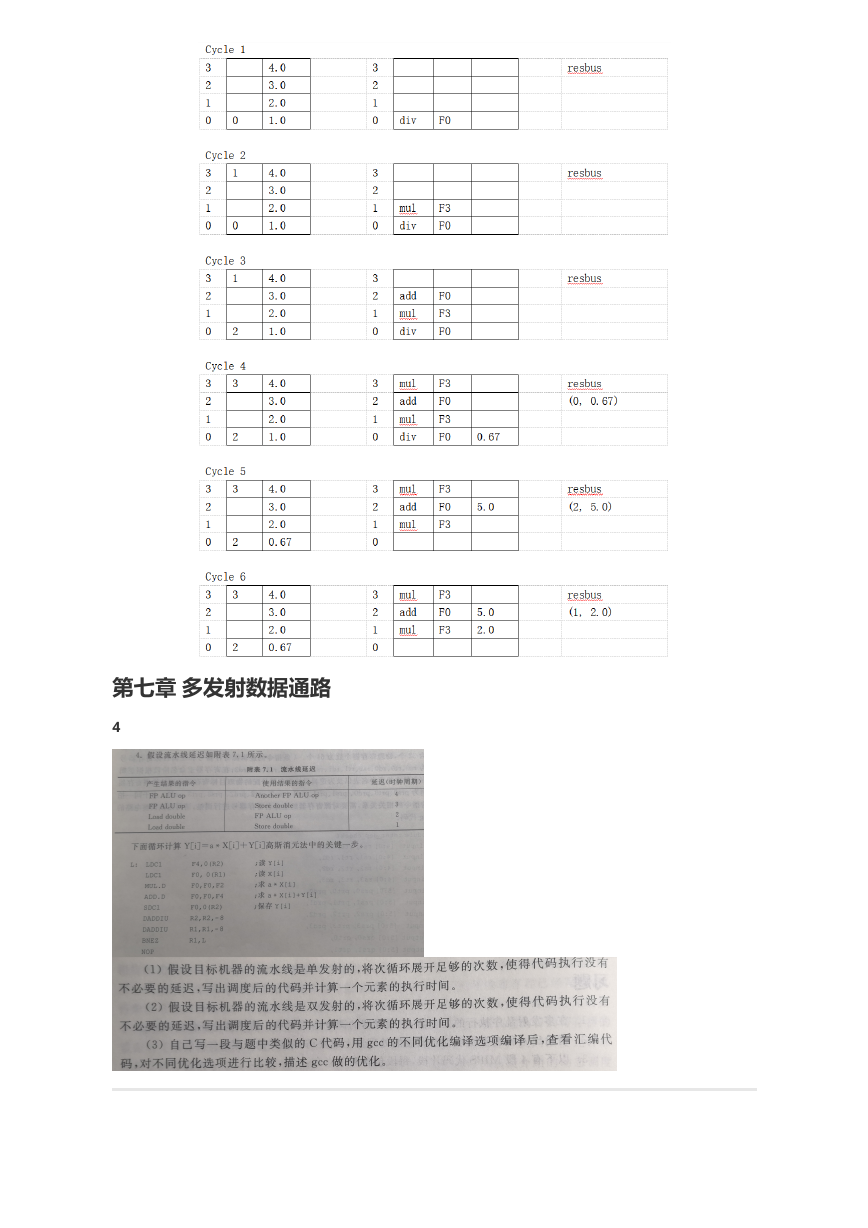

第七章 多发射数据通路

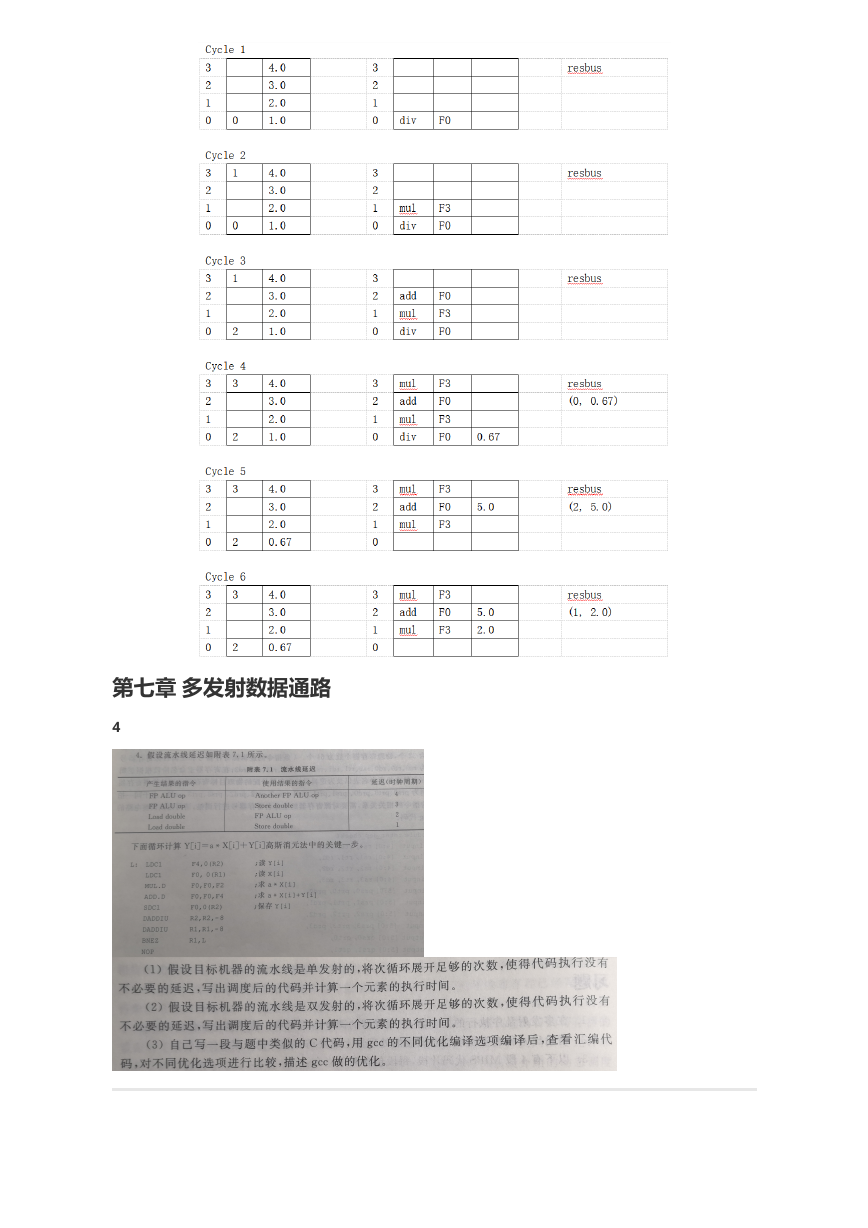

4

�

5 一个n发射的处理器,流水线情况如下:取指,译码,重命名到物理寄存器后送入发射队列,发射队

列乱序发射,功能部件乱序执行,乱序写回物理寄存器,最后顺序提交并释放物理寄存器。已知该处理

器有m个逻辑寄存器,i个功能部件(i>n),每条指令从重命名到写回需要t1拍,从重命名到提交需要t2

拍。为了能让流水线满负荷工作,最少需要多少个物理寄存器?

物理寄存器个数应至少为n×t2+m才能让流水线满负荷工作。每条指令在重命名的时候需要占用一个物

理寄存器,每拍n条指令发射,则需要占用n个物理寄存器,被重命名的物理寄存器只有在提交的时候,

并且不是当前逻辑寄存器的时候,才被释放。从重命名到提交共有t2拍,当流水线满负荷工作,流水线

占用了n×t2个物理寄存器,另外逻辑寄存器数目为m个,因此共需要物理寄存器的个数为n×t2+m。

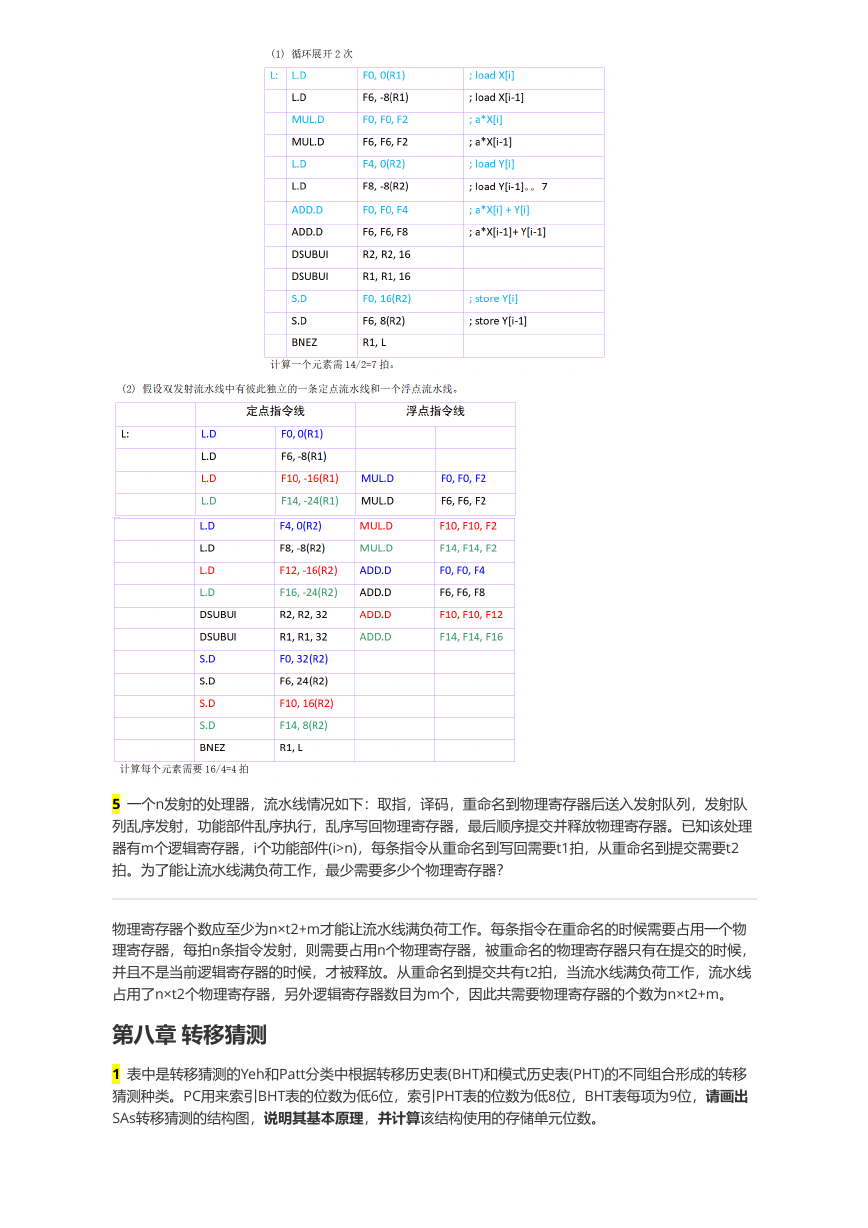

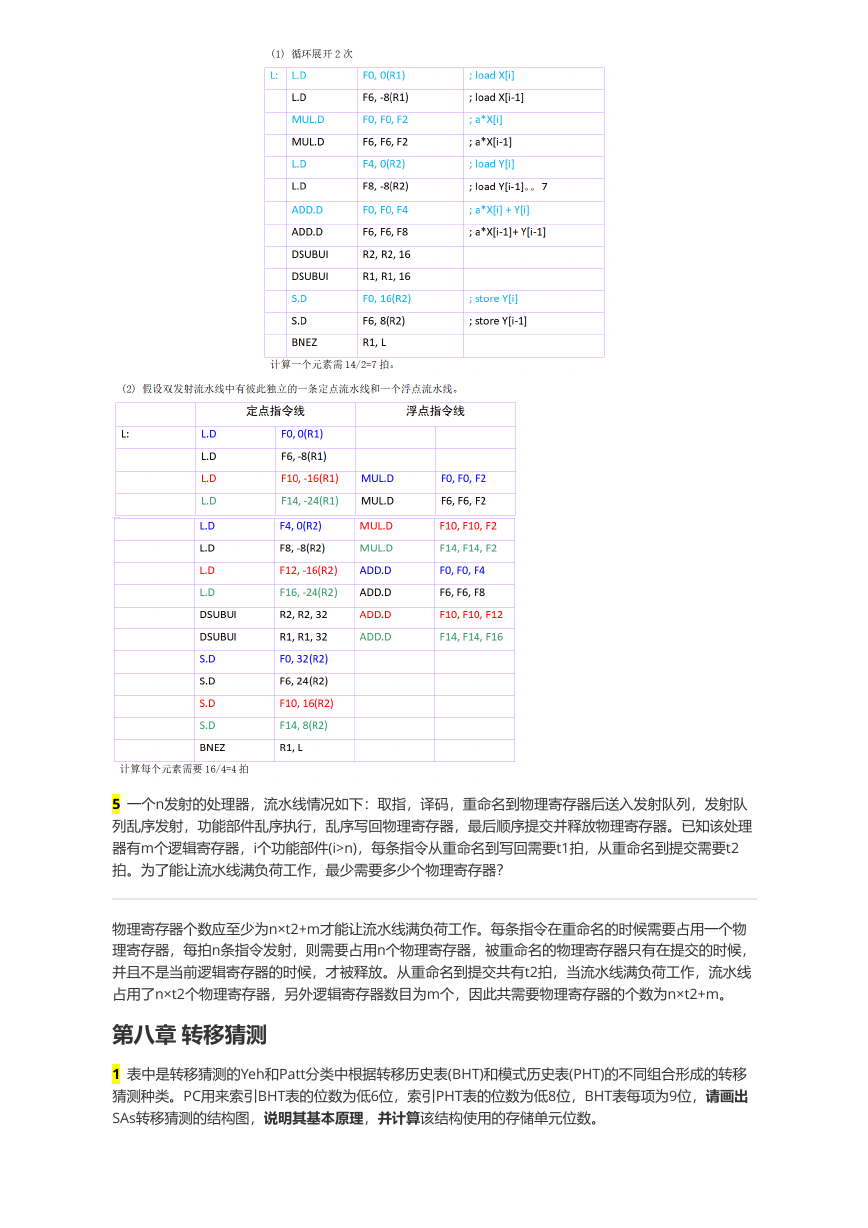

第八章 转移猜测

1 表中是转移猜测的Yeh和Patt分类中根据转移历史表(BHT)和模式历史表(PHT)的不同组合形成的转移

猜测种类。PC用来索引BHT表的位数为低6位,索引PHT表的位数为低8位,BHT表每项为9位,请画出

SAs转移猜测的结构图,说明其基本原理,并计算该结构使用的存储单元位数。

�

Global PHT

Per address PHT

Per set PHT

Global BHR

Per-address BHR

Ped-set BHR

GAg

PAg

SAg

Gap

PAp

SAp

GAs

PAs

SAs

BHT

,PHT

,共

。

BHT根据地址低6位选出一个9位向量,和地址低8位一起到PHT中选取2位饱和计数。

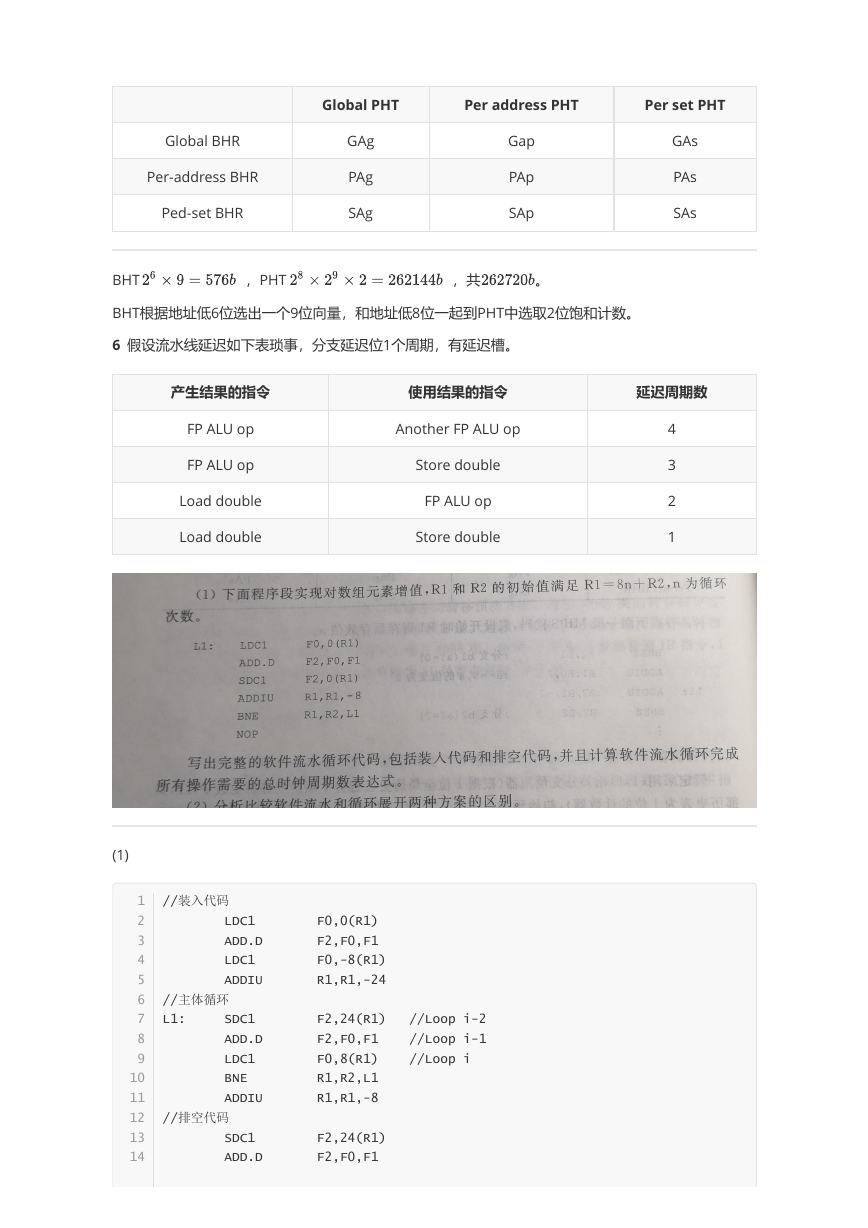

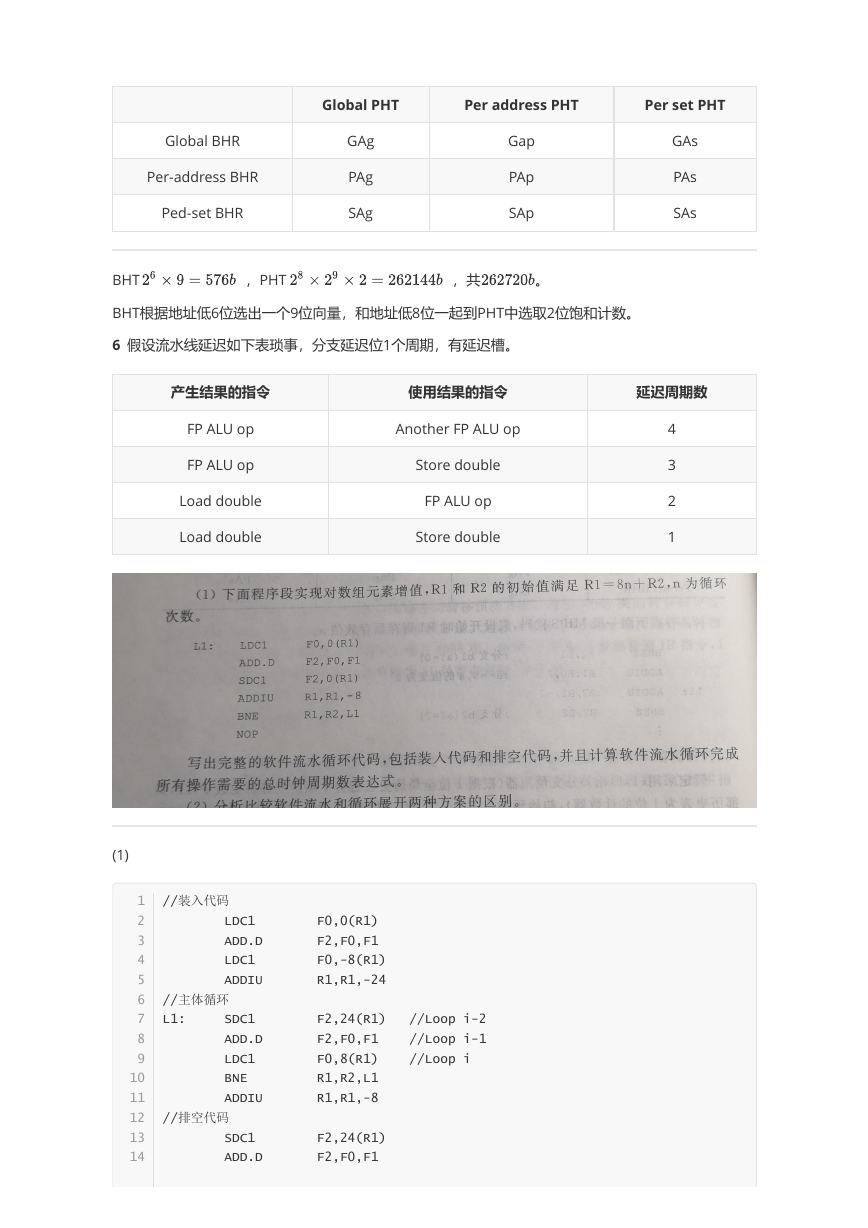

6 假设流水线延迟如下表琐事,分支延迟位1个周期,有延迟槽。

产生结果的指令

使用结果的指令

延迟周期数

FP ALU op

FP ALU op

Load double

Load double

Another FP ALU op

Store double

FP ALU op

Store double

4

3

2

1

(1)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

//装入代码

LDC1 F0,0(R1)

ADD.D F2,F0,F1

LDC1 F0,-8(R1)

ADDIU R1,R1,-24

//主体循环

L1: SDC1 F2,24(R1) //Loop i-2

ADD.D F2,F0,F1 //Loop i-1

LDC1 F0,8(R1) //Loop i

BNE R1,R2,L1

ADDIU R1,R1,-8

//排空代码

SDC1 F2,24(R1)

ADD.D F2,F0,F1

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc