SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

SSD2828QN4

Advance Information

MIPI Master Bridge

This document contains information on a new product. Specifications and information herein are subject to change

without notice.

http://www.solomon-systech.com

SSD2828QN4

Copyright © 2013 Solomon Systech Limited

Rev 1.3

P 1/168 Mar 2013

�

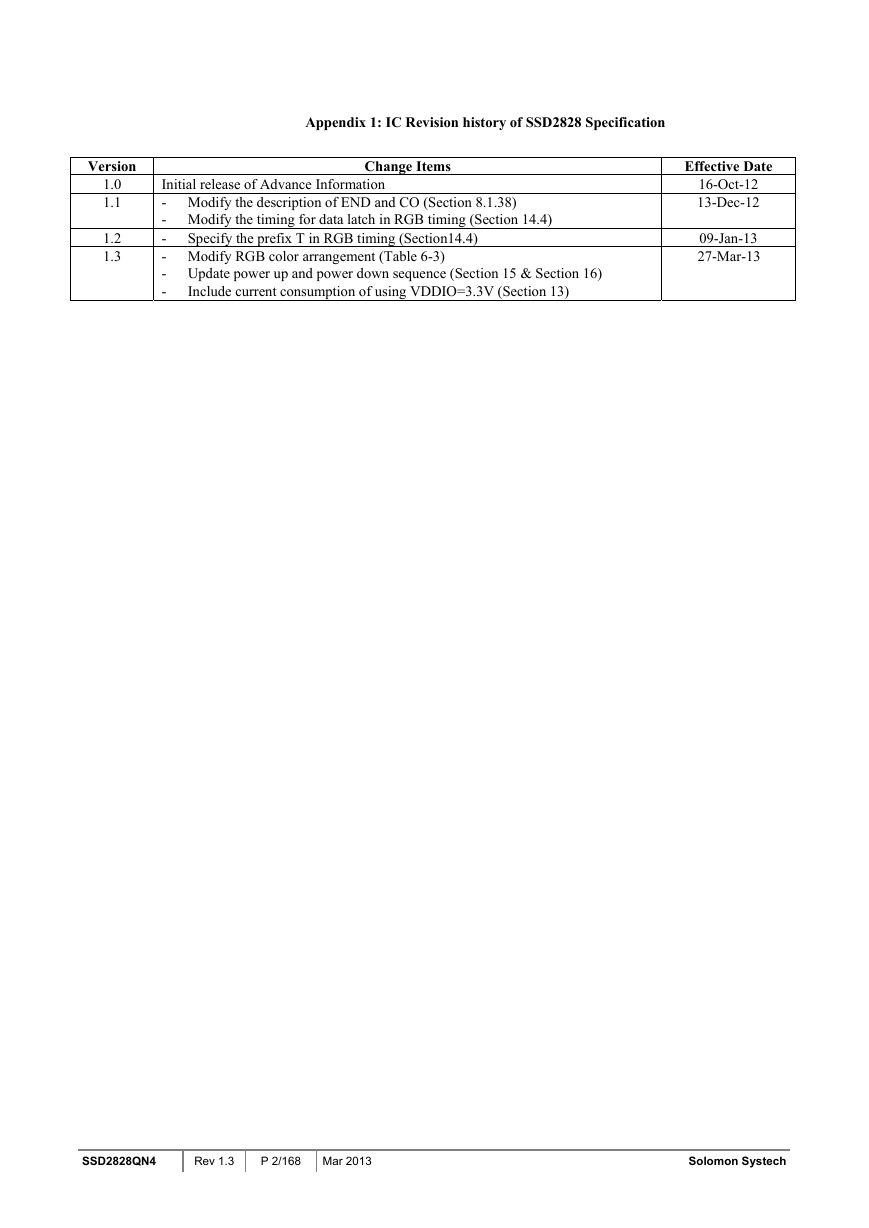

Version

1.0

1.1

1.2

1.3

Appendix 1: IC Revision history of SSD2828 Specification

Change Items

Initial release of Advance Information

- Modify the description of END and CO (Section 8.1.38)

- Modify the timing for data latch in RGB timing (Section 14.4)

-

- Modify RGB color arrangement (Table 6-3)

- Update power up and power down sequence (Section 15 & Section 16)

-

Include current consumption of using VDDIO=3.3V (Section 13)

Specify the prefix T in RGB timing (Section14.4)

Effective Date

16-Oct-12

13-Dec-12

09-Jan-13

27-Mar-13

SSD2828QN4

Rev 1.3

P 2/168 Mar 2013

Solomon Systech

�

CONTENTS

1 GENERAL DESCRIPTION ....................................................................................................... 9

2 FEATURES................................................................................................................................. 10

REFERENCES........................................................................................................................................................10

DEFINITIONS........................................................................................................................................................10

3 ORDERING INFORMATION ................................................................................................. 11

2.1

2.2

4 BLOCK DIAGRAM .................................................................................................................. 11

5 FUNCTIONAL DESCRIPTION .............................................................................................. 14

FUNCTIONAL BLOCKS..........................................................................................................................................14

5.1

CLOCK AND RESET MODULE ...............................................................................................................................14

5.2

EXTERNAL INTERFACE.........................................................................................................................................15

5.3

PROTOCOL CONTROL UNIT (PCU).......................................................................................................................15

5.4

PACKET PROCESSING UNIT (PPU) .......................................................................................................................15

5.5

ERROR CORRECTION CODE/ CYCLIC REDUNDANCY CHECK (ECC/CRC)............................................................16

5.6

LONG AND COMMAND BUFFERS..........................................................................................................................16

5.7

INTERRUPT SIGNAL ..............................................................................................................................................16

5.8

D-PHY CONTROLLER..........................................................................................................................................16

5.9

5.10 ANALOG TRANSCEIVER .......................................................................................................................................16

5.11

INTERNAL PLL ....................................................................................................................................................17

6 SSD2828QN4 PIN ASSIGNMENT........................................................................................... 18

7 PIN DESCRIPTION .................................................................................................................. 20

8.1

8 COMMAND TABLE ................................................................................................................. 23

REGISTER DESCRIPTION.......................................................................................................................................25

Device Identification Register.....................................................................................................................25

8.1.1

RGB Interface Control Register 1...............................................................................................................26

8.1.2

RGB Interface Control Register 2...............................................................................................................27

8.1.3

RGB Interface Control Register 3...............................................................................................................28

8.1.4

RGB Interface Control Register 4...............................................................................................................29

8.1.5

RGB Interface Control Register 5...............................................................................................................30

8.1.6

RGB Interface Control Register 6...............................................................................................................31

8.1.7

8.1.8

Configuration Register................................................................................................................................33

VC Control Register....................................................................................................................................35

8.1.9

8.1.10 PLL Control Register..................................................................................................................................36

8.1.11 PLL Configuration Register........................................................................................................................37

8.1.12 Clock Control Register................................................................................................................................38

8.1.13 Packet Size Control Register 1....................................................................................................................39

8.1.14 Packet Size Control Register 2....................................................................................................................40

8.1.15 Packet Size Control Register 3....................................................................................................................41

8.1.16 Generic Packet Drop Register ....................................................................................................................42

8.1.17 Operation Control Register ........................................................................................................................43

8.1.18 Maximum Return Size Register...................................................................................................................44

8.1.19 Return Data Count Register........................................................................................................................45

8.1.20 ACK Response Status Register....................................................................................................................46

Line Control Register..................................................................................................................................47

8.1.21

8.1.22

Interrupt Control Register ..........................................................................................................................49

8.1.23

Interrupt Status Register .............................................................................................................................50

8.1.24 Error Status Register ..................................................................................................................................52

8.1.25 Delay Adjustment Register 1.......................................................................................................................54

8.1.26 Delay Adjustment Register 2.......................................................................................................................55

SSD2828QN4

Rev 1.3

P 3/168 Mar 2013

Solomon Systech

�

8.1.27 Delay Adjustment Register 3.......................................................................................................................56

8.1.28 Delay Adjustment Register 4.......................................................................................................................57

8.1.29 Delay Adjustment Register 5.......................................................................................................................58

8.1.30 Delay Adjustment Register 6.......................................................................................................................59

8.1.31 HS TX Timer Register 1 ..............................................................................................................................60

8.1.32 HS TX Timer Register 2 ..............................................................................................................................61

LP RX Timer Register 1 ..............................................................................................................................62

8.1.33

8.1.34

LP RX Timer Register 2 ..............................................................................................................................63

8.1.35

TE Status Register.......................................................................................................................................64

8.1.36

SPI Read Register .......................................................................................................................................65

8.1.37 PLL Lock Register.......................................................................................................................................66

8.1.38

Test Register ...............................................................................................................................................67

8.1.39

TE Count Register.......................................................................................................................................69

8.1.40 Analog Control Register .............................................................................................................................70

8.1.41 Analog Control Register 2 ..........................................................................................................................71

8.1.42 Analog Control Register 3 ..........................................................................................................................72

8.1.43 Analog Control Register 4 ..........................................................................................................................73

8.1.44

Interrupt Output Control Register ..............................................................................................................74

8.1.45 RGB Interface Control Register 7...............................................................................................................75

8.1.46

Lane Configuration Register.......................................................................................................................76

8.1.47 Delay Adjustment Register 7.......................................................................................................................77

8.1.48 Pull Control Register 1 ...............................................................................................................................78

8.1.49 Pull Control Register 2 ...............................................................................................................................80

8.1.50 Pull Control Register 3 ...............................................................................................................................81

8.1.51 CABC Brightness Control Register 1..........................................................................................................82

8.1.52 CABC Brightness Control Register 2..........................................................................................................83

8.1.53 CABC Brightness Status Register ...............................................................................................................84

8.1.54 Encoder Control Register ...........................................................................................................................85

8.1.55 Video Sync Delay Register..........................................................................................................................86

8.1.56

Trimming Register ......................................................................................................................................87

8.1.57 GPIO1 Register...........................................................................................................................................89

8.1.58 GPIO2 Register...........................................................................................................................................91

8.1.59 DLYA01 Register ........................................................................................................................................93

8.1.60 DLYA23 Register ........................................................................................................................................94

8.1.61 DLYB01 Register ........................................................................................................................................95

8.1.62 DLYB23 Register ........................................................................................................................................96

8.1.63 DLYC01 Register ........................................................................................................................................97

8.1.64 DLYC23 Register ........................................................................................................................................98

8.1.65 Analog Control Register 5 ..........................................................................................................................99

8.1.66 Read Register............................................................................................................................................101

9 CONFIGURATION................................................................................................................. 102

LANE MANAGEMENT.........................................................................................................................................102

USE CASES .........................................................................................................................................................103

RGB + SPI Interface.................................................................................................................................103

9.2.1

MIPI DC Characteristics..........................................................................................................................105

9.2.2

High Speed Clock Transmission ...............................................................................................................106

9.2.3

Data Lane State Flow ...............................................................................................................................106

9.2.4

High Speed Data Transmission.................................................................................................................107

9.2.5

Bi-Directional Data Lane Turnaround .....................................................................................................109

9.2.6

Escape Mode.............................................................................................................................................109

9.2.7

Low Power Data Transmission.................................................................................................................111

9.2.8

Reset Trigger.............................................................................................................................................112

9.2.9

9.2.10

Tearing Effect............................................................................................................................................113

9.2.11 Acknowledge .............................................................................................................................................114

9.2.12 Packet Transmission .................................................................................................................................115

9.2.13 HS Transmission Example ........................................................................................................................115

9.2.14 General Packet Structure..........................................................................................................................116

Long Packet Format .................................................................................................................................116

9.2.15

9.2.16

Short Packet Structure ..............................................................................................................................117

9.1

9.2

SSD2828QN4

Rev 1.3

P 4/168 Mar 2013

Solomon Systech

�

9.3

9.2.17 Data Identifier (DI)...................................................................................................................................117

9.2.18 Victual Channel Identifier (VC)................................................................................................................118

9.2.19 Data Type (DT).........................................................................................................................................118

OPERATING MODES ...........................................................................................................................................122

9.3.2

State machine operation............................................................................................................................135

D-PHY operation ......................................................................................................................................136

9.3.3

Analog Transceiver...................................................................................................................................137

9.3.4

9.3.5

PLL ...........................................................................................................................................................137

9.3.6

Clock Source Example ..............................................................................................................................138

10 EXTERNAL INTERFACE.................................................................................................. 139

10.1 SPI INTERFACE 8 BIT 4 WIRE.............................................................................................................................139

10.2 SPI INTERFACE 8 BIT 3 WIRE.............................................................................................................................141

3 or 4 wires 8bit SPI read back sequence for 0xFF register which is stored MIPI read back data .........143

10.3 SPI INTERFACE 24 BIT 3 WIRE...........................................................................................................................145

3 wires 24bit SPI read back sequence for 0xFF register which is stored MIPI read back data...............147

11 MAXIMUM RATINGS........................................................................................................ 149

10.2.1

10.3.1

12 RECOMMENDED OPERATING CONDITIONS ........................................................... 150

13 DC CHARACTERISTICS................................................................................................... 151

14 AC CHARACTERISTICS................................................................................................... 153

14.1 8 BIT 4 WIRE SPI INTERFACE TIMING................................................................................................................154

14.2 8 BIT 3 WIRE SPI INTERFACE TIMING................................................................................................................155

14.3 24 BIT 3 WIRE SPI INTERFACE TIMING..............................................................................................................156

14.4 RGB INTERFACE TIMING...................................................................................................................................157

14.5 RESET TIMING .................................................................................................................................................158

14.6 TX_CLK TIMING ..............................................................................................................................................158

POWER UP SEQUENCE .................................................................................................... 159

15

16

POWER OFF SEQUENCE ................................................................................................. 160

17 EXAMPLE FOR SYSTEM SLEEP IN AND OUT ........................................................... 161

18

SERIAL LINK DATA ORDER........................................................................................... 162

19

PACKAGE INFORMATION.............................................................................................. 165

19.1 DIMENSION FOR SSD2828QN4 .........................................................................................................................165

SSD2828QN4

Rev 1.3

P 5/168 Mar 2013

Solomon Systech

�

TABLES

TABLE 3-1: ORDERING INFORMATION .................................................................................................................................11

TABLE 6-1: SSD2828QN4 PINOUT DIAGRAM – 68 QFN-EP (TOP VIEW)............................................................................18

TABLE 6-2: SSD2828QN4 PIN ASSIGNMENT – 68 QFN-EP (TOP VIEW) .............................................................................19

TABLE 6-3: SSD2828QN4 RGB DATA ARRANGEMENT.......................................................................................................19

TABLE 7-1: MIPI PINS.........................................................................................................................................................20

TABLE 7-2: INTERFACE LOGIC PINS.....................................................................................................................................21

TABLE 7-3: MISCELLANEOUS PINS ......................................................................................................................................22

TABLE 8-1: SSD2828 REGISTER SUMMARY ........................................................................................................................23

TABLE 8-2: DEVICE IDENTIFICATION REGISTER DESCRIPTION ............................................................................................25

TABLE 8-3: RGB INTERFACE CONTROL REGISTER 1 DESCRIPTION .....................................................................................26

TABLE 8-4: RGB INTERFACE CONTROL REGISTER 2 DESCRIPTION .....................................................................................27

TABLE 8-5: RGB INTERFACE CONTROL REGISTER 3 DESCRIPTION .....................................................................................28

TABLE 8-6: RGB INTERFACE CONTROL REGISTER 4 DESCRIPTION .....................................................................................29

TABLE 8-7: RGB INTERFACE CONTROL REGISTER 5 DESCRIPTION .....................................................................................30

TABLE 8-8: RGB INTERFACE CONTROL REGISTER 6 DESCRIPTION .....................................................................................31

TABLE 8-9: CONFIGURATION REGISTER DESCRIPTION ........................................................................................................33

TABLE 8-10: VC CONTROL REGISTER DESCRIPTION ...........................................................................................................35

TABLE 8-11: PLL CONTROL REGISTER DESCRIPTION..........................................................................................................36

TABLE 8-12: PLL CONFIGURATION REGISTER DESCRIPTION ..............................................................................................37

TABLE 8-13: CLOCK CONTROL REGISTER DESCRIPTION .....................................................................................................38

TABLE 8-14: PACKET SIZE CONTROL REGISTER 1 DESCRIPTION .........................................................................................39

TABLE 8-15: PACKET SIZE CONTROL REGISTER 2 DESCRIPTION .........................................................................................40

TABLE 8-16: PACKET SIZE CONTROL REGISTER 3 DESCRIPTION .........................................................................................41

TABLE 8-17: GENERIC PACKET DROP REGISTER DESCRIPTION ...........................................................................................42

TABLE 8-18: OPERATION CONTROL REGISTER DESCRIPTION ..............................................................................................43

TABLE 8-19: MAXIMUM RETURN SIZE REGISTER DESCRIPTION..........................................................................................44

TABLE 8-20: RETURN DATA COUNT REGISTER DESCRIPTION .............................................................................................45

TABLE 8-21: ACK RESPONSE STATUS REGISTER DESCRIPTION ..........................................................................................46

TABLE 8-22: LINE CONTROL REGISTER DESCRIPTION.........................................................................................................47

TABLE 8-23: INTERRUPT CONTROL REGISTER DESCRIPTION...............................................................................................49

TABLE 8-24: INTERRUPT STATUS REGISTER DESCRIPTION ..................................................................................................50

TABLE 8-25: ERROR STATUS REGISTER DESCRIPTION.........................................................................................................52

TABLE 8-26: DELAY ADJUSTMENT REGISTER 1 DESCRIPTION.............................................................................................54

TABLE 8-27: DELAY ADJUSTMENT REGISTER 2 DESCRIPTION.............................................................................................55

TABLE 8-28: DELAY ADJUSTMENT REGISTER 3 DESCRIPTION.............................................................................................56

TABLE 8-29: DELAY ADJUSTMENT REGISTER 4 0/1 DESCRIPTION.......................................................................................57

TABLE 8-30: DELAY ADJUSTMENT REGISTER 5 DESCRIPTION.............................................................................................58

TABLE 8-31: DELAY ADJUSTMENT REGISTER 6 DESCRIPTION.............................................................................................59

TABLE 8-32: HS TX TIMER REGISTER 1 DESCRIPTION........................................................................................................60

TABLE 8-33: HS RX TIMER REGISTER 2 DESCRIPTION........................................................................................................61

TABLE 8-34: LP TX TIMER REGISTER 1 DESCRIPTION ........................................................................................................62

TABLE 8-35: LP TX TIMER REGISTER 2 DESCRIPTION ........................................................................................................63

TABLE 8-36: TE STATUS REGISTER DESCRIPTION...............................................................................................................64

TABLE 8-37: SPI READ REGISTER DESCRIPTION .................................................................................................................65

TABLE 8-38: PLL LOCK REGISTER DESCRIPTION................................................................................................................66

TABLE 8-39: TEST REGISTER DESCRIPTION.........................................................................................................................67

TABLE 8-40: TE COUNT REGISTER DESCRIPTION................................................................................................................69

TABLE 8-41: ANALOG CONTROL 1 REGISTER DESCRIPTION................................................................................................70

TABLE 8-42: ANALOG CONTROL REGISTER 2 DESCRIPTION................................................................................................71

TABLE 8-43: ANALOG CONTROL REGISTER 3 DESCRIPTION................................................................................................72

TABLE 8-44: ANALOG CONTROL REGISTER 4 DESCRIPTION................................................................................................73

TABLE 8-45: INTERRUPT OUTPUT CONTROL REGISTER DESCRIPTION .................................................................................74

TABLE 8-46: RGB INTERFACE CONTROL REGISTER 7 DESCRIPTION ...................................................................................75

TABLE 8-47: LANE CONFIGURATION REGISTER DESCRIPTION.............................................................................................76

TABLE 8-48: DELAY ADJUSTMENT REGISTER 7 DESCRIPTION.............................................................................................77

TABLE 8-49: PULL CONTROL REGISTER 1 DESCRIPTION .....................................................................................................78

TABLE 8-50: PULL CONTROL REGISTER 2 DESCRIPTION .....................................................................................................80

TABLE 8-51: PULL CONTROL REGISTER 3 DESCRIPTION .....................................................................................................81

SSD2828QN4

Rev 1.3

P 6/168 Mar 2013

Solomon Systech

�

TABLE 8-52: CABC BRIGHTNESS CONTROL REGISTER 1 DESCRIPTION ..............................................................................82

TABLE 8-53: CABC BRIGHTNESS CONTROL REGISTER 2 DESCRIPTION ..............................................................................83

TABLE 8-54: CABC BRIGHTNESS STATUS REGISTER DESCRIPTION ....................................................................................84

TABLE 8-55: ENCODER CONTROL REGISTER DESCRIPTION .................................................................................................85

TABLE 8-56: VIDEO SYNC DELAY REGISTER DESCRIPTION.................................................................................................86

TABLE 8-57: TRIMMING REGISTER DESCRIPTION ................................................................................................................87

TABLE 8-58: GPIO1 REGISTER DESCRIPTION......................................................................................................................89

TABLE 8-59: GPIO1 REGISTER DESCRIPTION......................................................................................................................91

TABLE 8-60: DLYA01 REGISTER DESCRIPTION..................................................................................................................93

TABLE 8-61: DLYA23 REGISTER DESCRIPTION..................................................................................................................94

TABLE 8-62: DLYB01 REGISTER DESCRIPTION ..................................................................................................................95

TABLE 8-63: DLYB23 REGISTER DESCRIPTION ..................................................................................................................96

TABLE 8-64: DLYC01 REGISTER DESCRIPTION ..................................................................................................................97

TABLE 8-65: DLYC23 REGISTER DESCRIPTION ..................................................................................................................98

TABLE 8-66: ACR5 REGISTER DESCRIPTION.......................................................................................................................99

TABLE 8-67: READ REGISTER DESCRIPTION......................................................................................................................101

TABLE 9-1: SSD2828 LANE MANAGEMENT ......................................................................................................................102

TABLE 9-2: OPERATION DURING VIDEO MODE BLLP PERIOD ..........................................................................................104

TABLE 9-3: DSI STATE CODE AND DC CHARACTERISTICS................................................................................................105

TABLE 9-4: DATA LANE MODE ENTERING/EXITING SEQUENCES ......................................................................................106

TABLE 9-5: START-OF-TRANSMISSION SEQUENCE.............................................................................................................107

TABLE 9-6: END-OF-TRANSMISSION SEQUENCE................................................................................................................107

TABLE 9-7: MIPI ESCAPE MODE ENTRY CODE .................................................................................................................110

TABLE 9-8: DATA TYPES FOR PROCESSOR-SOURCED PACKETS .........................................................................................118

TABLE 9-9: DATA TYPES FOR PERIPHERAL-SOURCED PACKETS ........................................................................................119

TABLE 9-10: PLL SETTING FOR NON-BURST MODE (PLL REFERENCE USING PCLK) .........................................................123

TABLE 9-11: PLL SETTING FOR NON-BURST MODE (PLL REFERENCE USING TX_CLK) .....................................................123

TABLE 9-12: PLL SETTING FOR BURST MODE...................................................................................................................124

TABLE 9-13: MIPI ERROR REPORT.....................................................................................................................................132

TABLE 11-1: MAXIMUM RATINGS (VOLTAGE REFERENCED TO VSS).................................................................................149

TABLE 12-1: RECOMMENDED OPERATING CONDITIONS....................................................................................................150

TABLE 13-1: DC CHARACTERISTICS..................................................................................................................................151

TABLE 13-2: HS TRANSMITTER DC CHARACTERISTICS ....................................................................................................152

TABLE 13-3: LP TRANSMITTER DC CHARACTERISTICS.....................................................................................................152

TABLE 13-4: LP RECEIVER DC CHARACTERISTICS ...........................................................................................................152

TABLE 14-1: 8 BIT 4 WIRE SPI INTERFACE TIMING CHARACTERISTICS.............................................................................154

TABLE 14-2: 8 BIT 3 WIRE SPI INTERFACE TIMING CHARACTERISTICS.............................................................................155

TABLE 14-3: 24 BIT 3 WIRE SPI INTERFACE TIMING CHARACTERISTICS...........................................................................156

TABLE 14-4: RGB INTERFACE TIMING CHARACTERISTICS................................................................................................157

TABLE 14-5: RESET TIMING.............................................................................................................................................158

TABLE 14-6: TX_CLK TIMING CHARACTERISTICS ...........................................................................................................158

SSD2828QN4

Rev 1.3

P 7/168 Mar 2013

Solomon Systech

�

FIGURES

FIGURE 4-1: OVERVIEW OF DISPLAY SYSTEM USING SSD2828............................................................................................11

FIGURE 4-2: SSD2828 INTERFACE DIAGRAM......................................................................................................................12

FIGURE 4-3: BLOCK DIAGRAM ............................................................................................................................................13

FIGURE 5-1: THE CLOCKING SCHEME OF SSD2828.............................................................................................................14

FIGURE 8-1: TIMING FOR DELAY CALCULATION ..................................................................................................................54

FIGURE 8-2: TIMING FOR DELAY CALCULATION ..................................................................................................................55

FIGURE 8-3: TWAKEUP PERIOD DELAY CALCULATION............................................................................................................58

FIGURE 8-4: TIMING FOR DELAY CALCULATION ..................................................................................................................59

FIGURE 9-1: SSD2828 WITH RGB AND SPI INTERFACE ....................................................................................................103

FIGURE 9-2: MIPI LINE LEVELS ........................................................................................................................................105

FIGURE 9-3: SWITCHING THE CLOCK LANE BETWEEN HIGH SPEED MODE AND LOW-POWER MODE ................................106

FIGURE 9-4: HIGH-SPEED DATA TRANSMISSION IN BURSTS ..............................................................................................108

FIGURE 9-5: TURNAROUND PROCEDURE ...........................................................................................................................109

FIGURE 9-6: LOW POWER DATA TRANSMISSION ...............................................................................................................111

FIGURE 9-7: TRIGGER – RESET COMMAND IN ESCAPE MODE............................................................................................112

FIGURE 9-8: TEARING EFFECT COMMAND IN ESCAPE MODE.............................................................................................113

FIGURE 9-9: ACKNOWLEDGE COMMAND IN ESCAPE MODE...............................................................................................114

FIGURE 9-10: TWO DATA TRANSMISSION MODE (SEPARATE, SINGLE)..............................................................................115

FIGURE 9-11: ONE LANE DATA TRANSMISSION EXAMPLE ................................................................................................115

FIGURE 9-12: TWO LANE HS TRANSMISSION EXAMPLE....................................................................................................115

FIGURE 9-13: ENDIAN EXAMPLE (LONG PACKET) .............................................................................................................116

FIGURE 9-14: LONG PACKET STRUCTURE..........................................................................................................................116

FIGURE 9-15: SHORT PACKET STRUCTURE ........................................................................................................................117

FIGURE 9-16: DATA INDENTIFIER STRUCTURE ..................................................................................................................117

FIGURE 9-17: 16-BIT PER PIXEL RGB COLOR FORMAT, LONG PACKET FOR MIPI INTERFACE ...........................................120

FIGURE 9-18: 18-BIT PER PIXEL– RGB COLOR FORMAT, LONG PACKET FOR MIPI INTERFACE.........................................120

FIGURE 9-19: 18-BIT PER PIXEL IN THREE BYTES – RGB COLOR FORMAT, LONG PACKET FOR MIPI INTERFACE.............121

FIGURE 9-20: 24-BIT PER PIXEL – RGB COLOR FORMAT, LONG PACKET FOR MIPI INTERFACE........................................121

FIGURE 9-21: ILLUSTRATION OF RGB INTERFACE PARAMETERS FOR NON-BURST MODE WITH SYNC PULSES .................122

FIGURE 9-22: ILLUSTRATION OF RGB INTERFACE PARAMETERS FOR NON-BURST MODE WITH SYNC EVENTS AND BURST

MODE ........................................................................................................................................................................123

FIGURE 9-23: NON-BURST MODE MIPI STRUCTURE ..........................................................................................................124

FIGURE 9-24: BURST MODE MIPI STRUCTURE...................................................................................................................125

FIGURE 9-25: ACKNOWLEDGEMENT HANDLING AFTER NON-READ COMMAND ................................................................130

FIGURE 9-26: ACKNOWLEDGEMENT HANDLING AFTER READ COMMAND.........................................................................131

FIGURE 9-27: ILLUSTRATION OF INTERRUPT LATENCY......................................................................................................134

FIGURE 10-1: ILLUSTRATION OF WRITE OPERATION FOR 8 BIT 4 WIRE INTERFACE...........................................................140

FIGURE 10-2: ILLUSTRATION OF READ OPERATION FOR 8 BIT 4 WIRE INTERFACE ............................................................140

FIGURE 10-3: ILLUSTRATION OF WRITE OPERATION FOR 8 BIT 3 WIRE INTERFACE...........................................................141

FIGURE 10-4: ILLUSTRATION OF READ OPERATION FOR 8 BIT 3 WIRE INTERFACE ............................................................142

FIGURE 10-5: ILLUSTRATION OF WRITE OPERATION FOR 24 BIT 3 WIRE INTERFACE .........................................................145

FIGURE 10-6: ILLUSTRATION OF READ OPERATION FOR 24 BIT 3 WIRE INTERFACE ..........................................................146

FIGURE 14-1: 8 BIT 4 WIRE SPI INTERFACE TIMING DIAGRAM .........................................................................................154

FIGURE 14-2: 8 BIT 3 WIRE SPI INTERFACE TIMING DIAGRAM .........................................................................................155

FIGURE 14-3: 24 BIT 3 WIRE SPI INTERFACE TIMING DIAGRAM .......................................................................................156

FIGURE 14-4: RGB INTERFACE TIMING DIAGRAM ............................................................................................................157

FIGURE 14-5: TX_CLK TIMING DIAGRAM........................................................................................................................158

FIGURE 18-1- PACKAGE INFORMATION .............................................................................................................................165

FIGURE 18-2- MARKING INFORMATION.............................................................................................................................166

FIGURE 18-3- TRAY INFORMATION....................................................................................................................................167

SSD2828QN4

Rev 1.3

P 8/168 Mar 2013

Solomon Systech

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc