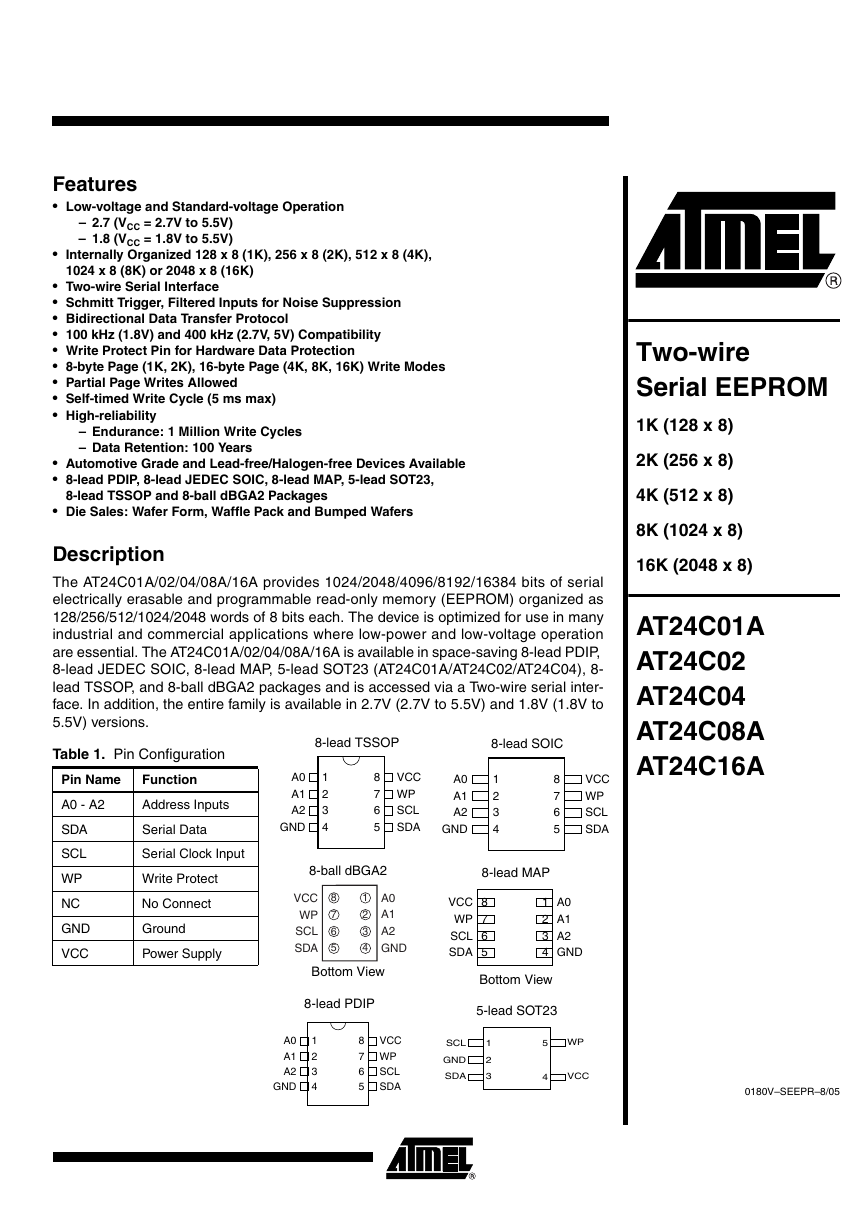

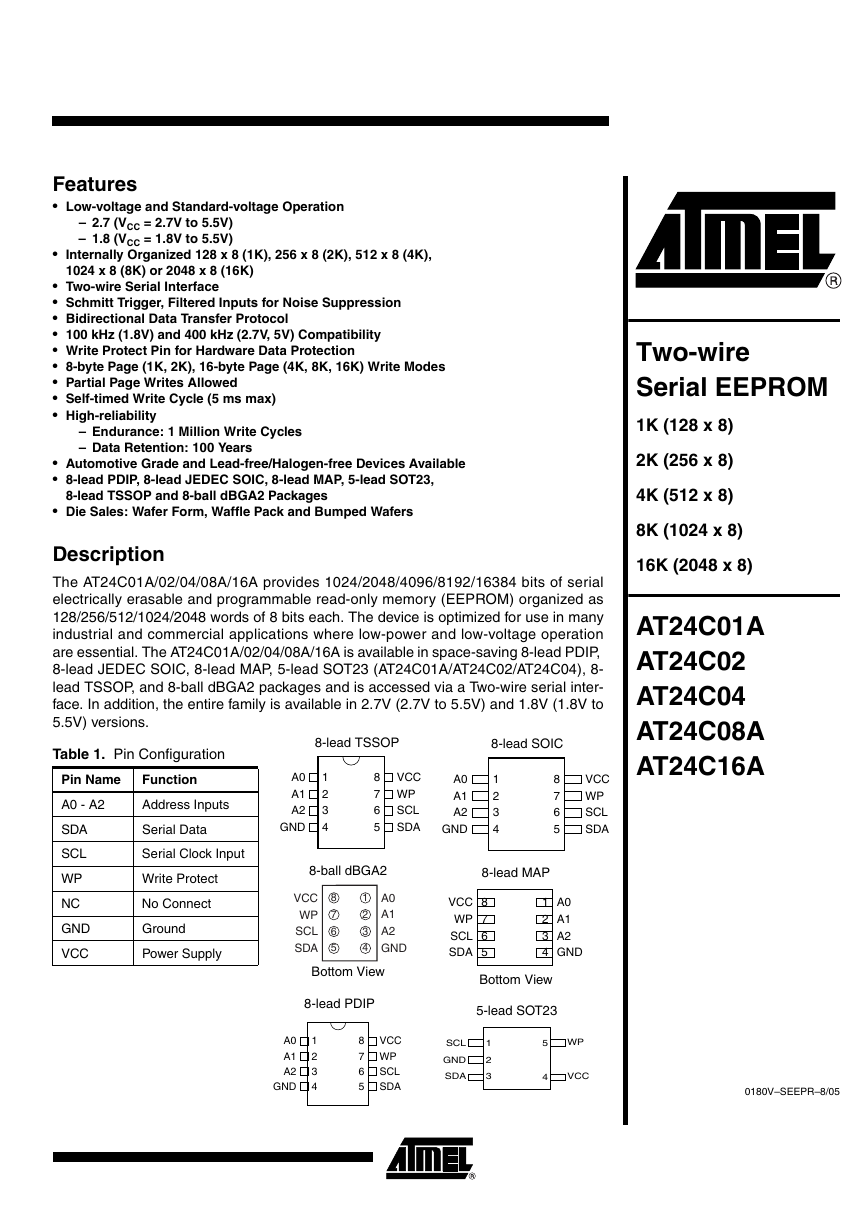

1Features•Low-voltage and Standard-voltage Operation–2.7 (VCC = 2.7V to 5.5V)–1.8 (VCC = 1.8V to 5.5V)Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),1024 x 8 (8K) or 2048 x 8 (16K)Two-wire Serial InterfaceSchmitt Trigger, Filtered Inputs for Noise SuppressionBidirectional Data Transfer Protocol100 kHz (1.8V) and 400 kHz (2.7V, 5V) CompatibilityWrite Protect Pin for Hardware Data Protection8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write ModesPartial Page Writes AllowedSelf-timed Write Cycle (5 ms max)High-reliability–Endurance: 1 Million Write Cycles–Data Retention: 100 YearsAutomotive Grade and Lead-free/Halogen-free Devices Available8-lead PDIP, 8-lead JEDEC SOIC, 8-lead MAP, 5-lead SOT23,8-lead TSSOP and 8-ball dBGA2 PackagesDie Sales: Wafer Form, Waffle Pack and Bumped WafersDescriptionThe AT24C01A/02/04/08A/16A provides 1024/2048/4096/8192/16384 bits of serialelectrically erasable and programmable read-only memory (EEPROM) organized as128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in manyindustrial and commercial applications where low-power and low-voltage operationare essential. The AT24C01A/02/04/08A/16A is available in space-saving 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead MAP, 5-lead SOT23 (AT24C01A/AT24C02/AT24C04), 8-lead TSSOP, and 8-ball dBGA2 packages and is accessed via a Two-wire serial inter-face. In addition, the entire family is available in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to5.5V) versions. Table 1. Pin ConfigurationPin NameFunctionA0 - A2Address InputsSDASerial DataSCLSerial Clock Input WPWrite ProtectNCNo ConnectGNDGroundVCCPower SupplyTwo-wireSerial EEPROM1K (128 x 8)2K (256 x 8)4K (512 x 8)8K (1024 x 8)16K (2048 x 8)AT24C01AAT24C02AT24C04AT24C08AAT24C16A0180V–SEEPR–8/058-lead SOIC12348765A0A1A2GNDVCCWPSCLSDA8-lead PDIP12348765A0A1A2GNDVCCWPSCLSDA8-lead MAPBottom View12348765VCCWPSCLSDAA0A1A2GND5-lead SOT2312354SCLGNDSDAWPVCC8-ball dBGA2Bottom ViewVCCWPSCLSDAA0A1A2GND123487658-lead TSSOP12348765A0A1A2GNDVCCWPSCLSDA�

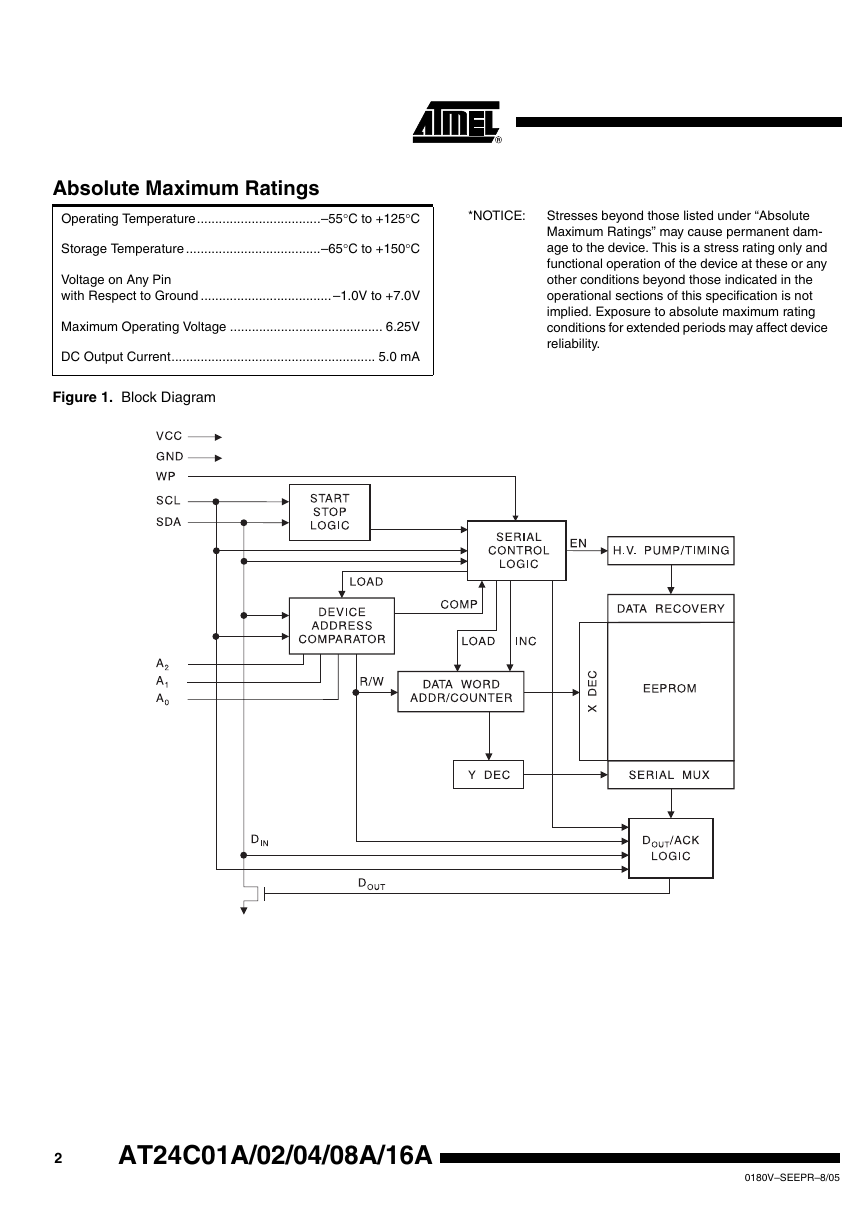

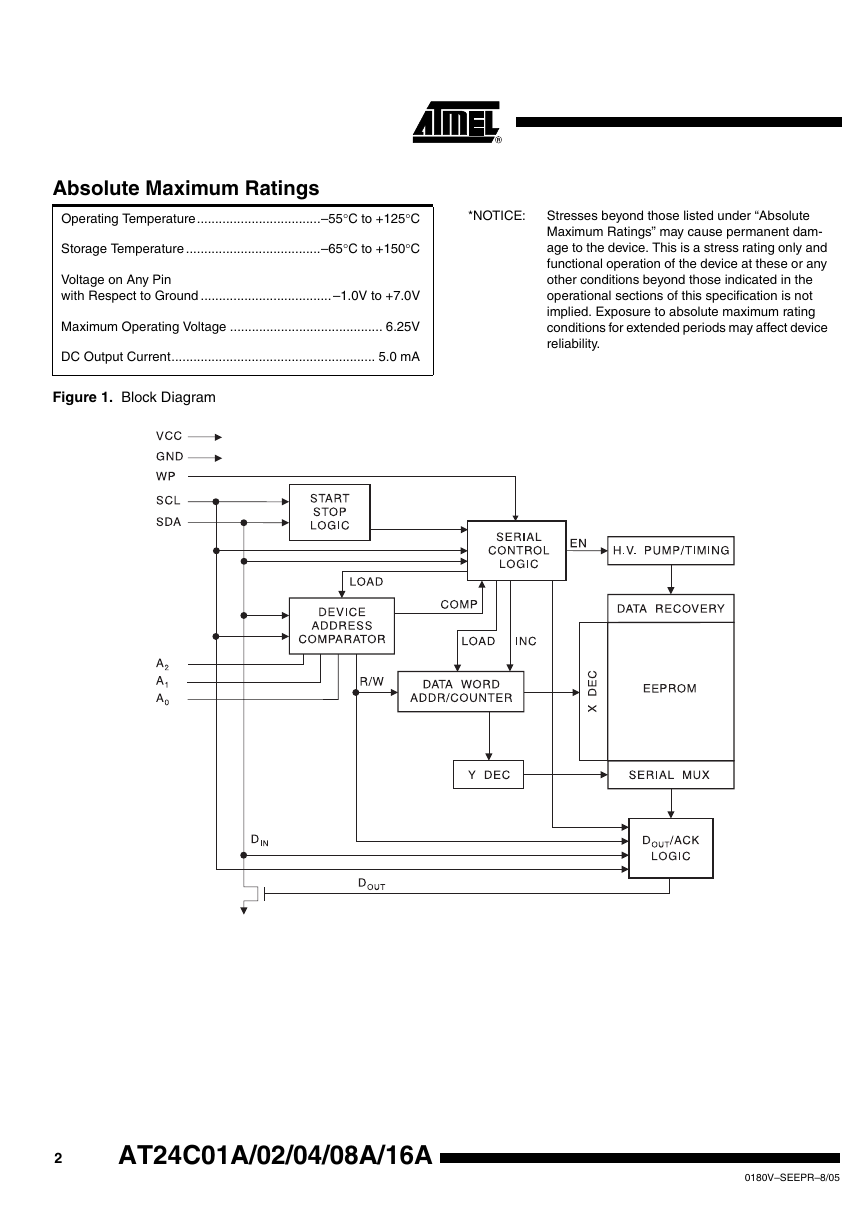

2AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Figure 1. Block DiagramAbsolute Maximum RatingsOperating Temperature..................................–55°C to +125°C*NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage Temperature.....................................–65°C to +150°CVoltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0VMaximum Operating Voltage..........................................6.25VDC Output Current........................................................5.0 mA�

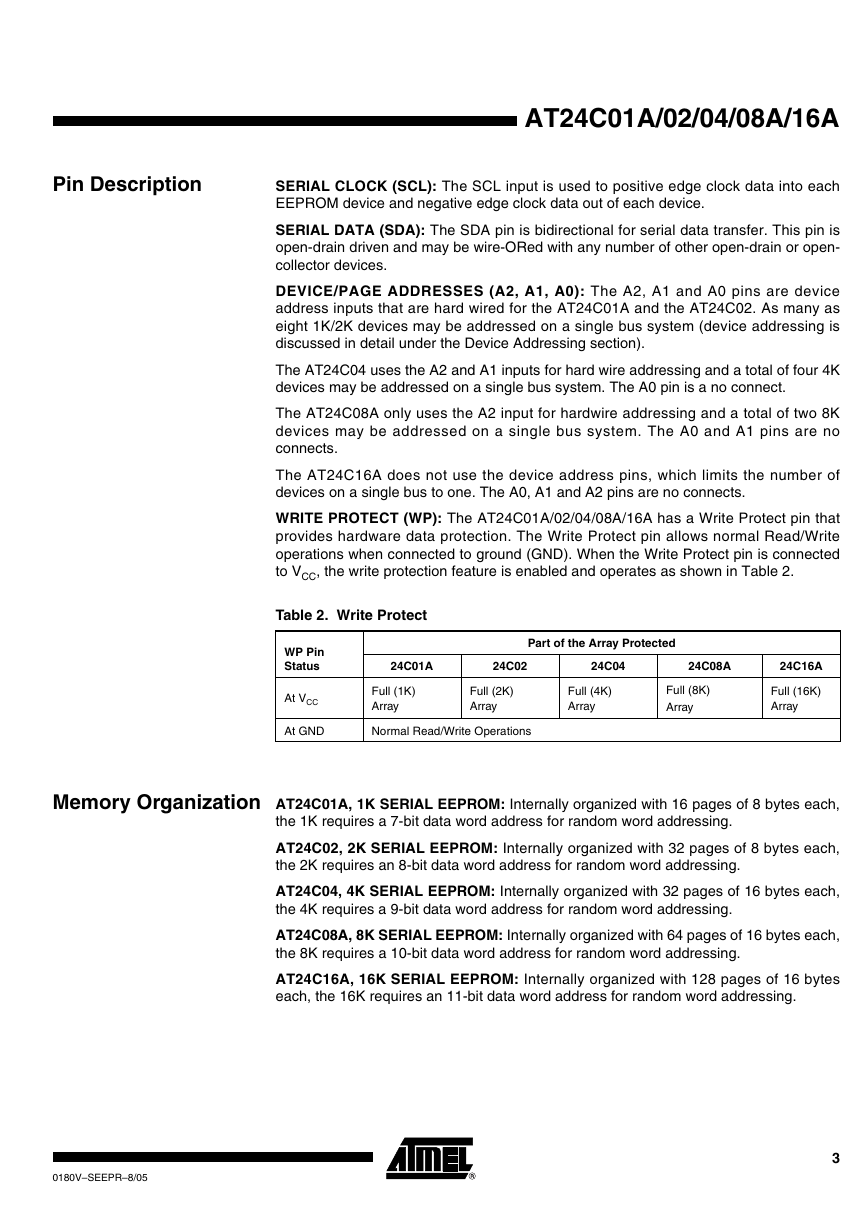

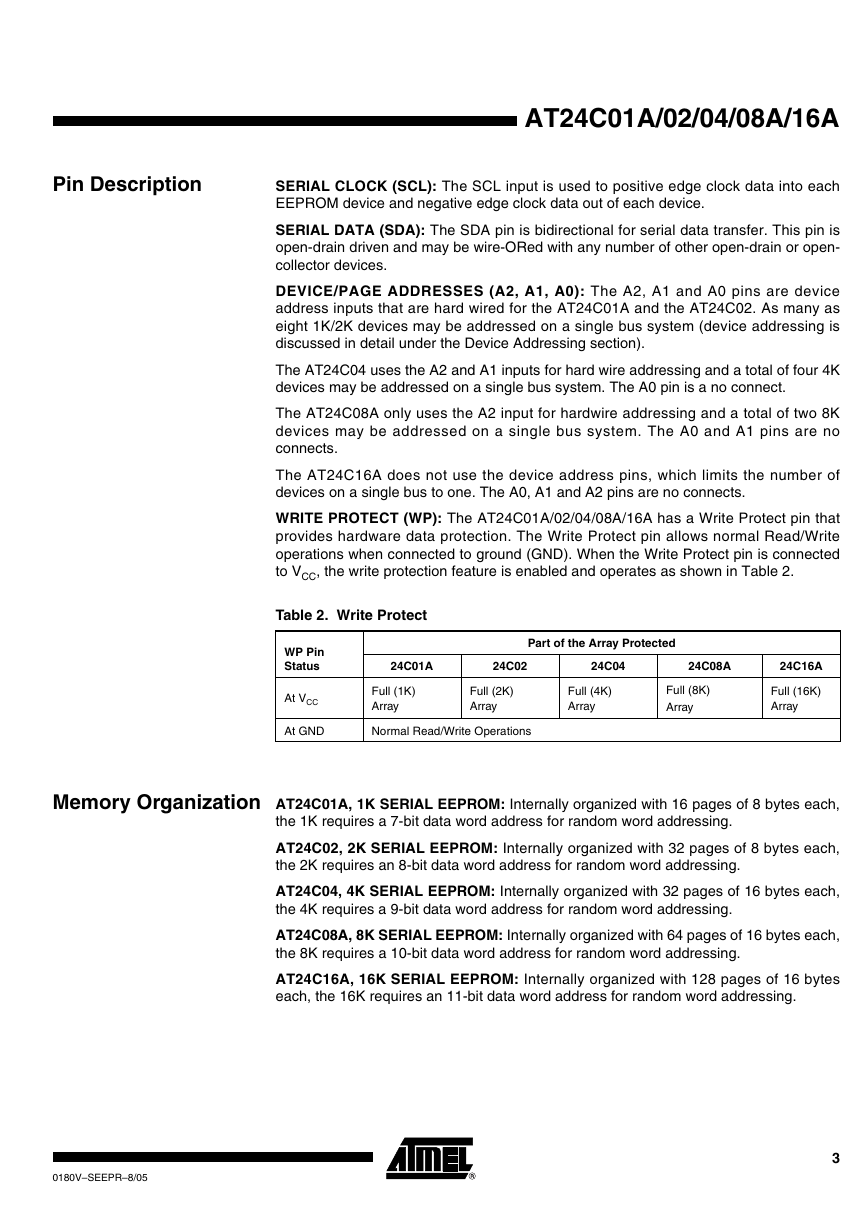

3AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into eachEEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin isopen-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are deviceaddress inputs that are hard wired for the AT24C01A and the AT24C02. As many aseight 1K/2K devices may be addressed on a single bus system (device addressing isdiscussed in detail under the Device Addressing section).The AT24C04 uses the A2 and A1 inputs for hard wire addressing and a total of four 4Kdevices may be addressed on a single bus system. The A0 pin is a no connect.The AT24C08A only uses the A2 input for hardwire addressing and a total of two 8Kdevices may be addressed on a single bus system. The A0 and A1 pins are noconnects.The AT24C16A does not use the device address pins, which limits the number ofdevices on a single bus to one. The A0, A1 and A2 pins are no connects.WRITE PROTECT (WP): The AT24C01A/02/04/08A/16A has a Write Protect pin thatprovides hardware data protection. The Write Protect pin allows normal Read/Writeoperations when connected to ground (GND). When the Write Protect pin is connectedto VCC, the write protection feature is enabled and operates as shown in Table 2.Table 2. Write ProtectMemory OrganizationAT24C01A, 1K SERIAL EEPROM: Internally organized with 16 pages of 8 bytes each,the 1K requires a 7-bit data word address for random word addressing. AT24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each,the 2K requires an 8-bit data word address for random word addressing. AT24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each,the 4K requires a 9-bit data word address for random word addressing. AT24C08A, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each,the 8K requires a 10-bit data word address for random word addressing. AT24C16A, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 byteseach, the 16K requires an 11-bit data word address for random word addressing. WP PinStatusPart of the Array Protected24C01A24C0224C0424C08A24C16AAt VCCFull (1K) ArrayFull (2K) ArrayFull (4K) ArrayFull (8K) ArrayFull (16K) ArrayAt GNDNormal Read/Write Operations�

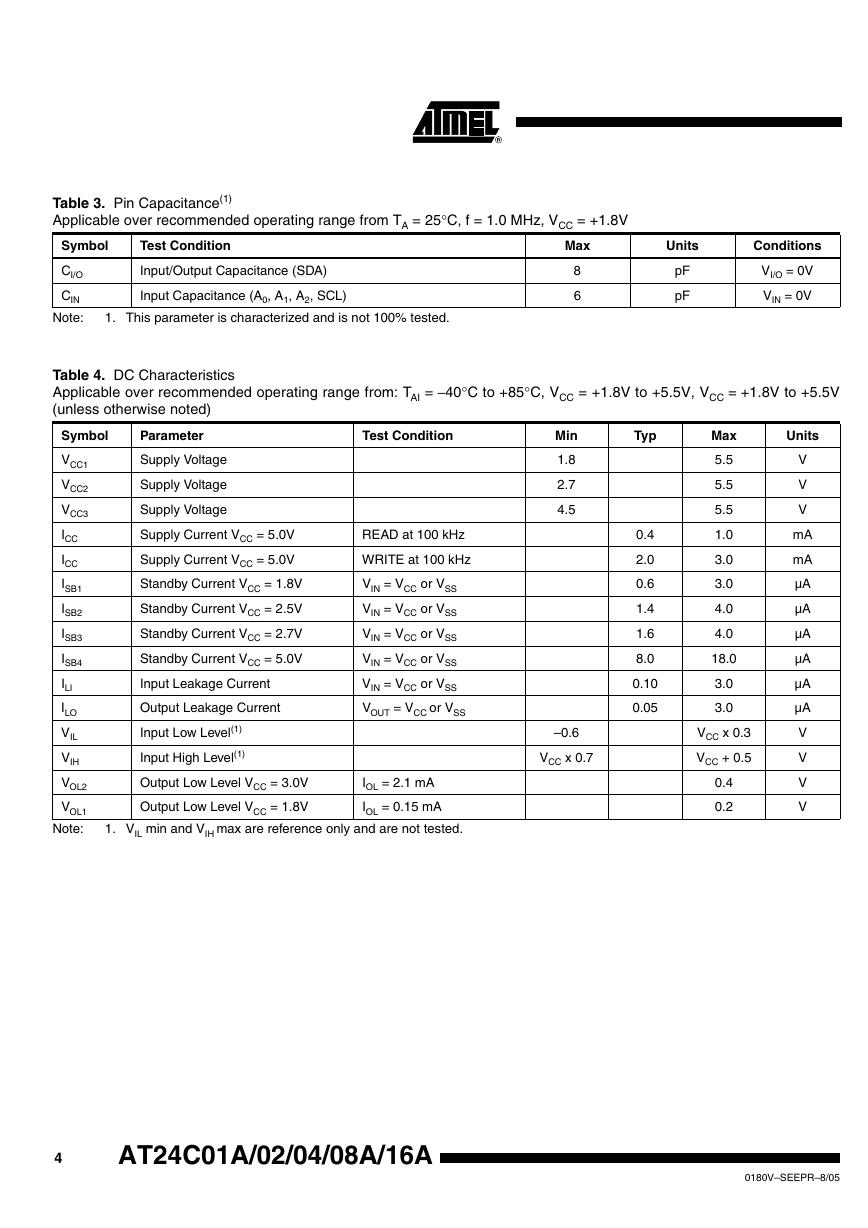

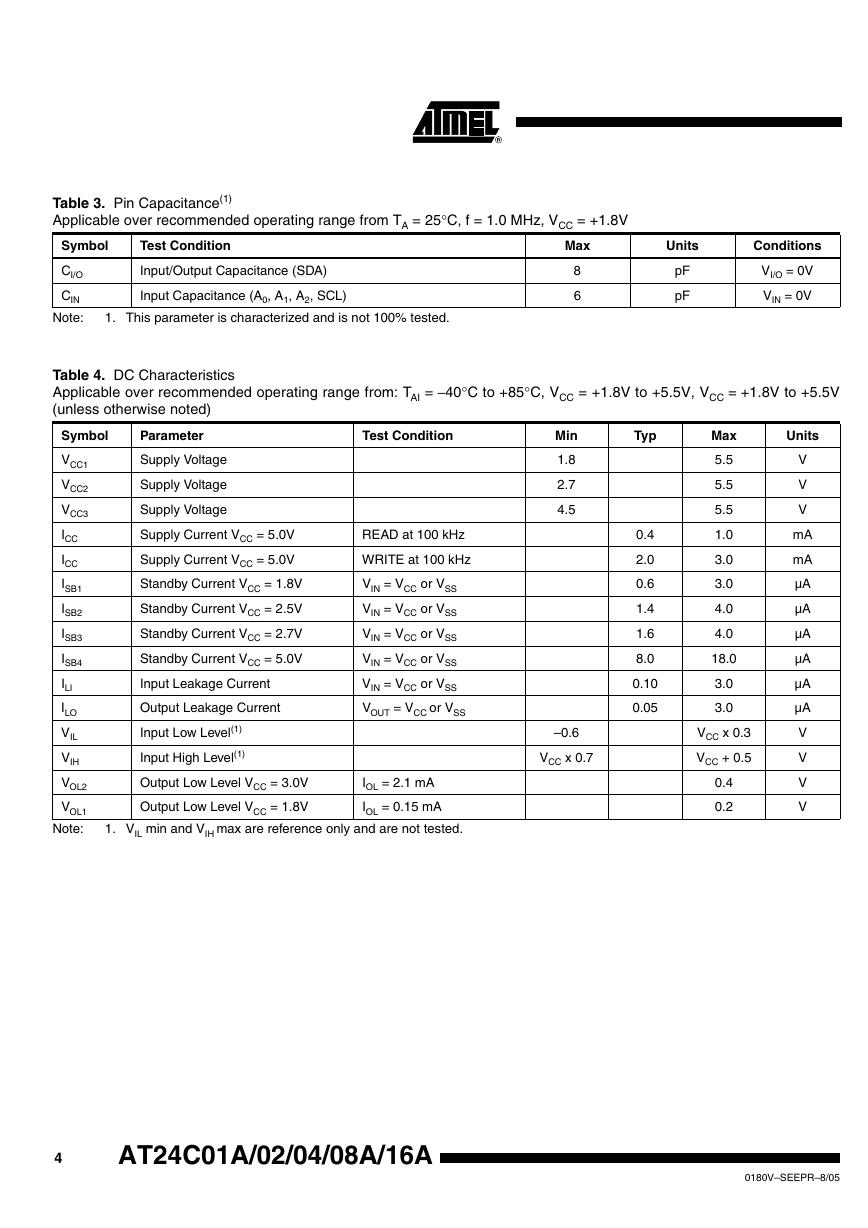

4AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Note:1.This parameter is characterized and is not 100% tested.Note:1.VIL min and VIH max are reference only and are not tested. Table 3. Pin Capacitance(1)Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +1.8VSymbolTest ConditionMaxUnitsConditionsCI/OInput/Output Capacitance (SDA)8pFVI/O = 0VCINInput Capacitance (A0, A1, A2, SCL)6pFVIN = 0VTable 4. DC CharacteristicsApplicable over recommended operating range from: TAI = –40°C to +85°C, VCC = +1.8V to +5.5V, VCC=+1.8V to +5.5V(unless otherwise noted)SymbolParameterTest ConditionMinTypMaxUnitsVCC1Supply Voltage1.85.5VVCC2Supply Voltage2.75.5VVCC3Supply Voltage4.55.5VICCSupply Current VCC = 5.0VREAD at 100 kHz0.41.0mAICCSupply Current VCC = 5.0VWRITE at 100 kHz2.03.0mAISB1Standby Current VCC = 1.8VVIN = VCC or VSS0.63.0µAISB2Standby Current VCC = 2.5VVIN = VCC or VSS1.44.0µAISB3Standby Current VCC = 2.7VVIN = VCC or VSS1.64.0µAISB4Standby Current VCC = 5.0VVIN = VCC or VSS8.018.0µAILIInput Leakage CurrentVIN = VCC or VSS0.103.0µAILOOutput Leakage CurrentVOUT = VCC or VSS0.053.0µAVILInput Low Level(1)–0.6VCC x 0.3VVIHInput High Level(1)VCC x 0.7VCC + 0.5VVOL2Output Low Level VCC = 3.0VIOL = 2.1 mA0.4VVOL1Output Low Level VCC = 1.8VIOL = 0.15 mA0.2V�

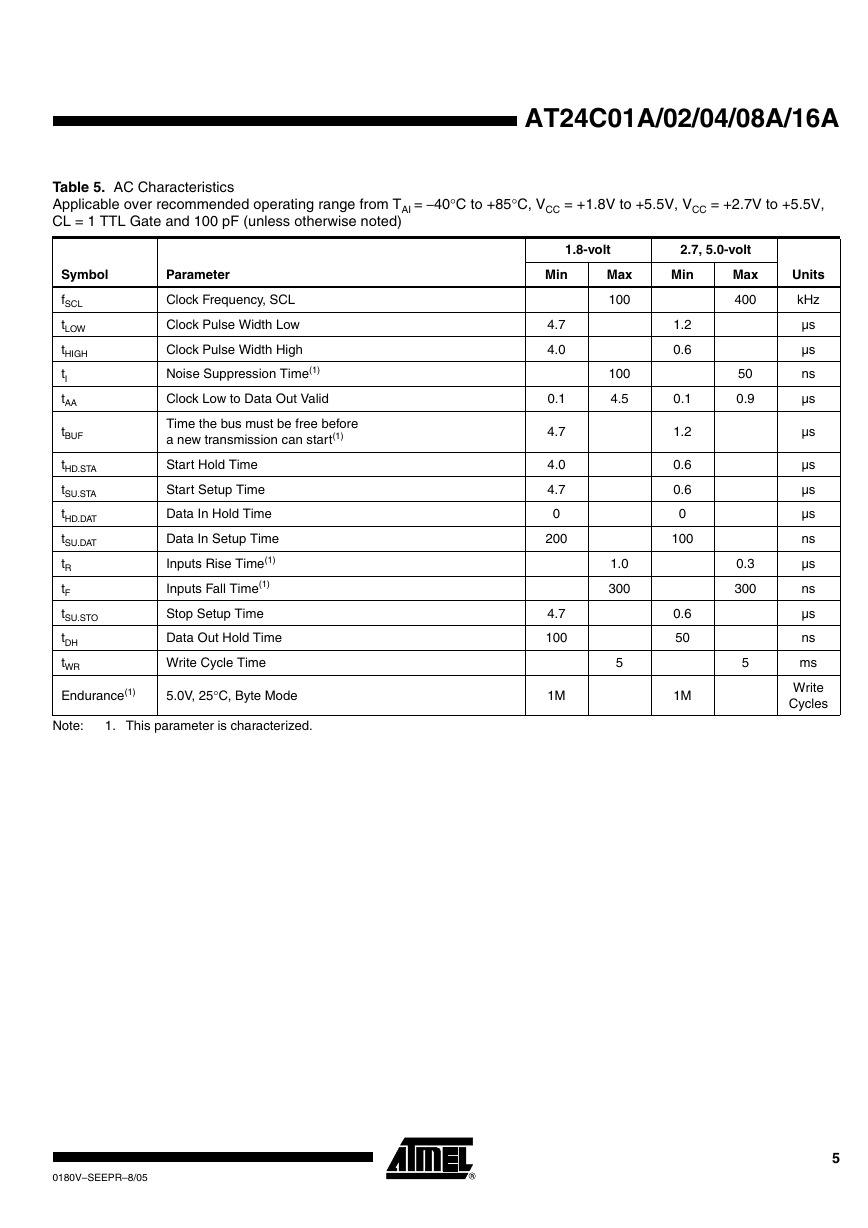

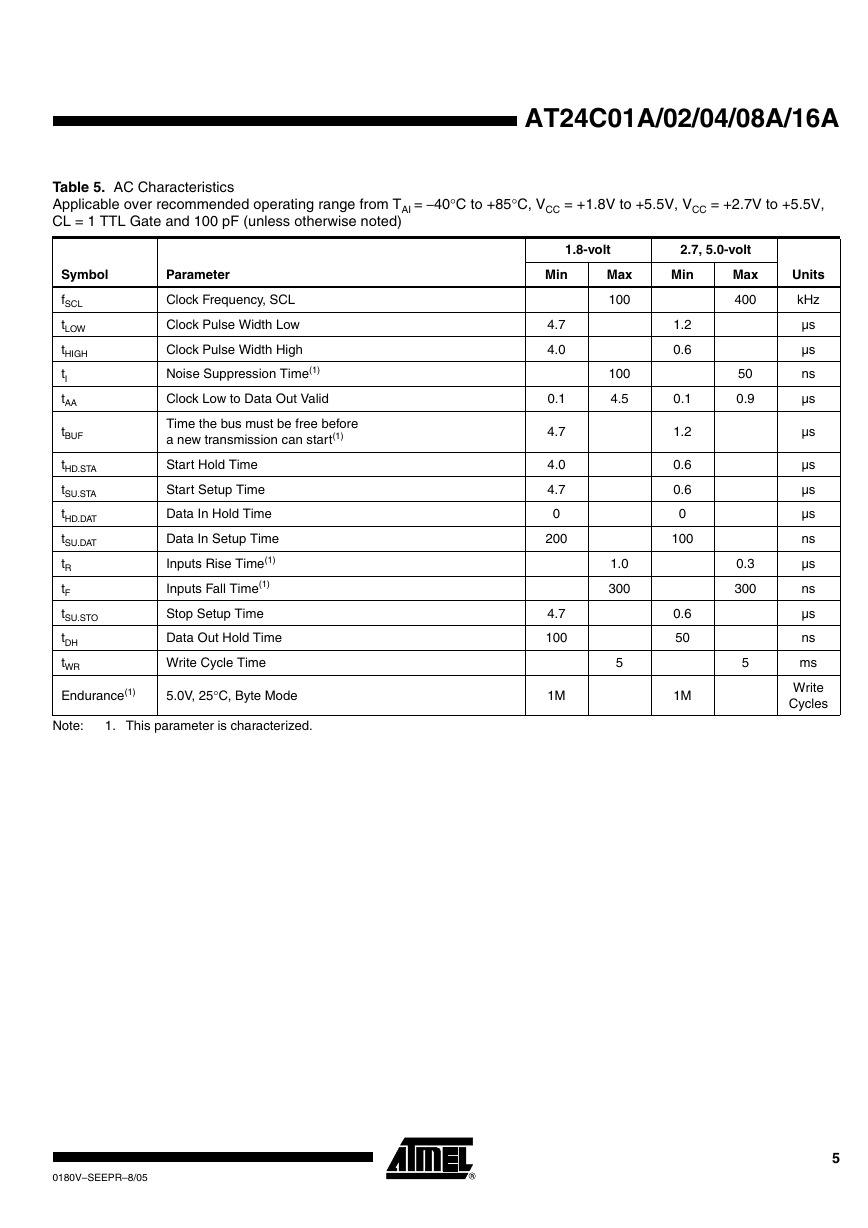

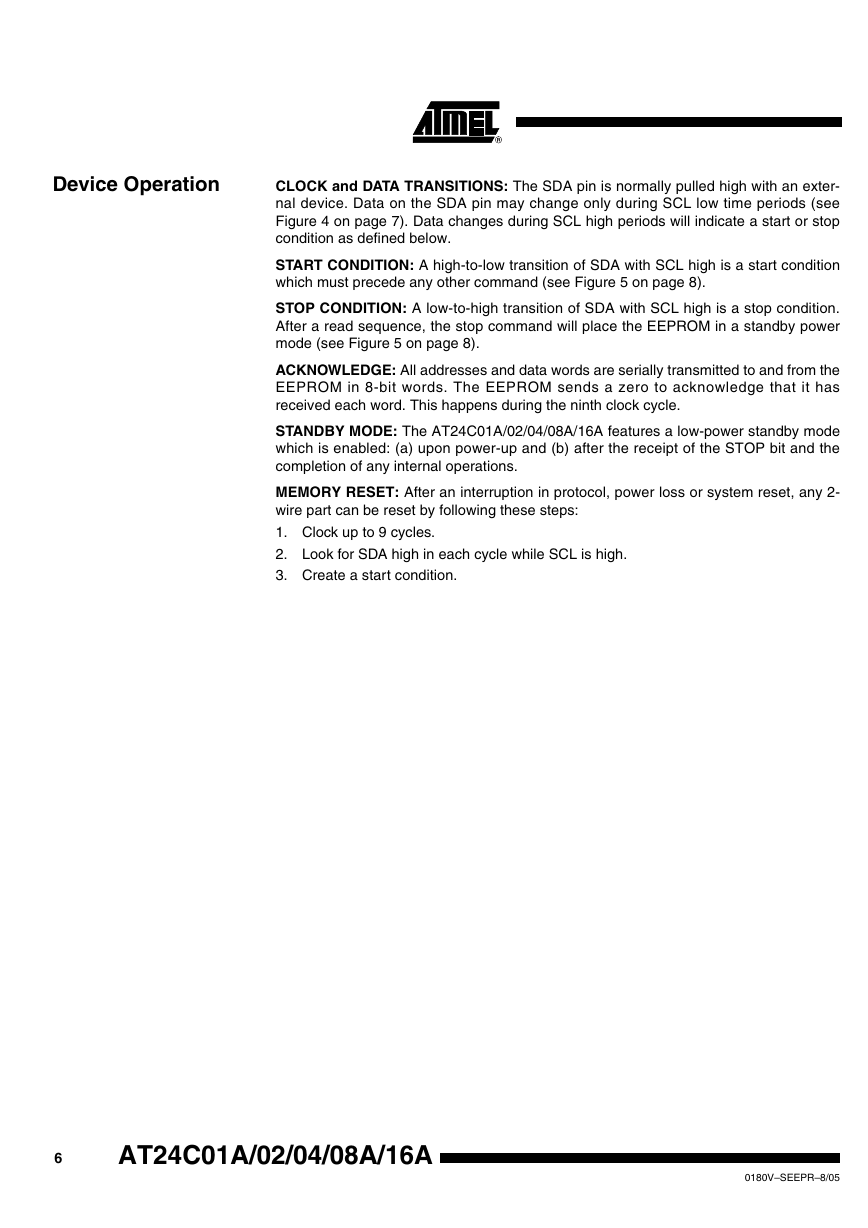

5AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Note:1.This parameter is characterized.Table 5. AC CharacteristicsApplicable over recommended operating range from TAI = –40°C to +85°C, VCC = +1.8V to +5.5V, VCC = +2.7V to +5.5V,CL = 1 TTL Gate and 100pF (unless otherwise noted)SymbolParameter1.8-volt 2.7, 5.0-voltUnitsMinMaxMinMaxfSCLClock Frequency, SCL100400kHztLOWClock Pulse Width Low4.71.2µstHIGHClock Pulse Width High4.00.6µstINoise Suppression Time(1)10050nstAAClock Low to Data Out Valid0.14.50.10.9µstBUFTime the bus must be free before a new transmission can start(1)4.71.2µstHD.STAStart Hold Time4.00.6µstSU.STAStart Setup Time4.70.6µstHD.DATData In Hold Time00µstSU.DATData In Setup Time200100nstRInputs Rise Time(1)1.00.3µstFInputs Fall Time(1)300300nstSU.STOStop Setup Time4.70.6µstDHData Out Hold Time10050nstWRWrite Cycle Time55msEndurance(1)5.0V, 25°C, Byte Mode1M1MWrite Cycles�

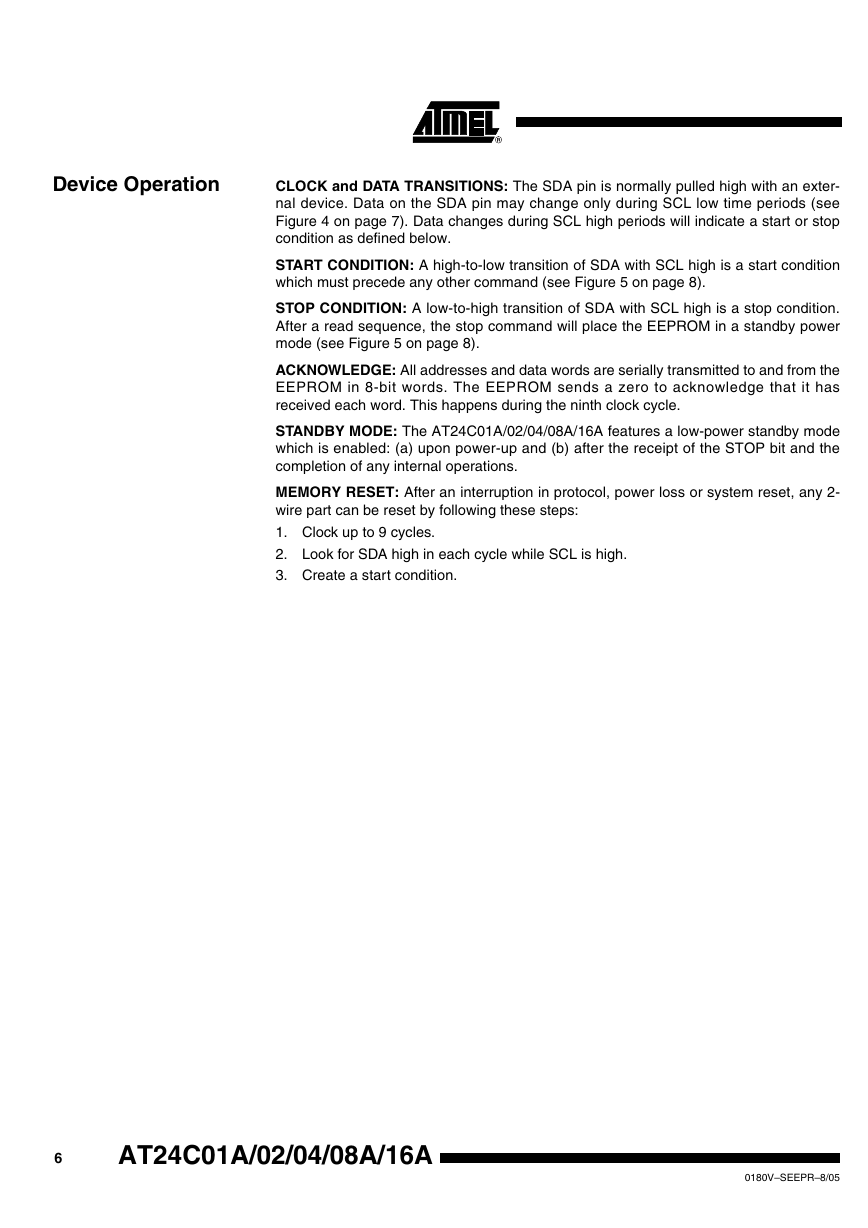

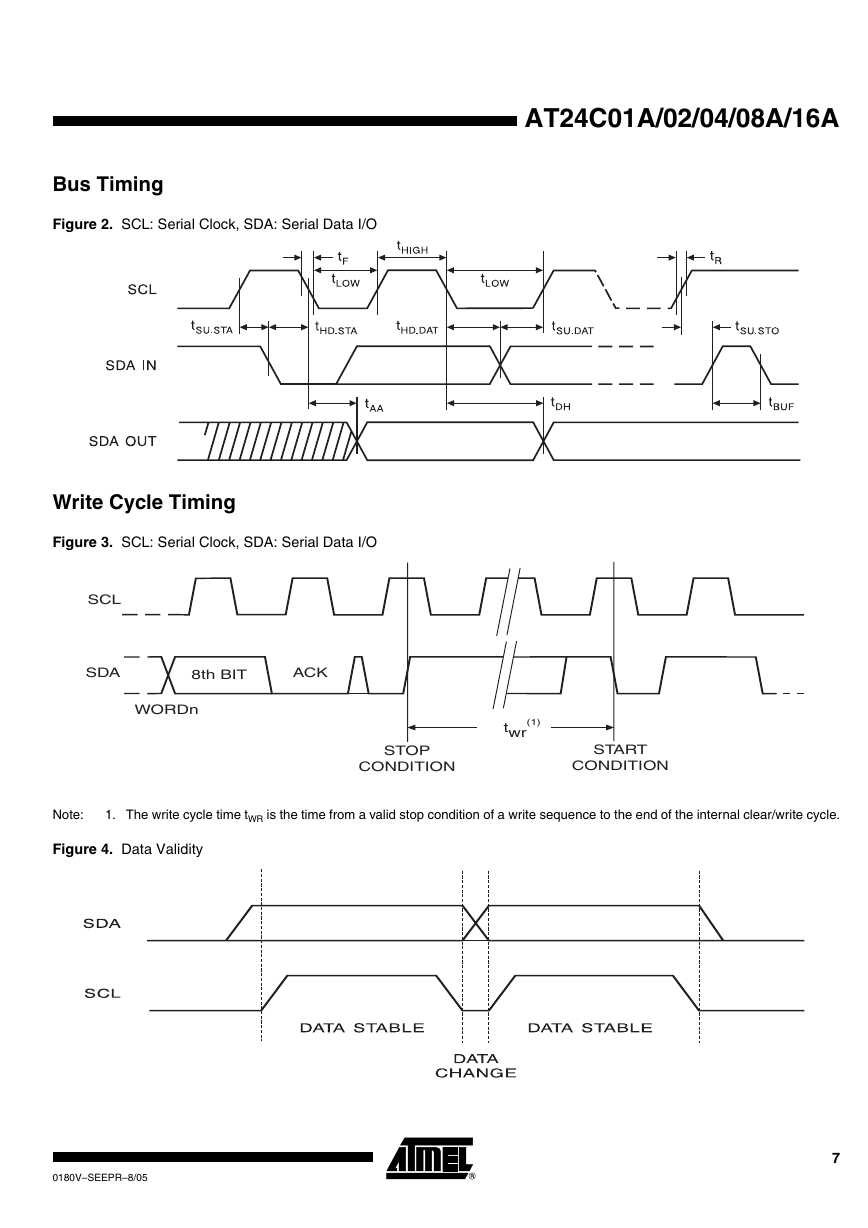

6AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Device Operation CLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-nal device. Data on the SDA pin may change only during SCL low time periods (seeFigure 4 on page 7). Data changes during SCL high periods will indicate a start or stopcondition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start conditionwhich must precede any othercommand (see Figure 5 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence, the stop command will place the EEPROM in a standby powermode (see Figure 5 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from theEEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it hasreceived each word. This happens during the ninth clock cycle.STANDBY MODE: The AT24C01A/02/04/08A/16A features a low-power standby modewhich is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and thecompletion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss or system reset, any 2-wire part can be reset by following these steps:1.Clock up to 9 cycles.2.Look for SDA high in each cycle while SCL is high.3.Create a start condition.�

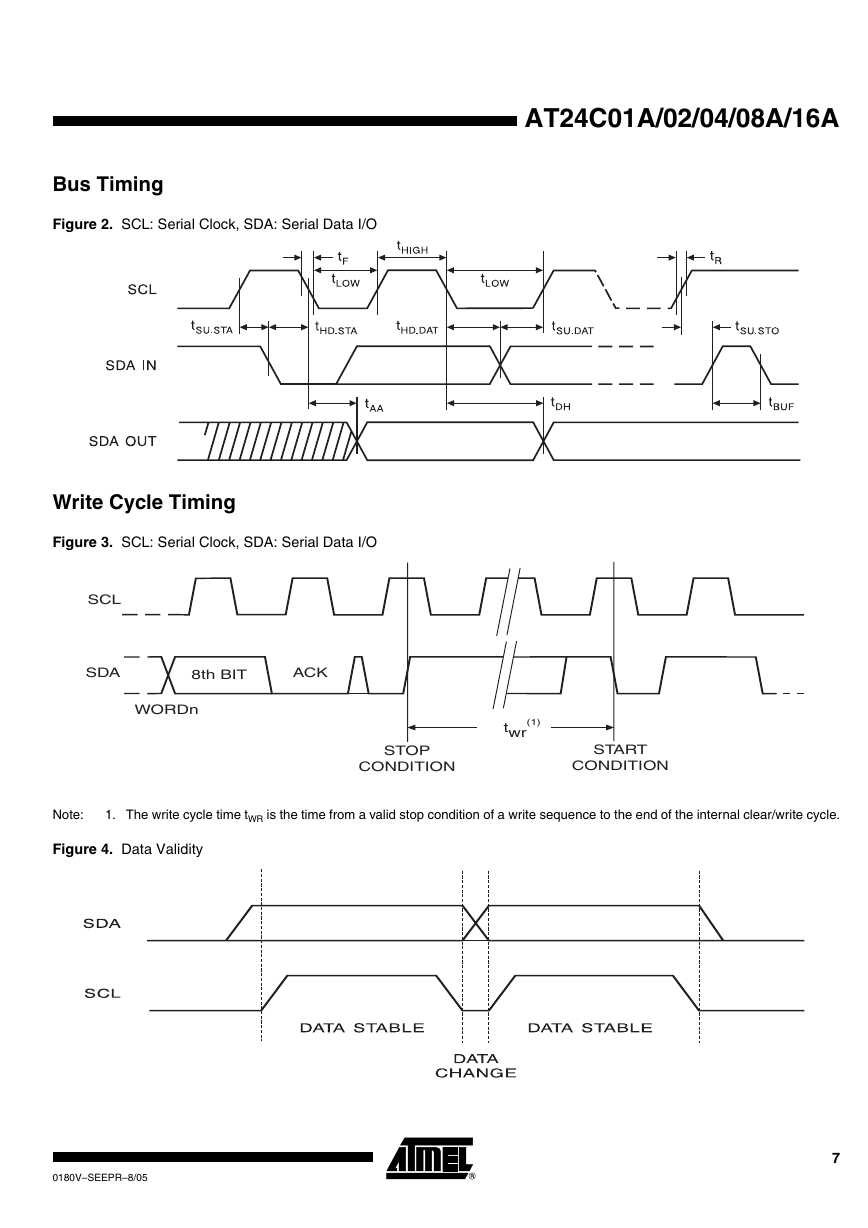

7AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Bus TimingFigure 2. SCL: Serial Clock, SDA: Serial Data I/O Write Cycle TimingFigure 3. SCL: Serial Clock, SDA: Serial Data I/O Note:1.The write cycle time tWR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4. Data Validity twr(1)STOPCONDITIONSTARTCONDITIONWORDnACK8th BITSCLSDA�

8AT24C01A/02/04/08A/16A0180V–SEEPR–8/05Figure 5. Start and Stop Definition Figure 6. Output Acknowledge �

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc