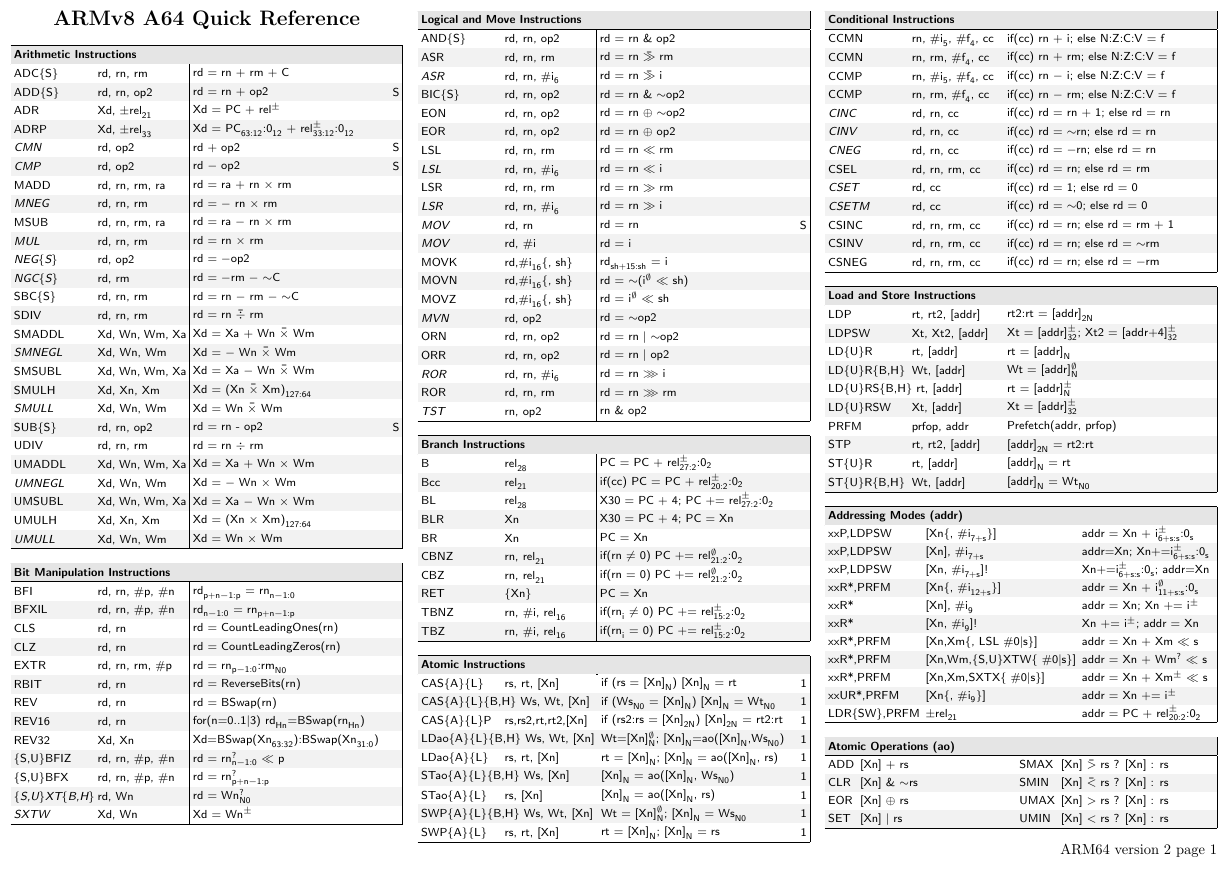

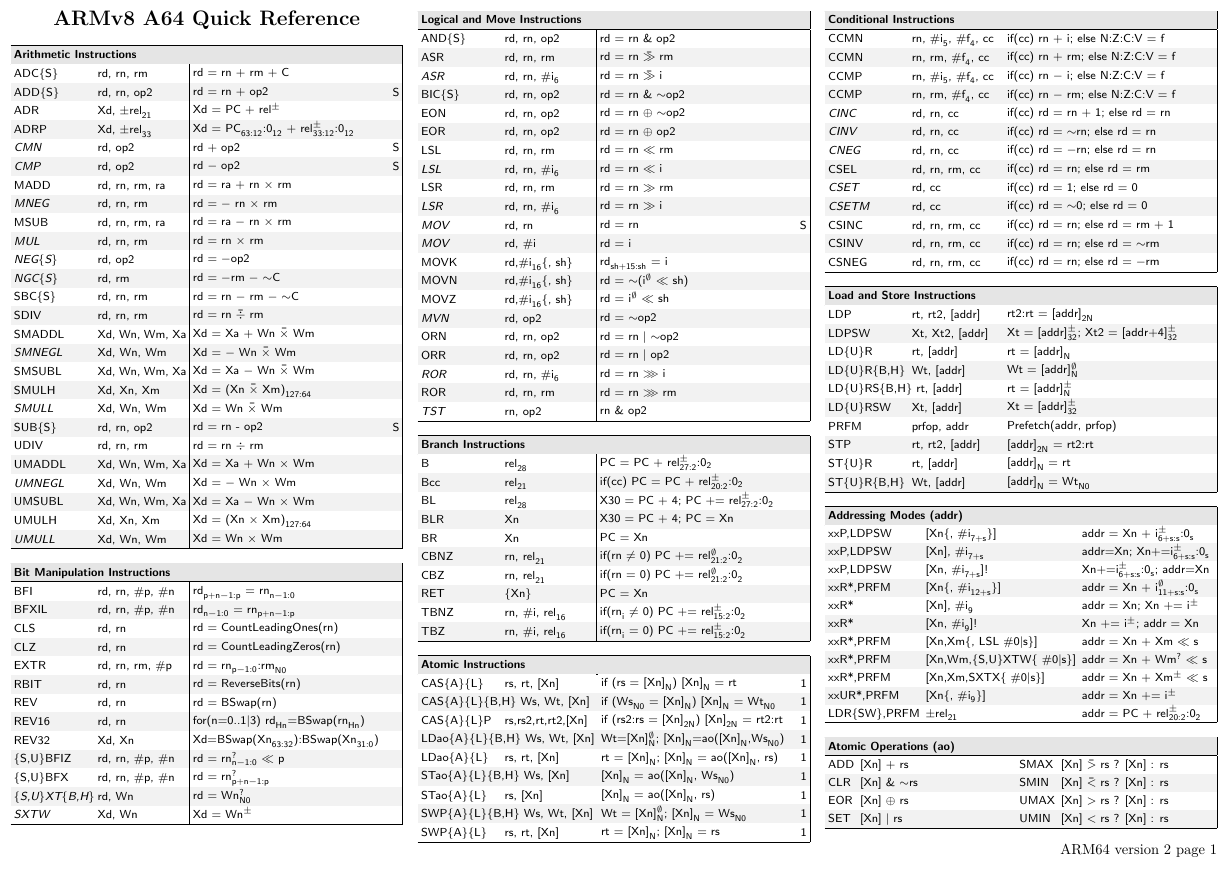

ARMv8 A64 Quick Reference

Arithmetic Instructions

ADC{S}

ADD{S}

ADR

rd, rn, rm

rd = rn + rm + C

rd = rn + op2

Xd = PC + rel±

Xd = PC63:12:012 + rel±

33:12:012

ADRP

CMN

CMP

MADD

MNEG

MSUB

MUL

NEG{S}

NGC{S}

SBC{S}

SDIV

SMADDL

SMNEGL

SMSUBL

SMULH

SMULL

SUB{S}

UDIV

UMADDL

UMNEGL

UMSUBL

UMULH

UMULL

rd, rn, op2

Xd, ±rel21

Xd, ±rel33

rd, op2

rd, op2

rd, rn, rm, ra

rd, rn, rm

rd, rn, rm, ra

rd, rn, rm

rd, op2

rd, rm

rd, rn, rm

rd + op2

rd − op2

rd = ra + rn × rm

rd = − rn × rm

rd = ra − rn × rm

rd = rn × rm

rd = −op2

rd = −rm − ∼C

rd = rn − rm − ∼C

rd = rn ¯÷ rm

Xd, Wn, Wm

Xd = − Wn ¯× Wm

rd, rn, rm

Xd, Wn, Wm, Xa Xd = Xa + Wn ¯× Wm

Xd, Wn, Wm

Xd, Wn, Wm, Xa Xd = Xa − Wn ¯× Wm

Xd = (Xn ¯× Xm)127:64

Xd, Xn, Xm

Xd = Wn ¯× Wm

rd = rn - op2

rd = rn ÷ rm

rd, rn, rm

Xd, Wn, Wm, Xa Xd = Xa + Wn × Wm

Xd, Wn, Wm

Xd, Wn, Wm, Xa Xd = Xa − Wn × Wm

Xd = (Xn × Xm)127:64

Xd, Xn, Xm

Xd = Wn × Wm

Xd = − Wn × Wm

Xd, Wn, Wm

rd, rn, op2

Bit Manipulation Instructions

BFI

BFXIL

CLS

CLZ

EXTR

RBIT

REV

REV16

rd, rn, #p, #n

rd, rn, #p, #n

rd, rn

rd, rn

rd, rn, rm, #p

rd, rn

rd, rn

rd, rn

Xd, Xn

REV32

{S,U}BFIZ

{S,U}BFX

{S,U}XT{B,H} rd, Wn

Xd, Wn

SXTW

rd, rn, #p, #n

rd, rn, #p, #n

rdp+n−1:p = rnn−1:0

rdn−1:0 = rnp+n−1:p

rd = CountLeadingOnes(rn)

rd = CountLeadingZeros(rn)

rd = rnp−1:0:rmN0

rd = ReverseBits(rn)

rd = BSwap(rn)

for(n=0..1|3) rdHn=BSwap(rnHn)

Xd=BSwap(Xn63:32):BSwap(Xn31:0)

rd = rn?

rd = rn?

rd = Wn?

Xd = Wn±

n−1:0 p

p+n−1:p

N0

Logical and Move Instructions

AND{S}

ASR

rd, rn, op2

ASR

BIC{S}

EON

EOR

LSL

LSL

LSR

LSR

MOV

MOV

MOVK

MOVN

MOVZ

MVN

ORN

ORR

ROR

ROR

TST

S

S

S

S

rd, rn, rm

rd, rn, #i6

rd, rn, op2

rd, rn, op2

rd, rn, op2

rd, rn, rm

rd, rn, #i6

rd, rn, rm

rd, rn, #i6

rd, rn

rd, #i

rd,#i16{, sh}

rd,#i16{, sh}

rd,#i16{, sh}

rd, op2

rd, rn, op2

rd, rn, op2

rd, rn, #i6

rd, rn, rm

rn, op2

Branch Instructions

B

Bcc

BL

BLR

BR

CBNZ

CBZ

RET

TBNZ

TBZ

rel28

rel21

rel28

Xn

Xn

rn, rel21

rn, rel21

{Xn}

rn, #i, rel16

rn, #i, rel16

rd = rn & op2

rd = rn ¯ rm

rd = rn ¯ i

rd = rn & ∼op2

rd = rn ⊕ ∼op2

rd = rn ⊕ op2

rd = rn rm

rd = rn i

rd = rn rm

rd = rn i

rd = rn

rd = i

rdsh+15:sh = i

rd = ∼(i∅ sh)

rd = i∅ sh

rd = ∼op2

rd = rn | ∼op2

rd = rn | op2

rd = rn ≫ i

rd = rn ≫ rm

rn & op2

PC = PC + rel±

27:2:02

if(cc) PC = PC + rel±

20:2:02

X30 = PC + 4; PC += rel±

X30 = PC + 4; PC = Xn

27:2:02

PC = Xn

if(rn = 0) PC += rel∅

if(rn = 0) PC += rel∅

PC = Xn

= 0) PC += rel±

if(rni

if(rni = 0) PC += rel±

21:2:02

21:2:02

15:2:02

15:2:02

rs, rt, [Xn]

Atomic Instructions

CAS{A}{L}

CAS{A}{L}{B,H} Ws, Wt, [Xn]

CAS{A}{L}P rs,rs2,rt,rt2,[Xn]

LDao{A}{L}{B,H} Ws, Wt, [Xn] Wt=[Xn]∅

LDao{A}{L}

STao{A}{L}{B,H} Ws, [Xn]

STao{A}{L}

SWP{A}{L}{B,H} Ws, Wt, [Xn] Wt = [Xn]∅

SWP{A}{L}

if (rs = [Xn]N) [Xn]N = rt

if (WsN0 = [Xn]N) [Xn]N = WtN0

if (rs2:rs = [Xn]2N) [Xn]2N = rt2:rt

N; [Xn]N=ao([Xn]N,WsN0)

rt = [Xn]N; [Xn]N = ao([Xn]N, rs)

[Xn]N = ao([Xn]N, WsN0)

[Xn]N = ao([Xn]N, rs)

N; [Xn]N = WsN0

rt = [Xn]N; [Xn]N = rs

rs, rt, [Xn]

rs, rt, [Xn]

rs, [Xn]

Conditional Instructions

CCMN

CCMN

CCMP

CCMP

CINC

CINV

CNEG

CSEL

CSET

CSETM

CSINC

CSINV

CSNEG

rn, #i5, #f4, cc

rn, rm, #f4, cc

rn, #i5, #f4, cc

rn, rm, #f4, cc

rd, rn, cc

rd, rn, cc

rd, rn, cc

rd, rn, rm, cc

rd, cc

rd, cc

rd, rn, rm, cc

rd, rn, rm, cc

rd, rn, rm, cc

if(cc) rn + i; else N:Z:C:V = f

if(cc) rn + rm; else N:Z:C:V = f

if(cc) rn − i; else N:Z:C:V = f

if(cc) rn − rm; else N:Z:C:V = f

if(cc) rd = rn + 1; else rd = rn

if(cc) rd = ∼rn; else rd = rn

if(cc) rd = −rn; else rd = rn

if(cc) rd = rn; else rd = rm

if(cc) rd = 1; else rd = 0

if(cc) rd = ∼0; else rd = 0

if(cc) rd = rn; else rd = rm + 1

if(cc) rd = rn; else rd = ∼rm

if(cc) rd = rn; else rd = −rm

Load and Store Instructions

LDP

rt, rt2, [addr]

Xt, Xt2, [addr]

LDPSW

LD{U}R

rt, [addr]

LD{U}R{B,H} Wt, [addr]

LD{U}RS{B,H} rt, [addr]

LD{U}RSW Xt, [addr]

prfop, addr

PRFM

rt, rt2, [addr]

STP

ST{U}R

rt, [addr]

ST{U}R{B,H} Wt, [addr]

32; Xt2 = [addr+4]±

32

N

rt2:rt = [addr]2N

Xt = [addr]±

rt = [addr]N

Wt = [addr]∅

rt = [addr]±

Xt = [addr]±

Prefetch(addr, prfop)

[addr]2N = rt2:rt

[addr]N = rt

[addr]N = WtN0

32

N

Addressing Modes (addr)

xxP,LDPSW

xxP,LDPSW

xxP,LDPSW

xxR*,PRFM

xxR*

xxR*

xxR*,PRFM

xxR*,PRFM

xxR*,PRFM

6+s:s:0s

6+s:s:0s

6+s:s:0s; addr=Xn

addr = Xn + i±

[Xn{, #i7+s}]

addr=Xn; Xn+=i±

[Xn], #i7+s

Xn+=i±

[Xn, #i7+s]!

addr = Xn + i∅

[Xn{, #i12+s}]

11+s:s:0s

addr = Xn; Xn += i±

[Xn], #i9

Xn += i±; addr = Xn

[Xn, #i9]!

[Xn,Xm{, LSL #0|s}]

addr = Xn + Xm s

[Xn,Wm,{S,U}XTW{ #0|s}] addr = Xn + Wm? s

addr = Xn + Xm± s

[Xn,Xm,SXTX{ #0|s}]

[Xn{, #i9}]

addr = Xn += i±

addr = PC + rel±

20:2:02

xxUR*,PRFM

LDR{SW},PRFM ±rel21

Atomic Operations (ao)

ADD [Xn] + rs

CLR [Xn] & ∼rs

EOR [Xn] ⊕ rs

SET [Xn] | rs

SMAX [Xn] ¯> rs ? [Xn] : rs

SMIN [Xn] ¯< rs ? [Xn] : rs

UMAX [Xn] > rs ? [Xn] : rs

UMIN [Xn] < rs ? [Xn] : rs

ARM64 version 2 page 1

S

1

1

1

1

1

1

1

1

1

�

Operand 2 (op2)

all

all

all

all

logical

arithmetic

arithmetic

arithmetic

arithmetic

arithmetic

arithmetic

rm

rm i

rm i

rm ¯ i

rm ≫ i

rm

rm, LSL #i6

rm, LSR #i6

rm, ASR #i6

rm, ROR #i6

B0 i

Wm, {S,U}XTB{ #i3} Wm?

H0 i

Wm, {S,U}XTH{ #i3} Wm?

Wm, {S,U}XTW{ #i3} Wm? i

Xm, {S,U}XTX{ #i3} Xm? i

#i12

#i24

i∅

i∅

23:12:012

mask

AND,EOR,ORR,TST #mask

Registers

X0-X7

Arguments and return values

X8

Indirect result

X9-X15 Temporary

X16-X17 Intra-procedure-call temporary

X18

Platform defined use

X19-X28 Temporary (must be preserved)

X29

X30

SP

XZR

PC

Frame pointer (must be preserved)

Return address

Stack pointer

Zero

Program counter

Special Purpose Registers

SPSR EL{1..3} Process state on exception entry to EL{1..3}

ELR EL{1..3} Exception return address from EL{1..3}

SP EL{0..2}

SPSel

Stack pointer for EL{0..2}

SP selection (0: SP=SP EL0, 1: SP=SP ELn)

CurrentEL

Current Exception level (at bits 3..2)

64

64

RO

DAIF

NZCV

FPCR

FPSR

Keys

N

s

rd, rn, rm, rt

Current interrupt mask bits (at bits 9..6)

Condition flags (at bits 31..28)

Floating-point operation control

Floating-point status

Operand bit size (8, 16, 32 or 64)

Operand log byte size (0=byte,1=hword,2=word,3=dword)

General register of either size (Wn or Xn)

P{LD,LI,ST}L{1..3}{KEEP,STRM}

Optional halfword left shift (LSL #{16,32,48})

prfop

{,sh}

val±, val∅, val? Value is sign/zero extended (? depends on instruction)

¯× ¯÷ ¯ ¯> ¯< Operation is signed

Checksum Instructions

CRC32{B,H} Wd, Wn, Wm Wd=CRC32(Wn,0x04c11db7,WmN0)

Wd, Wn, Wm Wd = CRC32(Wn,0x04c11db7,Wm)

CRC32W

Wd = CRC32(Wn,0x04c11db7,Xm)

CRC32X

CRC32C{B,H} Wd, Wn, Wm Wd=CRC32(Wn,0x1edc6f41,WmN0)

Wd, Wn, Wm Wd = CRC32(Wn,0x1edc6f41,Wm)

CRC32CW

Wd = CRC32(Wn,0x1edc6f41,Xm)

Wd, Wn, Xm

Wd, Wn, Xm

CRC32CX

rt, rt2, [Xn]

Load and Store Instructions with Attribute

LD{A}XP

LD{A}{X}R

LD{A}{X}R{B,H} Wt, [Xn]

LDNP

rt, [Xn]

rt:rt2 = [Xn, ]2N

rt = [Xn, ]N

Wt = [Xn, ]∅

N

LDTR

rt,rt2,[Xn{,#i7+s}]rt2:rt = [Xn + i±

rt, [Xn{, #i9}]

rt = [Xn += i±, ]N

LDTR{B,H} Wt, [Xn{, #i9}] Wt = [Xn += i±, ]∅

rt = [Xn += i±, ]±

LDTRS{B,H} rt, [Xn{, #i9}]

Xt, [Xn{, #i9}] Xt = [Xn += i±, ]±

LDTRSW

N

32

N

6+s:s:0s, ]2N

STLR

rt, [Xn]

STLR{B,H} Wt, [Xn]

ST{L}XP

ST{L}XR

ST{L}XR{B,H} Wd, Wt, [Xn]

STNP

Wd, rt, [Xn]

Wd, rt, rt2, [Xn]

rt,rt2,[Xn{,#i7+s}][Xn + i±

rt, [Xn{, #i9}]

STTR

STTR{B,H} Wt, [Xn{, #i9}]

[Xn, ]N = rt

[Xn, ]N = WtN0

[Xn, ]2N=rt:rt2; Wd=fail?1:0

[Xn, ]N=rt; Wd=fail?1:0

[Xn, ]N=WtN0; Wd=fail?1:0

6+s:s:0s, ]2N = rt2:rt

[Xn += i±, ]N = rt

[Xn += i±, ]N = WtN0

Condition Codes (cc)

EQ

NE

Equal

Not equal

Z

!Z

CS/HS Carry set, Unsigned higher or same C

CC/LO Carry clear, Unsigned lower

MI

PL

VS

VC

HI

LS

GE

LT

GT

LE

AL

Minus, Negative

Plus, Positive or zero

Overflow

No overflow

Unsigned higher

Unsigned lower or same

Signed greater than or equal

Signed less than

Signed greater than

Signed less than or equal

Always (default)

!C

N

!N

V

!V

C & !Z

!C | Z

N = V

N = V

!Z & N = V

Z | N = V

1

Notes for Instruction Set

S SP/WSP may be used as operand(s) instead of XZR/WZR

1 Introduced in ARMv8.1

S1{2}E{0..3}{R,W}, Xn PAR EL1 = AddrTrans(Xn)

System Instructions

AT

BRK #i16

CLREX {#i4}

DMB barrierop

DSB

barrierop

ERET

HVC #16

{SY}

ISB

Xd, sysreg

MRS

MSR

sysreg, Xn

SPSel, #i1

MSR

MSR DAIFSet, #i4

MSR DAIFClr, #i4

NOP

SEV

SEVL

SMC #i16

SVC #i16

WFE

WFI

YIELD

SoftwareBreakpoint(i)

ClearExclusiveLocal()

DataMemoryBarrier(barrierop)

DataSyncBarrier(barrierop)

PC=ELR ELn;PSTATE=SPSR ELn

CallHypervisor(i)

InstructionSyncBarrier(SY)

Xd = sysreg

sysreg = Xn

PSTATE.SP = i

PSTATE.DAIF |= i

PSTATE.DAIF &= ∼i

SendEvent()

EventRegisterSet()

CallSecureMonitor(i)

CallSupervisor(i)

WaitForEvent()

WaitForInterrupt()

Cache and TLB Maintenance Instructions

DC

DC

DC

DC

IC

{C,CI,I}SW, Xx

{C,CI,I}VAC, Xx

CVAU, Xx

ZVA, Xx

IALLU{IS}

IVAU, Xx

IC

TLBI ALLE{1..3}{IS}

TLBI ASIDE1{IS}, Xx

IPAS2{L}E1{IS}, Xx

TLBI

TLBI VAA{L}E1{IS}, Xx

TLBI VA{L}E{1..3}{IS}, Xx

TLBI VMALL{S12}E1{IS}

DC clean and/or inv by Set/Way

DC clean and/or inv by VA to PoC

DC clean by VA to PoU

DC zero by VA (len in DCZID EL0)

IC inv all to PoU

IC inv VA to PoU

TLB inv all

TLB inv by ASID

TLB inv by IPA {last level}

TLB inv by VA, all ASID {last level}

TLB inv by VA {last level}

TLB inv by VMID, all, at stage 1{&2}

DMB and DSB Options

OSH{,LD,ST} Outer shareable, {all,load,store}

NSH{,LD,ST} Non-shareable, {all,load,store}

ISH{,LD,ST} Inner shareable, {all,load,store}

LD

Full system, load

ST

SY

Full system, store

Full system, all

ARM64 version 2 page 2

�

ARMv8-A System

Control and Translation Registers

SCTLR EL{1..3}

ACTLR EL{1..3}

CPACR EL1

System Control

Auxiliary Control

Architectural Feature Access Control

HCR EL2

CPTR EL{2,3}

HSTR EL2

Hypervisor Configuration

Architectural Feature Trap

Hypervisor System Trap

HACR EL2

Hypervisor Auxiliary Control

SCR EL3

TTBR0 EL{1..3}

TTBR1 EL1

TCR EL{1..3}

VTTBR EL2

Secure Configuration

Translation Table Base 0 (4/16/64kb aligned)

Translation Table Base 1 (4/16/64kb aligned)

Translation Control

Virt Translation Table Base (4/16/64kb aligned)

Virt Translation Control

VTCR EL2

{A}MAIR EL{1..3} {Auxiliary} Memory Attribute Indirection

LOR{S,E}A EL1

LORegion {Start,End} Address

LOR{C,N,ID} EL1 LORegion {Control,Number,ID}

Exception Registers

AFSR{0,1} EL{1..3} Auxiliary Fault Status {0,1}

ESR EL{1..3}

FAR EL{1..3}

HPFAR EL2

Exception Syndrome

Hypervisor IPA Fault Address

Fault Address

PAR EL1

VBAR EL{1..3}

RVBAR EL{1..3}

RMR EL{1..3}

ISR EL1

Physical Address

Vector Base Address (2kb aligned)

Reset Vector Base Address

Reset Management

Interrupt Status

Performance Monitors Registers

PMCR EL0

PMCNTEN{SET,CLR} EL0 PM Count Enable {Set,Clear}

PM Overflow Flag Status Clear

PMOVSCLR EL0

PM Control

PMSWINC EL0

PM Software Increment

PMSELR EL0

PMCEID{0,1} EL0

PMCCNTR EL0

PM Event Counter Selection

PM Common Event ID {0,1}

PM Cycle Count Register

PMXEVTYPER EL0

PM Selected Event Type

PMXEVCNTR EL0

PM Selected Event Count

PMUSERENR EL0

PM User Enable

PM Overflow Flag Status Set

PMOVSSET EL0

PMINTEN{SET,CLR} EL1 PM Interrupt Enable {Set,Clear}

PMEVCNTR{0..30} EL0

PM Event Count {0..30}

PMEVTYPER{0..30} EL0 PM Event Type {0..30}

PM Cycle Count Filter

PMCCFILTR EL0

ID Registers

MIDR EL1

MPIDR EL1

REVIDR EL1

CCSIDR EL1

CLIDR EL1

AIDR EL1

CSSELR EL1

CTR EL0

DCZID EL0

VPIDR EL2

Main ID

Multiprocessor Affinity

Revision ID

Current Cache Size ID

Cache Level ID

Auxiliary ID

Cache Size Selection

Cache Type

Data Cache Zero ID

Virtualization Processor ID

RO

RO,64

RO

RO

RO

RO

RO

RO

64

Virtualization Multiprocessor ID

AArch64 Processor Feature {0,1}

AArch64 Debug Feature {0,1}

AArch64 Auxiliary Feature {0,1}

VMPIDR EL2

ID AA64PFR{0,1} EL1

ID AA64DFR{0,1} EL1

ID AA64AFR{0,1} EL1

RO,64

ID AA64ISAR{0,1} EL1 AArch64 Instruction Set Attribute {0,1} RO,64

ID AA64MMFR{0,1} EL1 AArch64 Memory Model Feature {0,1} RO,64

CONTEXTIDR EL1

TPIDR EL{0..3}

TPIDRRO EL0

EL0 Read-only Software Thread ID

Software Thread ID

Context ID

RO,64

RO,64

64

64

Exception Vectors

0x000,0x080,0x100,0x180 {Sync,IRQ,FIQ,SError} from cur lvl with SP EL0

0x200,0x280,0x300,0x380 {Sync,IRQ,FIQ,SError} from cur lvl with SP ELn

0x400,0x480,0x500,0x580 {Sync,IRQ,FIQ,SError} from lower lvl using A64

0x600,0x680,0x700,0x780 {Sync,IRQ,FIQ,SError} from lower lvl using A32

64

64

64

64

64

64

64

64,1

64,1

64

64

64

64

RO,64

System Control Register (SCTLR)

RO

WO

RO

64

M

A

C

SA

SA0

0x00000001 MMU enabled

0x00000002 Alignment check enabled

0x00000004 Data and unified caches enabled

0x00000008 Enable SP alignment check

0x00000010 Enable SP alignment check for EL0

UMA 0x00000200 Trap EL0 access of DAIF to EL1

I

0x00001000 Instruction cache enabled

DZE

0x00004000 Trap EL0 DC instruction to EL1

UCT 0x00008000 Trap EL0 access of CTR EL0 to EL1

nTWI 0x00010000 Trap EL0 WFI instruction to EL1

nTWE 0x00040000 Trap EL0 WFE instruction to EL1

WXN 0x00080000 Write permission implies XN

Generic Timer Registers

CNTFRQ EL0

CNT{P,V}CT EL0

CNTVOFF EL2

CNTHCTL EL2

Ct Frequency (in Hz)

Ct {Physical,Virtual} Count RO,64

64

Ct Virtual Offset

Ct Hypervisor Control

Ct Kernel Control

CNTKCTL EL1

CNT{P,V} {TVAL,CTL,CVAL} EL0 Ct {Physical,Virtual} Timer

CNTHP {TVAL,CTL,CVAL} EL2

Ct Hypervisor Physical Timer

CNTPS {TVAL,CTL,CVAL} EL1

CNTHV {TVAL,CTL,CVAL} EL2

Ct Physical Secure Timer

Ct Virtual Timer

1

Exception Classes

0x00

0x01

0x07

0x08

Unknown reason

Trapped WFI or WFE instruction execution

Trapped access to SIMD/FP

Trapped VMRS access

Illegal Execution state

0x0e

0x11,0x15 SVC instruction execution in AArch{32,64} state

0x12,0x16 HVC instruction execution in AArch{32,64} state

0x13,0x17 SMC instruction execution in AArch{32,64} state

0x18

Trapped MSR, MRS, or System instruction execution

Implementation defined exception to EL3

0x1f

0x20,0x21 Instruction Abort from {lower,current} level

0x22,0x26 {PC,SP} alignment fault

0x24,0x25 Data Abort from {lower,current} level

0x28,0x2c Trapped float-point exception from AArch{32,64} state

0x2f

0x30,0x31 Breakpoint exception from {lower,current} level

0x32,0x33 Software Step exception from {lower,current} level

0x34,0x35 Watchpoint exception from {lower,current} level

0x38,0x3c {BKPT,BRK} instruction excecution from AArch{32,64} state

SError interrupt

E1

E1

E1

E1

E1

E1

Secure Configuration Register (SCR)

NS

0x0001 System state is non-secure unless in EL3

IRQ 0x0002 IRQs taken to EL3

FIQ

EA

0x0004 FIQs taken to EL3

0x0008 External aborts and SError taken to EL3

SMD 0x0080 Secure monitor call disable

HCE 0x0100 Hyp Call enable

SIF

0x0200 Secure instruction fetch

SPAN 0x00800000 Set privileged access never

E1,1

RW 0x0400 Lower level is AArch64

E0E

EE

UCI

0x01000000 Data at EL0 is big-endian

0x02000000 Data at EL1 is big-endian

0x04000000 Trap EL0 cache instructions to EL1

E1

E1

ST

0x0800 Trap secure EL1 to CNTPS registers to EL3

0x1000 Trap EL{0..2} WFI instruction to EL3

TWI

TWE 0x2000 Trap EL{0..2} WFE instruction to EL3

TLOR 0x4000 Trap LOR registers

1

ARM64 version 2 page 3

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc