CPU 片上 cache 的设计

陈夏文 , 蔡敏

(广州华南理工大学应用物理系研究生 2001 信箱 510641)

摘 要 :本文主要介绍了一款 RISC 结构 CPU 的片上 Cache(高速缓冲存储器)的设计,从

系统级、电路级到版图级详细地介绍了主要的设计方法、cache 的结构、内存映射

技术及读写控制电路的设计。

关键词:高速缓冲存储器,全相联,直接映射,组相联,写透,回写

中图分类号:TN47;TP302 文献标识码:A

Design of on-chip Cache for CPU

Chen Xiawen , Cai Min

(Department of Applied Physics, South China University of Technology, Guangzhou,510641)

Abstract:In this paper, a design of an on-chip cache memory for a RISC architecture

microprocessor was discussed. The method of the design was introduced from system

to schematic, to layout. The architecture of the cache and the design of the read/write

controller were introduced, too.

Keywords: cache, fully associative, direct mapped, set associative, write through, and write back

EEACC:1265F

1 设计方法

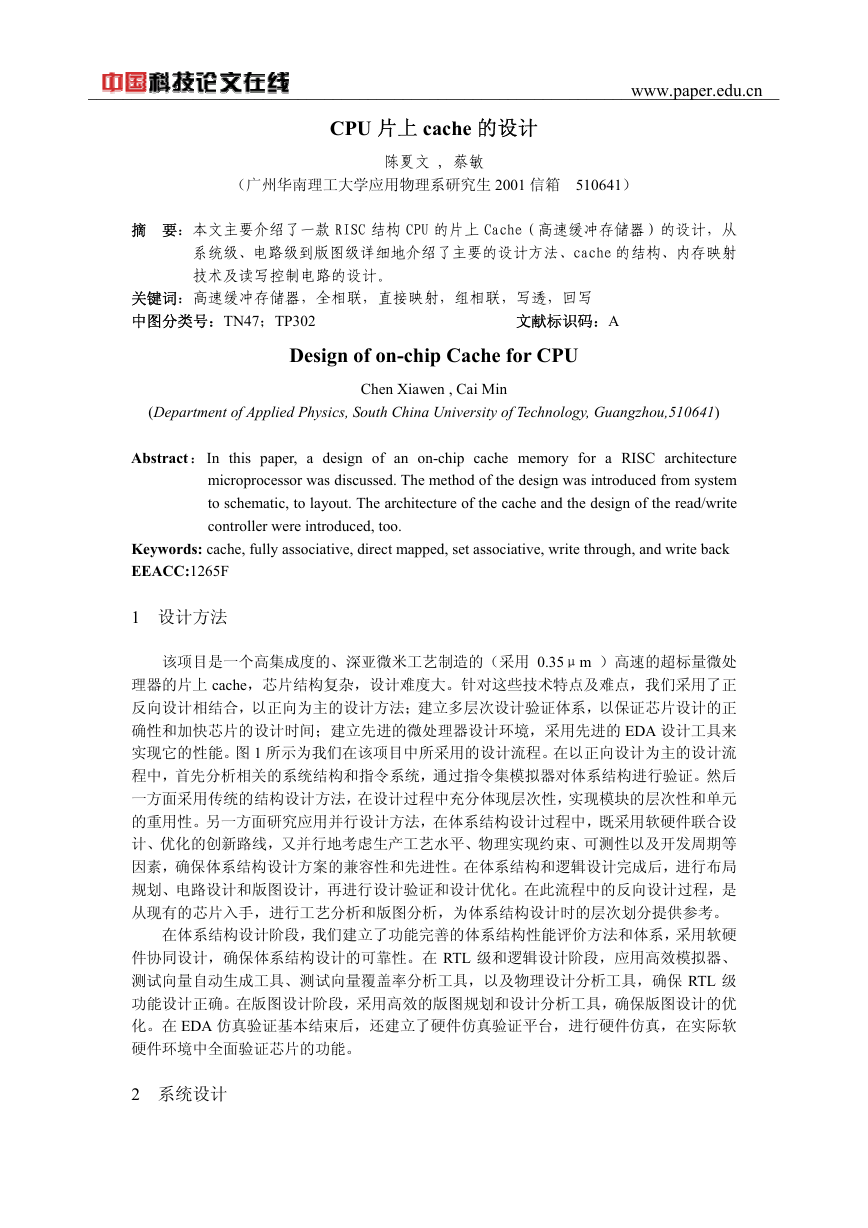

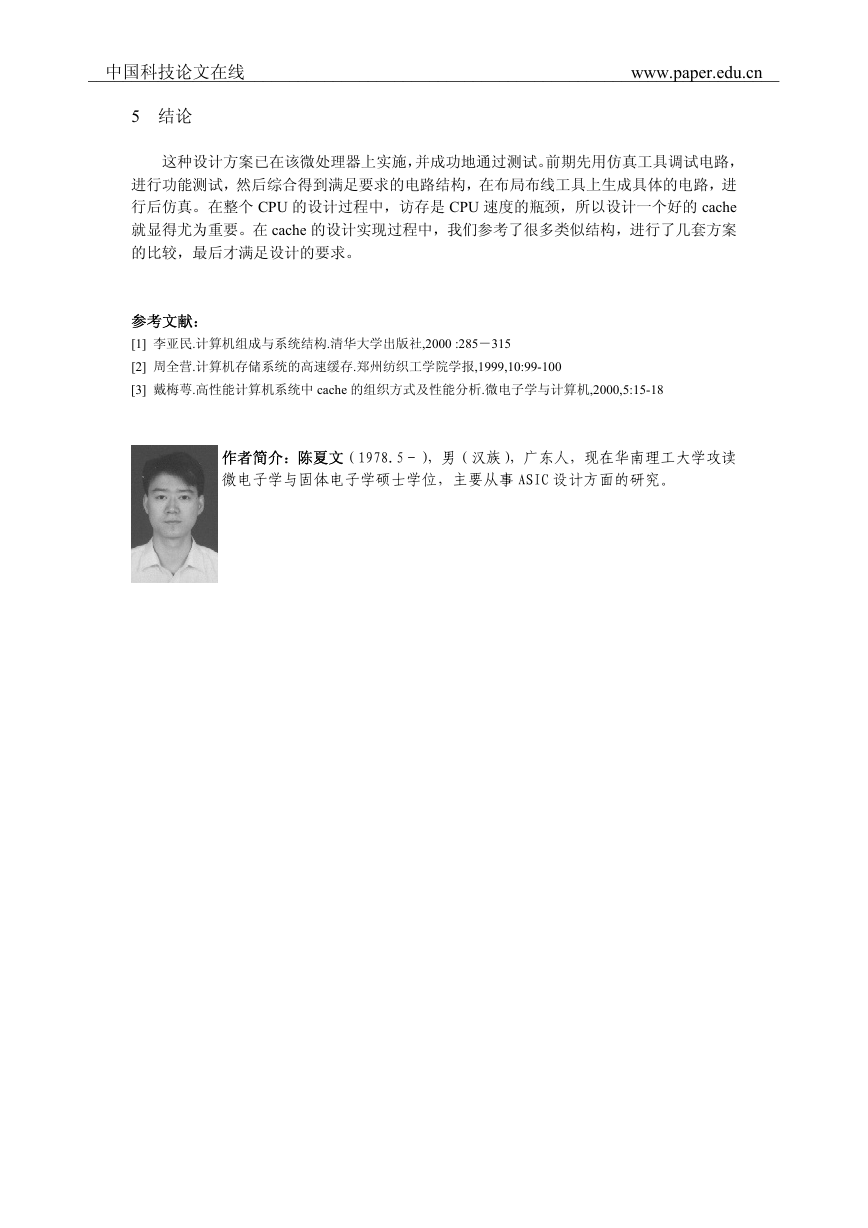

该项目是一个高集成度的、深亚微米工艺制造的(采用 0.35μm )高速的超标量微处

理器的片上 cache,芯片结构复杂,设计难度大。针对这些技术特点及难点,我们采用了正

反向设计相结合,以正向为主的设计方法;建立多层次设计验证体系,以保证芯片设计的正

确性和加快芯片的设计时间;建立先进的微处理器设计环境,采用先进的 EDA 设计工具来

实现它的性能。图 1 所示为我们在该项目中所采用的设计流程。在以正向设计为主的设计流

程中,首先分析相关的系统结构和指令系统,通过指令集模拟器对体系结构进行验证。然后

一方面采用传统的结构设计方法,在设计过程中充分体现层次性,实现模块的层次性和单元

的重用性。另一方面研究应用并行设计方法,在体系结构设计过程中,既采用软硬件联合设

计、优化的创新路线,又并行地考虑生产工艺水平、物理实现约束、可测性以及开发周期等

因素,确保体系结构设计方案的兼容性和先进性。在体系结构和逻辑设计完成后,进行布局

规划、电路设计和版图设计,再进行设计验证和设计优化。在此流程中的反向设计过程,是

从现有的芯片入手,进行工艺分析和版图分析,为体系结构设计时的层次划分提供参考。

在体系结构设计阶段,我们建立了功能完善的体系结构性能评价方法和体系,采用软硬

件协同设计,确保体系结构设计的可靠性。在 RTL 级和逻辑设计阶段,应用高效模拟器、

测试向量自动生成工具、测试向量覆盖率分析工具,以及物理设计分析工具,确保 RTL 级

功能设计正确。在版图设计阶段,采用高效的版图规划和设计分析工具,确保版图设计的优

化。在 EDA 仿真验证基本结束后,还建立了硬件仿真验证平台,进行硬件仿真,在实际软

硬件环境中全面验证芯片的功能。

2 系统设计

_______________________________________________________________________________www.paper.edu.cn�

我们所设计的cache采用了哈佛结构[1],即分立的数据cache及指令cache,各 16KB;采

用 4 路组相连的映射方式;可编程选择写透+写不装入 、写回+写装入的写策略;LRU替

换策略。

正向设计

逆向设计

系统设计

芯片解剖、照片

HDL编程

电路提取、整理

功能仿真

模块划分

逻辑、电路综合

仿真、验证

正反向设计模块相互验

证,设计确定

整体电路仿真验证

测试设计、测试码生成

硬件软件协同验证

控制部分

布局规划

I/O、特殊电路

存储器,规则单元

自动布局布线

全定制版图设计

总体版图整合

版图寄生参数提取

电路后仿真

版图验证

掩膜数据处理

图 1 设计流程

从物理结构上来说,cache 的结构有两种,统一的 cache 结构和分立的 cache 结构(哈

佛结构)。统一的 Cache 结构指的是指令和数据有同一个 Cache,哈佛结构指的是指令 cache

和数据 Cache 分开,这两种组织方式各有优点。统一 Cache 能够根据当前程序的需要自动调

整指令在 Cache 存储器中的比例,比固定划分有更好的性能。另一方面,分开的 Cache 使

Load /Store 指令能够单周期执行,使对数据和指令的访问能同时进行而互不干扰。为了达到

每周期发射 3 条指令,执行 5 条指令的设计指标,我们采用了哈佛结构,即把 32KB 的空间

划分为 16KB 指令 cache 和 16KB 数据 cache。以争取在较少的时钟周期内完成指令的执行,

让取指与取数同时进行,以提高 CPU 的效率。

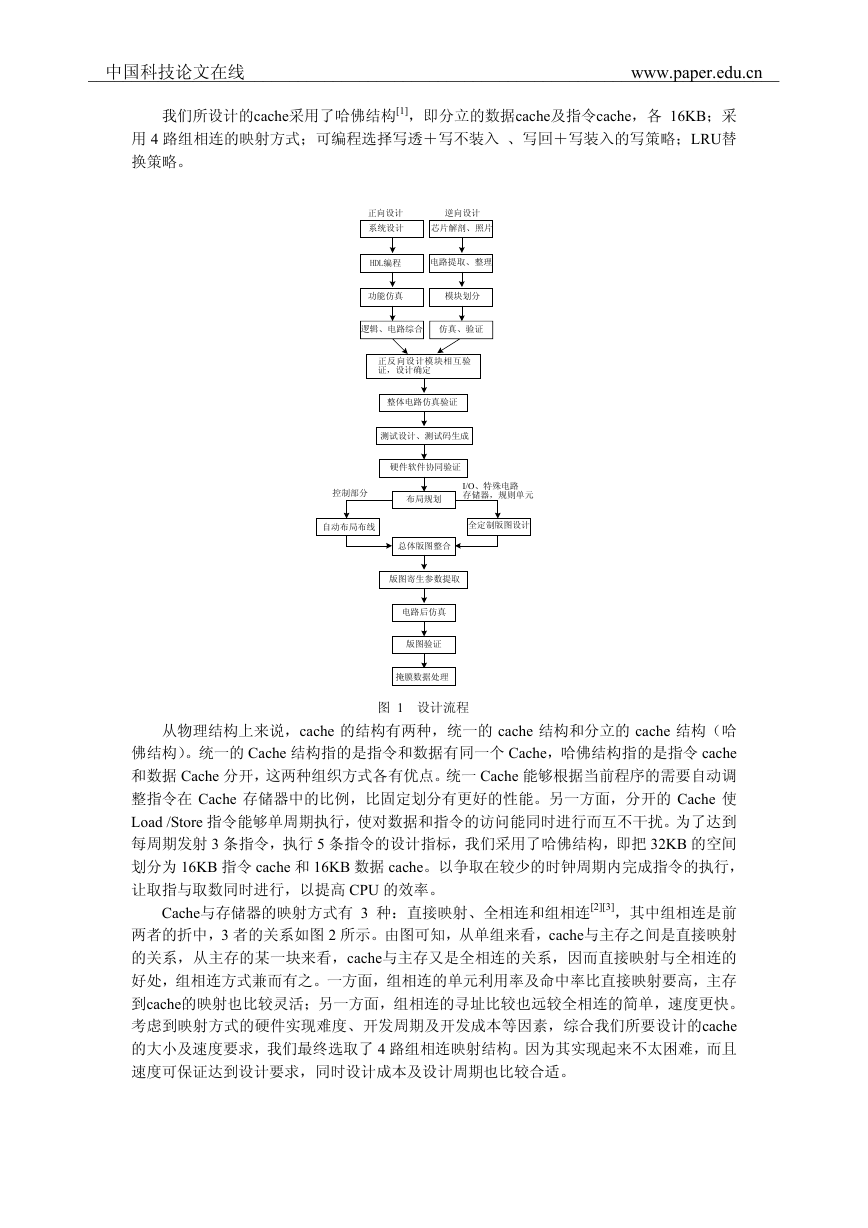

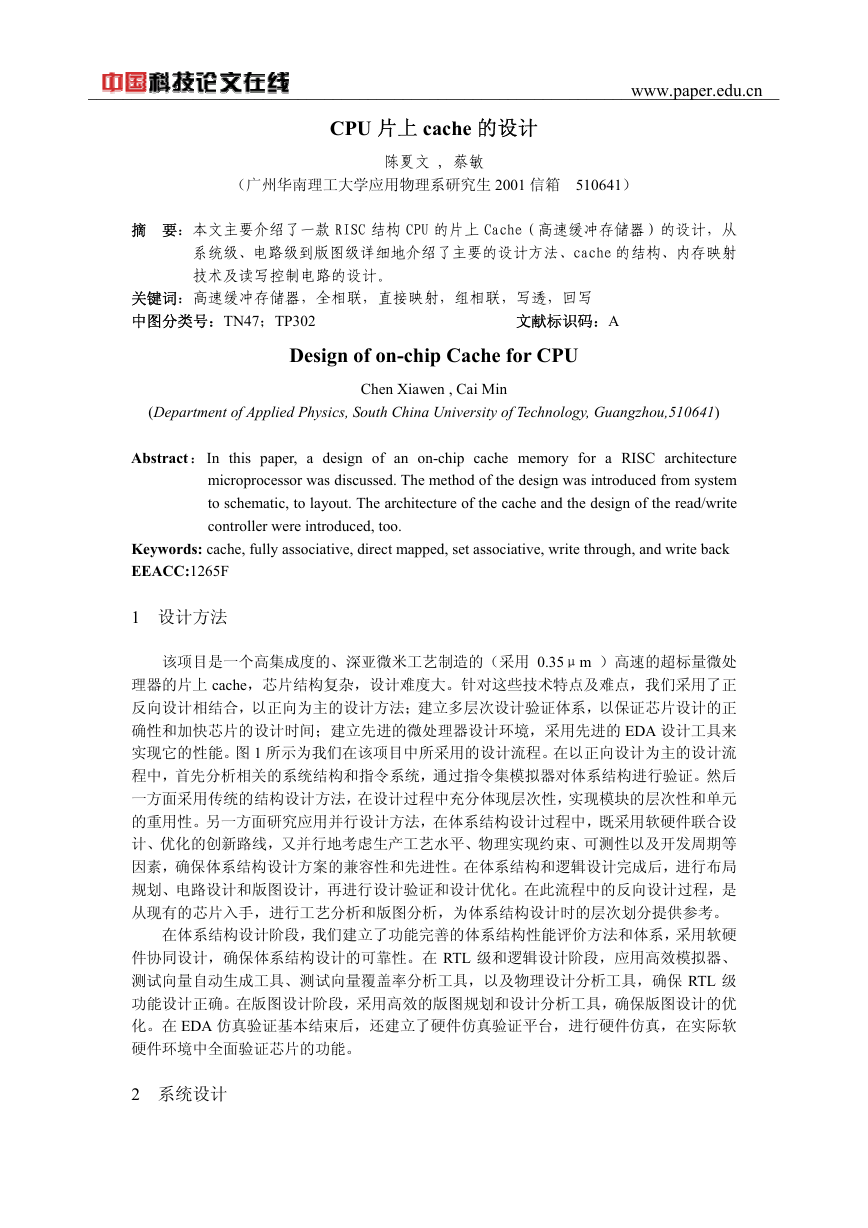

Cache与存储器的映射方式有 3 种:直接映射、全相连和组相连[2][3],其中组相连是前

两者的折中,3 者的关系如图 2 所示。由图可知,从单组来看,cache与主存之间是直接映射

的关系,从主存的某一块来看,cache与主存又是全相连的关系,因而直接映射与全相连的

好处,组相连方式兼而有之。一方面,组相连的单元利用率及命中率比直接映射要高,主存

到cache的映射也比较灵活;另一方面,组相连的寻址比较也远较全相连的简单,速度更快。

考虑到映射方式的硬件实现难度、开发周期及开发成本等因素,综合我们所要设计的cache

的大小及速度要求,我们最终选取了 4 路组相连映射结构。因为其实现起来不太困难,而且

速度可保证达到设计要求,同时设计成本及设计周期也比较合适。

中国科技论文在线_______________________________________________________________________________www.paper.edu.cn�

3 电路设计

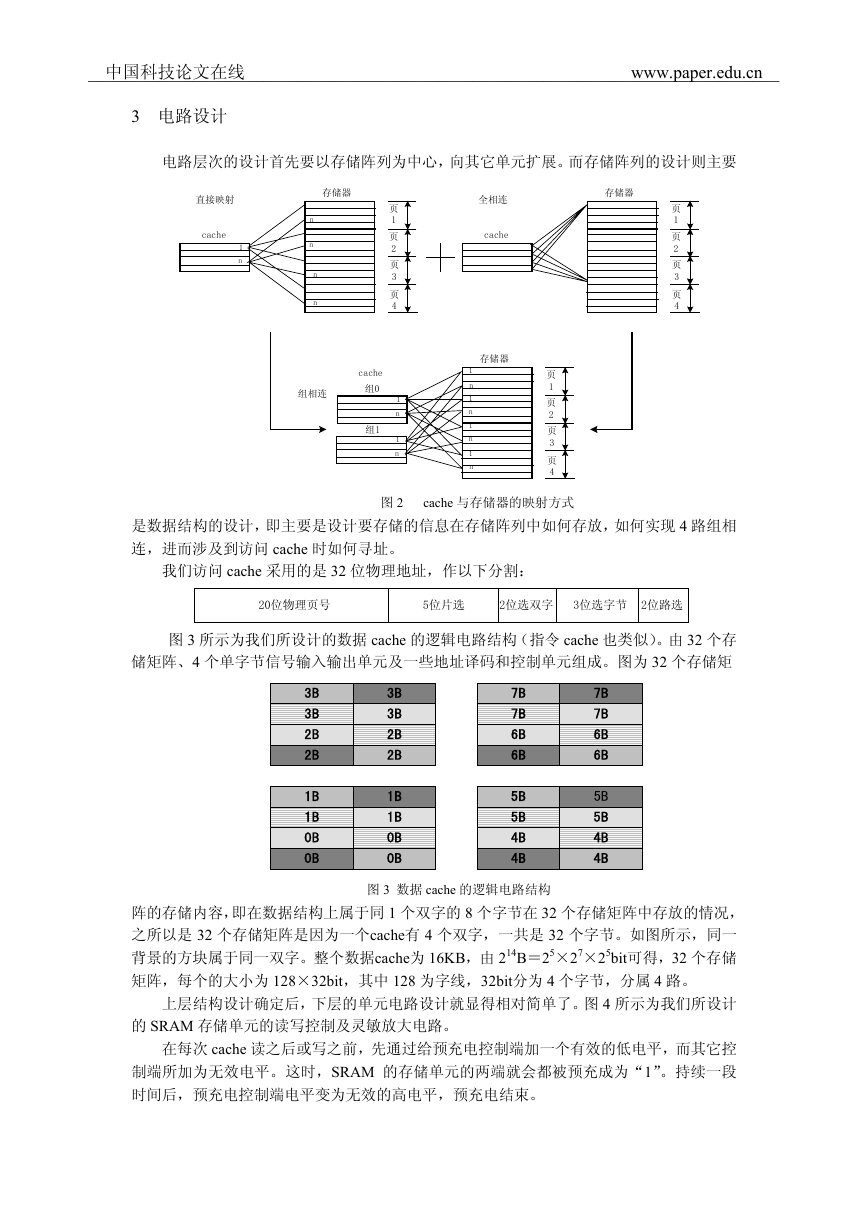

电路层次的设计首先要以存储阵列为中心,向其它单元扩展。而存储阵列的设计则主要

直接映射

cache

1

n

存储器

n

n

n

n

组相连

cache

组0

组1

页

1

页

2

页

3

页

4

1

n

1

n

全相连

cache

存储器

1

n

1

n

1

n

1

n

页

1

页

2

页

3

页

4

存储器

页

1

页

2

页

3

页

4

图 2 cache 与存储器的映射方式

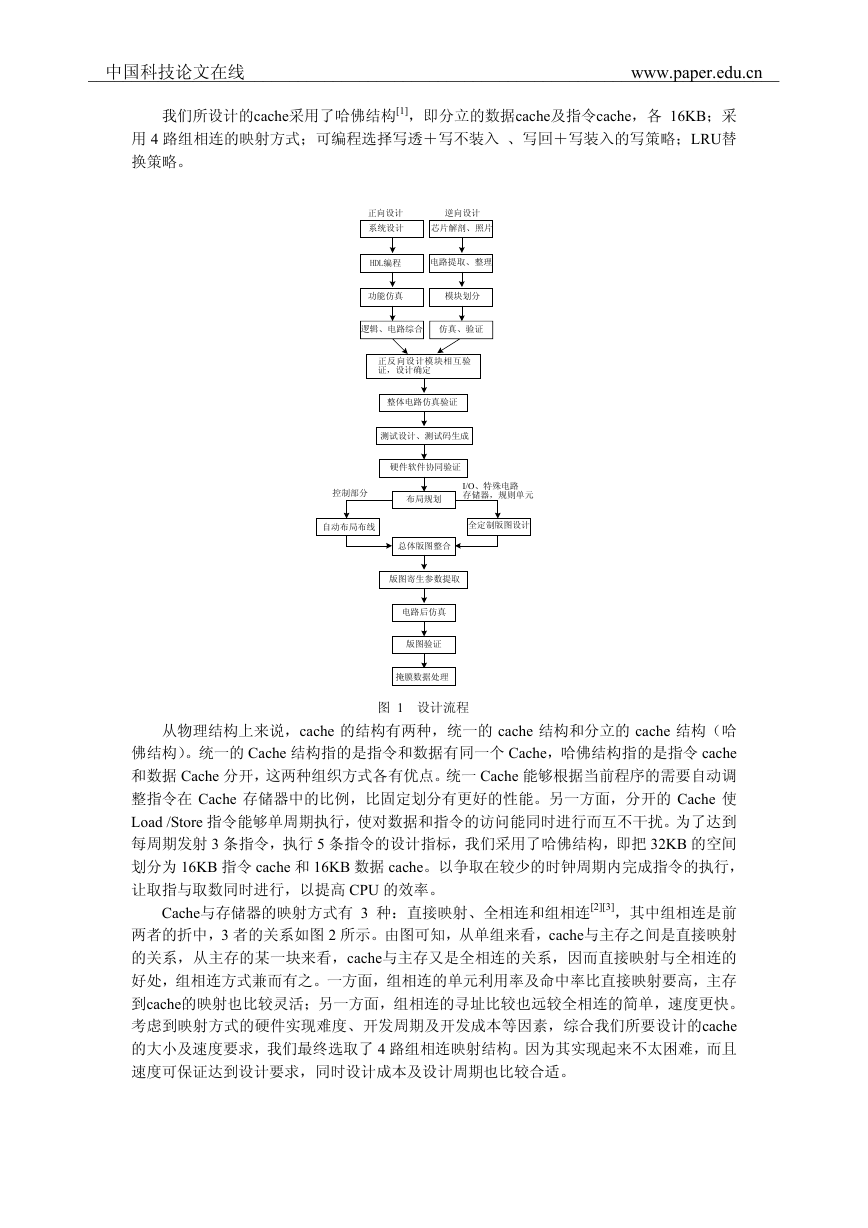

是数据结构的设计,即主要是设计要存储的信息在存储阵列中如何存放,如何实现 4 路组相

连,进而涉及到访问 cache 时如何寻址。

我们访问 cache 采用的是 32 位物理地址,作以下分割:

20位物理页号

5位片选

2位选双字 3位选字节 2位路选

图 3 所示为我们所设计的数据 cache 的逻辑电路结构(指令 cache 也类似)。由 32 个存

储矩阵、4 个单字节信号输入输出单元及一些地址译码和控制单元组成。图为 32 个存储矩

3B

3B

2B

2B

1B

1B

0B

0B

3B

3B

2B

2B

1B

1B

0B

0B

7B

7B

6B

6B

5B

5B

4B

4B

7B

7B

6B

6B

5B

5B

4B

4B

图 3 数据 cache 的逻辑电路结构

阵的存储内容,即在数据结构上属于同 1 个双字的 8 个字节在 32 个存储矩阵中存放的情况,

之所以是 32 个存储矩阵是因为一个cache有 4 个双字,一共是 32 个字节。如图所示,同一

背景的方块属于同一双字。整个数据cache为 16KB,由 214B=25×27×25bit可得,32 个存储

矩阵,每个的大小为 128×32bit,其中 128 为字线,32bit分为 4 个字节,分属 4 路。

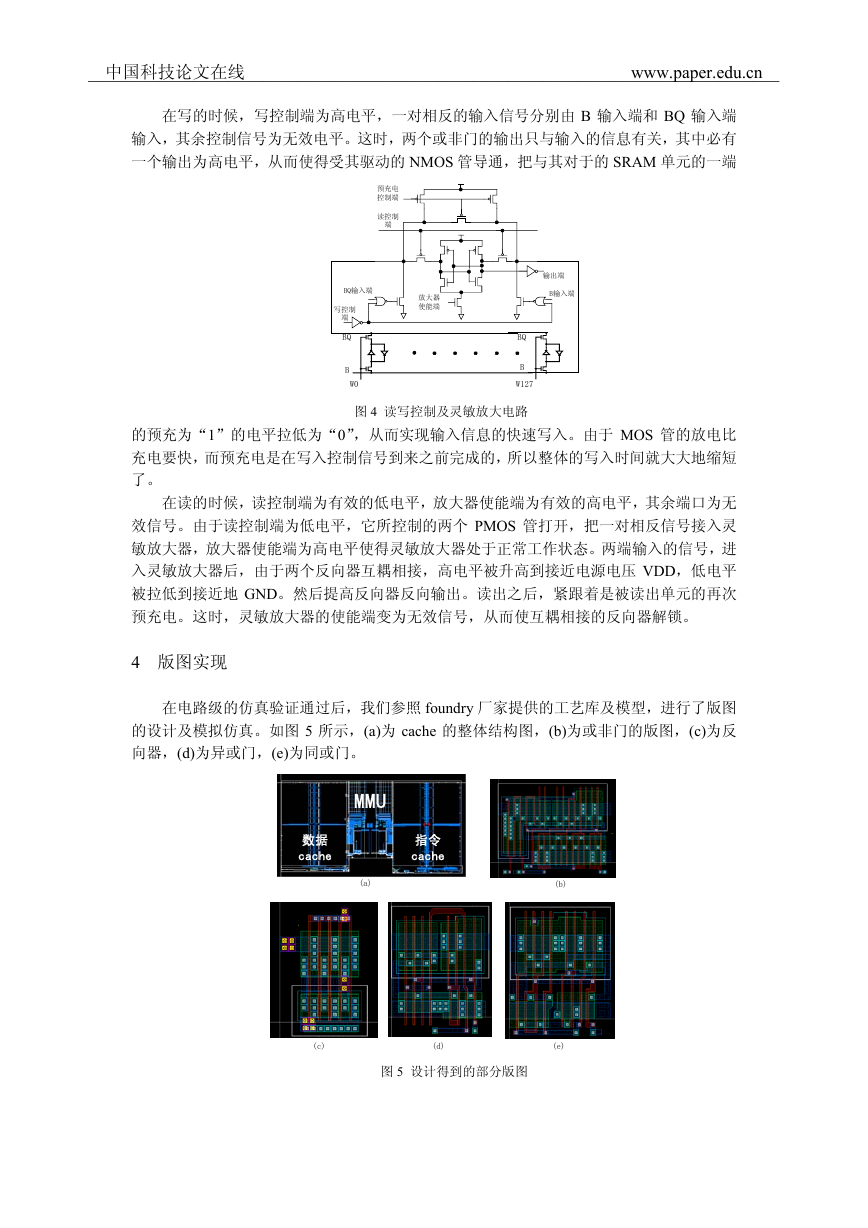

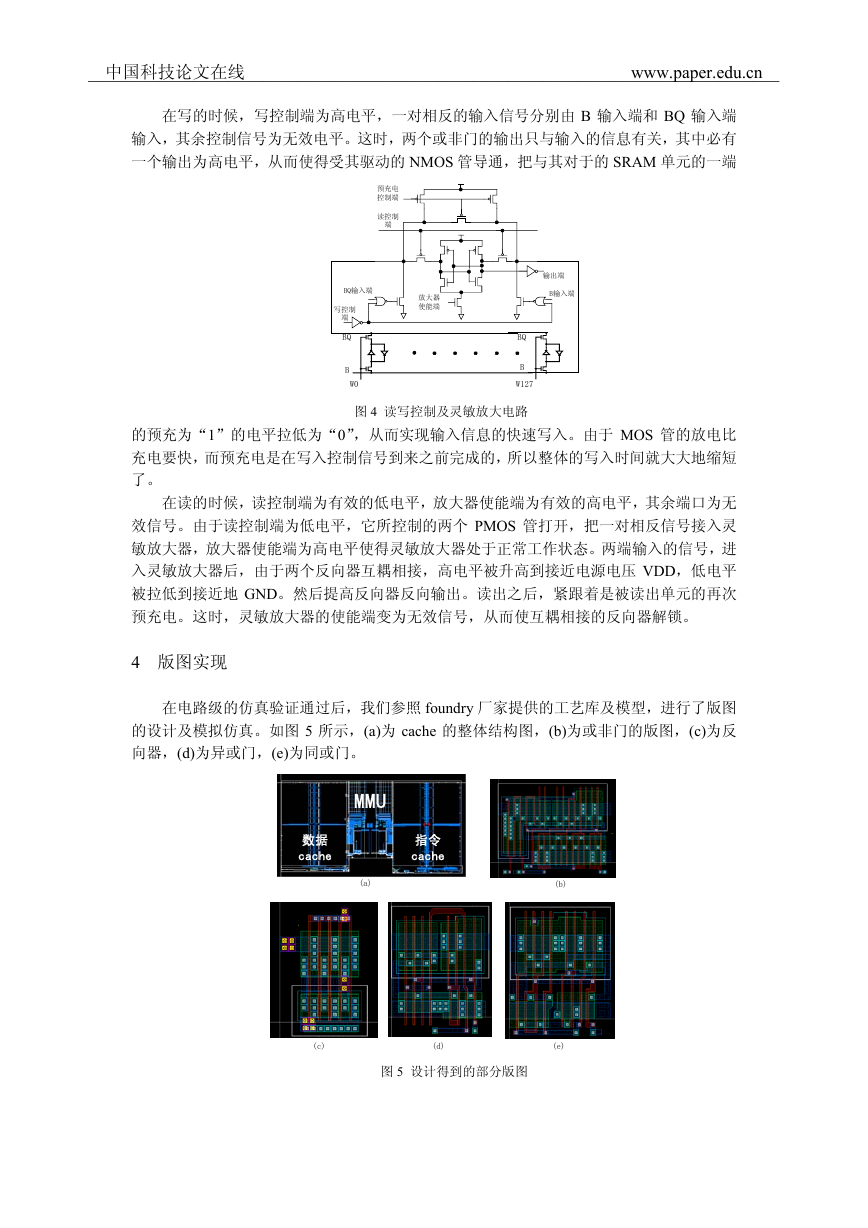

上层结构设计确定后,下层的单元电路设计就显得相对简单了。图 4 所示为我们所设计

的 SRAM 存储单元的读写控制及灵敏放大电路。

在每次 cache 读之后或写之前,先通过给预充电控制端加一个有效的低电平,而其它控

制端所加为无效电平。这时,SRAM 的存储单元的两端就会都被预充成为“1”。持续一段

时间后,预充电控制端电平变为无效的高电平,预充电结束。

中国科技论文在线_______________________________________________________________________________www.paper.edu.cn�

在写的时候,写控制端为高电平,一对相反的输入信号分别由 B 输入端和 BQ 输入端

输入,其余控制信号为无效电平。这时,两个或非门的输出只与输入的信息有关,其中必有

一个输出为高电平,从而使得受其驱动的 NMOS 管导通,把与其对于的 SRAM 单元的一端

预充电

控制端

读控制

端

放大器

使能端

BQ输入端

写控制

端

BQ

B

W0

输出端

B输入端

BQ

B

W127

图 4 读写控制及灵敏放大电路

的预充为“1”的电平拉低为“0”,从而实现输入信息的快速写入。由于 MOS 管的放电比

充电要快,而预充电是在写入控制信号到来之前完成的,所以整体的写入时间就大大地缩短

了。

在读的时候,读控制端为有效的低电平,放大器使能端为有效的高电平,其余端口为无

效信号。由于读控制端为低电平,它所控制的两个 PMOS 管打开,把一对相反信号接入灵

敏放大器,放大器使能端为高电平使得灵敏放大器处于正常工作状态。两端输入的信号,进

入灵敏放大器后,由于两个反向器互耦相接,高电平被升高到接近电源电压 VDD,低电平

被拉低到接近地 GND。然后提高反向器反向输出。读出之后,紧跟着是被读出单元的再次

预充电。这时,灵敏放大器的使能端变为无效信号,从而使互耦相接的反向器解锁。

4 版图实现

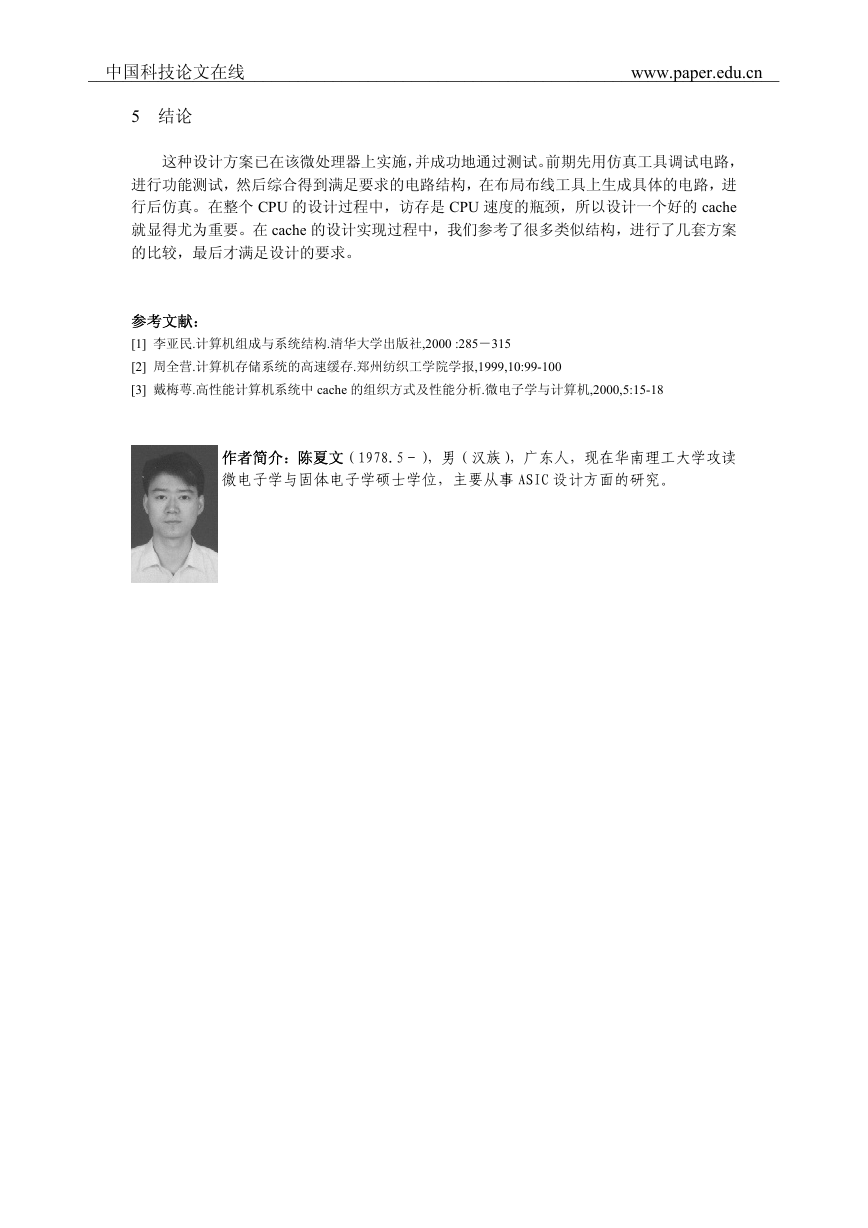

在电路级的仿真验证通过后,我们参照 foundry 厂家提供的工艺库及模型,进行了版图

的设计及模拟仿真。如图 5 所示,(a)为 cache 的整体结构图,(b)为或非门的版图,(c)为反

向器,(d)为异或门,(e)为同或门。

MMU

数据

cache

指令

cache

(a)

(b)

(c)

(d)

(e)

图 5 设计得到的部分版图

中国科技论文在线_______________________________________________________________________________www.paper.edu.cn�

5 结论

这种设计方案已在该微处理器上实施,并成功地通过测试。前期先用仿真工具调试电路,

进行功能测试,然后综合得到满足要求的电路结构,在布局布线工具上生成具体的电路,进

行后仿真。在整个 CPU 的设计过程中,访存是 CPU 速度的瓶颈,所以设计一个好的 cache

就显得尤为重要。在 cache 的设计实现过程中,我们参考了很多类似结构,进行了几套方案

的比较,最后才满足设计的要求。

参考文献:

[1] 李亚民.计算机组成与系统结构.清华大学出版社,2000 :285-315

[2] 周全营.计算机存储系统的高速缓存.郑州纺织工学院学报,1999,10:99-100

[3] 戴梅萼.高性能计算机系统中 cache 的组织方式及性能分析.微电子学与计算机,2000,5:15-18

作者简介:陈夏文(1978.5-),男(汉族),广东人,现在华南理工大学攻读

微电子学与固体电子学硕士学位,主要从事 ASIC 设计方面的研究。

中国科技论文在线_______________________________________________________________________________www.paper.edu.cn�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc