五人多数表决器

一,设计目的:

1,学习使用 EDA 开发工具 MAX+plusII。

2,学习使用 VHDL 语言设计五人多数表决器。

3,熟悉五人多数表决的原理。

二,设计任务:

设计一个五人多数表决器,使其有满足设计要求的功能。

三,设计要求:

1) 五人多数表决逻辑:多数通过;

2) 在主持人控制下,10 秒内表决有效;

3) 采用数码管显示表决 10 秒倒计时;

4) 表决结束后用发光二极管及数码管显示表决结果,数码管显示结果形式:通过,不通

过;

5) 设主持人控制键,复位键:

控制键:启动表决;

复位键:系统复位。

6) 自制实验方案,完成设计任务。

四,设计思路:

�

五人多数表决,只要在规定时间内,赞成人数大于或等于三,则表决通过。因此,只需将每

位表决人的结果相加,判断结果值。设五个开关作为表决器的五个输入变量,输入变量为逻

辑“1”时,表示表决者“赞成”;输入变量为“0”时,表示表决者“不赞成”。输出逻辑

“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。当表决器的五个输

入变量中有 3 个以上(含 3 个)为“1”时。则表决器输出为“1”;否则为“0”。

五,管脚说明:

AA:一维数组 AA 用来表示五位表决者;

PASS:表决最终是否通过(‘1’为“通过”,‘0’为“未通过”);

TOTAL:表决通过的人数;

SHIJIAN:用来显示倒计时;

FUWEI:主持人复位键,用来系统复位;

KAISHI:主持人控制键,用来启动表决;

CLK:系统时钟。

六,源程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_ARITH.all;

use ieee.std_logic_UNSIGNED.all;

ENTITY BIAOJUE IS

PORT(

AA:IN STD_LOGIC_VECTOR(1 TO 5);

�

PASS:OUT BIT;

TOTAL:OUT STD_LOGIC_VECTOR(3 DOWNTO 1);

SHIJIAN:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

FUWEI,KAISHI,CLK:IN STD_LOGIC);

END BIAOJUE;

ARCHITECTURE FUNG OF BIAOJUE IS

BEGIN

PROCESS(AA,CLK,KAISHI,FUWEI)

VARIABLE SUO:BOOLEAN;

VARIABLE SUM:STD_LOGIC_VECTOR(1 TO 3);

BEGIN

IF (FUWEI='0') THEN

PASS<='0';

SHIJIAN<="1010";

SUO:=FALSE;

SUM:="000";

TOTAL<="000";

ELSIF (CLK'EVENT AND CLK='1') THEN

�

IF (KAISHI='1') THEN

IF (NOT SUO) THEN

IF SHIJIAN="0000" THEN

SUO:=TRUE;

FOR N IN 1 TO 5 LOOP

SUM:=AA(N)+SUM;

END LOOP;

ELSE

SHIJIAN<=SHIJIAN-1;

END IF;

END IF;

TOTAL<=SUM;

IF (SUM >= 3) THEN

PASS<='1';

ELSE

PASS<='0';

END IF;

END IF;

�

END IF;

END PROCESS;

END FUNG;

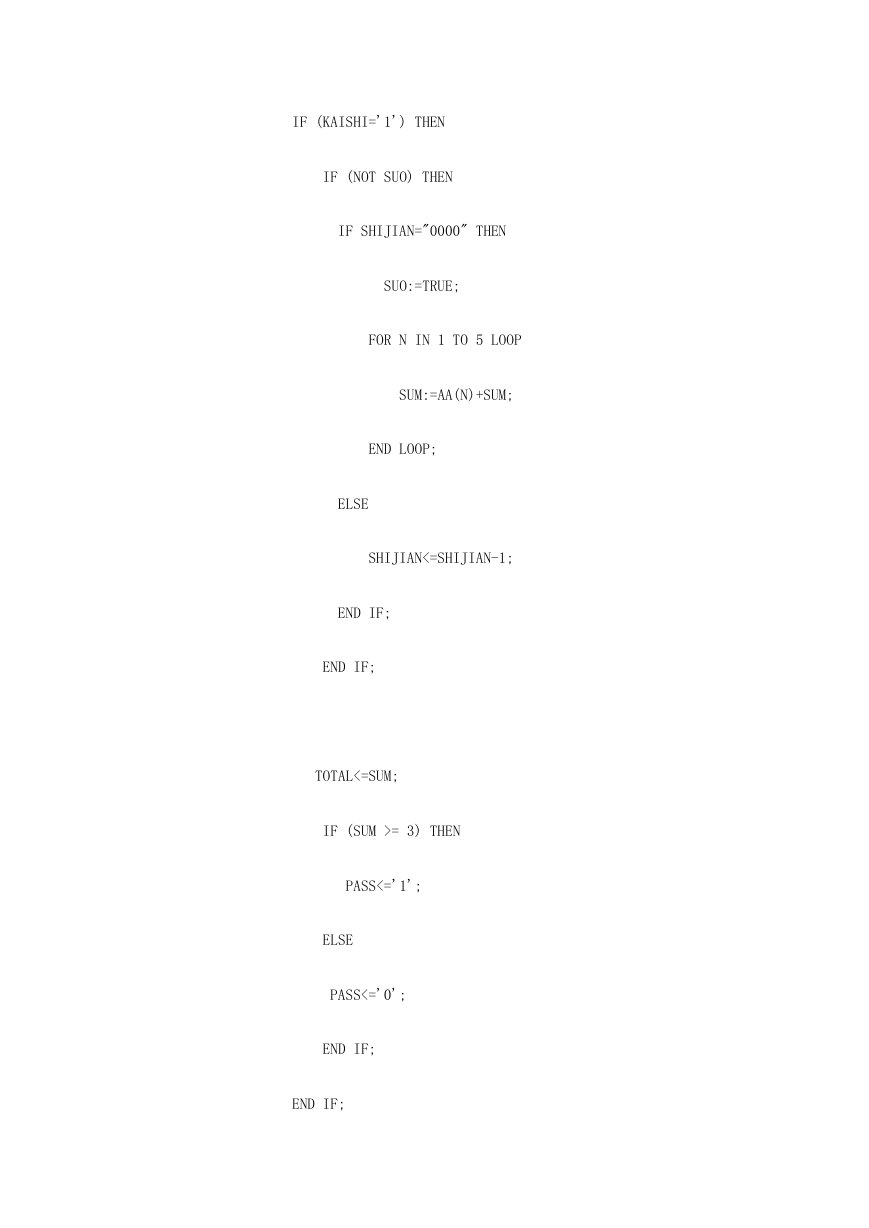

七,实验验证:

建立文本文件,选择 File/New/Text Editor File,输入源程序。保存(保存名

为:biaojue.vhd),编译。编译通过后建立 biaojue.scf 模拟文件,分别赋予不同的条件之

后,得到相应的结果。

八,仿真现象:

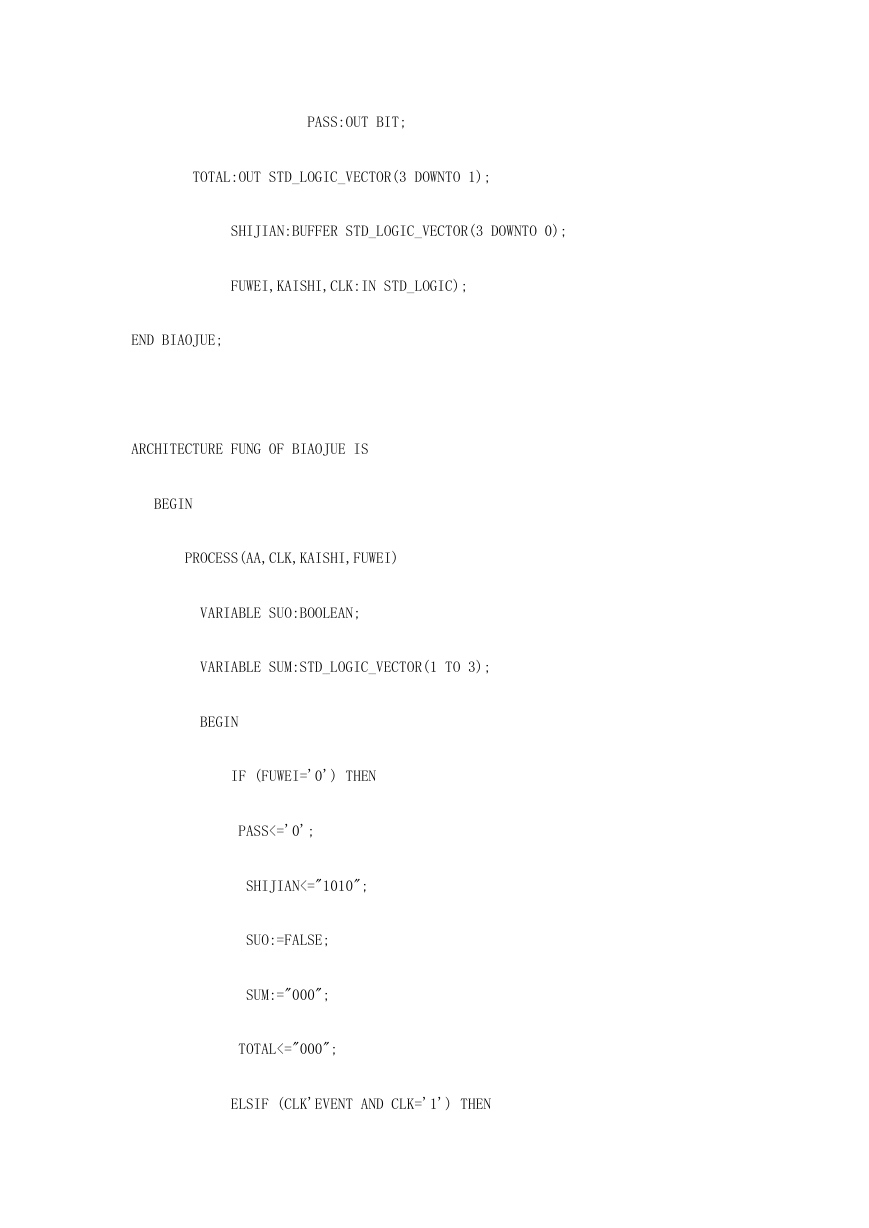

复位时的模拟结果:

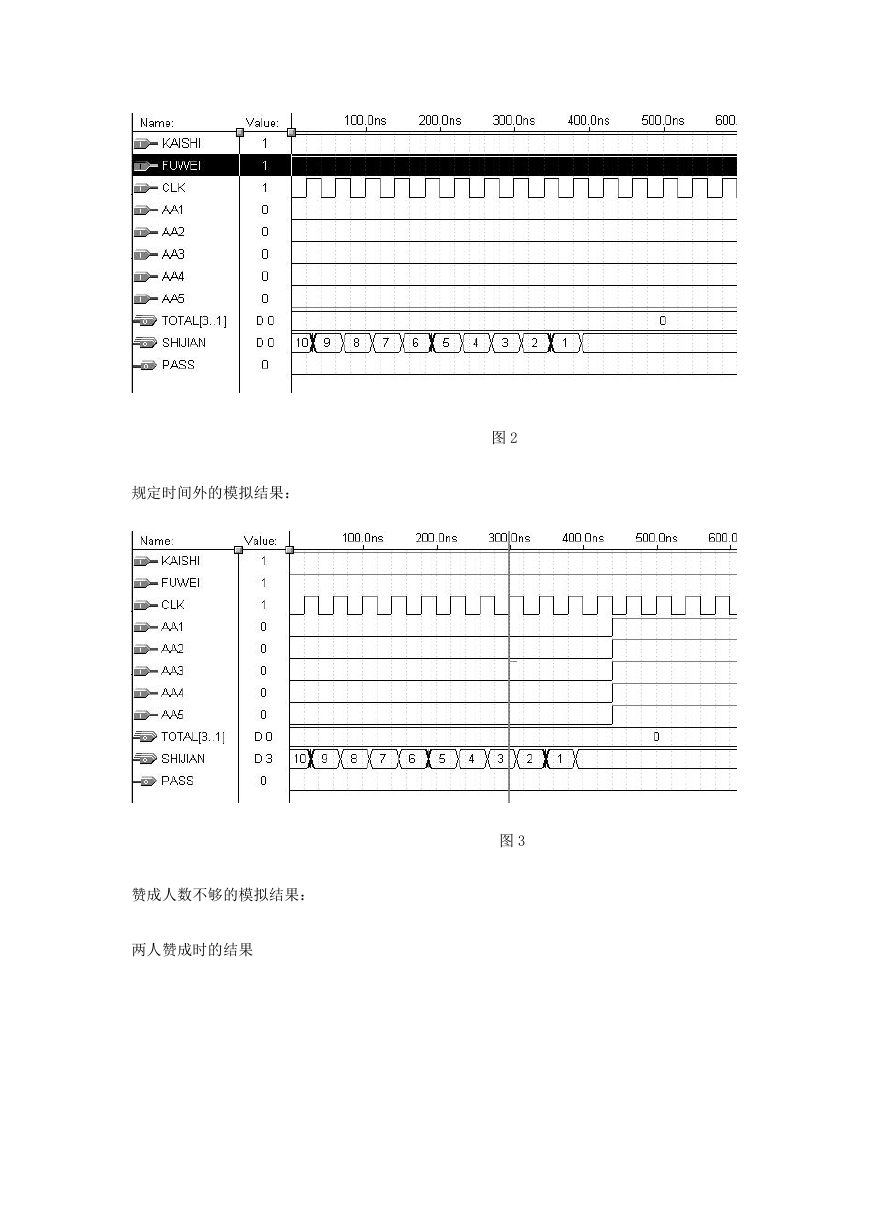

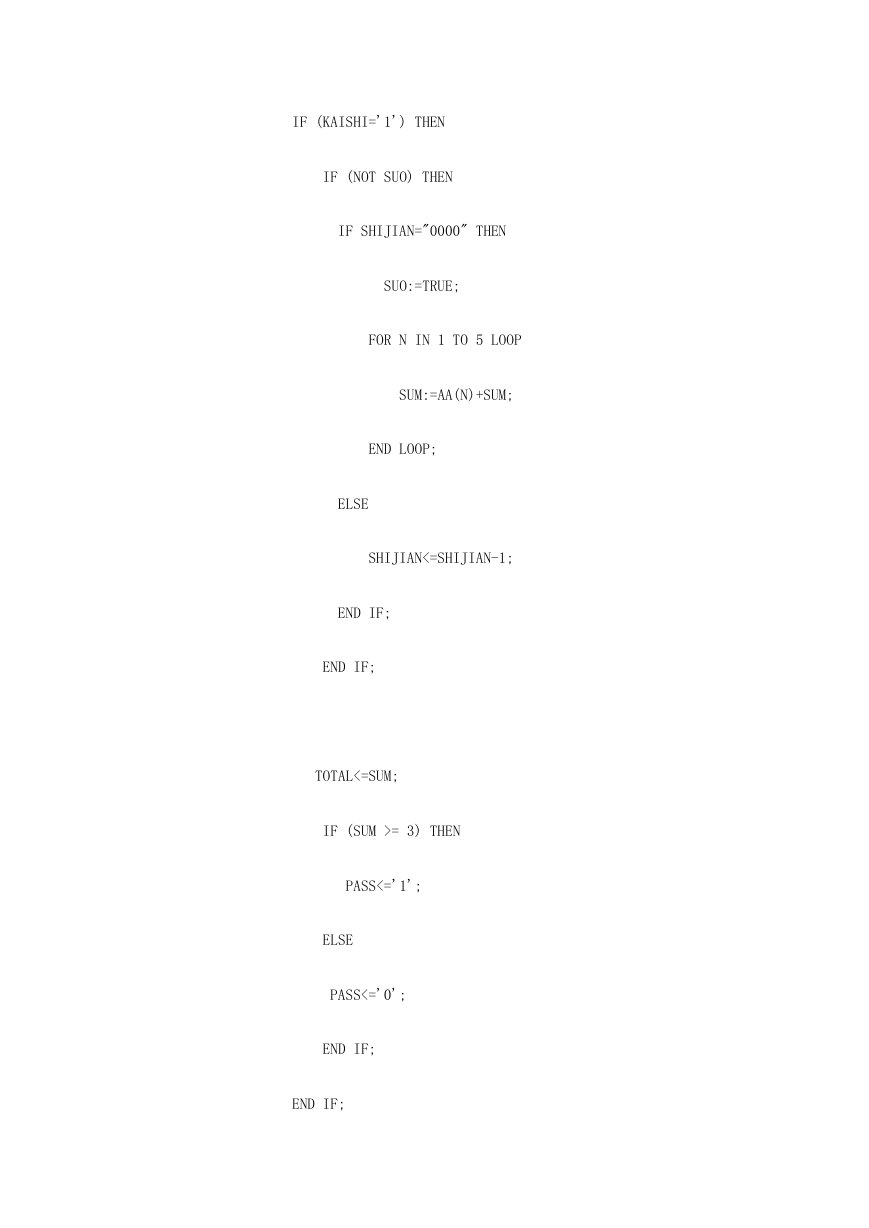

无人赞成时的模拟结果:

图 1

�

图 2

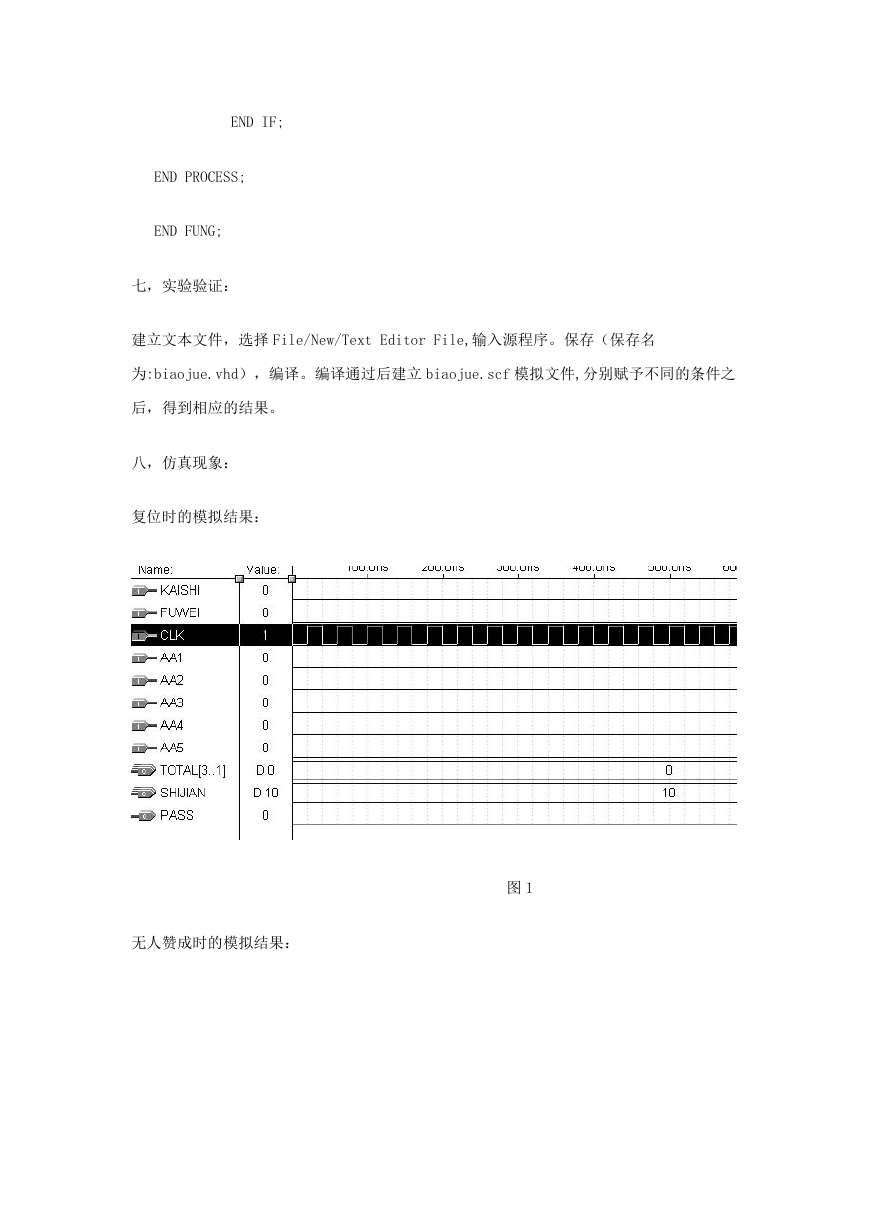

图 3

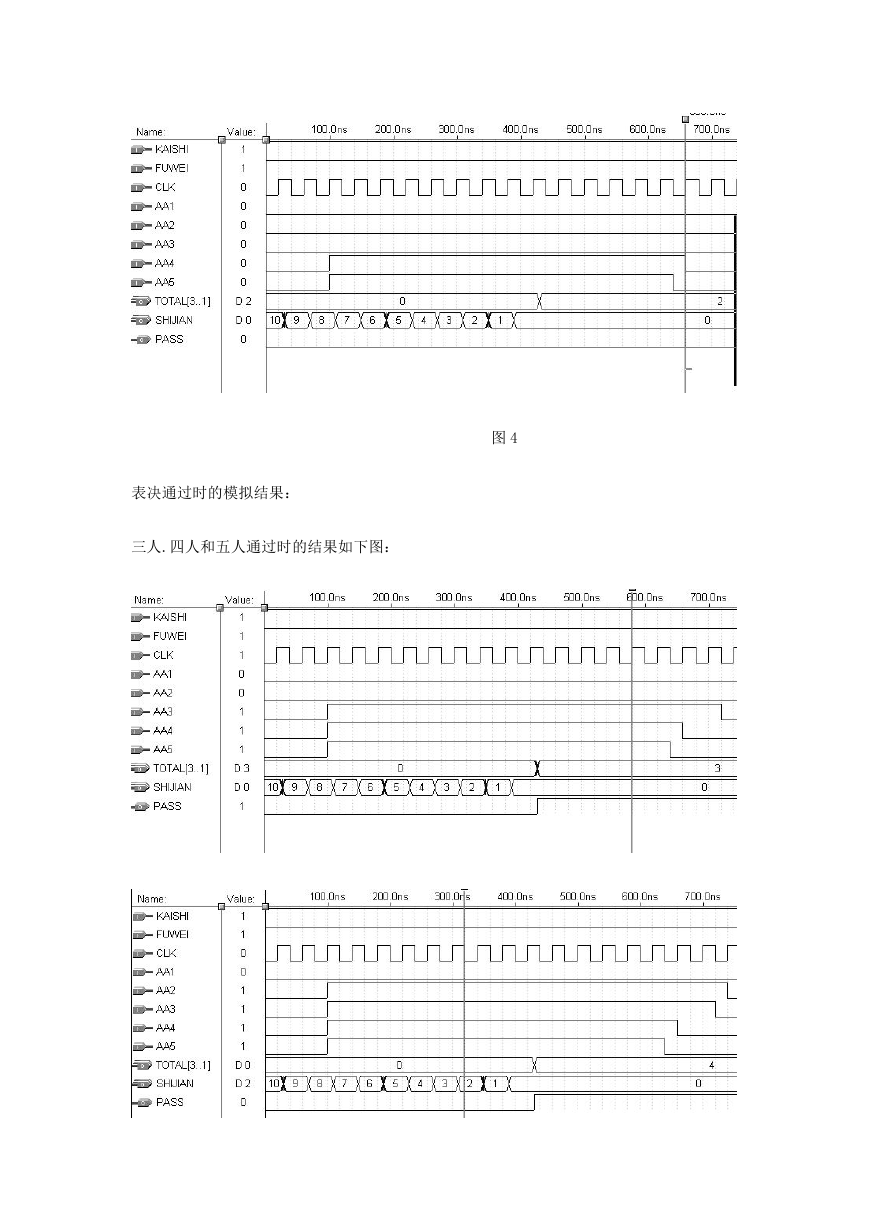

规定时间外的模拟结果:

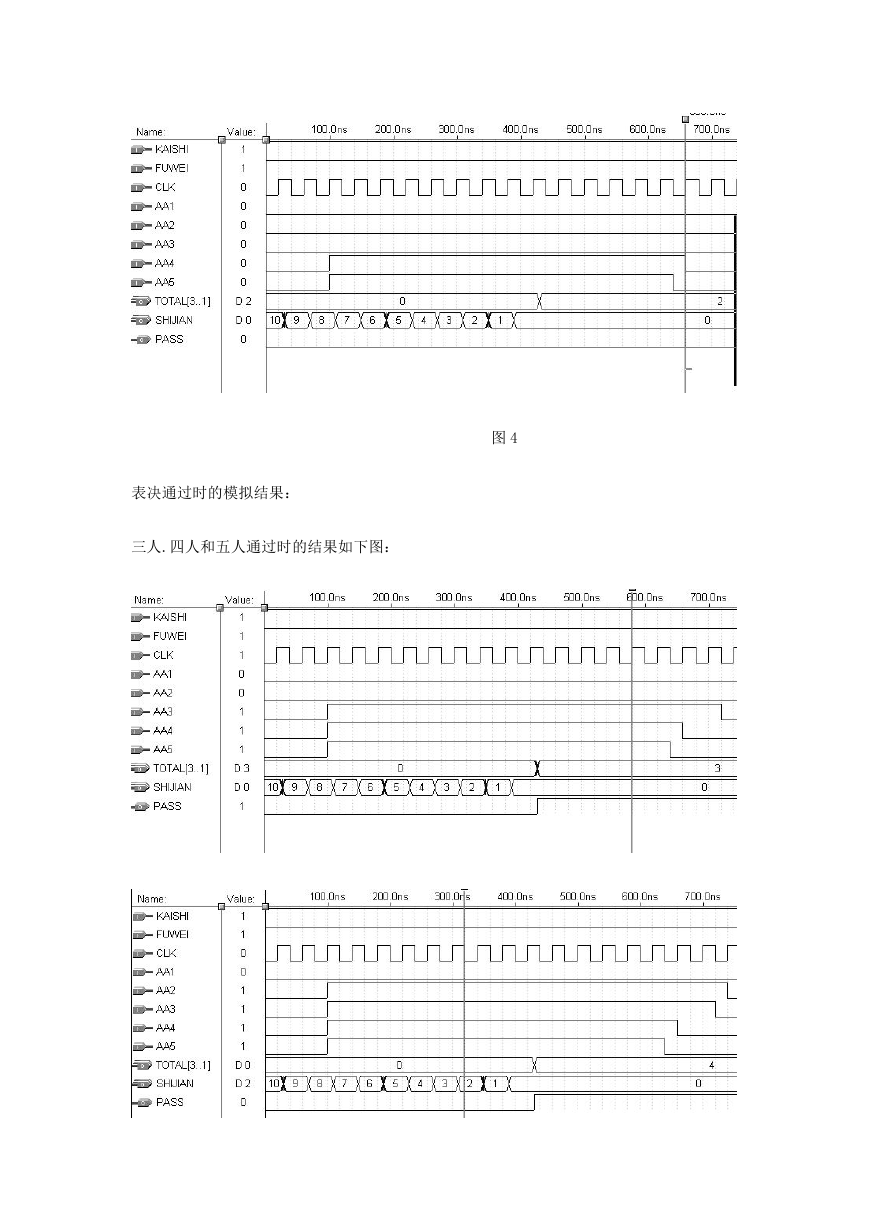

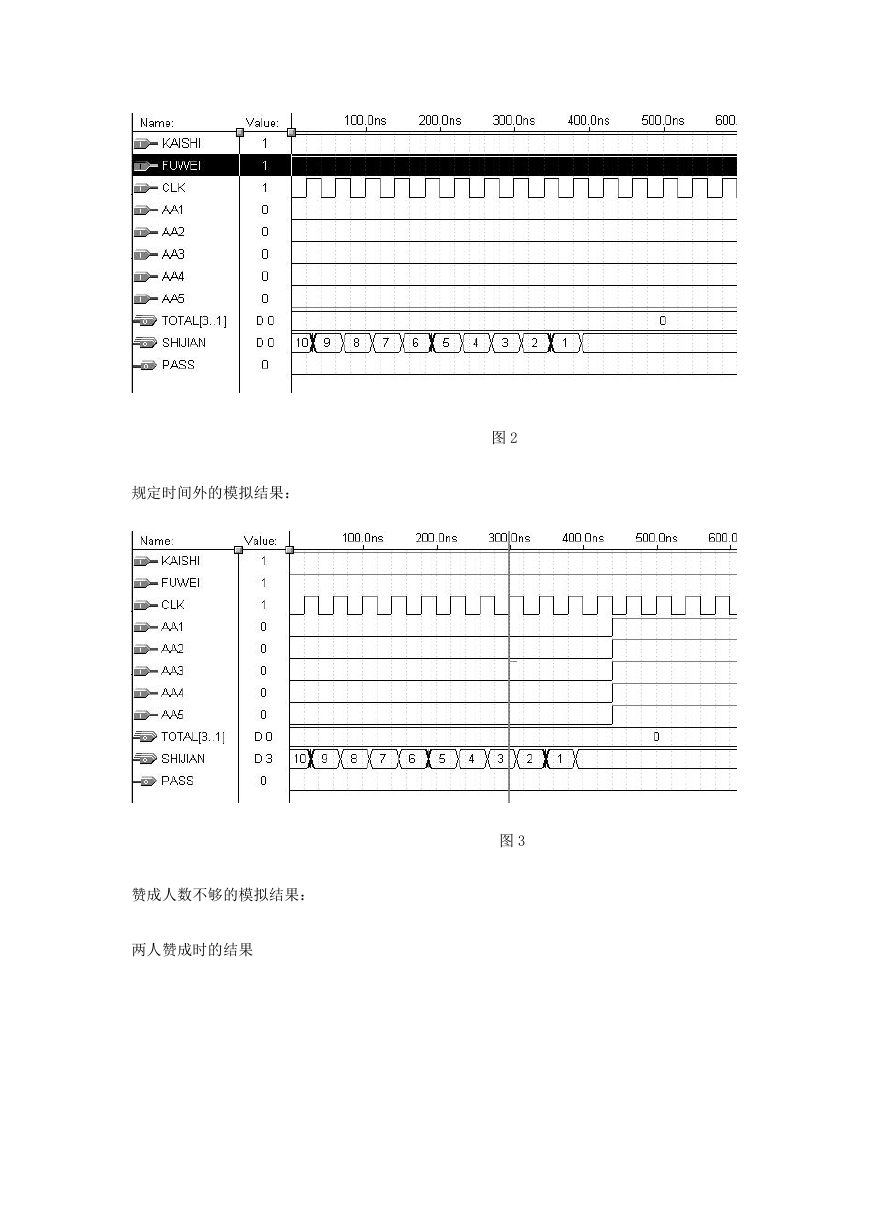

赞成人数不够的模拟结果:

两人赞成时的结果

�

图 4

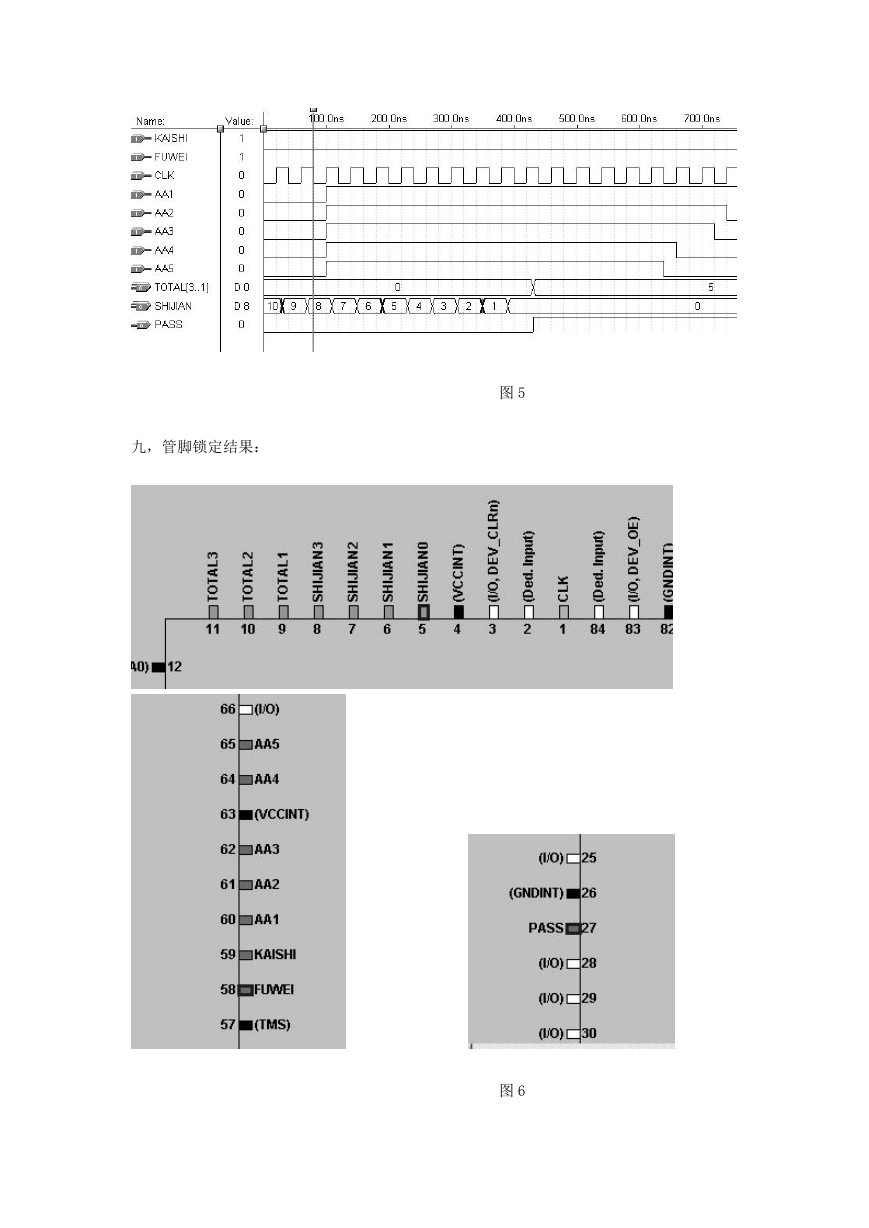

表决通过时的模拟结果:

三人.四人和五人通过时的结果如下图:

�

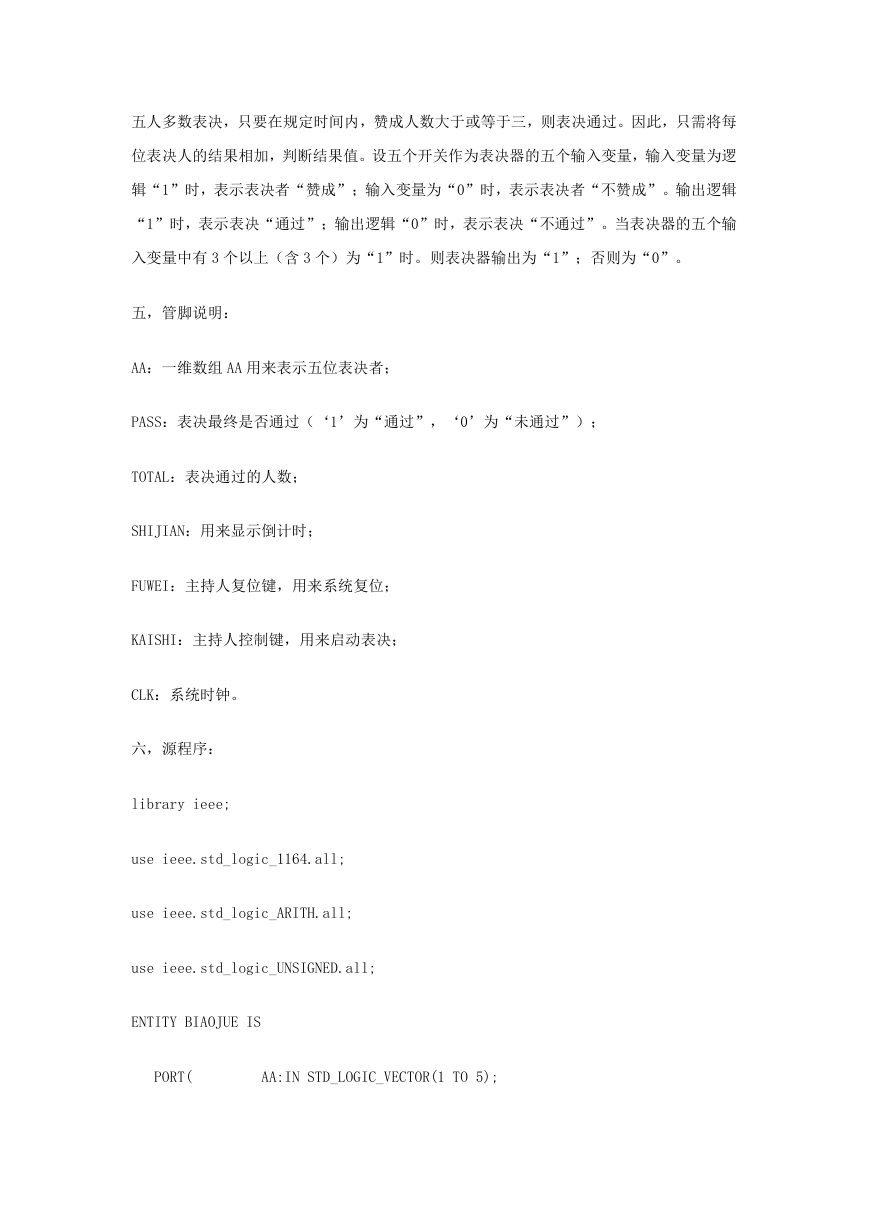

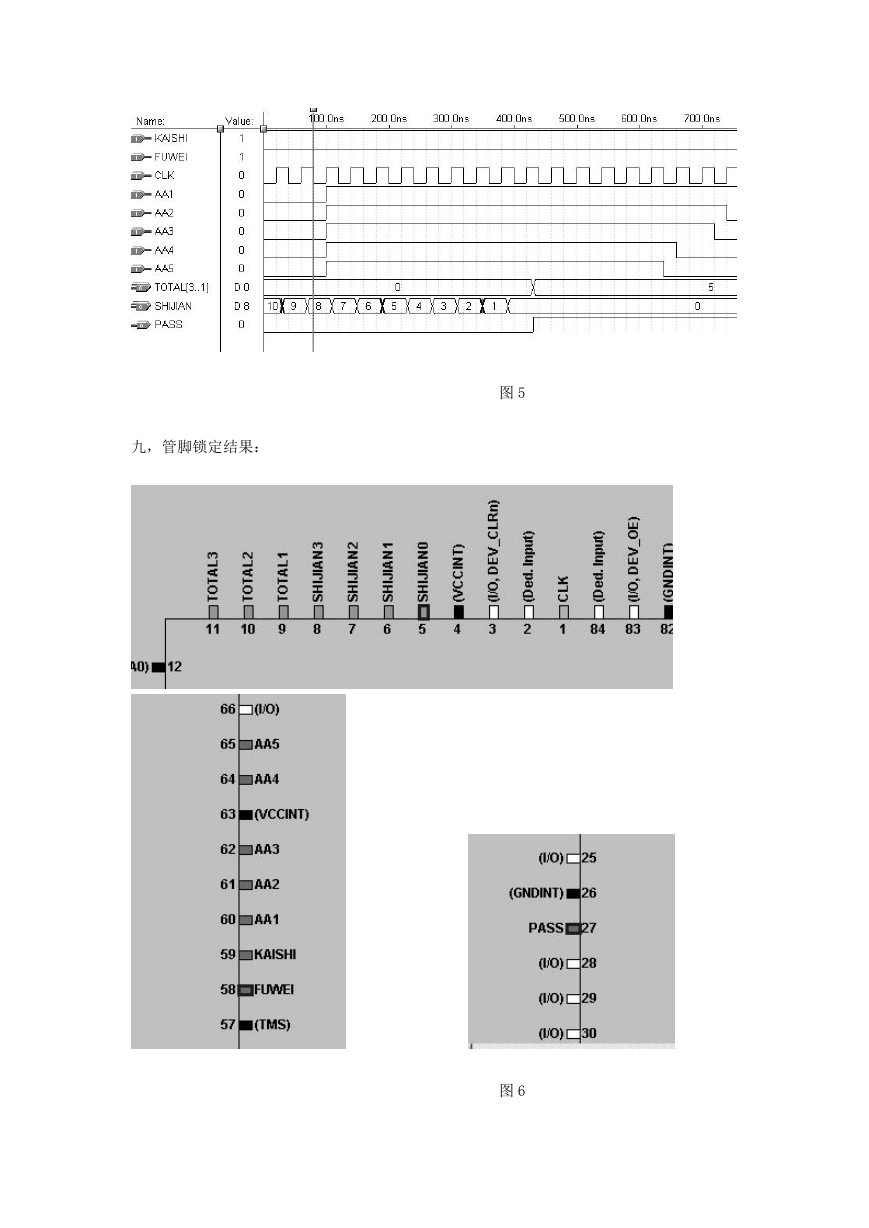

九,管脚锁定结果:

图 5

图 6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc