Chapter 1: Introduction

About This Document

Audience

Organization

Suggested Reading

General Information

Related Documentation

Conventions

Register Access

Register Diagram Field Access Type Legend

Register Macro Usage

Signal Conventions

Acronyms and Abbreviations

Introduction

Target Applications

Features

Architectural Overview

Simplified Block Diagram

Architectural Partitioning

Endianness Support

Memory Interfaces

Chapter 2: Memory Maps

Memory system overview

ARM Platform Memory Map

DMA memory map

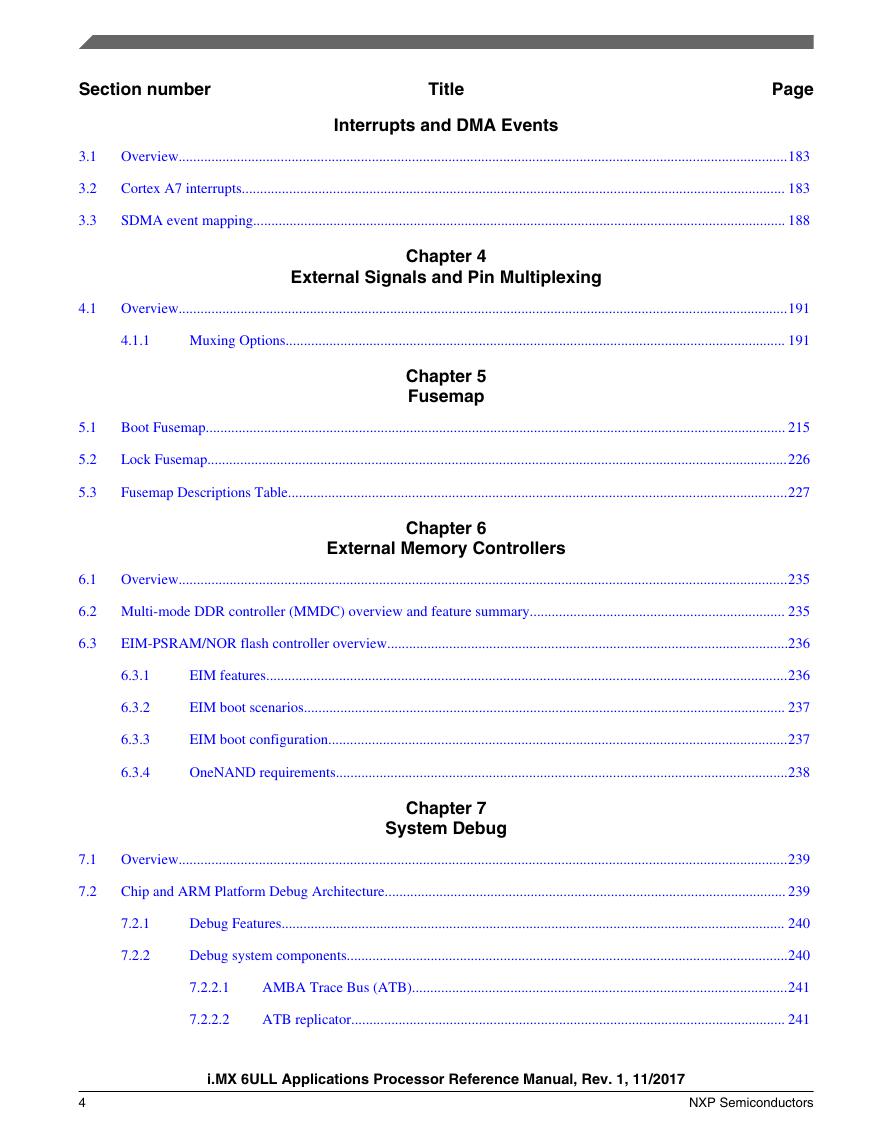

Chapter 3: Interrupts and DMA Events

Overview

Cortex A7 interrupts

SDMA event mapping

Chapter 4: External Signals and Pin Multiplexing

Overview

Muxing Options

Chapter 5: Fusemap

Boot Fusemap

Lock Fusemap

Fusemap Descriptions Table

Chapter 6: External Memory Controllers

Overview

Multi-mode DDR controller (MMDC) overview and feature summary

EIM-PSRAM/NOR flash controller overview

EIM features

EIM boot scenarios

EIM boot configuration

OneNAND requirements

Chapter 7: System Debug

Overview

Chip and ARM Platform Debug Architecture

Debug Features

Debug system components

AMBA Trace Bus (ATB)

ATB replicator

Embedded Cross Triggering

Cross-Trigger Matrix (CTM)

Cross-Trigger Interface (CTI)

Debug Access Port (DAP)

Chip-Specific SJC Features

JTAG Disable Mode

JTAG ID

System JTAG Controller - SJC

System JTAG controller main features

SJC TAP Port

SJC main blocks

Smart DMA (SDMA) core

SDMA On Chip Emulation Module (OnCE) Feature Summary

Other SDMA Debug Functionality

SDMA ROM Patching

Miscellaneous

Clock/Reset/Power

Supported tools

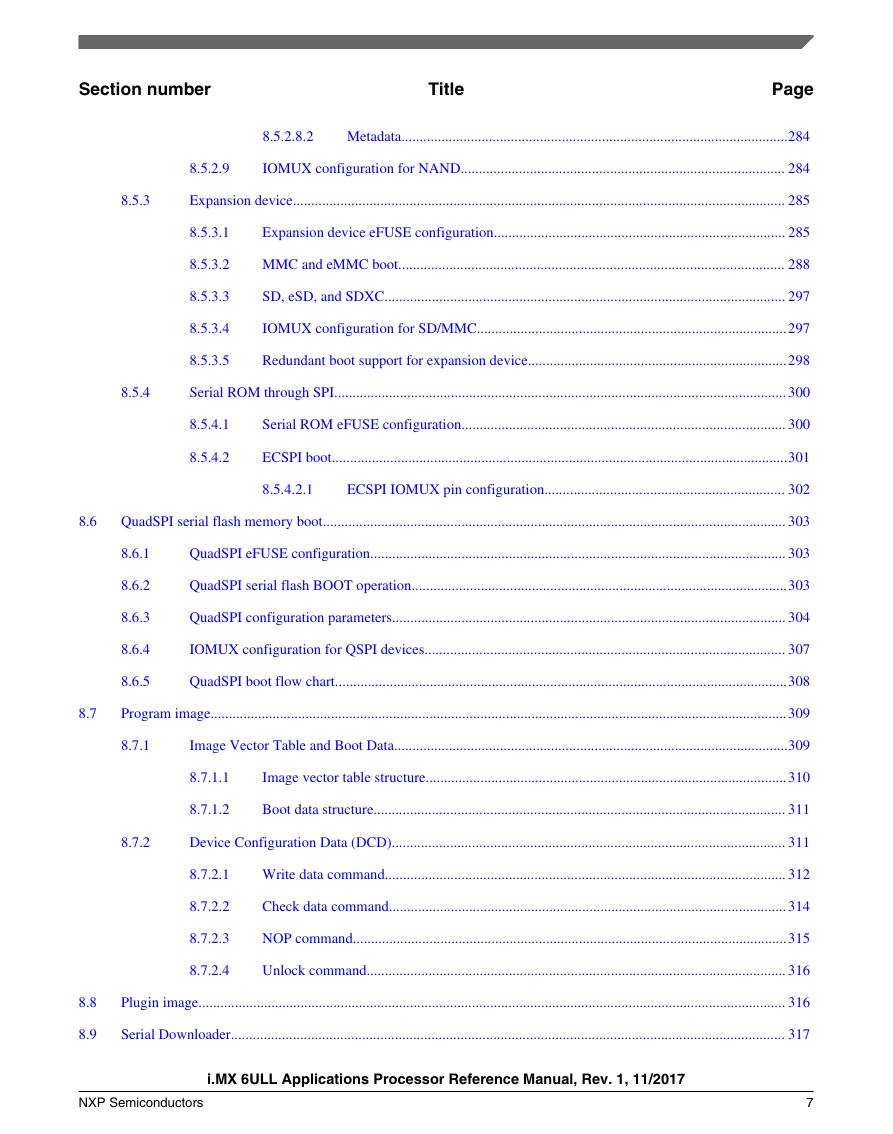

Chapter 8: System Boot

Overview

Boot modes

Boot mode pin settings

High-level boot sequence

Boot From Fuses mode (BOOT_MODE[1:0] = 00b)

Serial Downloader

Internal Boot mode (BOOT_MODE[1:0] = 0b10)

Boot security settings

Device configuration

Boot eFUSE descriptions

GPIO boot overrides

Device Configuration Data (DCD)

Device initialization

Internal ROM/RAM memory map

Boot block activation

Clocks at boot time

Enabling MMU and caches

Exception handling

Interrupt handling during boot

Persistent bits

Boot devices (internal boot)

NOR flash/OneNAND using EIM interface

NOR flash boot operation

OneNAND flash boot operation

IOMUX configuration for EIM devices

NAND flash

NAND eFUSE configuration

NAND flash boot flow and Boot Control Blocks (BCB)

Firmware configuration block

Discovered Bad Block Table (DBBT)

Bad block handling in ROM

Read-retry handling in the ROM

Toggle mode DDR NAND boot

GPMI and BCH clocks configuration

Setup DMA for DDR transfers

Reconfigure timing and speed using values in FCB

Typical NAND page organization

BCH ECC page organization

Metadata

IOMUX configuration for NAND

Expansion device

Expansion device eFUSE configuration

MMC and eMMC boot

SD, eSD, and SDXC

IOMUX configuration for SD/MMC

Redundant boot support for expansion device

Serial ROM through SPI

Serial ROM eFUSE configuration

ECSPI boot

ECSPI IOMUX pin configuration

QuadSPI serial flash memory boot

QuadSPI eFUSE configuration

QuadSPI serial flash BOOT operation

QuadSPI configuration parameters

IOMUX configuration for QSPI devices

QuadSPI boot flow chart

Program image

Image Vector Table and Boot Data

Image vector table structure

Boot data structure

Device Configuration Data (DCD)

Write data command

Check data command

NOP command

Unlock command

Plugin image

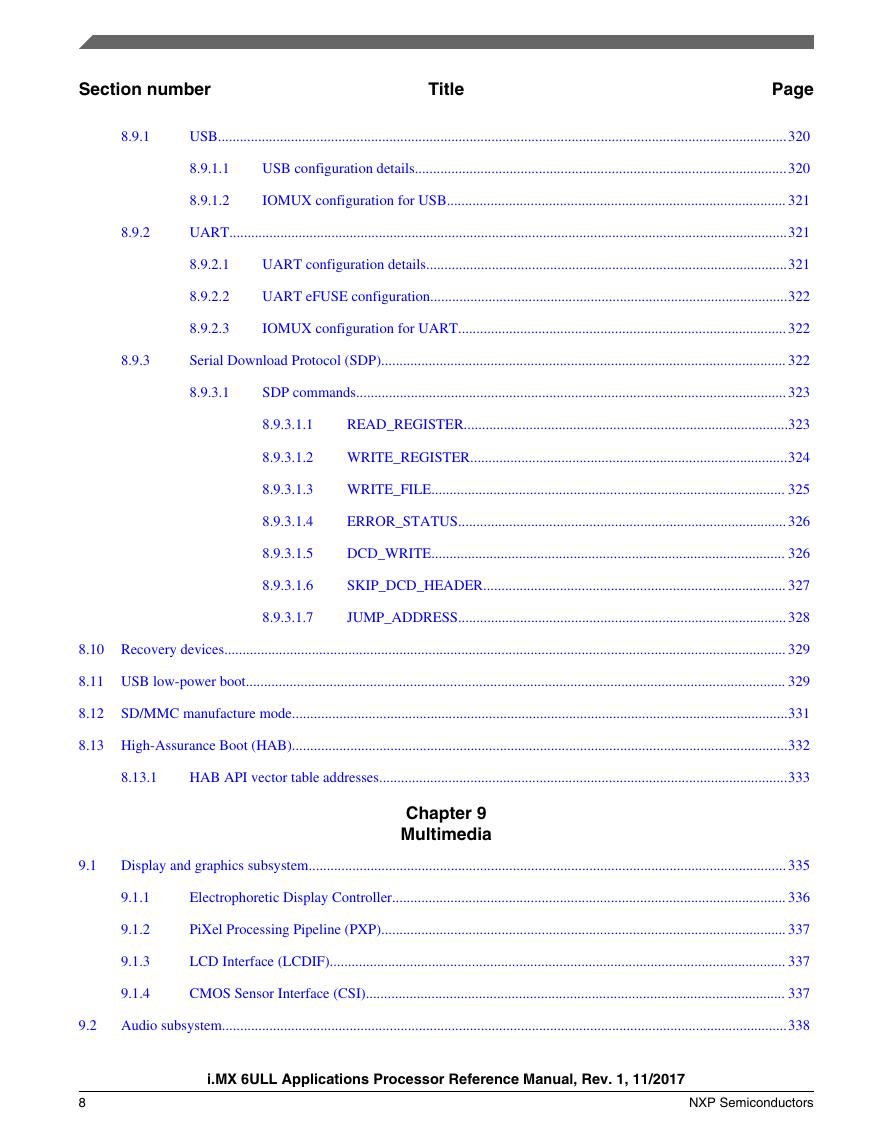

Serial Downloader

USB

USB configuration details

IOMUX configuration for USB

UART

UART configuration details

UART eFUSE configuration

IOMUX configuration for UART

Serial Download Protocol (SDP)

SDP commands

READ_REGISTER

WRITE_REGISTER

WRITE_FILE

ERROR_STATUS

DCD_WRITE

SKIP_DCD_HEADER

JUMP_ADDRESS

Recovery devices

USB low-power boot

SD/MMC manufacture mode

High-Assurance Boot (HAB)

HAB API vector table addresses

Chapter 9: Multimedia

Display and graphics subsystem

Electrophoretic Display Controller

PiXel Processing Pipeline (PXP)

LCD Interface (LCDIF)

CMOS Sensor Interface (CSI)

Audio subsystem

Audio Subsystem Module Overview

Medium Quality Sound (MQS)

Synchronous Audio Interface (SAI)

Enhanced Serial Audio Interface (ESAI)

Sony/Philips Digital Interface (SPDIF)

Asynchronous Sample Rate Converter (ASRC)

Chapter 10: Clock and Power Management

Introduction

Device Power Management Architecture Components

Centralized components of clock generation and management

Centralized components of power generation, distribution and management

Reset generation and distribution system

Power and clock management framework

Clock Management

Centralized components of clock management system

Clock generation

Crystal Oscillator (XTALOSC)

Low Voltage Differential Signaling (LVDS) I/O ports

PLLs

General PLL Control and Status Functions

CCM

Low Power Clock Gating unit (LPCG)

Peripheral components of clock management system

Interface and functional clock

Block level clock management

Master clock protocol

Slave clock protocol

Clock Domain(s)

Domain level clock management

Domain dependencies

Power management

Centralized Components of Power Management System

Integrated PMU

Digital LDO Regulators

Analog LDO regulators

USB LDO

SNVS regulator

GPC - General Power Controller

SRC - System reset Controller

Power domain(s)

Power distribution

Domain Memory and domain logic state retention in case of Power Gating

Power Gating Domain Management

ARM Core Platform

SOC_PD

SoC

Power Gating domain dependencies

Voltage domains

Voltage domain management

Dynamic

Voltage Scaling

Static

Standby Leakage reduction (SLR)

ANALOG PHYs IPs

System domains layout

Power management techniques

Power saving techniques

Thermal-aware power management

Peripheral Power management

Main memory power management

Video-Graphics system power management

IO power reduction

Examples of External Power Supply Interface

ONOFF (Button)

Chapter 11: System Security

Overview

Central Security Unit (CSU)

CSU Overview

CSU Features

CSU Functional Description

CSU Peripheral Access Policy

Secure Non-Volatile Storage (SNVS)

SNVS Overview

Tamper Detection

Data Co-Processor (DCP)

High-Assurance Boot (HAB)

System JTAG Controller (SJC)

Chapter 12: ARM Cortex A7 Platform (CA7)

Overview

External Signals

Clocks

Platform Configuration

Low-Power and Performance

Chapter 13: Analog-to-Digital Converter (ADC)

Overview

Features

ADC I/F block diagram

ADC block diagram

ADC module interface

Modes of Operation

External Signals

Functional Description

Clock Select and Divide Control

Voltage Reference Selection

Conversion Control

Initiating Conversions

Completing Conversions

Aborting Conversions

Power Control

Sample Time and Total Conversion Time

Conversion Time Examples

Typical conversion time configuration

Long conversion time configuration

Short conversion time configuration

Hardware Average Function

Automatic Compare Function

Calibration Function

User Defined Offset Function

MCU Wait Mode Operation

MCU Stop Mode Operation

Stop Mode With ADACK Disabled

Stop Mode With ADACK Enabled

Initialization Information

ADC Module Initialization Example

Initialization Sequence

Pseudo-Code Example

Application Information

Sources of Error

Sampling Error

Pin Leakage Error

Noise-Induced Errors

Code Width and Quantization Error

Linearity Errors

Code Jitter, Non-Monotonicity, and Missing Codes

Memory map and register definition

ADCx

ADCx_HC0

ADCx_HS

ADCx_R0

ADCx_CFG

ADCx_GC

ADCx_GS

ADCx_CV

ADCx_OFS

ADCx_CAL

Memory map and register definition

ADCx

ADCx_HC0

ADCx_HCn

ADCx_HS

ADCx_R0

ADCx_Rn

ADCx_CFG

ADCx_GC

ADCx_GS

ADCx_CV

ADCx_OFS

ADCx_CAL

Chapter 14: AHB to IP Bridge (AIPSTZ)

Overview

Features

Clocks

Functional Description

Access Protections

Access Support

Initialization Information

Security Block

AIPSTZ Memory Map/Register Definition

AIPSTZx

AIPSTZx_MPR

AIPSTZx_OPACR

AIPSTZx_OPACR1

AIPSTZx_OPACR2

AIPSTZx_OPACR3

AIPSTZx_OPACR4

Chapter 15: AHB-to-APBH Bridge with DMA (APBH-Bridge-DMA)

Overview

Clocks

APBH DMA

NAND Read Status Polling Example

APBH Memory Map/Register Definition

APBH

APBH_CTRL0n

APBH_CTRL1n

APBH_CTRL2n

APBH_CHANNEL_CTRLn

APBH_DEVSEL

APBH_DMA_BURST_SIZE

APBH_DEBUG

APBH_CHn_CURCMDAR

APBH_CHn_NXTCMDAR

APBH_CHn_CMD

APBH_CHn_BAR

APBH_CHn_SEMA

APBH_CHn_DEBUG1

APBH_CHn_DEBUG2

APBH_VERSION

Chapter 16: Asynchronous Sample Rate Converter (ASRC)

Overview

Features

Modes of Operation

Data Transfer Schemes

Data Input Modes

Data Output Modes

Word Alignment Supported

Input Data Alignment Modes

Output Data Alignment Modes

Clocks

Interrupts

DMA requests

Functional Description

Algorithm Description

Signal processing flow

Operation of the Filter

Support of Physical Clocks

Startup Procedure

ASRC Memory Map/Register Definition

ASRC

ASRC_ASRCTR

ASRC_ASRIER

ASRC_ASRCNCR

ASRC_ASRCFG

ASRC_ASRCSR

ASRC_ASRCDR1

ASRC_ASRCDR2

ASRC_ASRSTR

ASRC_ASRPMnn

ASRC_ASRTFR1

ASRC_ASRCCR

ASRC_ASRDIn

ASRC_ASRDOn

ASRC_ASRIDRHA

ASRC_ASRIDRLA

ASRC_ASRIDRHB

ASRC_ASRIDRLB

ASRC_ASRIDRHC

ASRC_ASRIDRLC

ASRC_ASR76K

ASRC_ASR56K

ASRC_ASRMCRA

ASRC_ASRFSTA

ASRC_ASRMCRB

ASRC_ASRFSTB

ASRC_ASRMCRC

ASRC_ASRFSTC

ASRC_ASRMCR1n

Chapter 17: 40-BIT Correcting ECC Accelerator (BCH)

Overview

Operation

BCH Limitations and Assumptions

Flash Page Layout

Determining the ECC layout for a device

4K+218 flash, 10 bytes metadata, 512 byte data blocks, separate metadata, Assuming GF(213)

4K+128 flash, 10 bytes metadata, 1024 byte data blocks, separate metadata, assuming GF(213) for data and GF(214) for metadata

Data Buffers in System Memory

Memory to Memory (Loopback) Operation

Programming the BCH/GPMI Interfaces

BCH Encoding for NAND Writes

DMA Structure Code Example

Using the BCH Encoder

BCH Decoding for NAND Reads

DMA Structure Code Example

Using the Decoder

Interrupts

Behavior During Reset

BCH Memory Map/Register Definition

BCH

BCH_CTRLn

BCH_STATUS0n

BCH_MODEn

BCH_ENCODEPTRn

BCH_DATAPTRn

BCH_METAPTRn

BCH_LAYOUTSELECTn

BCH_FLASH0LAYOUT0n

BCH_FLASH0LAYOUT1n

BCH_FLASH1LAYOUT0n

BCH_FLASH1LAYOUT1n

BCH_FLASH2LAYOUT0n

BCH_FLASH2LAYOUT1n

BCH_FLASH3LAYOUT0n

BCH_FLASH3LAYOUT1n

BCH_DEBUG0n

BCH_DBGKESREADn

BCH_DBGCSFEREADn

BCH_DBGSYNDGENREADn

BCH_DBGAHBMREADn

BCH_BLOCKNAMEn

BCH_VERSIONn

BCH_DEBUG1n

Chapter 18: Clock Controller Module (CCM)

Overview

Features

CCM Block Diagram

External Signals

CCM Clock Tree

System Clocks

Functional Description

Clock Generation

External Low Frequency Clock - CKIL

CKIL synchronizing to IPG_CLK

External High Frequency Clock - CKIH and internal oscillator

PLL reference clock

ARM PLL

USB PLLs

System PLL

Audio / Video PLL

Ethernet PLL

Phase Fractional Dividers (PFD)

CCM internal clock generation

Clock Switcher

PLL bypass procedure

PLL clock change

Clock Root Generator

Initial values controlled by the System JTAG Controller (SJC).

Divider change handshake

Disabling / Enabling PLLs

Clock Switching Multiplexers

Low Power Clock Gating module (LPCG)

MMDC handshake

DVFS support

Power modes

RUN mode

WAIT mode

Entering WAIT mode

Exiting WAIT mode

STOP mode

Entering STOP mode

Exiting STOP mode

CCM Memory Map/Register Definition

CCM

CCM_CCR

CCM_CCDR

CCM_CSR

CCM_CCSR

CCM_CACRR

CCM_CBCDR

CCM_CBCMR

CCM_CSCMR1

CCM_CSCMR2

CCM_CSCDR1

CCM_CS1CDR

CCM_CS2CDR

CCM_CDCDR

CCM_CHSCCDR

CCM_CSCDR2

CCM_CSCDR3

CCM_CDHIPR

CCM_CLPCR

CCM_CISR

CCM_CIMR

CCM_CCOSR

CCM_CGPR

CCM_CCGR0

CCM_CCGR1

CCM_CCGR2

CCM_CCGR3

CCM_CCGR4

CCM_CCGR5

CCM_CCGR6

CCM_CMEOR

CCM Analog Memory Map/Register Definition

CCM_ANALOG

CCM_ANALOG_PLL_ARMn

CCM_ANALOG_PLL_USB1n

CCM_ANALOG_PLL_USB2n

CCM_ANALOG_PLL_SYSn

CCM_ANALOG_PLL_SYS_SS

CCM_ANALOG_PLL_SYS_NUM

CCM_ANALOG_PLL_SYS_DENOM

CCM_ANALOG_PLL_AUDIOn

CCM_ANALOG_PLL_AUDIO_NUM

CCM_ANALOG_PLL_AUDIO_DENOM

CCM_ANALOG_PLL_VIDEOn

CCM_ANALOG_PLL_VIDEO_NUM

CCM_ANALOG_PLL_VIDEO_DENOM

CCM_ANALOG_PLL_ENETn

CCM_ANALOG_PFD_480n

CCM_ANALOG_PFD_528n

CCM_ANALOG_MISC0n

CCM_ANALOG_MISC1n

CCM_ANALOG_MISC2n

Chapter 19: CMOS Sensor Interface (CSI)

Overview

External Signals

Clocks

Principles of Operation

Data Transfer with the Embedded DMA Controllers

Gated Clock Mode

Non-Gated Clock Mode

CCIR656 Interlace Mode

CCIR656 Progressive Mode

Error Correction for CCIR656 Coding

Deinterlacer

Interrupt Generation

Start Of Frame Interrupt (SOF_INT)

End Of Frame Interrupt (EOF_INT)

Change Of Field Interrupt (COF_INT)

CCIR Error Interrupt (ECC_INT)

RxFIFO Full Interrupt (RxFF_INT)

Statistic FIFO Full Interrupt (STATFF_INT)

RxFIFO Overrun Interrupt (RFF_OR_INT)

Statistic FIFO Overrun Interrupt (SFF_OR_INT)

Frame Buffer1 DMA Transfer Done Interrupt (DMA_TSF_DONE_FB1)

Frame Buffer2 DMA Transfer Done Interrupt (DMA_TSF_DONE_FB2)

Statistic FIFO DMA Transfer Done Interrupt (DMA_TSF_DONE_SFF)

AHB Bus Response Error Interrupt (HRESP_ERR_INT)

DMA Field 0 Transfer Done Interrupt (DMA_FIELD0_DONE)

DMA Field 1 Transfer Done Interrupt (DMA_FIELD1_DONE)

Base Address Change Error Interrupt (BASEADDR_CHANGE_ERROR)

Data Packing Style

STAT FIFO Path

CSI Memory Map/Register Definition

CSI

CSI_CSICR1

CSI_CSICR2

CSI_CSICR3

CSI_CSISTATFIFO

CSI_CSIRFIFO

CSI_CSIRXCNT

CSI_CSISR

CSI_CSIDMASA_STATFIFO

CSI_CSIDMATS_STATFIFO

CSI_CSIDMASA_FB1

CSI_CSIDMASA_FB2

CSI_CSIFBUF_PARA

CSI_CSIIMAG_PARA

CSI_CSICR18

CSI_CSICR19

Chapter 20: Enhanced Configurable SPI (ECSPI)

Overview

Features

Modes and Operations

External Signals

Clocks

Functional Description

Master Mode

Slave Mode

Low Power Modes

Operations

Typical Master Mode

Master Mode with SPI_RDY

Master Mode with Wait States

Master Mode with SS_CTL[3:0] Control

Master Mode with Phase Control

Typical Slave Mode

Reset

Interrupts

DMA

Byte Order

Initialization

Applications

ECSPI Memory Map/Register Definition

ECSPIx

ECSPIx_RXDATA

ECSPIx_TXDATA

ECSPIx_CONREG

ECSPIx_CONFIGREG

ECSPIx_INTREG

ECSPIx_DMAREG

ECSPIx_STATREG

ECSPIx_PERIODREG

ECSPIx_TESTREG

ECSPIx_MSGDATA

Chapter 21: External Interface Module (EIM)

Overview

Features

Modes of Operation

Asynchronous Mode

Asynchronous Page Read Mode

Multiplexed Address/Data Mode

Burst Clock Mode

Low Power Modes

Boot Mode

External Signals

Other Important Block I/O Signals Internal to the SoC

Clocks

Chip Select Memory Map

Functional Description

Bus Sizing Configuration

8 BIT PORT SUPPORT

MOTOROLA 68000

INTEL 386

EIM Operational Modes

Burst Mode (Synchronous) Memory Operation

Burst Clock Divisor (BCD)

Burst Clock Start (BCS)

Multiplexed Address/Data Mode Support

Mixed Master/Memory Burst Modes Support

AXI (Master) Bus Cycles Support

WAIT_B Signal, RWSC and WWSC bit fields Usage

IPS Register Interface

MRS Set for PSRAM

EIM Access Termination

Error Conditions

DTACK Mode

EIM_GRANT / EIM_BUSY Handshake Description

LPMD / LPACK Handshake Description

Endianness

Strobe Signal Use

Initialization Information

Booting from EIM

Typical Application

Access to Intel Sibley Flash

Intel Sibley Flash Asynchronous Mode Configuration

Intel Sibley Flash Synchronous Mode Configuration

Intel Sibley Flash Utility

Access to MDOC Device

MDOC Device Boot

MDOC Device Asynchronous Mode Configuration

MDOC Device Utility

Access to Micron PSRAM

Micron PSRAM Asynchronous Mode Configuration

Micron PSRAM Synchronous Mode Configuration

Access to Samsung OneNAND

Samsung OneNAND Boot

Samsung OneNAND Asynchronous Mode Configuration

Samsung OneNAND Synchronous Mode Configuration

Samsung OneNAND Utility

Access to Samsung UtRAM

Samsung UtRAM Asynchronous Mode Configuration

Samsung UtRAM Synchronous Mode Configuration

Access to Spansion Flash

Spansion Flash Asynchronous Mode Configuration

Spansion Flash Synchronous Mode Configuration

Spansion Flash Utility

8 bit support

External Bus Timing Diagrams

Asynchronous Read Memory Accesses Timing Diagram

Asynchronous Write Memory Accesses Timing Diagram

Asynchronous Read/Write Memory Accesses Timing Diagram

Asynchronous Read/Write Using RAL, WAL and CSREC

Consecutive Asynchronous Write Memory Accesses Timing Diagram

Consecutive Asynchronous Read Memory Accesses Timing Diagram

Burst (Synchronous Mode) Read Memory Accesses Timing Diagram - BCD=0

Burst (Synchronous Mode) Read Memory Accesses Timing Diagram - BCD=1

Burst (Synchronous Mode) Write Memory Access Timing - BCD=1

Asynchronous Page Mode Access

DTACK Mode - AXI Single Access

DTACK Mode - AXI Single Write Access

DTACK Mode - AXI Burst Access

EIM Memory Map/Register Definition

EIM

EIM_CSnGCR1

EIM_CSnGCR2

EIM_CSnRCR1

EIM_CSnRCR2

EIM_CSnWCR1

EIM_CSnWCR2

EIM_WCR

Chapter 22: 10/100-Mbps Ethernet MAC (ENET)

Introduction

Overview

Features

Ethernet MAC features

IP protocol performance optimization features

IEEE 1588 features

Block diagram

External Signals

Clocks

Memory map/register definition

ENETx

ENETx_EIR

ENETx_EIMR

ENETx_RDAR

ENETx_TDAR

ENETx_ECR

ENETx_MMFR

ENETx_MSCR

ENETx_MIBC

ENETx_RCR

ENETx_TCR

ENETx_PALR

ENETx_PAUR

ENETx_OPD

ENETx_TXIC

ENETx_RXIC

ENETx_IAUR

ENETx_IALR

ENETx_GAUR

ENETx_GALR

ENETx_TFWR

ENETx_RDSR

ENETx_TDSR

ENETx_MRBR

ENETx_RSFL

ENETx_RSEM

ENETx_RAEM

ENETx_RAFL

ENETx_TSEM

ENETx_TAEM

ENETx_TAFL

ENETx_TIPG

ENETx_FTRL

ENETx_TACC

ENETx_RACC

ENETx_RMON_T_DROP

ENETx_RMON_T_PACKETS

ENETx_RMON_T_BC_PKT

ENETx_RMON_T_MC_PKT

ENETx_RMON_T_CRC_ALIGN

ENETx_RMON_T_UNDERSIZE

ENETx_RMON_T_OVERSIZE

ENETx_RMON_T_FRAG

ENETx_RMON_T_JAB

ENETx_RMON_T_COL

ENETx_RMON_T_P64

ENETx_RMON_T_P65TO127

ENETx_RMON_T_P128TO255

ENETx_RMON_T_P256TO511

ENETx_RMON_T_P512TO1023

ENETx_RMON_T_P1024TO2047

ENETx_RMON_T_P_GTE2048

ENETx_RMON_T_OCTETS

ENETx_IEEE_T_DROP

ENETx_IEEE_T_FRAME_OK

ENETx_IEEE_T_1COL

ENETx_IEEE_T_MCOL

ENETx_IEEE_T_DEF

ENETx_IEEE_T_LCOL

ENETx_IEEE_T_EXCOL

ENETx_IEEE_T_MACERR

ENETx_IEEE_T_CSERR

ENETx_IEEE_T_SQE

ENETx_IEEE_T_FDXFC

ENETx_IEEE_T_OCTETS_OK

ENETx_RMON_R_PACKETS

ENETx_RMON_R_BC_PKT

ENETx_RMON_R_MC_PKT

ENETx_RMON_R_CRC_ALIGN

ENETx_RMON_R_UNDERSIZE

ENETx_RMON_R_OVERSIZE

ENETx_RMON_R_FRAG

ENETx_RMON_R_JAB

ENETx_RMON_R_RESVD_0

ENETx_RMON_R_P64

ENETx_RMON_R_P65TO127

ENETx_RMON_R_P128TO255

ENETx_RMON_R_P256TO511

ENETx_RMON_R_P512TO1023

ENETx_RMON_R_P1024TO2047

ENETx_RMON_R_P_GTE2048

ENETx_RMON_R_OCTETS

ENETx_IEEE_R_DROP

ENETx_IEEE_R_FRAME_OK

ENETx_IEEE_R_CRC

ENETx_IEEE_R_ALIGN

ENETx_IEEE_R_MACERR

ENETx_IEEE_R_FDXFC

ENETx_IEEE_R_OCTETS_OK

ENETx_ATCR

ENETx_ATVR

ENETx_ATOFF

ENETx_ATPER

ENETx_ATCOR

ENETx_ATINC

ENETx_ATSTMP

ENETx_TGSR

ENETx_TCSRn

ENETx_TCCRn

Functional description

Ethernet MAC frame formats

Pause Frames

Magic packets

IP and higher layers frame format

Ethernet types

IPv4 datagram format

IPv6 datagram format

Internet Control Message Protocol (ICMP) datagram format

User Datagram Protocol (UDP) datagram format

TCP datagram format

IEEE 1588 message formats

Transport encapsulation

UDP/IP

Native Ethernet (PTPv2)

PTP header

PTPv1 header

PTPv2 header

MAC receive

Collision detection in half-duplex mode

Preamble processing

MAC address check

Unicast address check

Multicast and unicast address resolution

Broadcast address reject

Miss-bit implementation

Frame length/type verification: payload length check

Frame length/type verification: frame length check

VLAN frames processing

Pause frame termination

CRC check

Frame padding removal

MAC transmit

Frame payload padding

MAC address insertion

CRC-32 generation

Inter-packet gap (IPG)

Collision detection and handling — half-duplex operation only

Full-duplex flow control operation

Remote device congestion

Local device/FIFO congestion

Magic packet detection

Sleep mode

Magic packet detection

Wakeup

IP accelerator functions

Checksum calculation

Additional padding processing

32-bit Ethernet payload alignment

Receive processing

Transmit processing

Received frame discard

IPv4 fragments

IPv6 support

Receive processing

Transmit processing

Resets and stop controls

Hardware reset

Soft reset

Hardware freeze

Graceful stop

Graceful transmit stop (GTS)

Graceful receive stop (GRS)

Graceful stop interrupt (GRA)

IEEE 1588 functions

Adjustable timer module

Adjustable timer implementation

Transmit timestamping

Receive timestamping

Time synchronization

Input Capture and Output Compare

Input capture

Output compare

DMA requests

FIFO thresholds

Receive FIFO

Transmit FIFO

Loopback options

Legacy buffer descriptors

Legacy receive buffer descriptor

Legacy transmit buffer descriptor

Enhanced buffer descriptors

Enhanced receive buffer descriptor

Enhanced transmit buffer descriptor

Client FIFO application interface

Data structure description

Data structure examples

Frame status

FIFO protection

Transmit FIFO underflow

Transmit FIFO overflow

Receive FIFO overflow

PHY management interface

MDIO clause 22 frame format

MDIO clause 45 frame format

MDIO clock generation

MDIO operation

Ethernet interfaces

RMII interface

MII Interface — transmit

Transmit with collision — half-duplex

MII interface — receive

Interrupt coalescence

Interrupt coalescence setup

Updating the frame count threshold on-the-fly

Updating the timer threshold on-the-fly

Chapter 23: Electrophoretic Display Controller (EPDC)

Overview

EPDC Block Diagram

External Signals

Programming Model

Assumptions

Register Space (Write/Set/Clear/Toggle)

Interrupts

Interrupt Sources

Enabling/Masking Interrupts

Handling/Clearing Interrupts

Controller Setup

Memory Requirements

Panel Architecture Configuration

TFT Panel Timing Configuration

Source Driver and Pixel Clock Configuration

Initializing the Display

Reset/Clocks and Buffer Preparation

Performing an Initialization Display Update

Update Buffer Analysis Functions

Waveform Mode Selection (AUTOWV)

Panel Interface Generator (Pigeon Mode)

Display Update Programming

Initiating a Display Update

Update Processing and Collisions

Multiple Update Flow

Architectural Clock Gating (Low Power Mode)

Performance Tuning and Considerations

Memory and Bus Bandwidth Requirements

Pixel Latency FIFO

Basic Watermarking Control

Update/Refresh Tuning (VSCAN_HOLDOFF)

System-Level Arbitration Control

EPDC Memory Map/Register Definition

EPDC

EPDC_CTRLn

EPDC_WB_ADDR_TCE

EPDC_WVADDR

EPDC_WB_ADDR

EPDC_RES

EPDC_FORMATn

EPDC_WB_FIELD0

EPDC_WB_FIELD1

EPDC_WB_FIELD2

EPDC_WB_FIELD3

EPDC_FIFOCTRLn

EPDC_UPD_ADDR

EPDC_UPD_STRIDE

EPDC_UPD_CORD

EPDC_UPD_SIZE

EPDC_UPD_CTRLn

EPDC_UPD_FIXEDn

EPDC_TEMP

EPDC_AUTOWV_LUT

EPDC_LUT_STANDBY1n

EPDC_LUT_STANDBY2n

EPDC_TCE_CTRLn

EPDC_TCE_SDCFGn

EPDC_TCE_GDCFGn

EPDC_TCE_HSCAN1n

EPDC_TCE_HSCAN2n

EPDC_TCE_VSCANn

EPDC_TCE_OEn

EPDC_TCE_POLARITYn

EPDC_TCE_TIMING1n

EPDC_TCE_TIMING2n

EPDC_TCE_TIMING3n

EPDC_PIGEON_CTRL0n

EPDC_PIGEON_CTRL1n

EPDC_IRQ_MASK1n

EPDC_IRQ_MASK2n

EPDC_IRQ1n

EPDC_IRQ2n

EPDC_IRQ_MASKn

EPDC_IRQn

EPDC_STATUS_LUTS1n

EPDC_STATUS_LUTS2n

EPDC_STATUS_NEXTLUT

EPDC_STATUS_COL1n

EPDC_STATUS_COL2n

EPDC_STATUSn

EPDC_UPD_COL_CORD

EPDC_UPD_COL_SIZE

EPDC_HIST1_PARAM

EPDC_HIST2_PARAM

EPDC_HIST4_PARAM

EPDC_HIST8_PARAM0

EPDC_HIST8_PARAM1

EPDC_HIST16_PARAM0

EPDC_HIST16_PARAM1

EPDC_HIST16_PARAM2

EPDC_HIST16_PARAM3

EPDC_GPIOn

EPDC_VERSION

EPDC_PIGEON_0_0

EPDC_PIGEON_0_1

EPDC_PIGEON_0_2

EPDC_PIGEON_1_0

EPDC_PIGEON_1_1

EPDC_PIGEON_1_2

EPDC_PIGEON_2_0

EPDC_PIGEON_2_1

EPDC_PIGEON_2_2

EPDC_PIGEON_3_0

EPDC_PIGEON_3_1

EPDC_PIGEON_3_2

EPDC_PIGEON_4_0

EPDC_PIGEON_4_1

EPDC_PIGEON_4_2

EPDC_PIGEON_5_0

EPDC_PIGEON_5_1

EPDC_PIGEON_5_2

EPDC_PIGEON_6_0

EPDC_PIGEON_6_1

EPDC_PIGEON_6_2

EPDC_PIGEON_7_0

EPDC_PIGEON_7_1

EPDC_PIGEON_7_2

EPDC_PIGEON_8_0

EPDC_PIGEON_8_1

EPDC_PIGEON_8_2

EPDC_PIGEON_9_0

EPDC_PIGEON_9_1

EPDC_PIGEON_9_2

EPDC_PIGEON_10_0

EPDC_PIGEON_10_1

EPDC_PIGEON_10_2

EPDC_PIGEON_11_0

EPDC_PIGEON_11_1

EPDC_PIGEON_11_2

EPDC_PIGEON_12_0

EPDC_PIGEON_12_1

EPDC_PIGEON_12_2

EPDC_PIGEON_13_0

EPDC_PIGEON_13_1

EPDC_PIGEON_13_2

EPDC_PIGEON_14_0

EPDC_PIGEON_14_1

EPDC_PIGEON_14_2

EPDC_PIGEON_15_0

EPDC_PIGEON_15_1

EPDC_PIGEON_15_2

EPDC_PIGEON_16_0

EPDC_PIGEON_16_1

EPDC_PIGEON_16_2

Chapter 24: Enhanced Periodic Interrupt Timer (EPIT)

Overview

EPIT features

EPIT modes and operations

External signals

Clocks

Functional Description

Operating modes

Operating in set-and-forget mode

Operating in free-running mode

Operations

Compare Event

Counter Value Overwrite

Low-Power Mode Behavior

Debug Mode Behavior

Initialization/ Application Information

Change of Clock Source

EPIT Memory Map/Register Definition

EPITx

EPITx_CR

EPITx_SR

EPITx_LR

EPITx_CMPR

EPITx_CNR

Chapter 25: Enhanced Serial Audio Interface (ESAI)

Overview

Features

Modes of Operation

Normal/Network/On-Demand Mode Selection

Synchronous/Asynchronous Operating Modes

Frame Sync Selection

Shift Direction Selection

External Signals

Serial Transmit 0 Data Pin

Serial Transmit 1 Data Pin

Serial Transmit 2/Receive 3 Data Pin

Serial Transmit 3/Receive 2 Data Pin

Serial Transmit 4/Receive 1 Data Pin

Serial Transmit 5/Receive 0 Data Pin

Receiver Serial Clock

Transmitter Serial Clock

Frame Sync for Receiver

Frame Sync for Transmitter

High Frequency Clock for Transmitter

High Frequency Clock for Receiver

Serial I/O Flags

Clocks

Functional Description

ESAI After Reset

ESAI Interrupt Requests

ESAI DMA Requests from the FIFOs

ESAI Transmit and Receive Shift Registers

ESAI Transmit Shift Registers

ESAI Receive Shift Registers

Initialization Information

ESAI Initialization

ESAI Initialization Examples

Initializing the ESAI using Personal Reset

Initializing the ESAI Transmitter Section

Initializing the ESAI Receiver Section

ESAI Memory Map/Register Definition

ESAI

ESAI_ETDR

ESAI_ERDR

ESAI_ECR

ESAI_ESR

ESAI_TFCR

ESAI_TFSR

ESAI_RFCR

ESAI_RFSR

ESAI_TXn

ESAI_TSR

ESAI_RXn

ESAI_SAISR

ESAI_SAICR

ESAI_TCR

ESAI_TCCR

ESAI_RCR

ESAI_RCCR

ESAI_TSMA

ESAI_TSMB

ESAI_RSMA

ESAI_RSMB

ESAI_PRRC

ESAI_PCRC

Chapter 26: Flexible Controller Area Network (FLEXCAN)

Overview

Block Diagram

FLEXCAN Module Features

Modes of Operation

External Signals

Clocks

Message Buffer Structure

Rx FIFO Structure

Functional Description

Functional Overview

Transmit Process

Arbitration process

Lowest Mailbox number first

Highest Mailbox priority first

Local Priority disabled

Local Priority enabled

Receive Process

Matching Process

Move Process

Move-in

Move-out

Data Coherence

Transmission Abort Mechanism

Message Buffer Inactivation

Message Buffer Lock Mechanism

Rx FIFO

CAN Protocol Related Features

Remote Frames

Overload Frames

Time Stamp

Protocol Timing

Arbitration and Matching Timing

Modes of Operation Details

Freeze Mode

Module Disable Mode

Stop Mode

Interrupts

Initialization/Application Information

FLEXCAN Initialization Sequence

FLEXCAN Memory Map/Register Definition

FLEXCANx

FLEXCANx_MCR

FLEXCANx_CTRL1

FLEXCANx_TIMER

FLEXCANx_RXMGMASK

FLEXCANx_RX14MASK

FLEXCANx_RX15MASK

FLEXCANx_ECR

FLEXCANx_ESR1

FLEXCANx_IMASK2

FLEXCANx_IMASK1

FLEXCANx_IFLAG2

FLEXCANx_IFLAG1

FLEXCANx_CTRL2

FLEXCANx_ESR2

FLEXCANx_CRCR

FLEXCANx_RXFGMASK

FLEXCANx_RXFIR

FLEXCANx_RXIMRn

FLEXCANx_GFWR

Chapter 27: General Power Controller (GPC)

Overview

Clocks

Power Gating Control (PGC)

Overview

Features

GPC Interrupt Controller (INTC)

Interrupt Controller features

GPC Memory Map/Register Definition

GPC

GPC_CNTR

GPC_PGR

GPC_IMR1

GPC_IMR2

GPC_IMR3

GPC_IMR4

GPC_ISR1

GPC_ISR2

GPC_ISR3

GPC_ISR4

PGC Memory Map/Register Definition

PGC

PGC_MEGA_CTRL

PGC_MEGA_PUPSCR

PGC_MEGA_PDNSCR

PGC_MEGA_SR

PGC_CPU_CTRL

PGC_CPU_PUPSCR

PGC_CPU_PDNSCR

PGC_CPU_SR

Chapter 28: General Purpose Input/Output (GPIO)

Overview

Block Diagram

Features

External Signals

Clocks

GPIO Functional Description

GPIO Function

GPIO pad structure

Input Driver

Schmitt trigger

Input keeper

Output Driver

Drive strength

Output keeper

PU / PD / Keeper Logic

Open drain

GPIO Programming

GPIO Read Mode

GPIO Write Mode

Interrupt Control Unit

GPIO Memory Map/Register Definition

GPIOx

GPIOx_DR

GPIOx_GDIR

GPIOx_PSR

GPIOx_ICR1

GPIOx_ICR2

GPIOx_IMR

GPIOx_ISR

GPIOx_EDGE_SEL

Chapter 29: General Purpose Media Interface (GPMI)

Overview

External Signals

Clocks

GPMI NAND Mode

Multiple NAND Support

GPMI NAND Timing and Clocking

Basic NAND Timing

NAND Asynchronous Timing

NAND Asynchronous EDO Mode Timing

NAND ONFI Source Synchronous Mode Timing

NAND Toggle Mode Timing

Hardware BCH Interface

Behavior During Reset

GPMI Memory Map/Register Definition

GPMI

GPMI_CTRL0n

GPMI_COMPARE

GPMI_ECCCTRLn

GPMI_ECCCOUNT

GPMI_PAYLOAD

GPMI_AUXILIARY

GPMI_CTRL1n

GPMI_TIMING0

GPMI_TIMING1

GPMI_TIMING2

GPMI_DATA

GPMI_STAT

GPMI_DEBUG

GPMI_VERSION

GPMI_DEBUG2

GPMI_DEBUG3

GPMI_READ_DDR_DLL_CTRL

GPMI_WRITE_DDR_DLL_CTRL

GPMI_READ_DDR_DLL_STS

GPMI_WRITE_DDR_DLL_STS

Chapter 30: General Purpose Timer (GPT)

Overview

Features

Modes and Operation

External Signals

External Clock Input

Input Capture Trigger Signals

Output Compare Signals

Clocks

Functional Description

Operating Modes

Restart Mode

Free-Run Mode

Operation

Input Capture

Output Compare

Interrupts

Low Power Mode Behavior

Debug Mode Behavior

Initialization/ Application Information

Selecting the Clock Source

GPT Memory Map/Register Definition

GPTx

GPTx_CR

GPTx_PR

GPTx_SR

GPTx_IR

GPTx_OCR1

GPTx_OCR2

GPTx_OCR3

GPTx_ICR1

GPTx_ICR2

GPTx_CNT

Chapter 31: I2C Controller (I2C)

Overview

Features

Modes and operations

External Signals

Clocks

Functional description

I2C system configuration

Arbitration procedure

Clock synchronization

Handshaking

Clock stretching

Peripheral bus accesses

Generation of transfer error on IP bus

Reset

Interrupts

Byte order

Initialization

Initialization sequence

Generation of Start

Post-transfer software response

Generation of Stop

Generation of Repeated Start

Slave mode

Arbitration lost

Software restriction

I2C Memory Map/Register Definition

I2Cx

I2Cx_IADR

I2Cx_IFDR

I2Cx_I2CR

I2Cx_I2SR

I2Cx_I2DR

Chapter 32: IOMUX Controller (IOMUXC)

Overview

Features

Clocks

Functional description

ALT6 and ALT7 extended muxing modes

SW Loopback through SION bit

Daisy chain - multi pads driving same module input pin

IOMUXC GPR Memory Map/Register Definition

IOMUXC_GPR

IOMUXC_GPR_GPR0

IOMUXC_GPR_GPR1

IOMUXC_GPR_GPR2

IOMUXC_GPR_GPR3

IOMUXC_GPR_GPR4

IOMUXC_GPR_GPR5

IOMUXC_GPR_GPR9

IOMUXC_GPR_GPR10

IOMUXC_GPR_GPR14

IOMUXC SNVS Memory Map/Register Definition

IOMUXC_SNVS

IOMUXC_SNVS_SW_MUX_CTL_PAD_BOOT_MODE0

IOMUXC_SNVS_SW_MUX_CTL_PAD_BOOT_MODE1

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER0

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER1

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER2

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER3

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER4

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER5

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER6

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER7

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER8

IOMUXC_SNVS_SW_MUX_CTL_PAD_SNVS_TAMPER9

IOMUXC_SNVS_SW_PAD_CTL_PAD_TEST_MODE

IOMUXC_SNVS_SW_PAD_CTL_PAD_POR_B

IOMUXC_SNVS_SW_PAD_CTL_PAD_ONOFF

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_PMIC_ON_REQ

IOMUXC_SNVS_SW_PAD_CTL_PAD_CCM_PMIC_STBY_REQ

IOMUXC_SNVS_SW_PAD_CTL_PAD_BOOT_MODE0

IOMUXC_SNVS_SW_PAD_CTL_PAD_BOOT_MODE1

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER0

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER1

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER2

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER3

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER4

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER5

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER6

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER7

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER8

IOMUXC_SNVS_SW_PAD_CTL_PAD_SNVS_TAMPER9

IOMUXC Memory Map/Register Definition

IOMUXC

IOMUXC_SW_MUX_CTL_PAD_JTAG_MOD

IOMUXC_SW_MUX_CTL_PAD_JTAG_TMS

IOMUXC_SW_MUX_CTL_PAD_JTAG_TDO

IOMUXC_SW_MUX_CTL_PAD_JTAG_TDI

IOMUXC_SW_MUX_CTL_PAD_JTAG_TCK

IOMUXC_SW_MUX_CTL_PAD_JTAG_TRST_B

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO01

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO02

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO03

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO04

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO05

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO06

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO07

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO08

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO09

IOMUXC_SW_MUX_CTL_PAD_UART1_TX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART1_RX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART1_CTS_B

IOMUXC_SW_MUX_CTL_PAD_UART1_RTS_B

IOMUXC_SW_MUX_CTL_PAD_UART2_TX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART2_RX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART2_CTS_B

IOMUXC_SW_MUX_CTL_PAD_UART2_RTS_B

IOMUXC_SW_MUX_CTL_PAD_UART3_TX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART3_RX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART3_CTS_B

IOMUXC_SW_MUX_CTL_PAD_UART3_RTS_B

IOMUXC_SW_MUX_CTL_PAD_UART4_TX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART4_RX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART5_TX_DATA

IOMUXC_SW_MUX_CTL_PAD_UART5_RX_DATA

IOMUXC_SW_MUX_CTL_PAD_ENET1_RX_DATA0

IOMUXC_SW_MUX_CTL_PAD_ENET1_RX_DATA1

IOMUXC_SW_MUX_CTL_PAD_ENET1_RX_EN

IOMUXC_SW_MUX_CTL_PAD_ENET1_TX_DATA0

IOMUXC_SW_MUX_CTL_PAD_ENET1_TX_DATA1

IOMUXC_SW_MUX_CTL_PAD_ENET1_TX_EN

IOMUXC_SW_MUX_CTL_PAD_ENET1_TX_CLK

IOMUXC_SW_MUX_CTL_PAD_ENET1_RX_ER

IOMUXC_SW_MUX_CTL_PAD_ENET2_RX_DATA0

IOMUXC_SW_MUX_CTL_PAD_ENET2_RX_DATA1

IOMUXC_SW_MUX_CTL_PAD_ENET2_RX_EN

IOMUXC_SW_MUX_CTL_PAD_ENET2_TX_DATA0

IOMUXC_SW_MUX_CTL_PAD_ENET2_TX_DATA1

IOMUXC_SW_MUX_CTL_PAD_ENET2_TX_EN

IOMUXC_SW_MUX_CTL_PAD_ENET2_TX_CLK

IOMUXC_SW_MUX_CTL_PAD_ENET2_RX_ER

IOMUXC_SW_MUX_CTL_PAD_LCD_CLK

IOMUXC_SW_MUX_CTL_PAD_LCD_ENABLE

IOMUXC_SW_MUX_CTL_PAD_LCD_HSYNC

IOMUXC_SW_MUX_CTL_PAD_LCD_VSYNC

IOMUXC_SW_MUX_CTL_PAD_LCD_RESET

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA00

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA01

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA02

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA03

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA04

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA05

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA06

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA07

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA08

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA09

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA10

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA11

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA12

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA13

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA14

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA15

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA16

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA17

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA18

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA19

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA20

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA21

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA22

IOMUXC_SW_MUX_CTL_PAD_LCD_DATA23

IOMUXC_SW_MUX_CTL_PAD_NAND_RE_B

IOMUXC_SW_MUX_CTL_PAD_NAND_WE_B

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA00

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA01

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA02

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA03

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA04

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA05

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA06

IOMUXC_SW_MUX_CTL_PAD_NAND_DATA07

IOMUXC_SW_MUX_CTL_PAD_NAND_ALE

IOMUXC_SW_MUX_CTL_PAD_NAND_WP_B

IOMUXC_SW_MUX_CTL_PAD_NAND_READY_B

IOMUXC_SW_MUX_CTL_PAD_NAND_CE0_B

IOMUXC_SW_MUX_CTL_PAD_NAND_CE1_B

IOMUXC_SW_MUX_CTL_PAD_NAND_CLE

IOMUXC_SW_MUX_CTL_PAD_NAND_DQS

IOMUXC_SW_MUX_CTL_PAD_SD1_CMD

IOMUXC_SW_MUX_CTL_PAD_SD1_CLK

IOMUXC_SW_MUX_CTL_PAD_SD1_DATA0

IOMUXC_SW_MUX_CTL_PAD_SD1_DATA1

IOMUXC_SW_MUX_CTL_PAD_SD1_DATA2

IOMUXC_SW_MUX_CTL_PAD_SD1_DATA3

IOMUXC_SW_MUX_CTL_PAD_CSI_MCLK

IOMUXC_SW_MUX_CTL_PAD_CSI_PIXCLK

IOMUXC_SW_MUX_CTL_PAD_CSI_VSYNC

IOMUXC_SW_MUX_CTL_PAD_CSI_HSYNC

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA00

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA01

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA02

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA03

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA04

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA05

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA06

IOMUXC_SW_MUX_CTL_PAD_CSI_DATA07

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR00

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR01

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR02

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR03

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR04

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR05

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR06

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR07

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR08

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR09

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR10

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR11

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR12

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR13

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR14

IOMUXC_SW_PAD_CTL_PAD_DRAM_ADDR15

IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM0

IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM1

IOMUXC_SW_PAD_CTL_PAD_DRAM_RAS_B

IOMUXC_SW_PAD_CTL_PAD_DRAM_CAS_B

IOMUXC_SW_PAD_CTL_PAD_DRAM_CS0_B

IOMUXC_SW_PAD_CTL_PAD_DRAM_CS1_B

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDWE_B

IOMUXC_SW_PAD_CTL_PAD_DRAM_ODT0

IOMUXC_SW_PAD_CTL_PAD_DRAM_ODT1

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDBA0

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDBA1

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDBA2

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDCKE0

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDCKE1

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDCLK0_P

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS0_P

IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS1_P

IOMUXC_SW_PAD_CTL_PAD_DRAM_RESET

IOMUXC_SW_PAD_CTL_PAD_JTAG_MOD

IOMUXC_SW_PAD_CTL_PAD_JTAG_TMS

IOMUXC_SW_PAD_CTL_PAD_JTAG_TDO

IOMUXC_SW_PAD_CTL_PAD_JTAG_TDI

IOMUXC_SW_PAD_CTL_PAD_JTAG_TCK

IOMUXC_SW_PAD_CTL_PAD_JTAG_TRST_B

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO01

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO02

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO03

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO04

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO05

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO06

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO07

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO08

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO09

IOMUXC_SW_PAD_CTL_PAD_UART1_TX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART1_RX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART1_CTS_B

IOMUXC_SW_PAD_CTL_PAD_UART1_RTS_B

IOMUXC_SW_PAD_CTL_PAD_UART2_TX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART2_RX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART2_CTS_B

IOMUXC_SW_PAD_CTL_PAD_UART2_RTS_B

IOMUXC_SW_PAD_CTL_PAD_UART3_TX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART3_RX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART3_CTS_B

IOMUXC_SW_PAD_CTL_PAD_UART3_RTS_B

IOMUXC_SW_PAD_CTL_PAD_UART4_TX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART4_RX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART5_TX_DATA

IOMUXC_SW_PAD_CTL_PAD_UART5_RX_DATA

IOMUXC_SW_PAD_CTL_PAD_ENET1_RX_DATA0

IOMUXC_SW_PAD_CTL_PAD_ENET1_RX_DATA1

IOMUXC_SW_PAD_CTL_PAD_ENET1_RX_EN

IOMUXC_SW_PAD_CTL_PAD_ENET1_TX_DATA0

IOMUXC_SW_PAD_CTL_PAD_ENET1_TX_DATA1

IOMUXC_SW_PAD_CTL_PAD_ENET1_TX_EN

IOMUXC_SW_PAD_CTL_PAD_ENET1_TX_CLK

IOMUXC_SW_PAD_CTL_PAD_ENET1_RX_ER

IOMUXC_SW_PAD_CTL_PAD_ENET2_RX_DATA0

IOMUXC_SW_PAD_CTL_PAD_ENET2_RX_DATA1

IOMUXC_SW_PAD_CTL_PAD_ENET2_RX_EN

IOMUXC_SW_PAD_CTL_PAD_ENET2_TX_DATA0

IOMUXC_SW_PAD_CTL_PAD_ENET2_TX_DATA1

IOMUXC_SW_PAD_CTL_PAD_ENET2_TX_EN

IOMUXC_SW_PAD_CTL_PAD_ENET2_TX_CLK

IOMUXC_SW_PAD_CTL_PAD_ENET2_RX_ER

IOMUXC_SW_PAD_CTL_PAD_LCD_CLK

IOMUXC_SW_PAD_CTL_PAD_LCD_ENABLE

IOMUXC_SW_PAD_CTL_PAD_LCD_HSYNC

IOMUXC_SW_PAD_CTL_PAD_LCD_VSYNC

IOMUXC_SW_PAD_CTL_PAD_LCD_RESET

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA00

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA01

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA02

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA03

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA04

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA05

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA06

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA07

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA08

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA09

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA10

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA11

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA12

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA13

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA14

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA15

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA16

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA17

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA18

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA19

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA20

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA21

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA22

IOMUXC_SW_PAD_CTL_PAD_LCD_DATA23

IOMUXC_SW_PAD_CTL_PAD_NAND_RE_B

IOMUXC_SW_PAD_CTL_PAD_NAND_WE_B

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA00

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA01

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA02

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA03

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA04

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA05

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA06

IOMUXC_SW_PAD_CTL_PAD_NAND_DATA07

IOMUXC_SW_PAD_CTL_PAD_NAND_ALE

IOMUXC_SW_PAD_CTL_PAD_NAND_WP_B

IOMUXC_SW_PAD_CTL_PAD_NAND_READY_B

IOMUXC_SW_PAD_CTL_PAD_NAND_CE0_B

IOMUXC_SW_PAD_CTL_PAD_NAND_CE1_B

IOMUXC_SW_PAD_CTL_PAD_NAND_CLE

IOMUXC_SW_PAD_CTL_PAD_NAND_DQS

IOMUXC_SW_PAD_CTL_PAD_SD1_CMD

IOMUXC_SW_PAD_CTL_PAD_SD1_CLK

IOMUXC_SW_PAD_CTL_PAD_SD1_DATA0

IOMUXC_SW_PAD_CTL_PAD_SD1_DATA1

IOMUXC_SW_PAD_CTL_PAD_SD1_DATA2

IOMUXC_SW_PAD_CTL_PAD_SD1_DATA3

IOMUXC_SW_PAD_CTL_PAD_CSI_MCLK

IOMUXC_SW_PAD_CTL_PAD_CSI_PIXCLK

IOMUXC_SW_PAD_CTL_PAD_CSI_VSYNC

IOMUXC_SW_PAD_CTL_PAD_CSI_HSYNC

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA00

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA01

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA02

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA03

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA04

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA05

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA06

IOMUXC_SW_PAD_CTL_PAD_CSI_DATA07

IOMUXC_SW_PAD_CTL_GRP_ADDDS

IOMUXC_SW_PAD_CTL_GRP_DDRMODE_CTL

IOMUXC_SW_PAD_CTL_GRP_B0DS

IOMUXC_SW_PAD_CTL_GRP_DDRPK

IOMUXC_SW_PAD_CTL_GRP_CTLDS

IOMUXC_SW_PAD_CTL_GRP_B1DS

IOMUXC_SW_PAD_CTL_GRP_DDRHYS

IOMUXC_SW_PAD_CTL_GRP_DDRPKE

IOMUXC_SW_PAD_CTL_GRP_DDRMODE

IOMUXC_SW_PAD_CTL_GRP_DDR_TYPE

IOMUXC_ANATOP_USB_OTG_ID_SELECT_INPUT

IOMUXC_USB_OTG2_ID_SELECT_INPUT

IOMUXC_CCM_PMIC_READY_SELECT_INPUT

IOMUXC_CSI_DATA02_SELECT_INPUT

IOMUXC_CSI_DATA03_SELECT_INPUT

IOMUXC_CSI_DATA05_SELECT_INPUT

IOMUXC_CSI_DATA00_SELECT_INPUT

IOMUXC_CSI_DATA01_SELECT_INPUT

IOMUXC_CSI_DATA04_SELECT_INPUT

IOMUXC_CSI_DATA06_SELECT_INPUT

IOMUXC_CSI_DATA07_SELECT_INPUT

IOMUXC_CSI_DATA08_SELECT_INPUT

IOMUXC_CSI_DATA09_SELECT_INPUT

IOMUXC_CSI_DATA10_SELECT_INPUT

IOMUXC_CSI_DATA11_SELECT_INPUT

IOMUXC_CSI_DATA12_SELECT_INPUT

IOMUXC_CSI_DATA13_SELECT_INPUT

IOMUXC_CSI_DATA14_SELECT_INPUT

IOMUXC_CSI_DATA15_SELECT_INPUT

IOMUXC_CSI_DATA16_SELECT_INPUT

IOMUXC_CSI_DATA17_SELECT_INPUT

IOMUXC_CSI_DATA18_SELECT_INPUT

IOMUXC_CSI_DATA19_SELECT_INPUT

IOMUXC_CSI_DATA20_SELECT_INPUT

IOMUXC_CSI_DATA21_SELECT_INPUT

IOMUXC_CSI_DATA22_SELECT_INPUT

IOMUXC_CSI_DATA23_SELECT_INPUT

IOMUXC_CSI_HSYNC_SELECT_INPUT

IOMUXC_CSI_PIXCLK_SELECT_INPUT

IOMUXC_CSI_VSYNC_SELECT_INPUT

IOMUXC_CSI_FIELD_SELECT_INPUT

IOMUXC_ECSPI1_SCLK_SELECT_INPUT

IOMUXC_ECSPI1_MISO_SELECT_INPUT

IOMUXC_ECSPI1_MOSI_SELECT_INPUT

IOMUXC_ECSPI1_SS0_B_SELECT_INPUT

IOMUXC_ECSPI2_SCLK_SELECT_INPUT

IOMUXC_ECSPI2_MISO_SELECT_INPUT

IOMUXC_ECSPI2_MOSI_SELECT_INPUT

IOMUXC_ECSPI2_SS0_B_SELECT_INPUT

IOMUXC_ECSPI3_SCLK_SELECT_INPUT

IOMUXC_ECSPI3_MISO_SELECT_INPUT

IOMUXC_ECSPI3_MOSI_SELECT_INPUT

IOMUXC_ECSPI3_SS0_B_SELECT_INPUT

IOMUXC_ECSPI4_SCLK_SELECT_INPUT

IOMUXC_ECSPI4_MISO_SELECT_INPUT

IOMUXC_ECSPI4_MOSI_SELECT_INPUT

IOMUXC_ECSPI4_SS0_B_SELECT_INPUT

IOMUXC_ENET1_REF_CLK1_SELECT_INPUT

IOMUXC_ENET1_MAC0_MDIO_SELECT_INPUT

IOMUXC_ENET2_REF_CLK2_SELECT_INPUT

IOMUXC_ENET2_MAC0_MDIO_SELECT_INPUT

IOMUXC_FLEXCAN1_RX_SELECT_INPUT

IOMUXC_FLEXCAN2_RX_SELECT_INPUT

IOMUXC_GPT1_CAPTURE1_SELECT_INPUT

IOMUXC_GPT1_CAPTURE2_SELECT_INPUT

IOMUXC_GPT1_CLK_SELECT_INPUT

IOMUXC_GPT2_CAPTURE1_SELECT_INPUT

IOMUXC_GPT2_CAPTURE2_SELECT_INPUT

IOMUXC_GPT2_CLK_SELECT_INPUT

IOMUXC_I2C1_SCL_SELECT_INPUT

IOMUXC_I2C1_SDA_SELECT_INPUT

IOMUXC_I2C2_SCL_SELECT_INPUT

IOMUXC_I2C2_SDA_SELECT_INPUT

IOMUXC_I2C3_SCL_SELECT_INPUT

IOMUXC_I2C3_SDA_SELECT_INPUT

IOMUXC_I2C4_SCL_SELECT_INPUT

IOMUXC_I2C4_SDA_SELECT_INPUT

IOMUXC_KPP_COL0_SELECT_INPUT

IOMUXC_KPP_COL1_SELECT_INPUT

IOMUXC_KPP_COL2_SELECT_INPUT

IOMUXC_KPP_ROW0_SELECT_INPUT

IOMUXC_KPP_ROW1_SELECT_INPUT

IOMUXC_KPP_ROW2_SELECT_INPUT

IOMUXC_LCD_BUSY_SELECT_INPUT

IOMUXC_SAI1_MCLK_SELECT_INPUT

IOMUXC_SAI1_RX_DATA_SELECT_INPUT

IOMUXC_SAI1_TX_BCLK_SELECT_INPUT

IOMUXC_SAI1_TX_SYNC_SELECT_INPUT

IOMUXC_SAI2_MCLK_SELECT_INPUT

IOMUXC_SAI2_RX_DATA_SELECT_INPUT

IOMUXC_SAI2_TX_BCLK_SELECT_INPUT

IOMUXC_SAI2_TX_SYNC_SELECT_INPUT

IOMUXC_SAI3_MCLK_SELECT_INPUT

IOMUXC_SAI3_RX_DATA_SELECT_INPUT

IOMUXC_SAI3_TX_BCLK_SELECT_INPUT

IOMUXC_SAI3_TX_SYNC_SELECT_INPUT

IOMUXC_SDMA_EVENTS0_SELECT_INPUT

IOMUXC_SDMA_EVENTS1_SELECT_INPUT

IOMUXC_SPDIF_IN_SELECT_INPUT

IOMUXC_SPDIF_EXT_CLK_SELECT_INPUT

IOMUXC_UART1_RTS_B_SELECT_INPUT

IOMUXC_UART1_RX_DATA_SELECT_INPUT

IOMUXC_UART2_RTS_B_SELECT_INPUT

IOMUXC_UART2_RX_DATA_SELECT_INPUT

IOMUXC_UART3_RTS_B_SELECT_INPUT

IOMUXC_UART3_RX_DATA_SELECT_INPUT

IOMUXC_UART4_RTS_B_SELECT_INPUT

IOMUXC_UART4_RX_DATA_SELECT_INPUT

IOMUXC_UART5_RTS_B_SELECT_INPUT

IOMUXC_UART5_RX_DATA_SELECT_INPUT

IOMUXC_UART6_RTS_B_SELECT_INPUT

IOMUXC_UART6_RX_DATA_SELECT_INPUT

IOMUXC_UART7_RTS_B_SELECT_INPUT

IOMUXC_UART7_RX_DATA_SELECT_INPUT

IOMUXC_UART8_RTS_B_SELECT_INPUT

IOMUXC_UART8_RX_DATA_SELECT_INPUT

IOMUXC_USB_OTG2_OC_SELECT_INPUT

IOMUXC_USB_OTG_OC_SELECT_INPUT

IOMUXC_USDHC1_CD_B_SELECT_INPUT

IOMUXC_USDHC1_WP_SELECT_INPUT

IOMUXC_USDHC2_CLK_SELECT_INPUT

IOMUXC_USDHC2_CD_B_SELECT_INPUT

IOMUXC_USDHC2_CMD_SELECT_INPUT

IOMUXC_USDHC2_DATA0_SELECT_INPUT

IOMUXC_USDHC2_DATA1_SELECT_INPUT

IOMUXC_USDHC2_DATA2_SELECT_INPUT

IOMUXC_USDHC2_DATA3_SELECT_INPUT

IOMUXC_USDHC2_DATA4_SELECT_INPUT

IOMUXC_USDHC2_DATA5_SELECT_INPUT

IOMUXC_USDHC2_DATA6_SELECT_INPUT

IOMUXC_USDHC2_DATA7_SELECT_INPUT

IOMUXC_USDHC2_WP_SELECT_INPUT

Chapter 33: Keypad Port (KPP)

Overview

Features

Modes and Operations

Clocks

External Signals

Input Pins

Output Pins

Generation of Transfer Error Signal on Peripheral Bus

Functional Description

Keypad Matrix Construction

Keypad Port Configuration

Keypad Matrix Scanning

Keypad Standby

Glitch Suppression on Keypad Inputs

Multiple Key Closures

Ghost Key Problem and Correction

3-Point Contact Keys Support

Initialization/Application Information

Typical Keypad Configuration and Scanning Sequence

Key Press Interrupt Scanning Sequence

Additional Comments

KPP Memory Map/Register Definition

KPP

KPP_KPCR

KPP_KPSR

KPP_KDDR

KPP_KPDR

Chapter 34: Enhanced LCD Interface (eLCDIF)

Overview

External Signals

Clocks

Functional Description

Bus Interface Mechanisms

Bus Master Operation in Write/Display Modes

System Bus Master Performance

Write Data Path

Read Data Path

eLCDIF Interrupts

Initializing the eLCDIF

Write Modes

MPU Read Mode

MPU Interface

Code Example to Initialize the eLCDIF in MPU Write Mode

VSYNC Interface

Code Example to Initialize eLCDIF in VSYNC Mode

DOTCLK Interface

Code Example

CSI HANDSHAKE INTERFACE

Alpha Blending Interface

ITU-R BT.656 Digital Video Interface (DVI)

eLCDIF Pin Usage by Interface Mode

Behavior During Reset

eLCDIF Memory Map/Register Definition

LCDIF

LCDIF_CTRLn

LCDIF_CTRL1n

LCDIF_CTRL2n

LCDIF_TRANSFER_COUNT

LCDIF_CUR_BUF

LCDIF_NEXT_BUF

LCDIF_TIMING

LCDIF_VDCTRL0n

LCDIF_VDCTRL1

LCDIF_VDCTRL2

LCDIF_VDCTRL3

LCDIF_VDCTRL4

LCDIF_DVICTRL0

LCDIF_DVICTRL1

LCDIF_DVICTRL2

LCDIF_DVICTRL3

LCDIF_DVICTRL4

LCDIF_CSC_COEFF0

LCDIF_CSC_COEFF1

LCDIF_CSC_COEFF2

LCDIF_CSC_COEFF3

LCDIF_CSC_COEFF4

LCDIF_CSC_OFFSET

LCDIF_CSC_LIMIT

LCDIF_DATA

LCDIF_BM_ERROR_STAT

LCDIF_CRC_STAT

LCDIF_STAT

LCDIF_THRES

LCDIF_AS_CTRL

LCDIF_AS_BUF

LCDIF_AS_NEXT_BUF

LCDIF_AS_CLRKEYLOW

LCDIF_AS_CLRKEYHIGH

LCDIF_SYNC_DELAY

Chapter 35: Multi Mode DDR Controller (MMDC)

Overview

MMDC feature summary

External Signals

Clocks

Functional Description

Write/Read data flow

Write data flow

Read data flow

MMDC initialization

Configuring the MMDC registers

MMDC Address Space

Address decoding

Chip select settings

Creating 4 Gbyte address space with 2 Gbyte CS density

Creating 2 Gbyte address spaces with 1 Gbyte CS density

Translation of AXI accesses to DDR accessess

Example 1

Example 2

Example 3

Example 4

Example 5

Address mirroring

LPDDR2 and DDR3 pin mux mapping

Power Saving and Clock Frequency Change modes

Power saving general

Self refresh and Frequency change entry/exit

Reset

Hard reset

Warm reset

Software reset

Refresh Scheme

Burst Length options towards DDR

Exclusive accesses handling

AXI Error Handling

Performance

Arbitration and reordering mechanism

Arbitration General

Real time channel mode

Dynamic scoring mode (Arbitration Winning Conditions)

Guarding (aging) mechanism

Prediction mechanism

Special Optimization for accesses towards DDR3

MMDC Debug

Hardware debug monitor

Step By Step (SBS) software monitor

MMDC Profiling

LPDDR2 Refresh Rate Update and Timing Derating

DLL Switching

DLL Off mode

ODT Configuration

Calibration Process

Delay-line

ZQ calibration

ZQ automatic (hardware) calibration process

ZQ automatic Pull-up calibration

ZQ automatic Pull-down calibration

ZQ software calibration process

ZQ calibration commands

Read DQS Gating Calibration

Hardware DQS Gating Calibration

Hardware DQS Calibration with MPR

Hardware DQS Calibration with pre-defined value

SW read DQS gating Calibration

SW read Calibration with MPR

SW read Calibration with pre-defined value

Read Calibration

Hardware (automatic) Read Calibration

Hardware (automatic) Calibration with MPR/DQ Calibration

Hardware (automatic) Calibration with pre-defined value

SW Read Calibration

Calibration with MPR/DQ calibration

Calibration with pre-defined value

Write Calibration

HW (automatic) Write Calibration

SW Write Calibration

Write leveling Calibration

Hardware Write Leveling Calibration

SW Write Leveling Calibration

Write fine tuning

Read fine tuning

ZQ Fine Tuning

Duty cycle adjustment

MMDC Memory Map/Register Definition

MMDC

MMDC_MDCTL

MMDC_MDPDC

MMDC_MDOTC

MMDC_MDCFG0

MMDC_MDCFG1

MMDC_MDCFG2

MMDC_MDMISC

MMDC_MDSCR

MMDC_MDREF

MMDC_MDRWD

MMDC_MDOR

MMDC_MDMRR

MMDC_MDCFG3LP

MMDC_MDMR4

MMDC_MDASP

MMDC_MAARCR

MMDC_MAPSR

MMDC_MAEXIDR0

MMDC_MAEXIDR1

MMDC_MADPCR0

MMDC_MADPCR1

MMDC_MADPSR0

MMDC_MADPSR1

MMDC_MADPSR2

MMDC_MADPSR3

MMDC_MADPSR4

MMDC_MADPSR5

MMDC_MASBS0

MMDC_MASBS1

MMDC_MAGENP

MMDC_MPZQHWCTRL

MMDC_MPZQSWCTRL

MMDC_MPWLGCR

MMDC_MPWLDECTRL0

MMDC_MPWLDECTRL1

MMDC_MPWLDLST

MMDC_MPODTCTRL

MMDC_MPRDDQBY0DL

MMDC_MPRDDQBY1DL

MMDC_MPWRDQBY0DL

MMDC_MPWRDQBY1DL

MMDC_MPWRDQBY2DL

MMDC_MPWRDQBY3DL

MMDC_MPDGCTRL0

MMDC_MPDGCTRL1

MMDC_MPDGDLST0

MMDC_MPRDDLCTL

MMDC_MPRDDLST

MMDC_MPWRDLCTL

MMDC_MPWRDLST

MMDC_MPSDCTRL

MMDC_MPZQLP2CTL

MMDC_MPRDDLHWCTL

MMDC_MPWRDLHWCTL

MMDC_MPRDDLHWST0

MMDC_MPWRDLHWST0

MMDC_MPWLHWERR

MMDC_MPDGHWST0

MMDC_MPDGHWST1

MMDC_MPDGHWST2

MMDC_MPDGHWST3

MMDC_MPPDCMPR1

MMDC_MPPDCMPR2

MMDC_MPSWDAR0

MMDC_MPSWDRDR0

MMDC_MPSWDRDR1

MMDC_MPSWDRDR2

MMDC_MPSWDRDR3

MMDC_MPSWDRDR4

MMDC_MPSWDRDR5

MMDC_MPSWDRDR6

MMDC_MPSWDRDR7

MMDC_MPMUR0

MMDC_MPWRCADL

MMDC_MPDCCR

Chapter 36: Medium Quality Sound (MQS)

Overview

Block Diagram

External Signals

Interface Signals

Programming Considerations

Usage Model

Chapter 37: On-Chip OTP Controller (OCOTP_CTRL)

Overview

Features

Clocks

Top-Level Symbol and Functional Overview

Operation

Shadow Register Reload

Fuse and Shadow Register Read

Fuse and Shadow Register Writes

Write Postamble

Fuse Shadow Memory Footprint

OTP Read/Write Timing Parameters

Hardware Visible Fuses

Behavior During Reset

Secure JTAG control

Fuse Map

OCOTP Memory Map/Register Definition

OCOTP

OCOTP_CTRLn

OCOTP_TIMING

OCOTP_DATA

OCOTP_READ_CTRL

OCOTP_READ_FUSE_DATA

OCOTP_SW_STICKY

OCOTP_SCSn

OCOTP_CRC_ADDR

OCOTP_CRC_VALUE

OCOTP_VERSION

OCOTP_TIMING2

OCOTP_LOCK

OCOTP_CFG0

OCOTP_CFG1

OCOTP_CFG2

OCOTP_CFG3

OCOTP_CFG4

OCOTP_CFG5

OCOTP_CFG6

OCOTP_MEM0

OCOTP_MEM1

OCOTP_MEM2

OCOTP_MEM3

OCOTP_MEM4

OCOTP_ANA0

OCOTP_ANA1

OCOTP_ANA2

OCOTP_OTPMK0

OCOTP_OTPMK1

OCOTP_OTPMK2

OCOTP_OTPMK3

OCOTP_OTPMK4

OCOTP_OTPMK5

OCOTP_OTPMK6

OCOTP_OTPMK7

OCOTP_SRK0

OCOTP_SRK1

OCOTP_SRK2

OCOTP_SRK3

OCOTP_SRK4

OCOTP_SRK5

OCOTP_SRK6

OCOTP_SRK7

OCOTP_SJC_RESP0

OCOTP_SJC_RESP1

OCOTP_MAC0

OCOTP_MAC1

OCOTP_MAC

OCOTP_CRC

OCOTP_GP1

OCOTP_GP2

OCOTP_SW_GP0

OCOTP_SW_GP1

OCOTP_SW_GP2

OCOTP_SW_GP3

OCOTP_SW_GP4

OCOTP_MISC_CONF

OCOTP_FIELD_RETURN

OCOTP_SRK_REVOKE

OCOTP_ROM_PATCH0

OCOTP_ROM_PATCH1

OCOTP_ROM_PATCH2

OCOTP_ROM_PATCH3

OCOTP_ROM_PATCH4

OCOTP_ROM_PATCH5

OCOTP_ROM_PATCH6

OCOTP_ROM_PATCH7

OCOTP_GP3_0

OCOTP_GP3_1

OCOTP_GP3_2

OCOTP_GP3_3

OCOTP_GP4_0

OCOTP_GP4_1

OCOTP_GP4_2

OCOTP_GP4_3

Chapter 38: On-Chip RAM Memory Controller (OCRAM)

Overview

Basic Functions

Read/Write Arbitration

Advanced Features

Read Data Wait State

Read Address Pipeline

Write Data Pipeline

Write Address Pipeline

Programmable Registers

Chapter 39: Power Management Unit (PMU)

Overview

Digital LDO Regulators

Analog LDO Regulators

LDO 1P1

LDO 2P5

Low Power Operation

USB LDO Regulator

SNVS Regulator

PMU Memory Map/Register Definition

PMU

PMU_REG_1P1n

PMU_REG_3P0n

PMU_REG_2P5n

PMU_REG_COREn

PMU_MISC0n

PMU_MISC1n

PMU_MISC2n

PMU_LOWPWR_CTRLn

Chapter 40: Pulse Width Modulation (PWM)

Overview

External Signals

Clocks

Functional Description

Operation

FIFO

Rollover and Compare Event

Low Power Mode Behavior

Debug Mode Behavior

Enable Sequence for the PWM

Disable Sequence for the PWM

PWM Memory Map/Register Definition

PWMx

PWMx_PWMCR

PWMx_PWMSR

PWMx_PWMIR

PWMx_PWMSAR

PWMx_PWMPR

PWMx_PWMCNR

Chapter 41: Pixel Pipeline (PXP)

Overview

Clocks

Top-level architecture

Processing Details

Scaling Operation

Decimation Image Scaling

Bilinear Image Scaling Filter

YUV 4:2:2 Image Scaling

YUV 4:2:0 Image Scaling

RGB/YUV444 Image Scaling

Color Space Conversion (CSC)

CSC1 Operation

YUV versus YCbCr Support

CSC2 operation

Alpha Blending/Color Key

Alpha Blend

Normal Alpha Blend

Porter-Duff Alpha Blend

Color Key

LUT

Lookup Modes

DIRECT_Y8

DIRECT_RGB444

DIRECT_RGB454

CACHE_RGB565

Output Modes

Y8

RGBW4444CFA

CFA Correction

RGB888

Rotation

Output Buffer

Address calculator

Block size selection

Interlaced Video Support

LCDIF Handshake

LCDIF Abort

Theory of Operation

Pixel Handling

Output Buffer Composition

PS Image Processing

Letterboxing

Clipping source images

Color Key Processing

In Place Processing (PS buffer is destination buffer)

Alpha Surface (AS) Processing

Alpha Handling

Color Key Processing (AS_CTRL)

Output Image Processing

Output Image Size

Output Format

Rotation/Flip operations

Queuing PXP transactions

Error Handling

Known PXP Limitations/Issues

Dither Engine Block

Top Level Connections

Dither Engine Design

Pipelined Data Flow

Initialization of Dedicated Memories

Register Configuration Interface

Waveform Engines

Overview

Functionality

PXP Store Engine Block Description

Overview

Top-Level Architecture

Store Engine Design

Input Data Source

Store data shift operation

Data Packing

Data Store Format

Output Format Modes

Limitations

Histogram

Basic Operation

Mask Functionality

Collision use-case Example

PXP Memory Map/Register Definition

PXP

PXP_HW_PXP_CTRLn

PXP_HW_PXP_STATn

PXP_HW_PXP_OUT_CTRLn

PXP_HW_PXP_OUT_BUF

PXP_HW_PXP_OUT_BUF2

PXP_HW_PXP_OUT_PITCH

PXP_HW_PXP_OUT_LRC

PXP_HW_PXP_OUT_PS_ULC

PXP_HW_PXP_OUT_PS_LRC

PXP_HW_PXP_OUT_AS_ULC

PXP_HW_PXP_OUT_AS_LRC

PXP_HW_PXP_PS_CTRLn

PXP_HW_PXP_PS_BUF

PXP_HW_PXP_PS_UBUF

PXP_HW_PXP_PS_VBUF

PXP_HW_PXP_PS_PITCH

PXP_HW_PXP_PS_BACKGROUND_0

PXP_HW_PXP_PS_SCALE

PXP_HW_PXP_PS_OFFSET

PXP_HW_PXP_PS_CLRKEYLOW_0

PXP_HW_PXP_PS_CLRKEYHIGH_0

PXP_HW_PXP_AS_CTRL

PXP_HW_PXP_AS_BUF

PXP_HW_PXP_AS_PITCH

PXP_HW_PXP_AS_CLRKEYLOW_0

PXP_HW_PXP_AS_CLRKEYHIGH_0

PXP_HW_PXP_CSC1_COEF0

PXP_HW_PXP_CSC1_COEF1

PXP_HW_PXP_CSC1_COEF2

PXP_HW_PXP_CSC2_CTRL

PXP_HW_PXP_CSC2_COEF0

PXP_HW_PXP_CSC2_COEF1

PXP_HW_PXP_CSC2_COEF2

PXP_HW_PXP_CSC2_COEF3

PXP_HW_PXP_CSC2_COEF4

PXP_HW_PXP_CSC2_COEF5

PXP_HW_PXP_LUT_CTRL

PXP_HW_PXP_LUT_ADDR

PXP_HW_PXP_LUT_DATA

PXP_HW_PXP_LUT_EXTMEM

PXP_HW_PXP_CFA

PXP_HW_PXP_ALPHA_A_CTRL

PXP_HW_PXP_PS_BACKGROUND_1

PXP_HW_PXP_PS_CLRKEYLOW_1

PXP_HW_PXP_PS_CLRKEYHIGH_1

PXP_HW_PXP_AS_CLRKEYLOW_1

PXP_HW_PXP_AS_CLRKEYHIGH_1

PXP_HW_PXP_CTRL2n

PXP_HW_PXP_POWER_REG0

PXP_HW_PXP_POWER_REG1

PXP_HW_PXP_DATA_PATH_CTRL0n

PXP_HW_PXP_DATA_PATH_CTRL1n

PXP_HW_PXP_INIT_MEM_CTRLn

PXP_HW_PXP_INIT_MEM_DATA

PXP_HW_PXP_INIT_MEM_DATA_HIGH

PXP_HW_PXP_IRQ_MASKn

PXP_HW_PXP_IRQn

PXP_HW_PXP_NEXT_ENn

PXP_HW_PXP_NEXT

PXP_HW_PXP_DEBUGCTRL

PXP_HW_PXP_DEBUG

PXP_HW_PXP_VERSION

PXP_HW_PXP_DITHER_STORE_SIZE_CH0

PXP_HW_PXP_WFB_FETCH_CTRLn

PXP_HW_PXP_WFB_FETCH_BUF1_ADDR

PXP_HW_PXP_WFB_FETCH_BUF1_PITCH

PXP_HW_PXP_WFB_FETCH_BUF1_SIZE

PXP_HW_PXP_WFB_FETCH_BUF2_ADDR

PXP_HW_PXP_WFB_FETCH_BUF2_PITCH

PXP_HW_PXP_WFB_FETCH_BUF2_SIZE

PXP_HW_PXP_WFB_ARRAY_PIXEL0_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL1_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL2_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL3_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL4_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL5_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL6_MASK

PXP_HW_PXP_WFB_ARRAY_PIXEL7_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG0_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG1_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG2_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG3_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG4_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG5_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG6_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG7_MASK

PXP_HW_PXP_WFB_FETCH_BUF1_CORD

PXP_HW_PXP_WFB_FETCH_BUF2_CORD

PXP_HW_PXP_WFB_ARRAY_FLAG8_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG9_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG10_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG11_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG12_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG13_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG14_MASK

PXP_HW_PXP_WFB_ARRAY_FLAG15_MASK

PXP_HW_PXP_WFB_ARRAY_REG0

PXP_HW_PXP_WFB_ARRAY_REG1

PXP_HW_PXP_WFB_ARRAY_REG2

PXP_HW_PXP_WFE_B_STORE_CTRL_CH0n

PXP_HW_PXP_WFE_B_STORE_CTRL_CH1n

PXP_HW_PXP_WFE_B_STORE_STATUS_CH0

PXP_HW_PXP_WFE_B_STORE_STATUS_CH1

PXP_HW_PXP_WFE_B_STORE_SIZE_CH0

PXP_HW_PXP_WFE_B_STORE_SIZE_CH1

PXP_HW_PXP_WFE_B_STORE_PITCH

PXP_HW_PXP_WFE_B_STORE_SHIFT_CTRL_CH0n

PXP_HW_PXP_WFE_B_STORE_SHIFT_CTRL_CH1n

PXP_HW_PXP_WFE_B_STORE_ADDR_0_CH0

PXP_HW_PXP_WFE_B_STORE_ADDR_1_CH0

PXP_HW_PXP_WFE_B_STORE_FILL_DATA_CH0

PXP_HW_PXP_WFE_B_STORE_ADDR_0_CH1

PXP_HW_PXP_WFE_B_STORE_ADDR_1_CH1

PXP_HW_PXP_WFE_B_STORE_D_MASK0_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK0_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK1_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK1_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK2_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK2_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK3_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK3_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK4_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK4_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK5_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK5_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK6_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK6_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK7_H_CH0

PXP_HW_PXP_WFE_B_STORE_D_MASK7_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_SHIFT_L_CH0

PXP_HW_PXP_WFE_B_STORE_D_SHIFT_H_CH0

PXP_HW_PXP_WFE_B_STORE_F_SHIFT_L_CH0

PXP_HW_PXP_WFE_B_STORE_F_SHIFT_H_CH0

PXP_HW_PXP_WFE_B_STORE_F_MASK_L_CH0

PXP_HW_PXP_WFE_B_STORE_F_MASK_H_CH0

PXP_HW_PXP_FETCH_WFE_B_DEBUG

PXP_HW_PXP_DITHER_CTRLn

PXP_HW_PXP_DITHER_FINAL_LUT_DATA0n

PXP_HW_PXP_DITHER_FINAL_LUT_DATA1n

PXP_HW_PXP_DITHER_FINAL_LUT_DATA2n

PXP_HW_PXP_DITHER_FINAL_LUT_DATA3n

PXP_HW_PXP_WFE_B_CTRLn

PXP_HW_PXP_WFE_B_DIMENSIONS

PXP_HW_PXP_WFE_B_OFFSET

PXP_HW_PXP_WFE_B_SW_DATA_REGS

PXP_HW_PXP_WFE_B_SW_FLAG_REGS

PXP_HW_PXP_WFE_B_STAGE1_MUX0n

PXP_HW_PXP_WFE_B_STAGE1_MUX1n

PXP_HW_PXP_WFE_B_STAGE1_MUX2n

PXP_HW_PXP_WFE_B_STAGE1_MUX3n

PXP_HW_PXP_WFE_B_STAGE1_MUX4n

PXP_HW_PXP_WFE_B_STAGE1_MUX5n

PXP_HW_PXP_WFE_B_STAGE1_MUX6n

PXP_HW_PXP_WFE_B_STAGE1_MUX7n

PXP_HW_PXP_WFE_B_STAGE1_MUX8n

PXP_HW_PXP_WFE_B_STAGE2_MUX0n

PXP_HW_PXP_WFE_B_STAGE2_MUX1n

PXP_HW_PXP_WFE_B_STAGE2_MUX2n

PXP_HW_PXP_WFE_B_STAGE2_MUX3n

PXP_HW_PXP_WFE_B_STAGE2_MUX4n

PXP_HW_PXP_WFE_B_STAGE2_MUX5n

PXP_HW_PXP_WFE_B_STAGE2_MUX6n

PXP_HW_PXP_WFE_B_STAGE2_MUX7n

PXP_HW_PXP_WFE_B_STAGE2_MUX8n

PXP_HW_PXP_WFE_B_STAGE2_MUX9n

PXP_HW_PXP_WFE_B_STAGE2_MUX10n

PXP_HW_PXP_WFE_B_STAGE2_MUX11n

PXP_HW_PXP_WFE_B_STAGE2_MUX12n

PXP_HW_PXP_WFE_B_STAGE3_MUX0n

PXP_HW_PXP_WFE_B_STAGE3_MUX1n

PXP_HW_PXP_WFE_B_STAGE3_MUX2n

PXP_HW_PXP_WFE_B_STAGE3_MUX3n

PXP_HW_PXP_WFE_B_STAGE3_MUX4n

PXP_HW_PXP_WFE_B_STAGE3_MUX5n

PXP_HW_PXP_WFE_B_STAGE3_MUX6n

PXP_HW_PXP_WFE_B_STAGE3_MUX7n

PXP_HW_PXP_WFE_B_STAGE3_MUX8n

PXP_HW_PXP_WFE_B_STAGE3_MUX9n

PXP_HW_PXP_WFE_B_STAGE3_MUX10n

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_0

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_1

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_2

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_3

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_4

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_5

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_6

PXP_HW_PXP_WFE_B_STG1_5X8_OUT0_7

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_0

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_1

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_2

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_3

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_4

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_5

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_6

PXP_HW_PXP_WFE_B_STG1_5X8_OUT1_7

PXP_HW_PXP_WFE_B_STAGE1_5X8_MASKS_0

PXP_HW_PXP_WFE_B_STG1_5X1_OUT0

PXP_HW_PXP_WFE_B_STG1_5X1_MASKS

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_0

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_1

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_2

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_3

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_4

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_5

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_6

PXP_HW_PXP_WFE_B_STG1_8X1_OUT0_7

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_0

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_1

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_2

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_3

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_4

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_5

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_6

PXP_HW_PXP_WFE_B_STG1_8X1_OUT1_7

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_0

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_1

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_2

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_3

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_4

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_5

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_6

PXP_HW_PXP_WFE_B_STG1_8X1_OUT2_7

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_0

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_1

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_2

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_3

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_4

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_5

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_6

PXP_HW_PXP_WFE_B_STG1_8X1_OUT3_7

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_0

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_1

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_2

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_3

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_4

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_5

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_6

PXP_HW_PXP_WFE_B_STG1_8X1_OUT4_7

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_0

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_1

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_2

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_3

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_4

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_5

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_6

PXP_HW_PXP_WFE_B_STG2_5X6_OUT0_7

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_0

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_1

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_2

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_3

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_4

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_5

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_6

PXP_HW_PXP_WFE_B_STG2_5X6_OUT1_7

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_0

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_1

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_2

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_3

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_4

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_5

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_6

PXP_HW_PXP_WFE_B_STG2_5X6_OUT2_7

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_0

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_1

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_2

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_3

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_4

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_5

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_6

PXP_HW_PXP_WFE_B_STG2_5X6_OUT3_7

PXP_HW_PXP_WFE_B_STAGE2_5X6_MASKS_0

PXP_HW_PXP_WFE_B_STAGE2_5X6_ADDR_0

PXP_HW_PXP_WFE_B_STG2_5X1_OUT0

PXP_HW_PXP_WFE_B_STG2_5X1_OUT1

PXP_HW_PXP_WFE_B_STG2_5X1_OUT2

PXP_HW_PXP_WFE_B_STG2_5X1_OUT3

PXP_HW_PXP_WFE_B_STG2_5X1_MASKS

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_0

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_1

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_2

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_3

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_4

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_5

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_6

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT0_7

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_0

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_1

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_2

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_3

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_4

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_5

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_6

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT1_7

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_0

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_1

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_2

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_3

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_4

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_5

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_6

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT2_7

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_0

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_1

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_2

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_3

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_4

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_5

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_6

PXP_HW_PXP_WFE_B_STG3_F8X1_OUT3_7

PXP_HW_PXP_WFE_B_STG3_F8X1_MASKS

PXP_HW_PXP_ALU_B_CTRLn

PXP_HW_PXP_ALU_B_BUF_SIZE

PXP_HW_PXP_ALU_B_INST_ENTRY

PXP_HW_PXP_ALU_B_PARAM

PXP_HW_PXP_ALU_B_CONFIG

PXP_HW_PXP_ALU_B_LUT_CONFIGn

PXP_HW_PXP_ALU_B_LUT_DATA0

PXP_HW_PXP_ALU_B_LUT_DATA1

PXP_HW_PXP_ALU_B_DBG

PXP_HW_PXP_HIST_A_CTRL

PXP_HW_PXP_HIST_A_MASK

PXP_HW_PXP_HIST_A_BUF_SIZE

PXP_HW_PXP_HIST_A_TOTAL_PIXEL

PXP_HW_PXP_HIST_A_ACTIVE_AREA_X

PXP_HW_PXP_HIST_A_ACTIVE_AREA_Y

PXP_HW_PXP_HIST_A_RAW_STAT0

PXP_HW_PXP_HIST_A_RAW_STAT1

PXP_HW_PXP_HIST_B_CTRL

PXP_HW_PXP_HIST_B_MASK

PXP_HW_PXP_HIST_B_BUF_SIZE

PXP_HW_PXP_HIST_B_TOTAL_PIXEL

PXP_HW_PXP_HIST_B_ACTIVE_AREA_X

PXP_HW_PXP_HIST_B_ACTIVE_AREA_Y

PXP_HW_PXP_HIST_B_RAW_STAT0

PXP_HW_PXP_HIST_B_RAW_STAT1

PXP_HW_PXP_HIST2_PARAM

PXP_HW_PXP_HIST4_PARAM

PXP_HW_PXP_HIST8_PARAM0

PXP_HW_PXP_HIST8_PARAM1

PXP_HW_PXP_HIST16_PARAM0

PXP_HW_PXP_HIST16_PARAM1

PXP_HW_PXP_HIST16_PARAM2

PXP_HW_PXP_HIST16_PARAM3

PXP_HW_PXP_HIST32_PARAM0