存档资料

成绩:

华东交通大学理工学院

课 程 设 计 报 告 书

所属课程

《电子系统设计》

题

分

目

院

专业班级

学

号

学生姓名

指导教师

自动售货机系统设计

电 信 分 院

赵

巍

2011 年 12 月 31 日

�

华东交通大学理工学院

课程设计任务书

专 业

班 级

姓名

一、课程设计题目

自动售货机系统设计

二、课程设计工作:自 2011 年 12 月 24 日起至 2012 年 1 月 2 日

止。

三、课程设计的内容要求:

设计一个自动售货机,此机能出售 1 元、2 元、5 元、10 元的四种

商品。出售哪种商品可由顾客按动相应的一个按键即可,并同时用数码

管显示出此商品的价格。顾客投币后,按一次确认键,如果投币额不足

时则报警,报警时间 3 秒(可用点阵模拟报警)。如果投币额足够时自

动送出货物(送出的货物用相应不同的指示灯显示来模拟),同时多余

的钱应找回,找回的钱数用数码管显示出来。

学生签名:

2011 年 12 月 24 日

�

华东交通大学理工学院课程设计报告

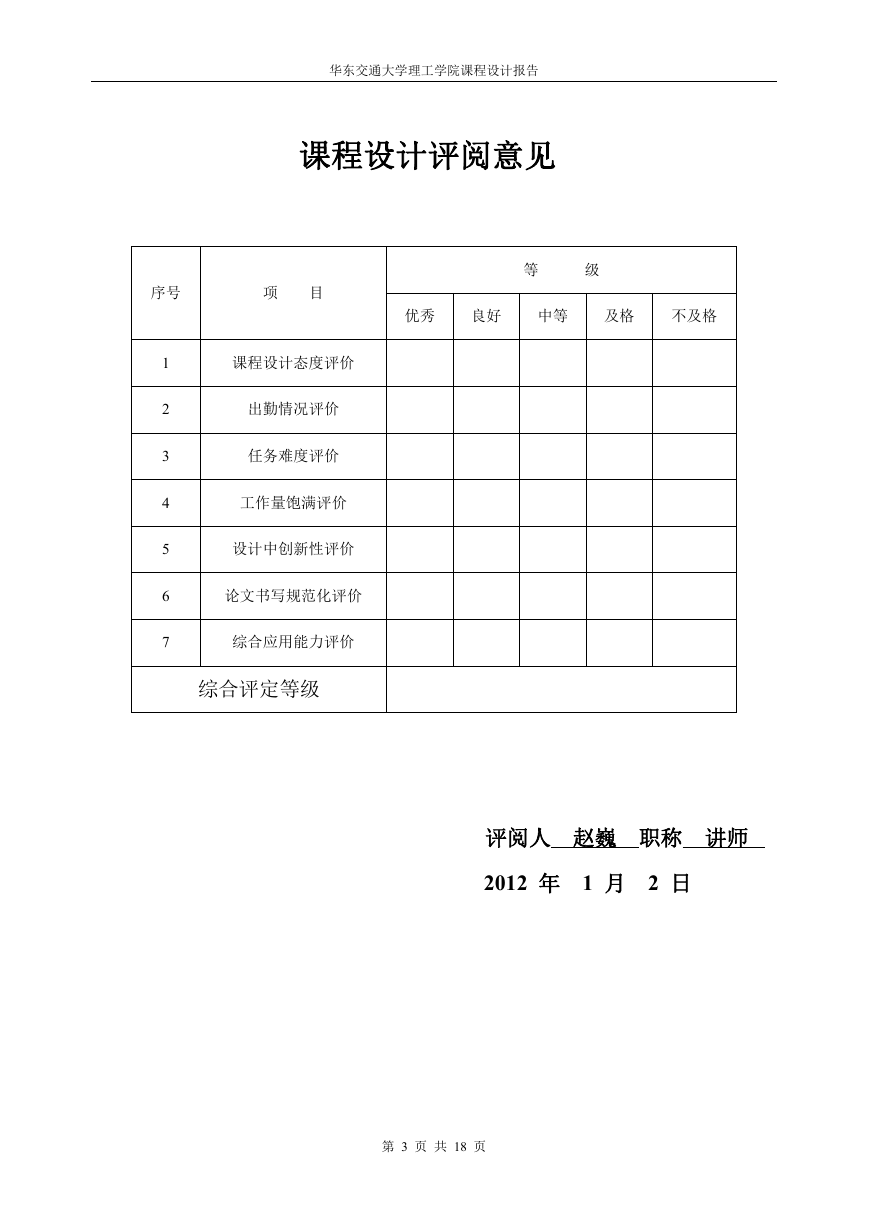

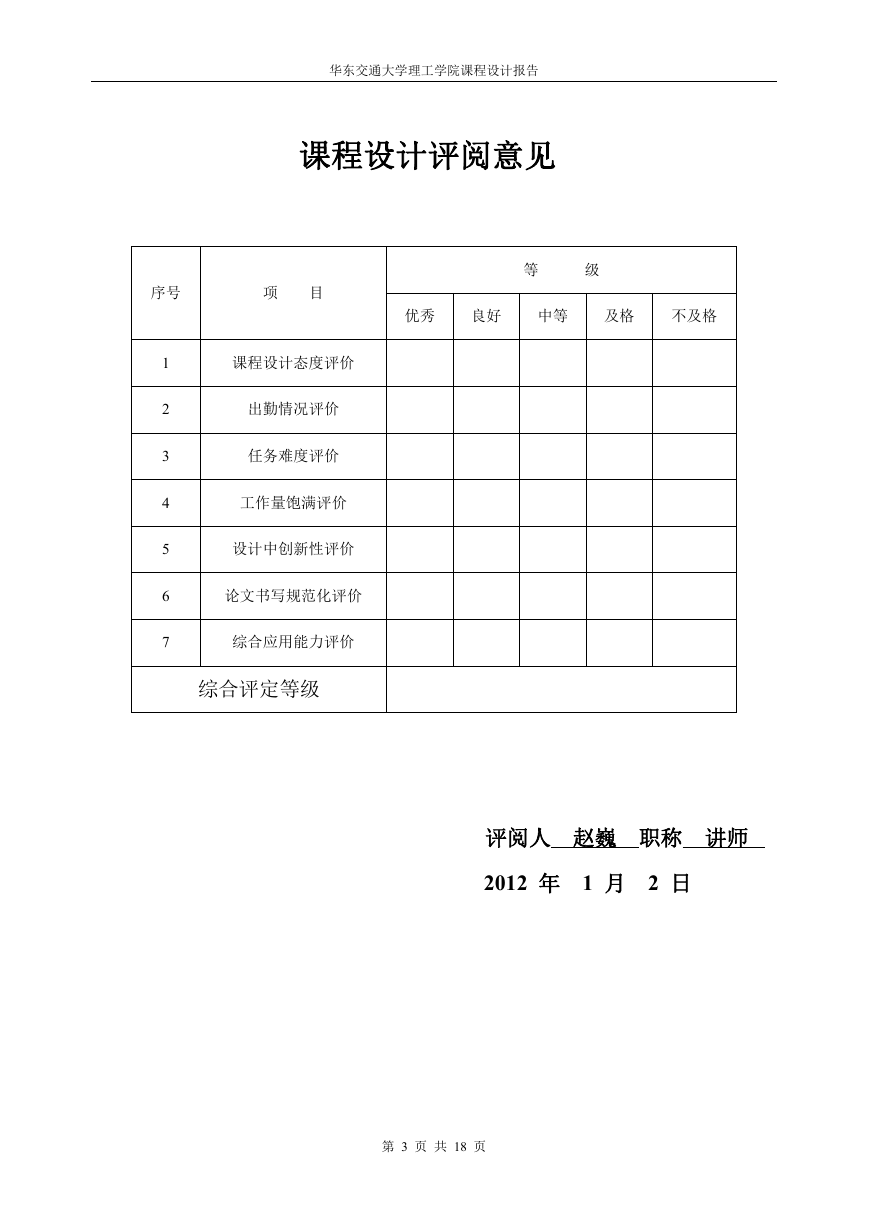

课程设计评阅意见

序号

项

目

等

级

优秀

良好

中等

及格

不及格

1

2

3

4

5

6

7

课程设计态度评价

出勤情况评价

任务难度评价

工作量饱满评价

设计中创新性评价

论文书写规范化评价

综合应用能力评价

综合评定等级

评阅人 赵巍 职称 讲师

2012 年 1 月 2 日

第 3 页 共 18 页

�

华东交通大学理工学院课程设计报告

目 录

第 1 章 课程设计任务书.....................................2

第 2 章 课程设计目的.......................................5

第 3 章 分析与设计.........................................6

3.1 VHDL 简介............................................6

3.2 工作原理..............................................7

第 4 章 系统实施...........................................8

4.1 自动售货机 VHDL 程序..................................8

4.2 各功能部件系统仿真图..................................12

第 5 章 课程设计心得.......................................17

第 6 章 参考文献...........................................18

第 4 页 共 18 页

�

华东交通大学理工学院课程设计报告

第 2 章 课程设计目的

人类社会已进入到高度发达的信息化社会,信息社会的发展离不开电子产品的进步。

现代电子产品在性能提高、复杂度增大的同时,价格却一直呈下降趋势,而且产品更新换

代的步伐也越来越快,实现这种进步的主要原因就是生产制造技术和电子设计技术的发

展。

自动售货是 20 世纪 70 年代在日本、欧美发展起来的一种全新的消费方式,自动售货

机又被称为 24 小时营业的微型自助超市,它的售货领域非常广泛,是发达国家商品零售

的一种主要方式。自动售货机能够根据投入钱币自动收货的机器,是商业自动化的常用设

备。不受时间、地点的限制,能节省人力物力。现代售货机的功能、结构根据商品的种类

而异。货币装置是售货机的核心,其主要功能是确认投入币数及面值,计算余额,找兑余

额。因此,自动售货机在商业,食品业越来越普及,更方便消费者购买自己所需的商品。

使用方便、可靠、节省人力的自动售货机将在社会生活中成为一种趋势。

采用 VHDL 硬件描述语言编程的设计方法设计系统核心电路的硬件程序,与一般的软

件开发不同,VHDL 编程更需要熟悉一些底层的硬件知识,特别是数字逻辑电路的设计,

因此 VHDL 编程的方法、思路都要更多的与硬件电路联系起来。完成系统各个功能模块的

硬件程序设计后,在软件平台上进行编译和电路仿真,最后生成的目标文件下载到实验台

内的 FPGA 芯片以实现该系统,并在实验台上对设计进行验证。

本设计主要实现的功能如下:

1)设计一个自动售货机,此机能出售 1 元、2 元、5 元、10 元的四种商品。出售哪

种商品可有顾客按动相应的一个按键即可,并同时用数码管显示出此商品的价格。

2)顾客投入硬币的钱数也是有 1 元、2 元、5 元、10 元四种,但每次只能投入其中

的一种硬币,此操作通过按动相应的一个按键来模拟,并同时用数码管将投币额显示出来。

3)顾客投币后,按一次确认键,如果投币额不足时则报警,报警时间 3 秒。如果投

币额足够时自动送出货物,同时多余的钱应找回,找回的钱数用数码管显示出来。

4)顾客一旦按动确认键 3 秒后,自动售货机即可自动恢复到初始状态,此时才允许

顾客进行下一次购货操作。

通过这次设计,可以更好的运用所学的知识,加深对数字电子系统这门课的掌握,达

到理论与实践想结合,实现创新的目的。同时了解自动售货机的原理,培养学生严肃认真

的工作作风和严谨踏实的科学态度,以及独立分析和动手解决实际问题的能力。

第 5 页 共 18 页

�

华东交通大学理工学院课程设计报告

第 3 章 分析与设计

3.1 VHDL 简介

VHDL 的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware Description

Language,诞生于 1982 年。1987 年底,VHDL 被 IEEE 和美国国防部确认为标准硬件

描述语言。

VHDL 主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件

特征的语句外,VHDL 的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

VHDL 的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路

模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及

实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发

完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是

VHDL 系统设计的基本点。

VHDL 语言的特点如下:

VHDL 语言能够成为标准化的硬件描述语言并获得广泛应用,它自身必然具有很多

其他硬件描述语言所不具备的优点。归纳起来,VHDL 语言主要具有以下优点:

(1)VHDL 语言功能强大,设计方式多样

VHDL 语言具有强大的语言结构,只需采用简单明确的 VHDL 语言程序就可以描述

十分复杂的硬件电路。同时,它还具有多层次的电路设计描述功能。此外,VHDL 语言

能够同时支持同步电路、异步电路和随机电路的设计实现,这是其他硬件描述语言所不能

比拟的。VHDL 语言设计方法灵活多样,既支持自顶向下的设计方式,也支持自底向上

的设计方法; 既支持模块化设计方法,也支持层次化设计方法。

(2)VHDL 语言具有强大的硬件描述能力

VHDL 语言具有多层次的电路设计描述功能,既可描述系统级电路,也可以描述门

级电路;描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三者

的混合描述方式。同时,VHDL 语言也支持惯性延迟和传输延迟,这样可以准确地建立

硬件电路的模型。VHDL 语言的强大描述能力还体现在它具有丰富的数据类型。VHDL

语言既支持标准定义的数据类型,也支持用户定义的数据类型,这样便会给硬件描述带来

较大的自由度。

(3)VHDL 语言具有很强的移植能力

第 6 页 共 18 页

�

华东交通大学理工学院课程设计报告

VHDL 语言很强的移植能力主要体现在:对于同一个硬件电路的 VHDL 语言描述,

它可以从一个模拟器移植到另一个模拟器上、从一个综合器移植到另一个综合器上或者从

一个工作平台移植到另一个工作平台上去执行。

(4)VHDL 语言的设计描述与器件无关

采用 VHDL 语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器件。

这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他的问

题。当硬件电路的设计描述完成以后,VHDL 语言允许采用多种不同的器件结构来实现。

(5)VHDL 语言程序易于共享和复用

VHDL 语言采用基于库(library)的设计方法。在设计过程中,设计人员可以建立各种

可再次利用的模块,一个大规模的硬件电路的设计不可能从门级电路开始一步步地进行设

计,而是一些模块的累加。这些模块可以预先设计或者使用以前设计中的存档模块,将这

些模块存放在库中,就可以在以后的设计中进行复用。

由于 VHDL 语言是一种描述、模拟、综合、优化和布线的标准硬件描述语言,因此

它可以使设计成果在设计人员之间方便地进行交流和共享,从而减小硬件电路设计的工作

量,缩短开发周期。

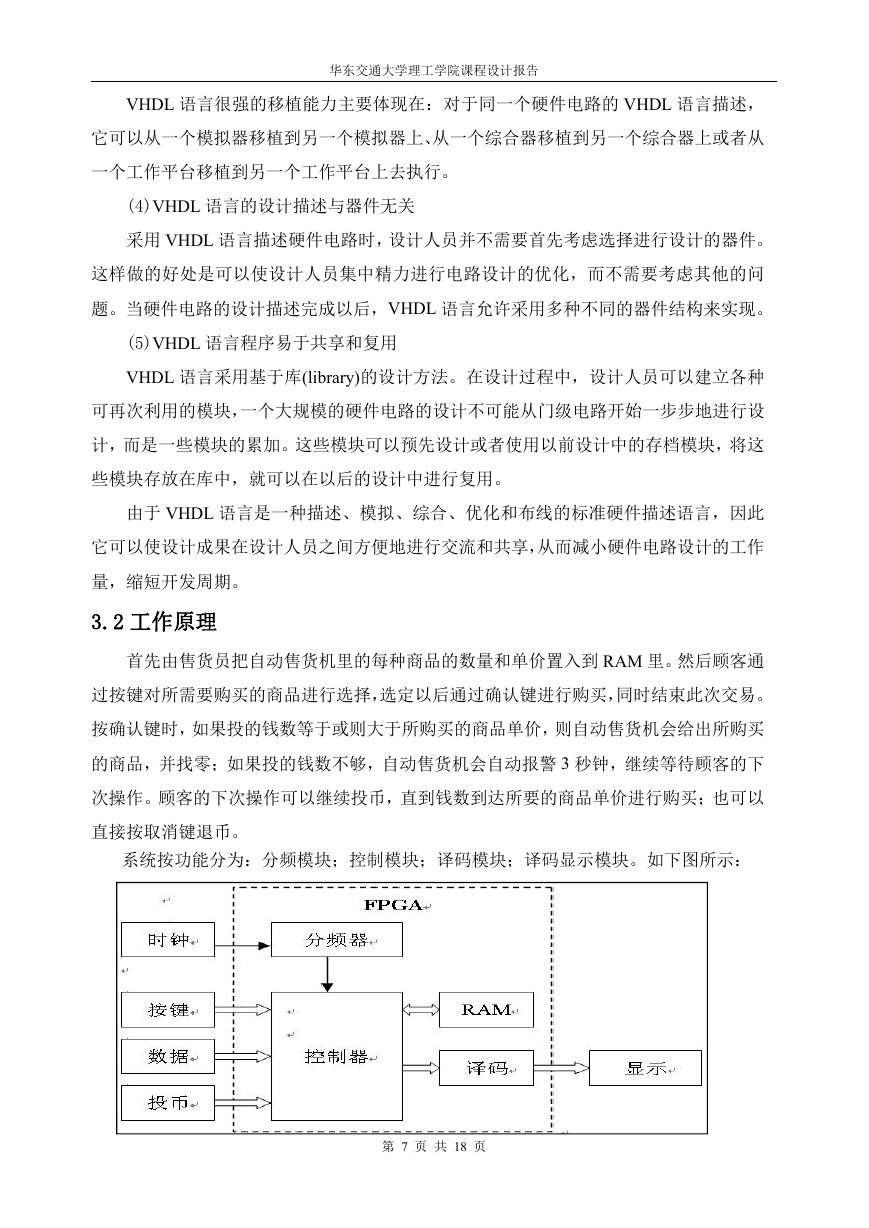

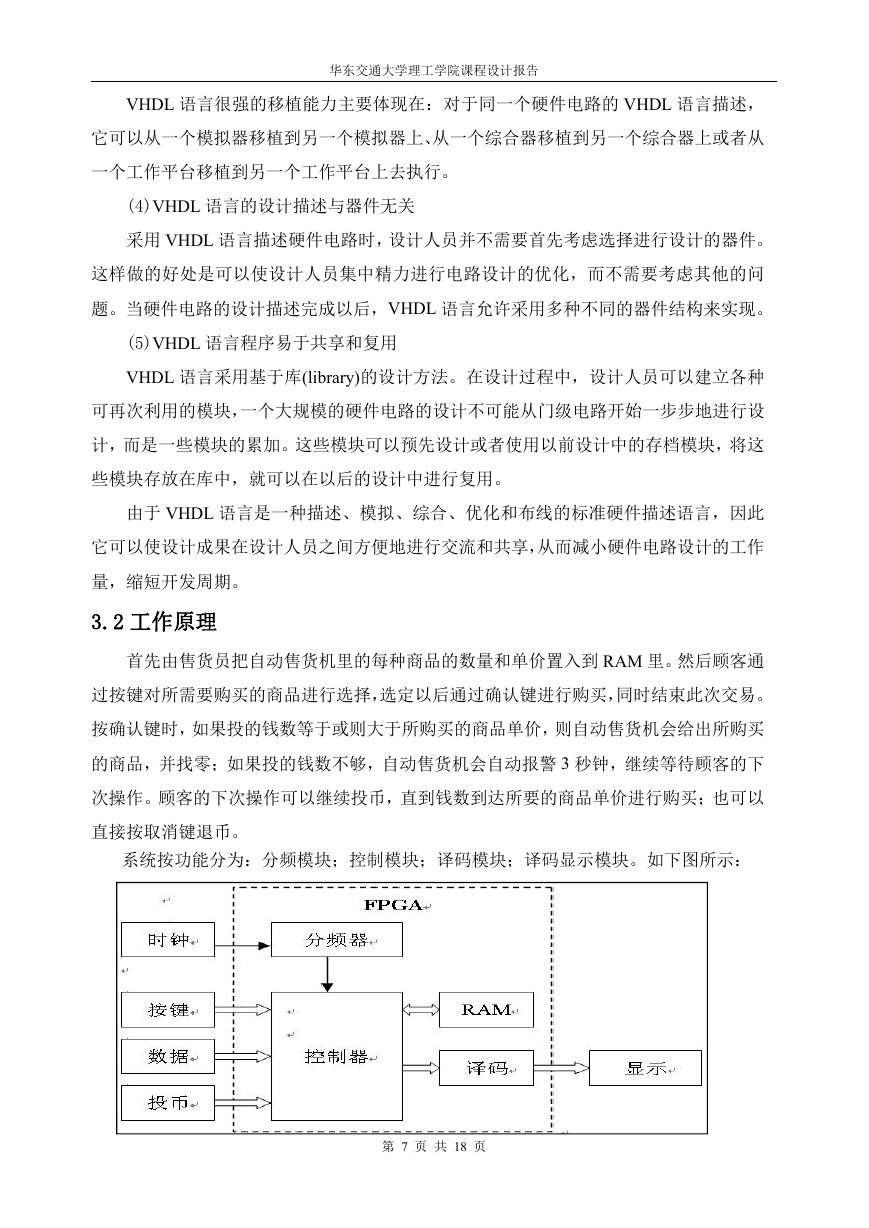

3.2 工作原理

首先由售货员把自动售货机里的每种商品的数量和单价置入到 RAM 里。然后顾客通

过按键对所需要购买的商品进行选择,选定以后通过确认键进行购买,同时结束此次交易。

按确认键时,如果投的钱数等于或则大于所购买的商品单价,则自动售货机会给出所购买

的商品,并找零;如果投的钱数不够,自动售货机会自动报警 3 秒钟,继续等待顾客的下

次操作。顾客的下次操作可以继续投币,直到钱数到达所要的商品单价进行购买;也可以

直接按取消键退币。

系统按功能分为:分频模块;控制模块;译码模块;译码显示模块。如下图所示:

第 7 页 共 18 页

�

华东交通大学理工学院课程设计报告

第 4 章 系统实施

4.1 自动售货机 VHDL 程序

--文件名:AUTO.vhd。

--功能:硬币处理,余额计算,输出商品。

--系统时钟

--设定、买、选择、完成信号

--5 角硬币、1 元硬币

:in std_logic_vector(3 downto 0); --价格、数量数据

--显示、开关信号

--钱数、商品数量显示数据

--1 元硬币、5 角硬币

--说明:显示的钱数 coin 的以 5 角为单位。

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity AUTO is

port ( clk:in std_logic;

set,get,sel,finish: in std_logic;

coin0,coin1: in std_logic;

price,quantity

item0 , act:out std_logic_vector(3 downto 0);

y0,y1 :out std_logic_vector(6 downto 0);

act10,act5

end AUTO;

:out std_logic);

architecture behav of AUTO is

type

signal ram :ram_type;

signal item: std_logic_vector(1 downto 0);

signal coin: std_logic_vector(3 downto 0);

signal pri,qua:std_logic_vector(3 downto 0);

signal clk1: std_logic;

begin

com:process(set,clk1)

variable quan:std_logic_vector(3 downto 0);

第 8 页 共 18 页

ram_type is array(3 downto 0)of std_logic_vector(7 downto 0);

--定义 RAM

--商品种类

--币数计数器

--商品单价、数量

--控制系统的时钟信号

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc