THE DESIGNER’S GUIDE TO VERILOG-AMS

�

THE DESIGNER’S GUIDE BOOK SERIES

Consulting Editor

Kenneth S. Kundert

Books in the series:

The Designer’s Guide to Verilog-AMS

ISBN: 1-4020-8044-1

The Designer’s Guide to SPICE AND Spectre®

ISBN: 0-7923-9571-9

�

THE DESIGNER’S GUIDE TO VERILOG-AMS

First Edition

June 2004

KENNETH S. KUNDERT

Cadence Design Systems

OLAF ZINKE

Cadence Design Systems

KLUWER ACADEMIC PUBLISHERS

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

�

eBook ISBN:

Print ISBN:

1-4020-8045-X

1-4020-8044-1

©2004 Kluwer Academic Publishers

New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers

Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic,

mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at:

and Kluwer's eBookstore at:

http://kluweronline.com

http://ebooks.kluweronline.com

�

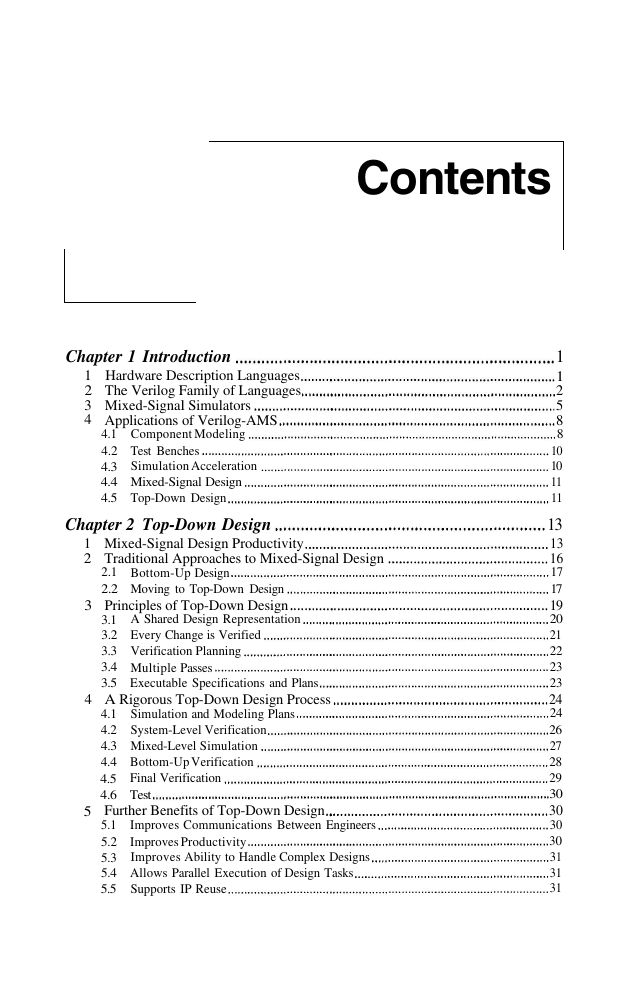

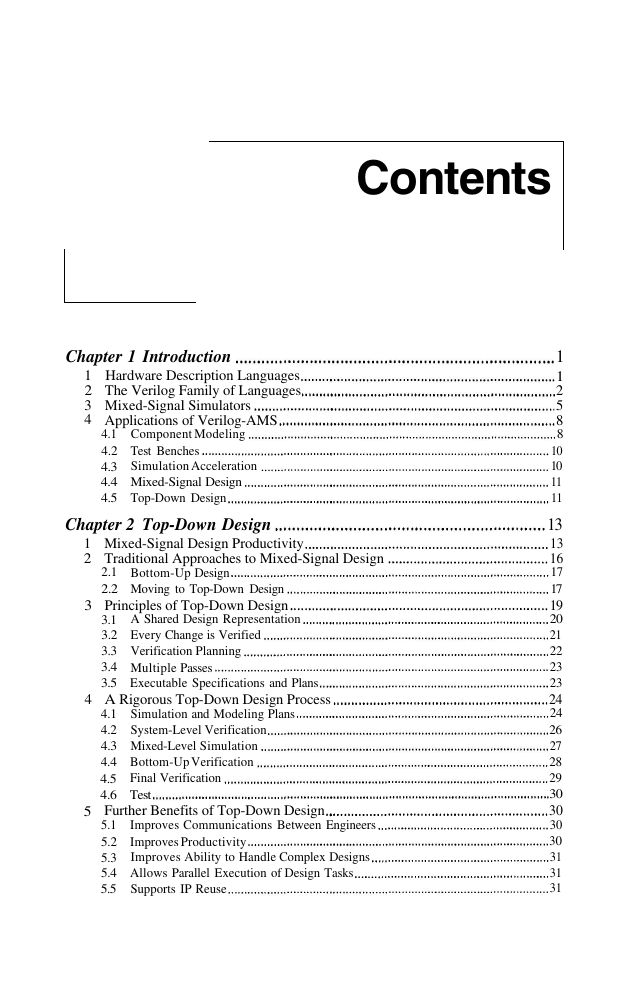

Contents

Chapter 1 Introduction

1

2

3

4

Hardware Description Languages

The Verilog Family of Languages

Mixed-Signal Simulators

Applications of Verilog-AMS

4.1

4.2

4.3

4.4

4.5

Component Modeling

Test Benches

Simulation Acceleration

Mixed-Signal Design

Top-Down Design

Chapter 2 Top-Down Design

1

2

3

4

5

A Shared Design Representation

Every Change is Verified

Verification Planning

Multiple Passes

Executable Specifications and Plans

Simulation and Modeling Plans

System-Level Verification

Mixed-Level Simulation

Bottom-Up Verification

Final Verification

Test

Mixed-Signal Design Productivity

Traditional Approaches to Mixed-Signal Design

2.1

Bottom-Up Design

Moving to Top-Down Design

2.2

Principles of Top-Down Design

3.1

3.2

3.3

3.4

3.5

A Rigorous Top-Down Design Process

4.1

4.2

4.3

4.4

4.5

4.6

Further Benefits of Top-Down Design

5.1

5.2

5.3

5.4

5.5

Improves Communications Between Engineers

Improves Productivity

Improves Ability to Handle Complex Designs

Allows Parallel Execution of Design Tasks

Supports IP Reuse

1

1

2

5

8

8

10

10

11

11

13

13

16

17

17

19

20

21

22

23

23

24

24

26

27

28

29

30

30

30

30

31

31

31

�

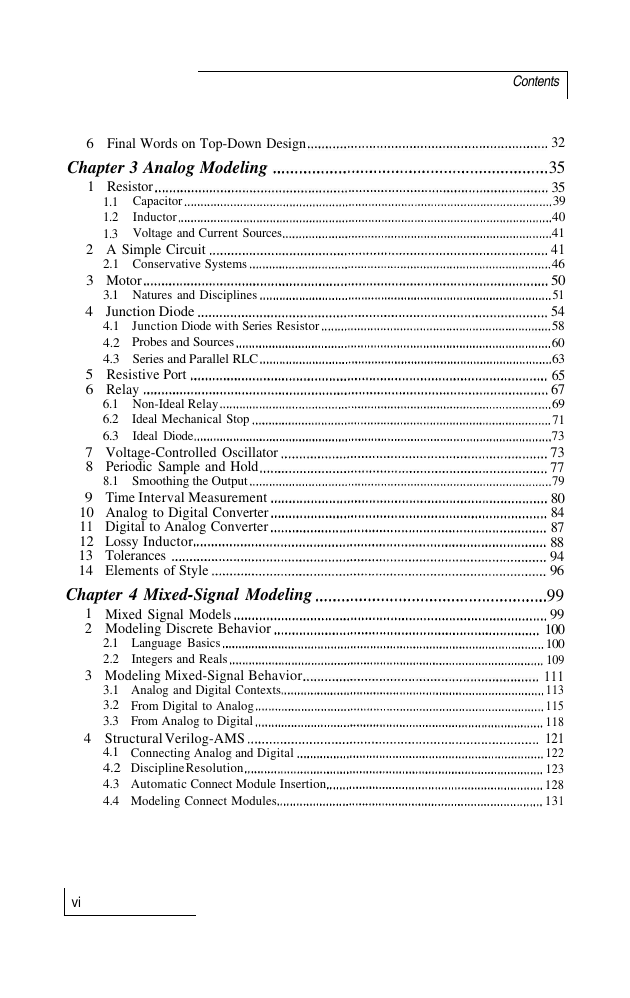

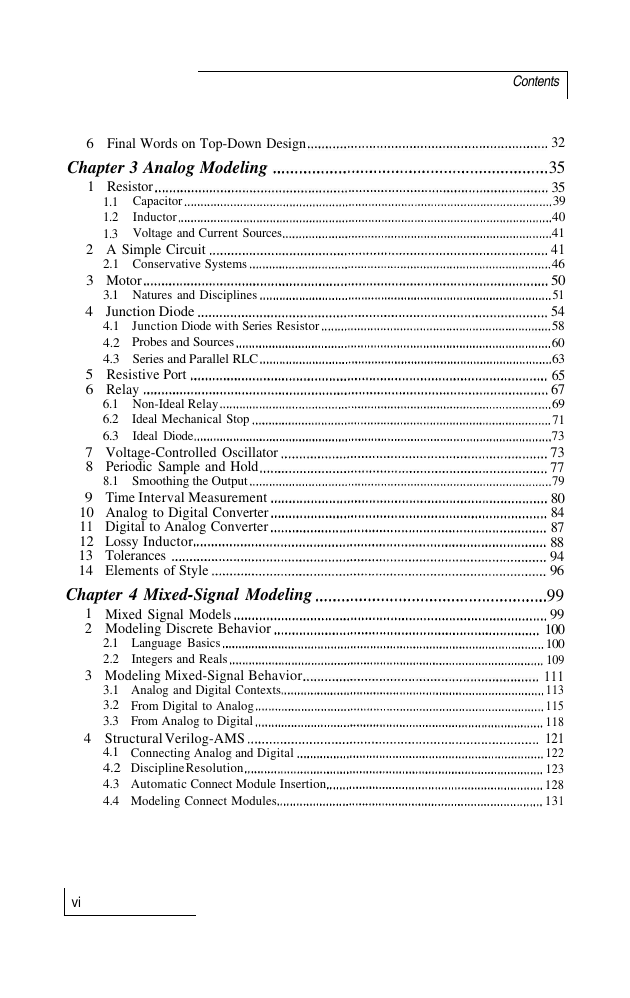

Contents

32

35

35

39

40

41

41

46

50

51

54

58

60

63

65

67

69

71

73

73

77

79

80

84

87

88

94

96

99

99

100

100

109

111

113

115

118

121

122

123

128

131

6 Final Words on Top-Down Design

Chapter 3 Analog Modeling

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Conservative Systems

Natures and Disciplines

Junction Diode with Series Resistor

Probes and Sources

Series and Parallel RLC

Capacitor

Inductor

Voltage and Current Sources

Resistor

1.1

1.2

1.3

A Simple Circuit

2.1

Motor

3.1

Junction Diode

4.1

4.2

4.3

Resistive Port

Relay

6.1

6.2

6.3

Voltage-Controlled Oscillator

Periodic Sample and Hold

8.1

Time Interval Measurement

Analog to Digital Converter

Digital to Analog Converter

Lossy Inductor

Tolerances

Elements of Style

Non-Ideal Relay

Ideal Mechanical Stop

Ideal Diode

Smoothing the Output

Chapter 4 Mixed-Signal Modeling

Language Basics

Integers and Reals

Mixed Signal Models

Modeling Discrete Behavior

2.1

2.2

Modeling Mixed-Signal Behavior

3.1

3.2

3.3

Structural Verilog-AMS

4.1

4.2

4.3

4.4

Connecting Analog and Digital

Discipline Resolution

Automatic Connect Module Insertion

Modeling Connect Modules

Analog and Digital Contexts

From Digital to Analog

From Analog to Digital

1

2

3

4

vi

�

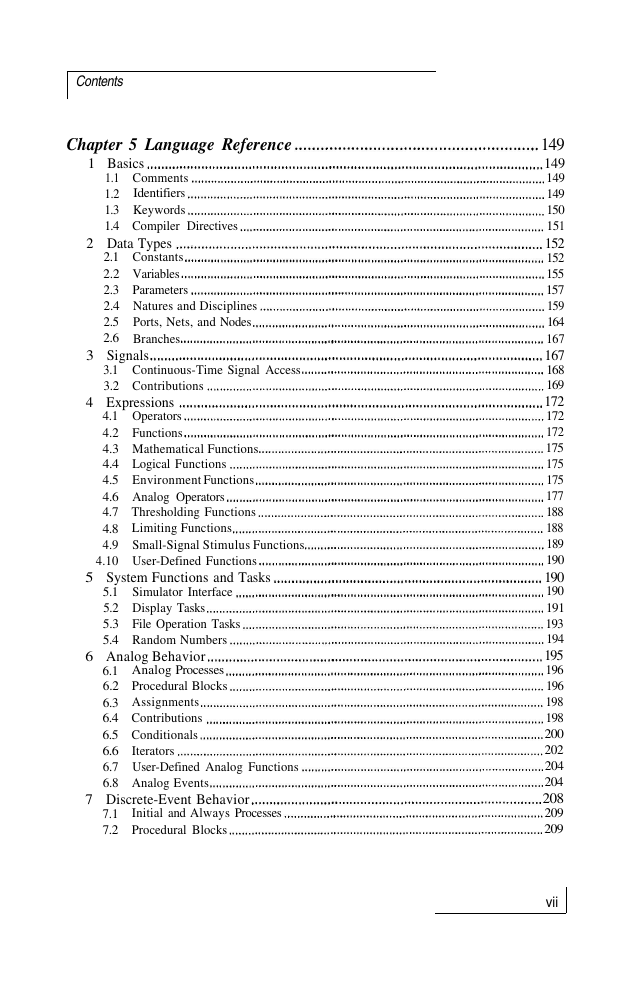

Contents

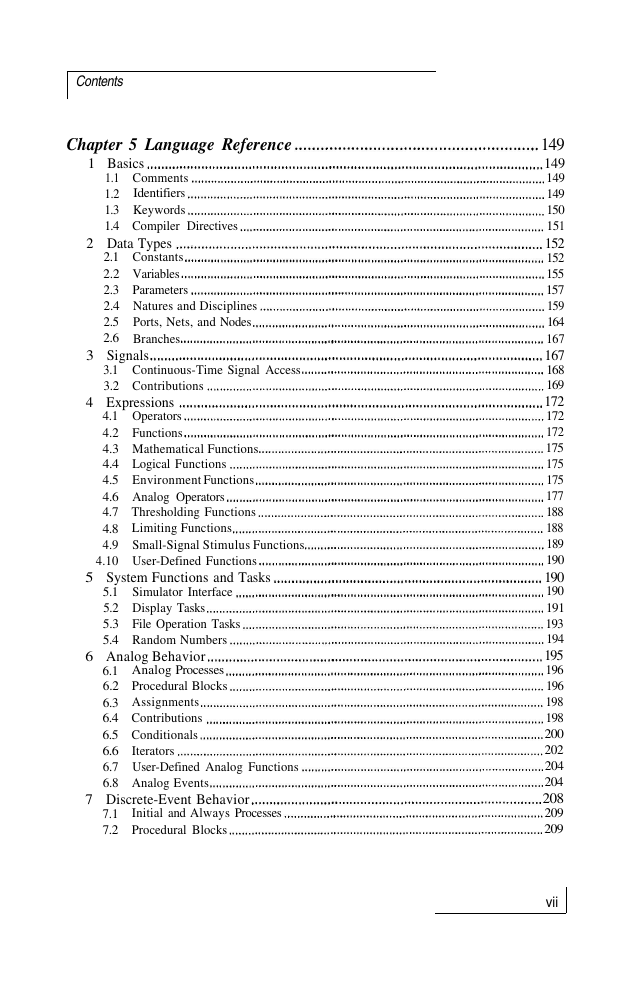

Chapter 5 Language Reference

1 Basics

Comments

Identifiers

Keywords

Compiler Directives

Constants

Variables

Parameters

Natures and Disciplines

Ports, Nets, and Nodes

Branches

1.1

1.2

1.3

1.4

Data Types

2.1

2.2

2.3

2.4

2.5

2.6

Signals

3.1

3.2

Expressions

Operators

4.1

Functions

4.2

Mathematical Functions

4.3

Logical Functions

4.4

Environment Functions

4.5

Analog Operators

4.6

Thresholding Functions

4.7

Limiting Functions

4.8

Small-Signal Stimulus Functions

4.9

4.10

User-Defined Functions

Continuous-Time Signal Access

Contributions

2

3

4

5

6

7

Simulator Interface

Display Tasks

File Operation Tasks

Random Numbers

System Functions and Tasks

5.1

5.2

5.3

5.4

Analog Behavior

6.1

6.2

6.3

6.4

6.5

6.6

6.7

6.8

Discrete-Event Behavior

7.1

7.2

Analog Processes

Procedural Blocks

Assignments

Contributions

Conditionals

Iterators

User-Defined Analog Functions

Analog Events

Initial and Always Processes

Procedural Blocks

149

149

149

149

150

151

152

152

155

157

159

164

167

167

168

169

172

172

172

175

175

175

177

188

188

189

190

190

190

191

193

194

195

196

196

198

198

200

202

204

204

208

209

209

vii

�

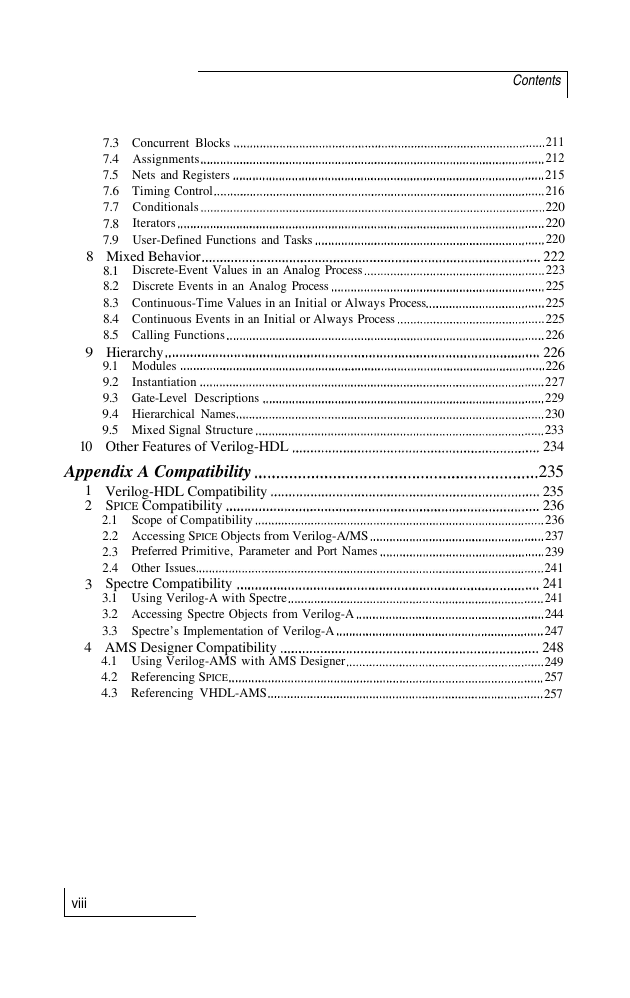

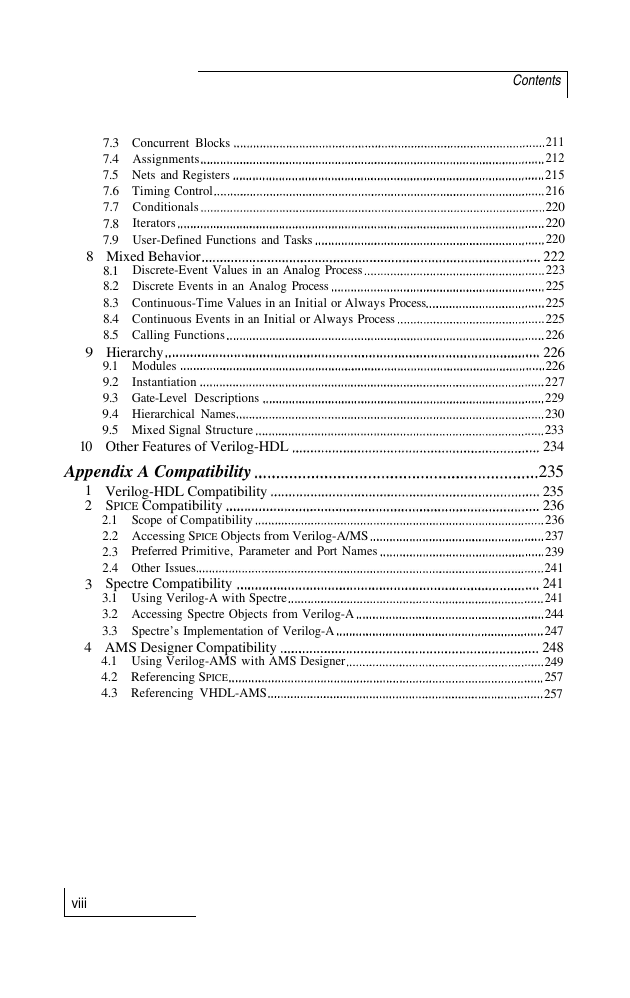

Contents

211

212

215

216

220

220

220

222

223

225

225

225

226

226

226

227

229

230

233

234

235

235

236

236

237

239

241

241

241

244

247

248

249

257

257

Concurrent Blocks

Assignments

Nets and Registers

Timing Control

Conditionals

Iterators

User-Defined Functions and Tasks

7.3

7.4

7.5

7.6

7.7

7.8

7.9

Mixed Behavior

8.1

8.2

8.3

8.4

8.5

Hierarchy

9.1

9.2

9.3

9.4

9.5

Other Features of Verilog-HDL

Modules

Instantiation

Gate-Level Descriptions

Hierarchical Names

Mixed Signal Structure

Discrete-Event Values in an Analog Process

Discrete Events in an Analog Process

Continuous-Time Values in an Initial or Always Process

Continuous Events in an Initial or Always Process

Calling Functions

Appendix A Compatibility

8

9

10

1

2

3

4

viii

Scope of Compatibility

Accessing SPICE Objects from Verilog-A/MS

Preferred Primitive, Parameter and Port Names

Other Issues

Verilog-HDL Compatibility

SPICE Compatibility

2.1

2.2

2.3

2.4

Spectre Compatibility

3.1

3.2

3.3

AMS Designer Compatibility

4.1

4.2

4.3

Using Verilog-A with Spectre

Accessing Spectre Objects from Verilog-A

Spectre’s Implementation of Verilog-A

Using Verilog-AMS with AMS Designer

Referencing SPICE

Referencing VHDL-AMS

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc