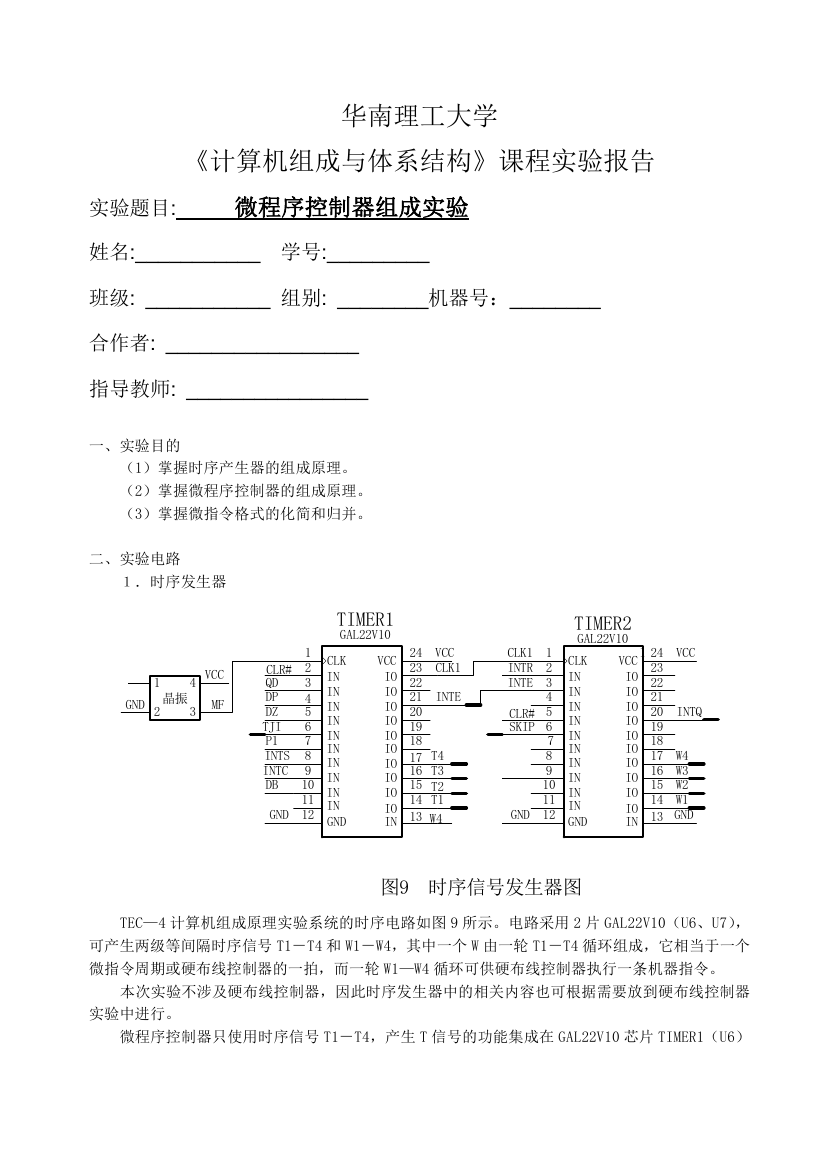

华南理工大学

《计算机组成与体系结构》课程实验报告

实验题目:

微程序控制器组成实验

姓名:___________ 学号:_________

班级: ___________ 组别: ________机器号:________

合作者: _________________

指导教师: ________________

一、实验目的

(1)掌握时序产生器的组成原理。

(2)掌握微程序控制器的组成原理。

(3)掌握微指令格式的化简和归并。

二、实验电路

1.时序发生器

1

2

晶振

VCC

MF

4

3

GND

TIMER1

GAL22V10

1

2

3

4

5

6

7

8

9

10

11

12

CLR#

QD

DP

DZ

TJI

P1

INTS

INTC

DB

GND

CLK

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

GND

24

23

22

21

20

19

18

17

16

15

14

13

VCC

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IN

VCC

CLK1

INTE

T4

T3

T2

T1

W4

TIMER2

GAL22V10

CLK

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

GND

1

VCC

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IN

24

23

22

21

20

19

18

17

16

15

14

13

VCC

INTQ

W4

W3

W2

W1

GND

CLR#

SKIP

CLK1 1

INTR

2

3

INTE

4

5

6

7

8

9

10

11

12

GND

图9 时序信号发生器图

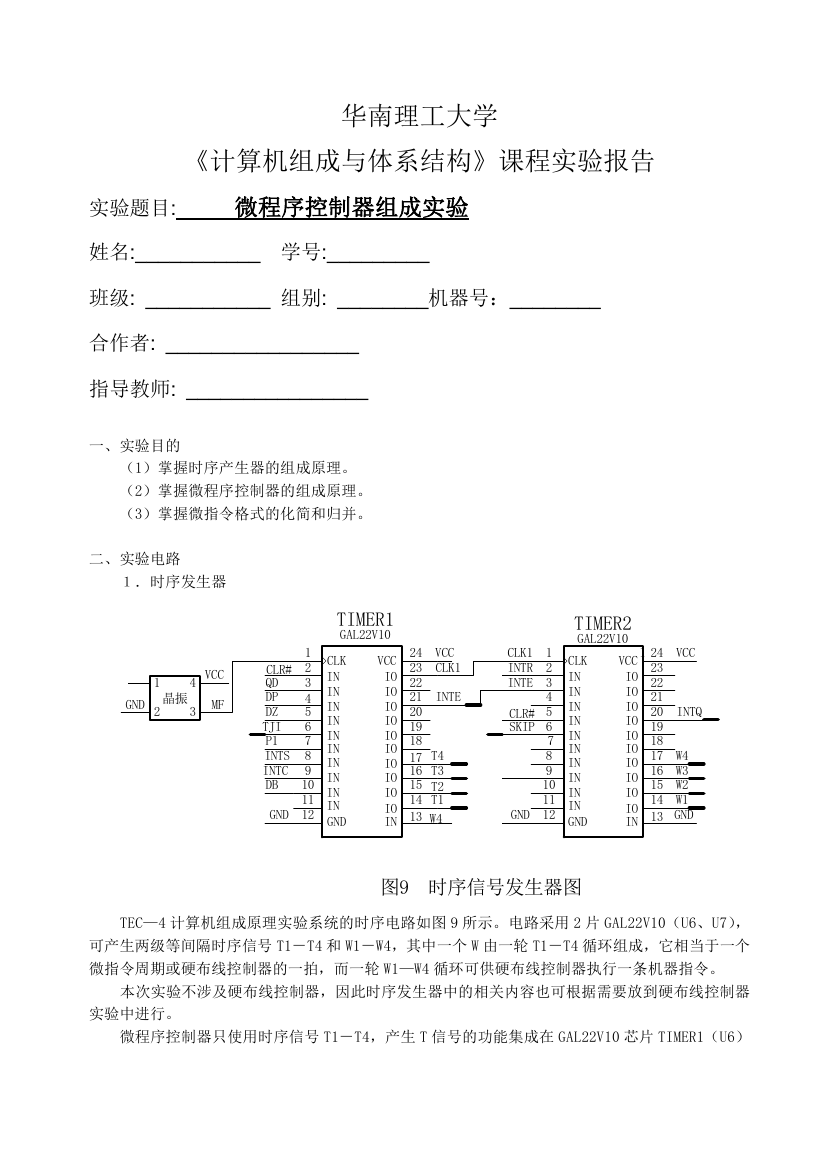

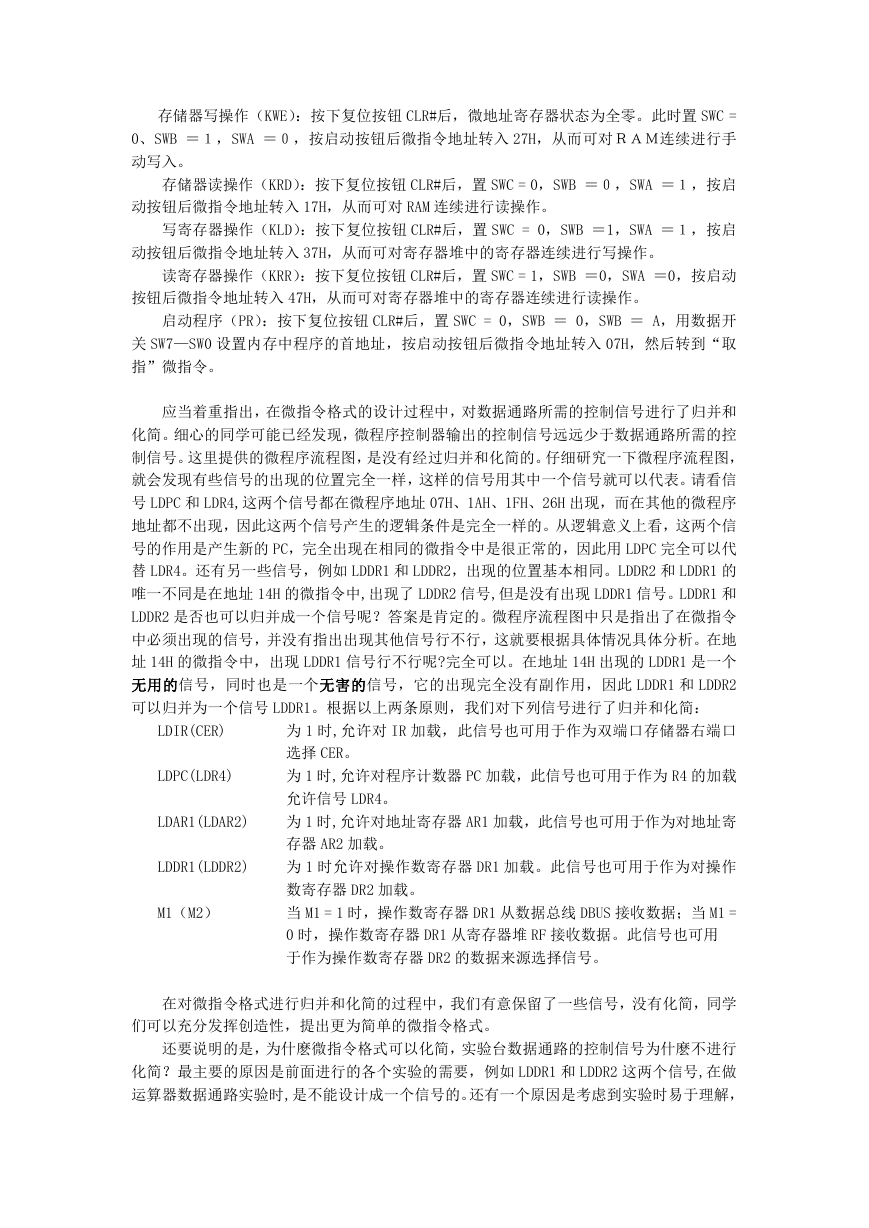

TEC—4 计算机组成原理实验系统的时序电路如图 9 所示。电路采用 2 片 GAL22V10(U6、U7),

可产生两级等间隔时序信号 T1-T4 和 W1-W4,其中一个 W 由一轮 T1-T4 循环组成,它相当于一个

微指令周期或硬布线控制器的一拍,而一轮 W1—W4 循环可供硬布线控制器执行一条机器指令。

本次实验不涉及硬布线控制器,因此时序发生器中的相关内容也可根据需要放到硬布线控制器

实验中进行。

微程序控制器只使用时序信号 T1-T4,产生 T 信号的功能集成在 GAL22V10 芯片 TIMER1(U6)

�

中,另外它还产生节拍信号 W1、W2、W3、W4 的控制时钟 CLK1。该芯片的逻辑功能用 ABEL 语言实现,

其源程序如下:

MODULE TIMER1

TITLE 'CLOCK

"2000,9

GGENERATOR T1,T2,T3,T4'

"INPUT

"OUTPUT

MF,CLR,QD,DP,DZ,TJ,P1,INTS,INTC,DB

W4 PIN 13;

PIN 1..10;

T1,T2,T3,T4,QD1,QD2,ACT,INTE,QDR PIN 14..22;

CLK1 PIN 23;

T1,T2,T3,T4,QD1,QD2,INTE,QDR ISTYPE 'REG';

ACT,CLK1 ISTYPE 'COM';

CLK = .C.;

S =[T1,T2,T3,T4,QD1,QD2,INTE,QDR];

EQUATIONS

QD1 := QD;

QD2 := QD1;

QDR := CLR & QD # CLR & QDR;

ACT = QD1 & !QD2;

T1 := CLR & T4 & ACT # CLR & T4 & !(DP # TJ # DZ & P1 # DB & W4) & QDR;

T2 := CLR & T1;

T3 := CLR & T2;

T4 := !CLR # T3 # T4 & !ACT & (DP # TJ

INTE := CLR & INTS # CLR & INTE & !INTC;

CLK1 = T1 # !CLR & MF;

S.CLK = MF;

# DZ & P1 # DB & W4) # !QDR;

END

�

MF

QD

QD1

QD2

ACT

QDR

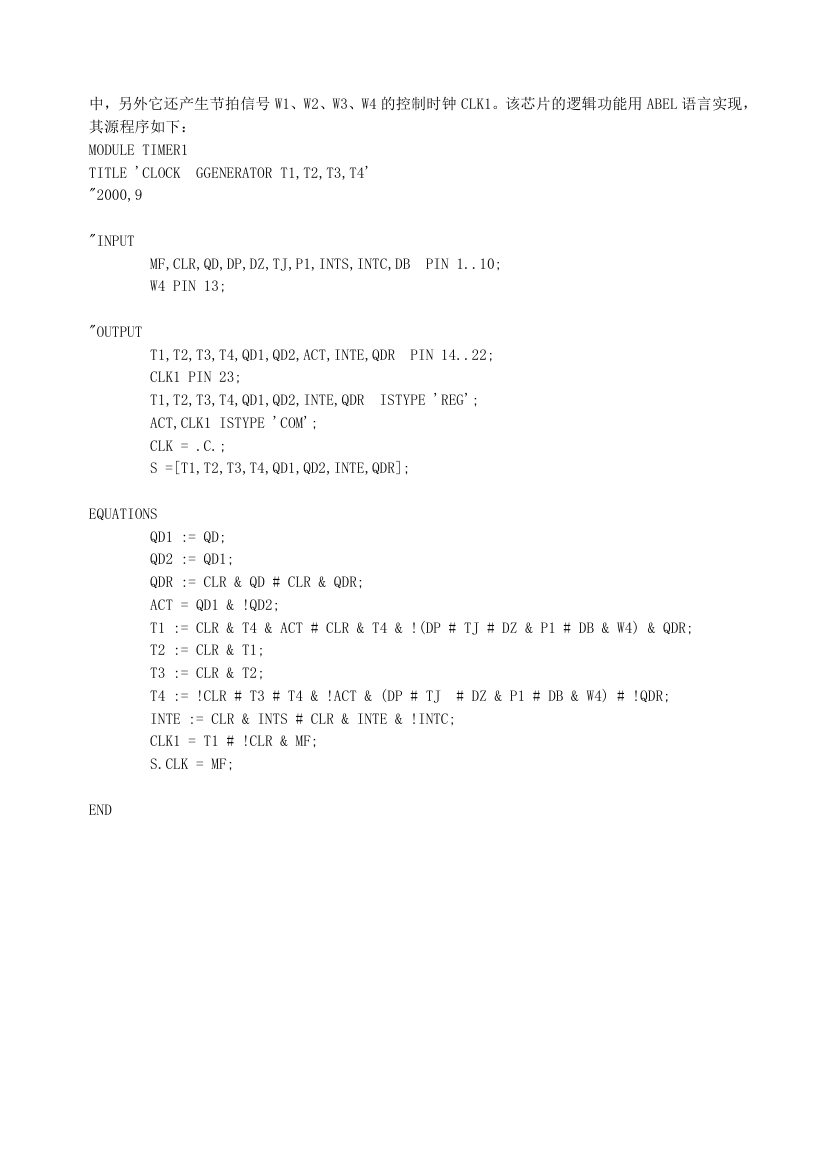

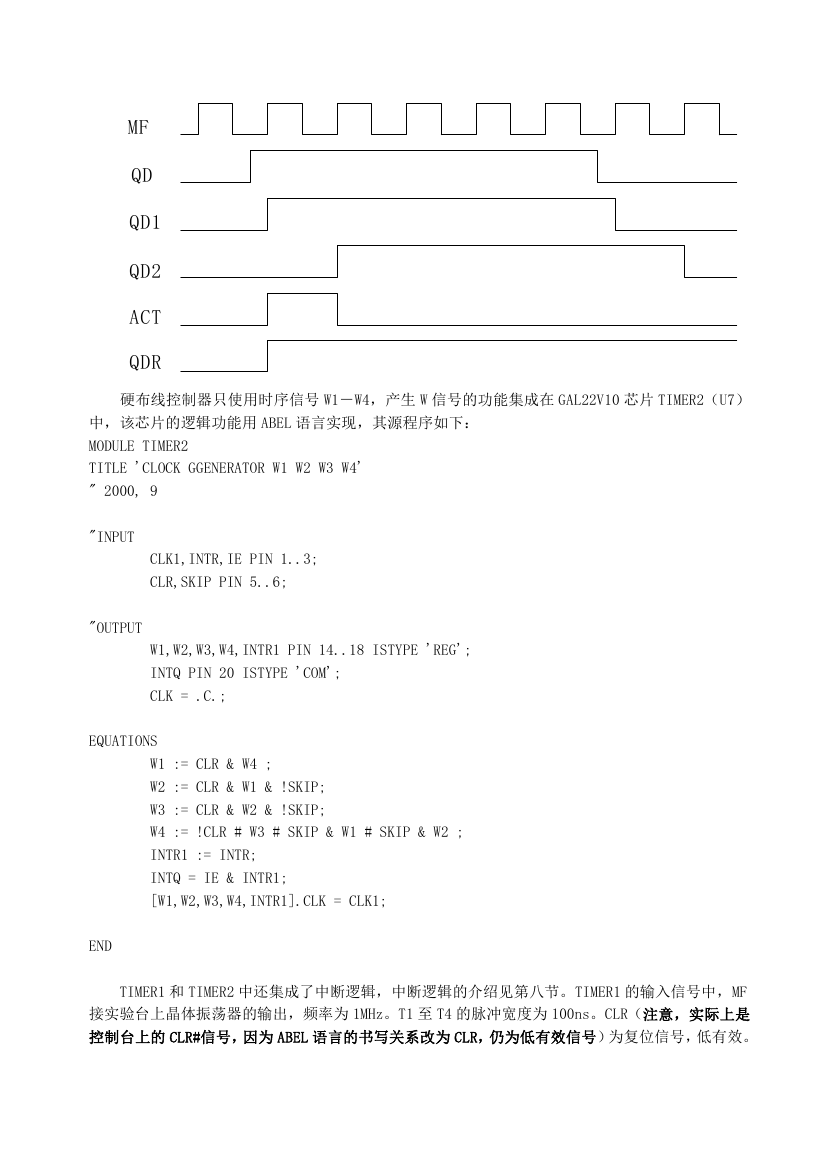

硬布线控制器只使用时序信号 W1-W4,产生 W 信号的功能集成在 GAL22V10 芯片 TIMER2(U7)

中,该芯片的逻辑功能用 ABEL 语言实现,其源程序如下:

MODULE TIMER2

TITLE 'CLOCK GGENERATOR W1 W2 W3 W4'

" 2000, 9

CLK1,INTR,IE PIN 1..3;

CLR,SKIP PIN 5..6;

"INPUT

"OUTPUT

W1,W2,W3,W4,INTR1 PIN 14..18 ISTYPE 'REG';

INTQ PIN 20 ISTYPE 'COM';

CLK = .C.;

EQUATIONS

W1 := CLR & W4 ;

W2 := CLR & W1 & !SKIP;

W3 := CLR & W2 & !SKIP;

W4 := !CLR # W3 # SKIP & W1 # SKIP & W2 ;

INTR1 := INTR;

INTQ = IE & INTR1;

[W1,W2,W3,W4,INTR1].CLK = CLK1;

END

TIMER1 和 TIMER2 中还集成了中断逻辑,中断逻辑的介绍见第八节。TIMER1 的输入信号中,MF

接实验台上晶体振荡器的输出,频率为 1MHz。T1 至 T4 的脉冲宽度为 100ns。CLR(注意,实际上是

控制台上的 CLR#信号,因为 ABEL 语言的书写关系改为 CLR,仍为低有效信号)为复位信号,低有效。

�

实验台处于任何状态下令 CLR# = 0,都会使时序发生器和微程序控制器复位(回到初始状态),

CLR# =1时,则可以正常运行。复位后时序发生器停在 T4、W4 状态,微程序地址为 000000B。建

议每次实验仪加电后,先用 CLR#复位一次。控制台上有一个 CLR#按钮,按一次,产生一个 CLR#负

脉冲,实验台印制板上已连好控制台 CLR#到时序电路 CLR 的连线。

TJ(停机)是控制器的输出信号之一。连续运行时,如果控制信号 TJ=1,会使机器停机,停

止发送时序脉冲 T1—T4、W1—W4,时序停在 T4。在实验台上为了将时序信号发生器的输入信号 TJ

和控制存储器产生的 TJ 信号区分开来,以便于连线操作,在实验台上时序信号发生器的输入信号

TJ 命名为 TJI,而控制存储器产生的信号 TJ 仍命名为 TJ。QD(启动)是来自启动按钮 QD 的脉冲信

号,在 TIMER1 中,对 QD 用 MF 进行了同步,产生 QD1 和 QD2。ACT 表示 QD1 上升沿,表达式是 QD1 & !QD2,

脉冲宽度为 1000ns 。QDR 是运行标志,QD 信号使其为 1,CLR 信号将其置 0。DP(单拍)是来自控

制台的 DP 开关信号,当 DP =1时,机器处于单拍运行状态,按一次启动按钮 QD,只发送一条微指

令周期的时序信号就停机。利用单拍方式,每次只执行一条微指令,因而可以观察微指令代码和当

前微指令的执行结果。DZ(单指)信号是针对微程序控制器的,接控制台开关 DZ 和 P1 信号配合使

用。P1 是微指令字判断字段中的一个条件信号,从微程序控制器输出。P1 信号在微程序中每条机器

指令执行结束时为1,用于检测有无中断请求 INTQ,而时序发生器用它来实现单条机器指令停机。

在 DB =0且 DP = 0 的前提下,当 DZ =0时,机器连续运行。当 DZ =1时,机器处于单指方式,

每次只执行一条机器指令。

DB、SKIP、CLK1 信号以及 W1—W4 时序信号都是针对硬布线控制器的。W1—W4 是节拍信号,硬

布线控制器执行一条机器指令需要一组 W1—W4 信号。DB(单步)信号就是每次发送一组W信号后停

机,可见其功能与 DZ 类似。执行某些机器指令不需要完整的一组W信号周期,SKIP 信号就是用来

跳过本指令剩余的W节拍信号的。中断允许标志 IE 由控制存储器的输出信号 INTS 将其置 1,由控制

存储器的输出信号 INTC 将其置 0。在 TIMER2 内部,控制台产生的中断请求被用时钟 CLK1 进行同步,

产生了 INTR1。只有在 INTE = 1 时,控制台产生的中断请求脉冲 INTR 才能起作用,即产生向控制

器输出的中断中断信号 INTQ,INTQ = INTE & INTR1。

2.数据通路

微程序控制器是根据数据通路和指令系统来设计的。这里采用的数据通路是在综合前面各实验

模块的基础上,又增加程序计数器 PC(U18)、地址加法器 ALU2(U17)、地址缓冲寄存器 R4(U25、

U26)和中断地址寄存器 IAR(U19),详见第二节的图 4。PC 和 ALU2 各采用一片 GAL22V10,两者配

合使用,可完成程序地址的存储、增 1 和加偏移量的功能。R4 由两片 74HC298 组成,带二选一输入

端。IAR 是一片 74HC374,用于中断时保存断点地址。有关数据通路总体的详细说明,请参看第一节。

3.微指令格式与微程序控制器电路

J

T

2

S

1

S

0

S

1

M

1

R

D

D

L

D

R

W

W

R

L

#

L

E

C

S

U

B

_

U

L

A

#

S

U

B

_

S

R

#

S

U

B

_

W

S

#

S

U

B

_

R

A

I

C

N

I

_

1

R

A

1

R

A

D

L

R

A

I

D

L

4

M

C

N

I

_

C

P

D

D

A

_

C

P

R

E

D

L

3

M

C

P

D

L

R

I

D

L

C

T

N

I

S

T

N

I

3

P

2

P

1

P

0

P

5

A

u

4

A

u

3

A

u

2

A

u

1

A

u

0

A

u

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

判断条件

后继微地址

图10 微指令格式

�

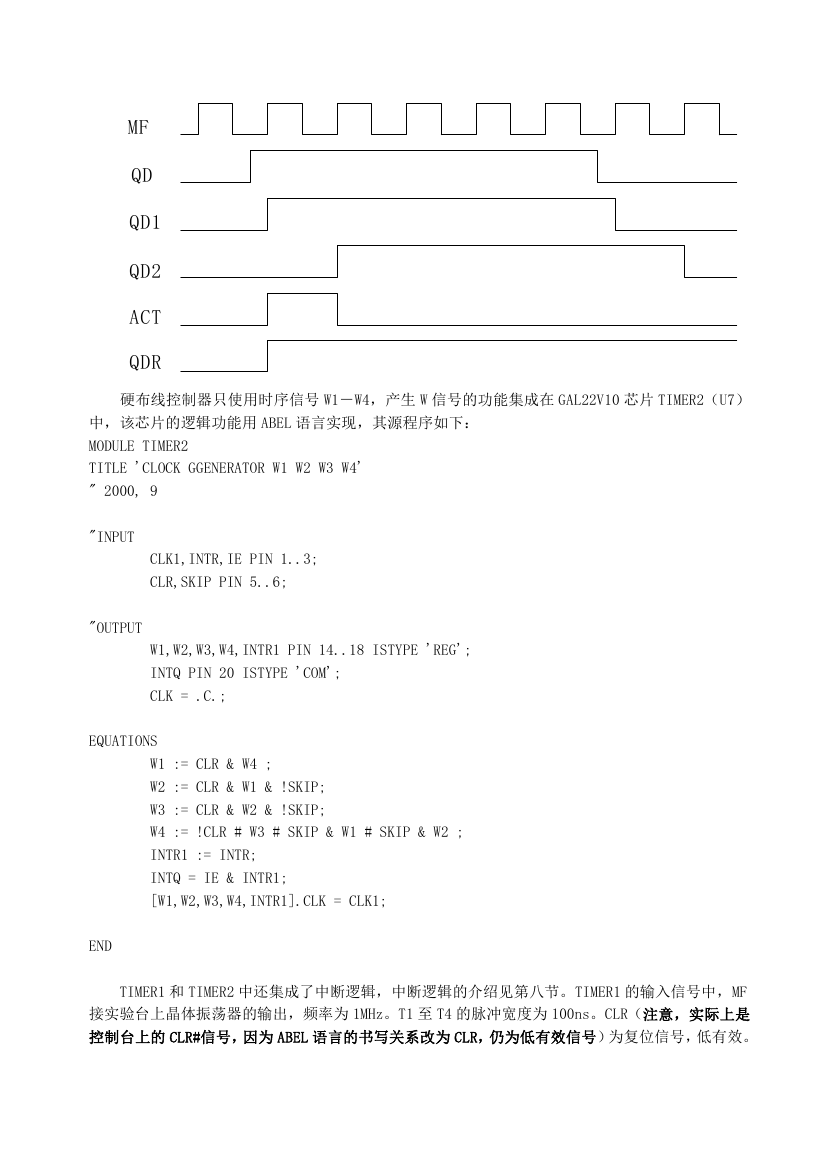

根据给定的 12 条机器指令功能和数据通路总体图的控制信号,采用的微指令格式见图 10。微

指令字长共 35 位。其中顺序控制部分 10 位:后继微地址6位,判别字段4位,操作控制字段 25 位,

各位进行直接控制。微指令格式中,信号名带有后缀“#”的信号为低有效信号,不带有后缀“#”

的信号为高有效信号。

判断指示灯

4

C

N

3

C

N

2

C

N

1

C

N

0

C

N

J

T

2

S

1

S

0

S

1

M

1

R

D

D

L

D

R

W

W

R

L

#

L

E

C

S

U

B

_

U

L

A

#

S

U

B

_

S

R

#

S

U

B

_

W

S

#

S

U

B

_

R

A

I

C

N

I

_

1

R

A

3

M

R

E

D

L

1

R

A

D

L

R

A

I

D

L

4

M

C

N

I

_

C

P

D

D

A

_

C

P

C

P

D

L

R

I

D

L

C

T

N

I

S

T

N

I

3

P

2

P

1

P

0

P

5

A

u

4

A

u

3

A

u

2

A

u

1

A

u

0

A

u

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

CM4

28C64

CM3

28C64

CM2

28C64

CM1

28C64

CM0

28C64

5

A

4

A

3

A

2

A

1

A

0

A

5

A

4

A

3

A

2

A

1

A

0

A

5

A

4

A

3

A

2

A

1

A

0

A

5

A

4

A

3

A

2

A

1

A

0

A

u_A0— u_A5

5

Q

4

Q

3

Q

2

Q

1

Q

0

Q

uAR

74HC174

0

D

1

D

2

D

3

D

4

D

5

D

CLR#

T1

uD0— uD5

JUMP

2

A

1

A

0

A

......

5

A

4

A

3

A

微

地

址

指

示

灯

4

R

I

5

R

I

6

R

I

7

R

I

图11 微程序控制器的组成

C

A

W

S

Q

T

N

I

B

W

S

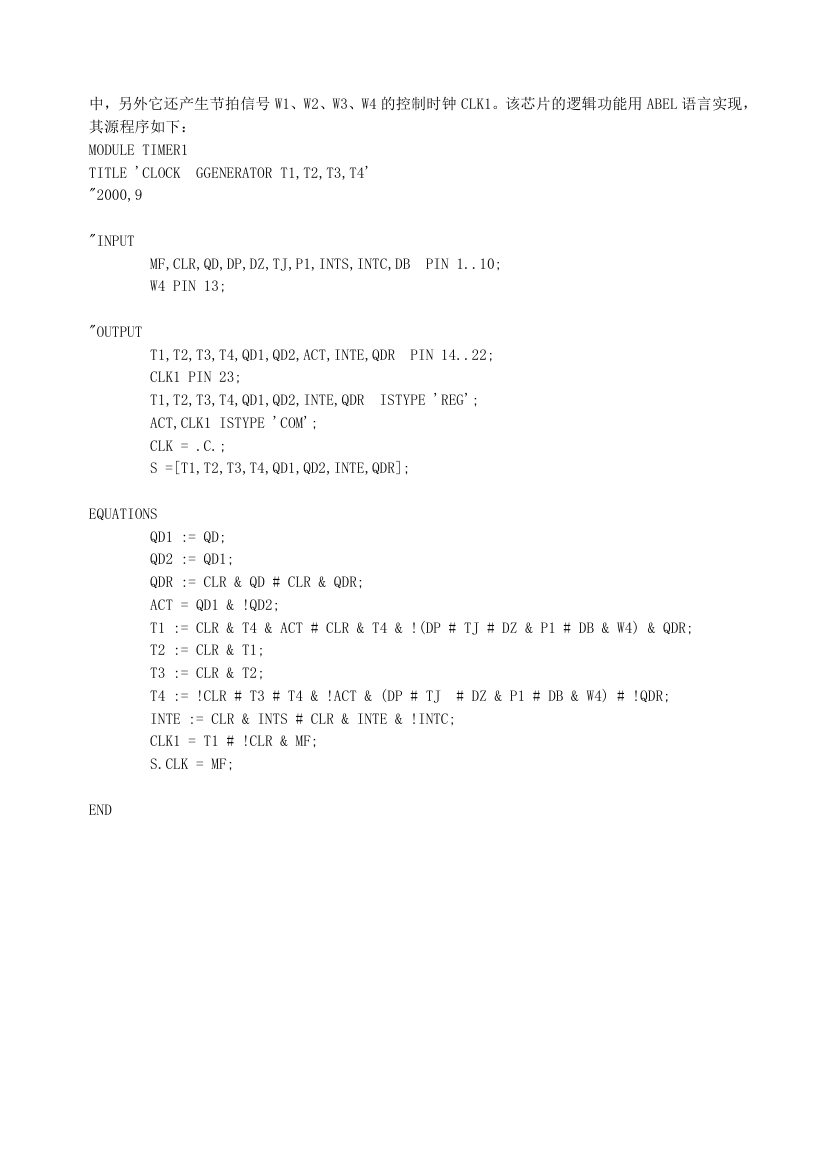

对应微指令格式,微程序控制器的组成见图 11。控制存储器采用 5 片 EEPROM

28C64(U8、U9、

U10、U11、U12)。28C64 的输出是 D0—D7,分别与引脚 11、12、13、15、16、17、18、19 相对应,

CM0 是最低字节,CM4 是最高字节。微地址寄存器6位,用一片 6D 触发器 74HC174(U1)组成,带

有清零端。两级与门、或门构成微地址转移逻辑,用于产生下一微指令的地址。在每个 T1 上升沿时

刻,新的微指令地址会打入微地址寄存器中,控制存储器随即输出相应的微命令代码。微地址转移

逻辑生成下一地址,等下一个 T1 上升沿时打入微地址寄存器。跳转开关 JUMP(J1)是一组 6 个跳

线开关。当用短路子将它们连通时,微地址寄存器AR 从本实验系统提供的微程序地址译码电路得

到新的微程序地址D0—D5。当他们被断开时,用户提供自己的新微程序地址D0—D5。这样用户

能够使用自己设计的微程序地址译码电路。5 片 EEPROM 的地址 A6(引脚 4)直接与控制台开关 SWC

连接,当 SWC = 1 时,微地址大于或者等于 40H,当 SWC = 0 时,微地址的范围为 00H—3FH。SWC

主要用于实现读寄存器堆的功能。

微地址转移逻辑的多个输入信号中,INTQ 是中断请求,本实验中可以不理会。SWA、SWB 是控制

台的两个二进制开关信号,实验台上线已接好接。C是进位信号,IR7—IR4 是机器指令代码,由于

�

本次实验不连接数据通路,这些信号都接到二进制开关 K0—K15 上。

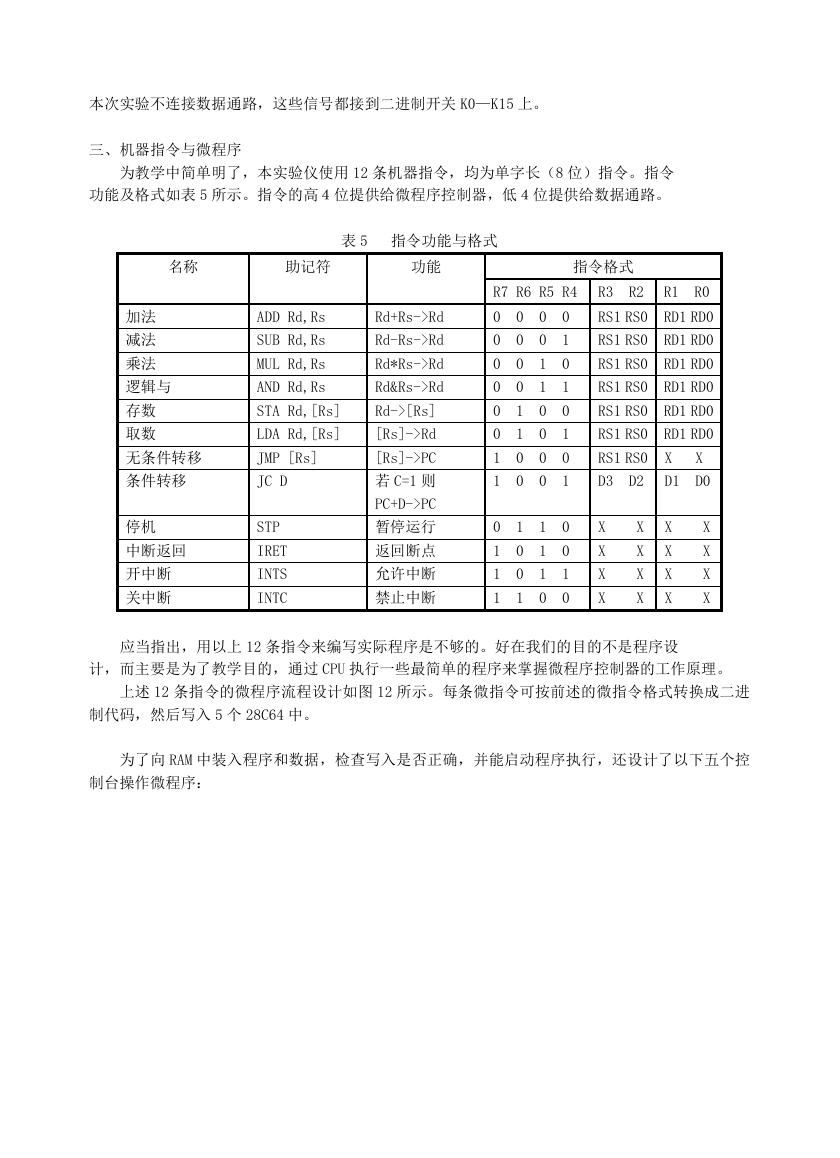

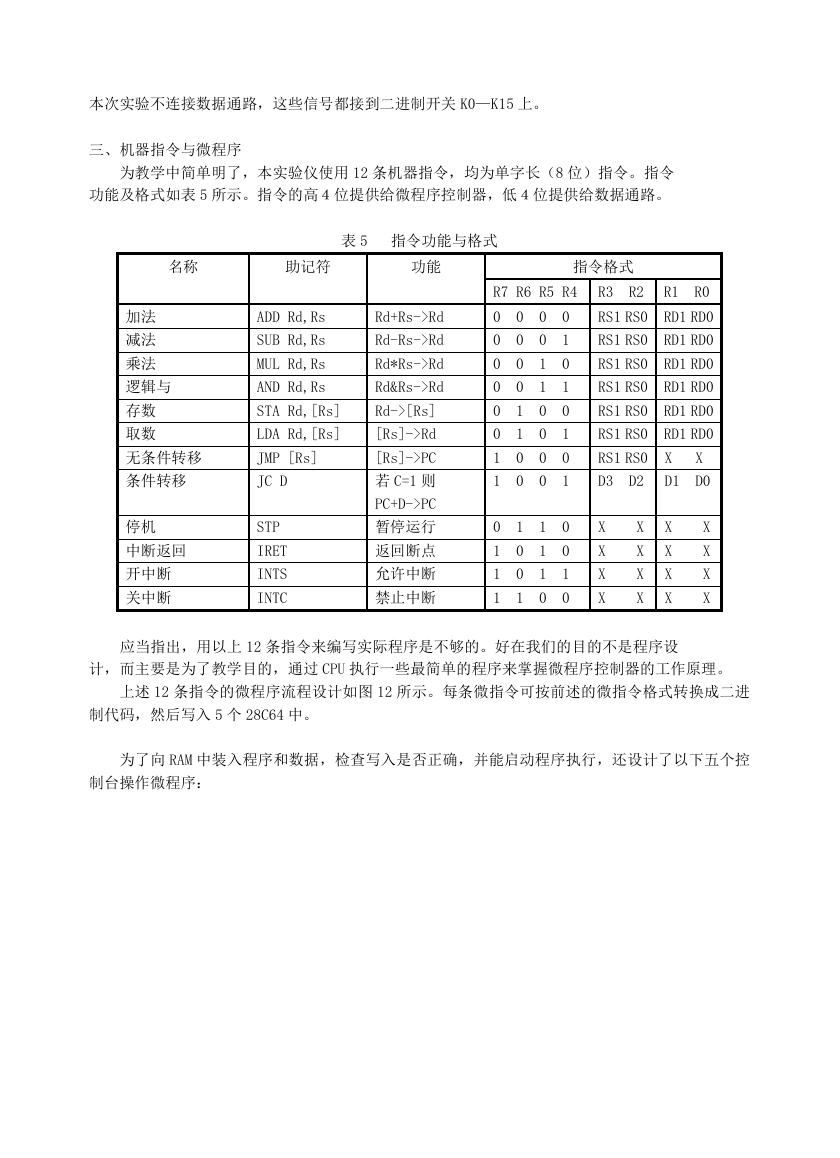

三、机器指令与微程序

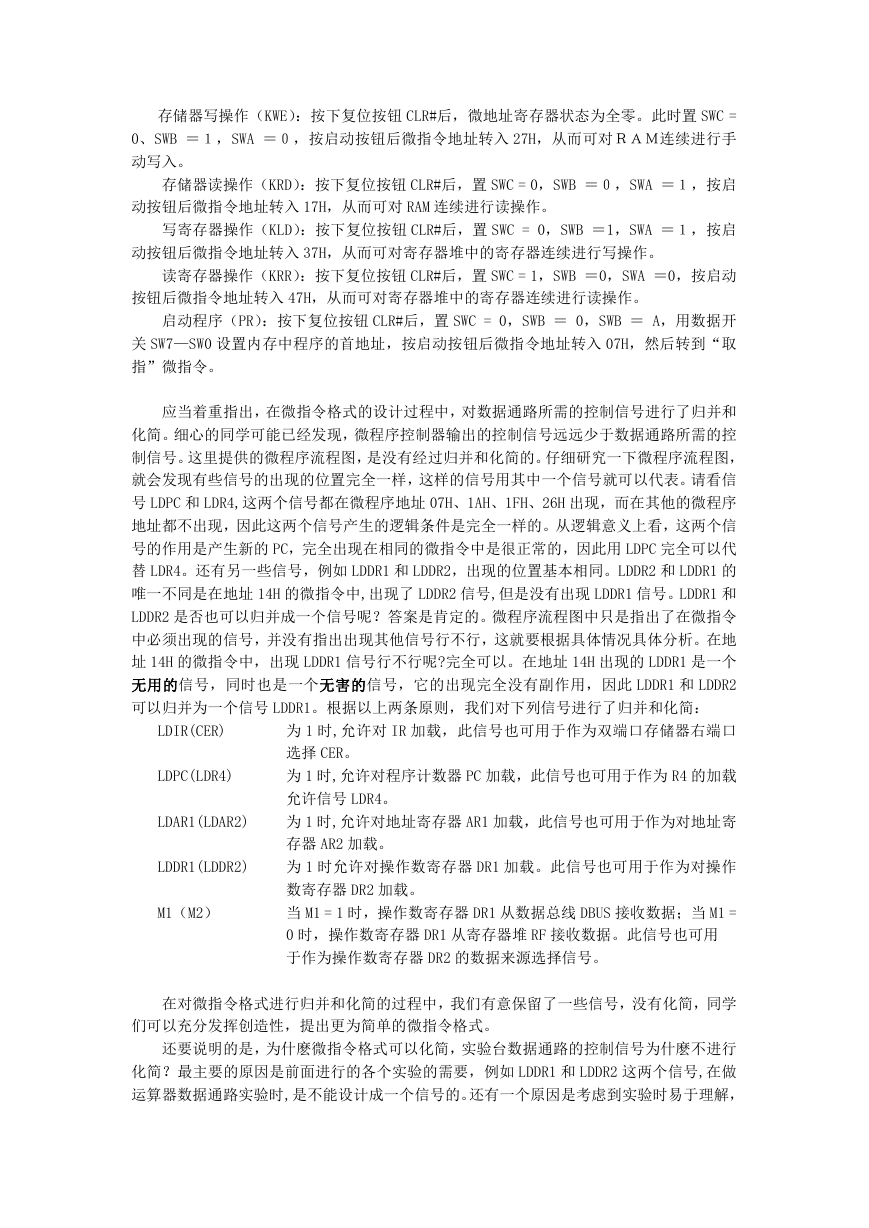

为教学中简单明了,本实验仪使用 12 条机器指令,均为单字长(8 位)指令。指令

功能及格式如表 5 所示。指令的高4位提供给微程序控制器,低4位提供给数据通路。

名称

助记符

功能

指令格式

表 5 指令功能与格式

加法

减法

乘法

逻辑与

存数

取数

ADD Rd,Rs

SUB Rd,Rs

MUL Rd,Rs

AND Rd,Rs

STA Rd,[Rs]

LDA Rd,[Rs]

无条件转移

JMP [Rs]

条件转移

停机

中断返回

开中断

关中断

JC D

STP

IRET

INTS

INTC

Rd+Rs->Rd

Rd-Rs->Rd

Rd*Rs->Rd

Rd&Rs->Rd

Rd->[Rs]

[Rs]->Rd

[Rs]->PC

若 C=1 则

PC+D->PC

暂停运行

返回断点

允许中断

禁止中断

R7 R6 R5 R4

R3

R2

R1

R0

0

0

0

0

0

0

1

1

0

1

1

1

0

0

0

0

1

1

0

0

1

0

0

1

0

0

1

1

0

0

0

0

1

1

1

0

0

1

0

1

0

1

0

1

0

0

1

0

RS1 RS0

RD1 RD0

RS1 RS0

RD1 RD0

RS1 RS0

RD1 RD0

RS1 RS0

RD1 RD0

RS1 RS0

RD1 RD0

RS1 RS0

RD1 RD0

RS1 RS0

X

X

D3

D2

D1

D0

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

应当指出,用以上 12 条指令来编写实际程序是不够的。好在我们的目的不是程序设

计,而主要是为了教学目的,通过 CPU 执行一些最简单的程序来掌握微程序控制器的工作原理。

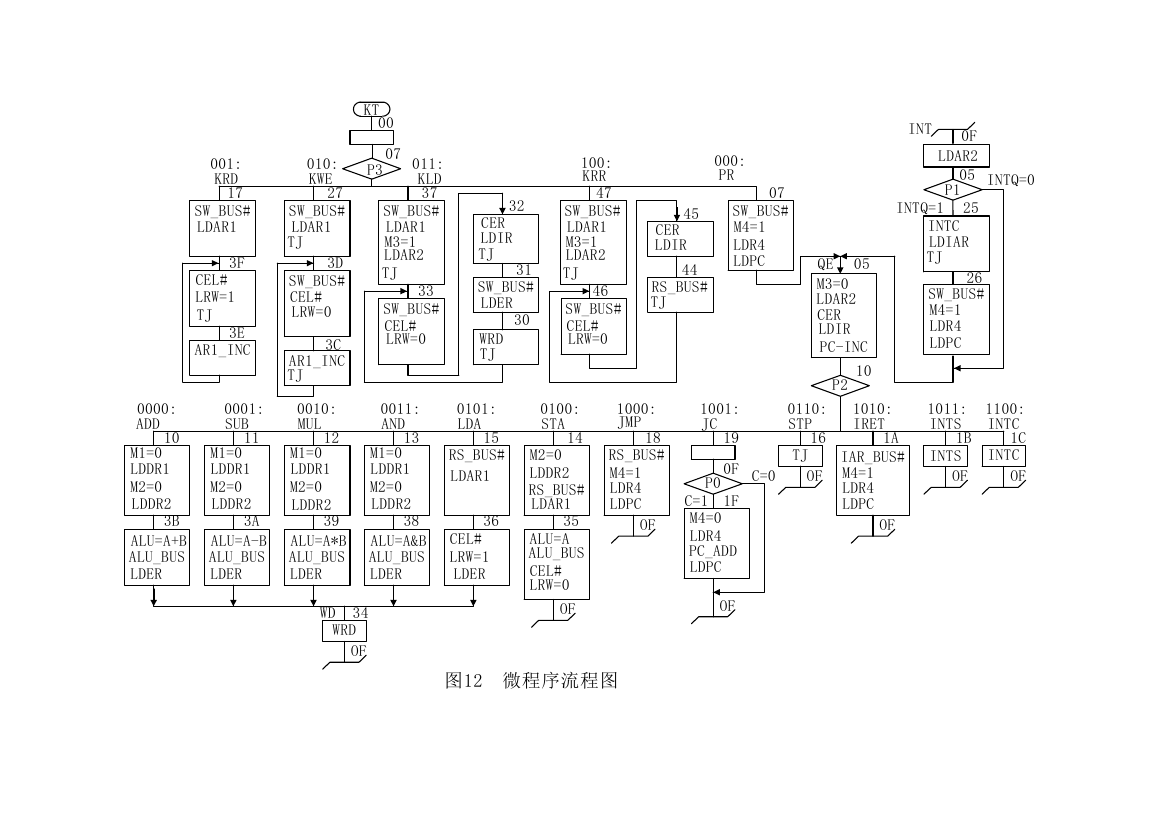

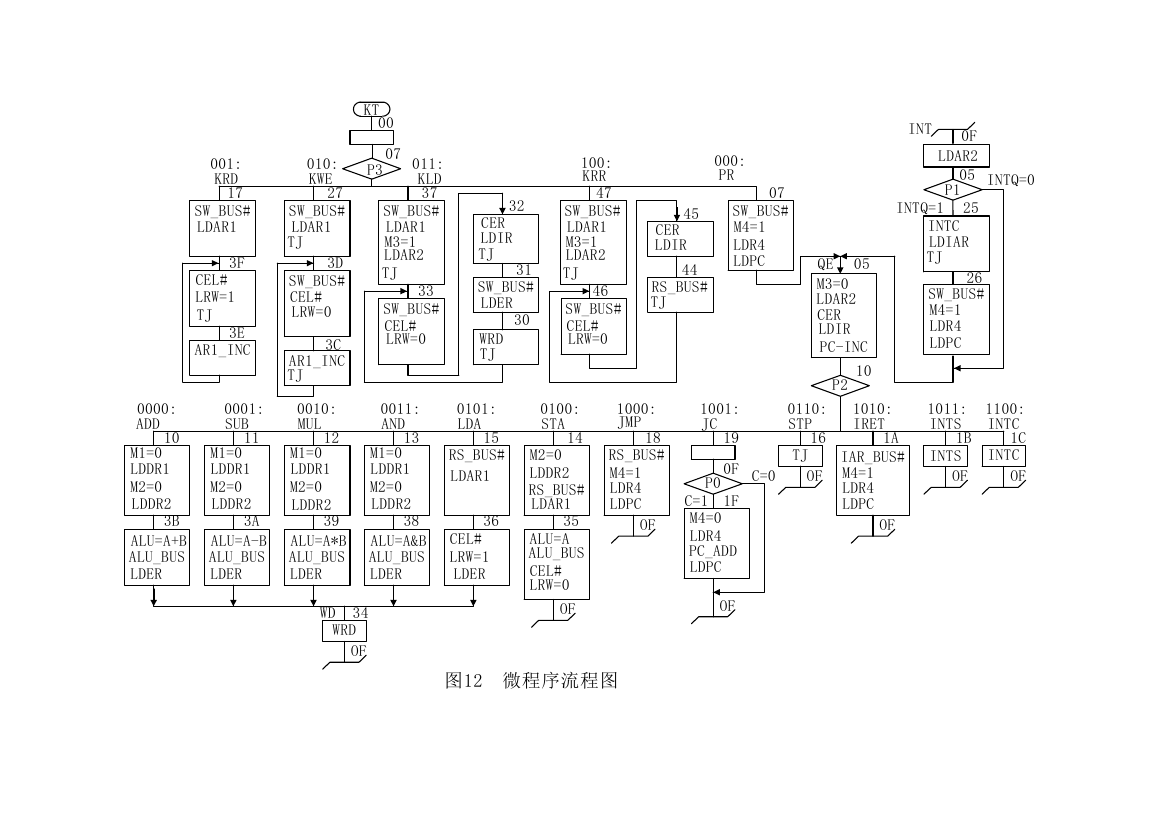

上述 12 条指令的微程序流程设计如图 12 所示。每条微指令可按前述的微指令格式转换成二进

制代码,然后写入 5 个 28C64 中。

为了向 RAM 中装入程序和数据,检查写入是否正确,并能启动程序执行,还设计了以下五个控

制台操作微程序:

�

KT

00

P3

07

011:

KLD

37

SW_BUS#

LDAR1

M3=1

LDAR2

TJ

33

SW_BUS#

CEL#

LRW=0

100:

KRR

47

SW_BUS#

LDAR1

M3=1

LDAR2

TJ

46

SW_BUS#

CEL#

LRW=0

32

CER

LDIR

TJ

31

SW_BUS#

LDER

30

WRD

TJ

000:

PR

07

SW_BUS#

M4=1

LDR4

LDPC

45

CER

LDIR

44

RS_BUS#

TJ

INT

0F

LDAR2

05

P1

INTQ=1

25

INTQ=0

INTC

LDIAR

TJ

26

SW_BUS#

M4=1

LDR4

LDPC

05

QE

M3=0

LDAR2

CER

LDIR

PC-INC

10

P2

001:

KRD

17

SW_BUS#

LDAR1

3F

CEL#

LRW=1

TJ

3E

AR1_INC

0000:

ADD

10

M1=0

LDDR1

M2=0

LDDR2

3B

ALU=A+B

ALU_BUS

LDER

0001:

SUB

11

M1=0

LDDR1

M2=0

LDDR2

3A

ALU=A-B

ALU_BUS

LDER

010:

KWE

27

SW_BUS#

LDAR1

TJ

3D

SW_BUS#

CEL#

LRW=0

3C

AR1_INC

TJ

0010:

MUL

12

M1=0

LDDR1

M2=0

LDDR2

39

ALU=A*B

ALU_BUS

LDER

0110:

STP

16

TJ

C=0

OF

1010:

IRET

1A

IAR_BUS#

M4=1

LDR4

LDPC

OF

1011:

INTS

1B

INTS

OF

1100:

INTC

1C

INTC

OF

0011:

AND

13

M1=0

LDDR1

M2=0

LDDR2

38

ALU=A&B

ALU_BUS

LDER

0101:

LDA

15

RS_BUS#

LDAR1

36

CEL#

LRW=1

LDER

0100:

STA

14

M2=0

LDDR2

RS_BUS#

LDAR1

35

ALU=A

ALU_BUS

CEL#

LRW=0

OF

1000:

JMP

18

RS_BUS#

M4=1

LDR4

LDPC

OF

1001:

JC

19

0F

P0

1F

C=1

M4=0

LDR4

PC_ADD

LDPC

OF

图12 微程序流程图

WD

34

WRD

OF

�

存储器写操作(KWE):按下复位按钮 CLR#后,微地址寄存器状态为全零。此时置 SWC =

0、SWB =1,SWA =0,按启动按钮后微指令地址转入 27H,从而可对RAM连续进行手

动写入。

存储器读操作(KRD):按下复位按钮 CLR#后,置 SWC = 0,SWB =0,SWA =1,按启

动按钮后微指令地址转入 17H,从而可对 RAM 连续进行读操作。

写寄存器操作(KLD):按下复位按钮 CLR#后,置 SWC = 0,SWB =1,SWA =1,按启

动按钮后微指令地址转入 37H,从而可对寄存器堆中的寄存器连续进行写操作。

读寄存器操作(KRR):按下复位按钮 CLR#后,置 SWC = 1,SWB =0,SWA =0,按启动

按钮后微指令地址转入 47H,从而可对寄存器堆中的寄存器连续进行读操作。

启动程序(PR):按下复位按钮 CLR#后,置 SWC = 0,SWB = 0,SWB = A,用数据开

关 SW7—SW0 设置内存中程序的首地址,按启动按钮后微指令地址转入 07H,然后转到“取

指”微指令。

应当着重指出,在微指令格式的设计过程中,对数据通路所需的控制信号进行了归并和

化简。细心的同学可能已经发现,微程序控制器输出的控制信号远远少于数据通路所需的控

制信号。这里提供的微程序流程图,是没有经过归并和化简的。仔细研究一下微程序流程图,

就会发现有些信号的出现的位置完全一样,这样的信号用其中一个信号就可以代表。请看信

号 LDPC 和 LDR4,这两个信号都在微程序地址 07H、1AH、1FH、26H 出现,而在其他的微程序

地址都不出现,因此这两个信号产生的逻辑条件是完全一样的。从逻辑意义上看,这两个信

号的作用是产生新的 PC,完全出现在相同的微指令中是很正常的,因此用 LDPC 完全可以代

替 LDR4。还有另一些信号,例如 LDDR1 和 LDDR2,出现的位置基本相同。LDDR2 和 LDDR1 的

唯一不同是在地址 14H 的微指令中,出现了 LDDR2 信号,但是没有出现 LDDR1 信号。LDDR1 和

LDDR2 是否也可以归并成一个信号呢?答案是肯定的。微程序流程图中只是指出了在微指令

中必须出现的信号,并没有指出出现其他信号行不行,这就要根据具体情况具体分析。在地

址 14H 的微指令中,出现 LDDR1 信号行不行呢?完全可以。在地址 14H 出现的 LDDR1 是一个

无用的信号,同时也是一个无害的信号,它的出现完全没有副作用,因此 LDDR1 和 LDDR2

可以归并为一个信号 LDDR1。根据以上两条原则,我们对下列信号进行了归并和化简:

LDIR(CER)

LDPC(LDR4)

LDAR1(LDAR2)

LDDR1(LDDR2)

M1(M2)

为 1 时,允许对 IR 加载,此信号也可用于作为双端口存储器右端口

选择 CER。

为 1 时,允许对程序计数器 PC 加载,此信号也可用于作为 R4 的加载

允许信号 LDR4。

为 1 时,允许对地址寄存器 AR1 加载,此信号也可用于作为对地址寄

存器 AR2 加载。

为 1 时允许对操作数寄存器 DR1 加载。此信号也可用于作为对操作

数寄存器 DR2 加载。

当 M1 = 1 时,操作数寄存器 DR1 从数据总线 DBUS 接收数据;当 M1 =

0 时,操作数寄存器 DR1 从寄存器堆 RF 接收数据。此信号也可用

于作为操作数寄存器 DR2 的数据来源选择信号。

在对微指令格式进行归并和化简的过程中,我们有意保留了一些信号,没有化简,同学

们可以充分发挥创造性,提出更为简单的微指令格式。

还要说明的是,为什麽微指令格式可以化简,实验台数据通路的控制信号为什麽不进行

化简?最主要的原因是前面进行的各个实验的需要,例如 LDDR1 和 LDDR2 这两个信号,在做

运算器数据通路实验时,是不能设计成一个信号的。还有一个原因是考虑到实验时易于理解,

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc