扉 页

前 言

目 录

通用格式约定

表格内容约定

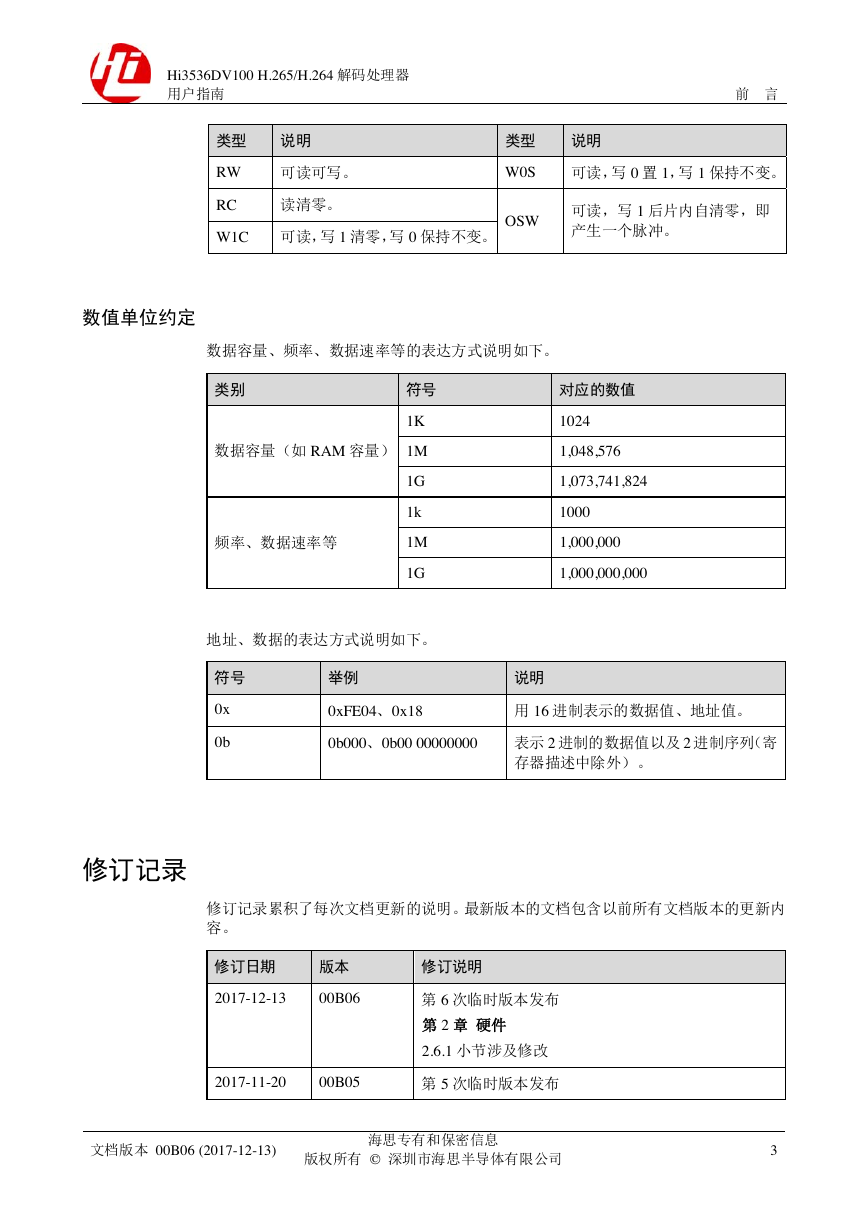

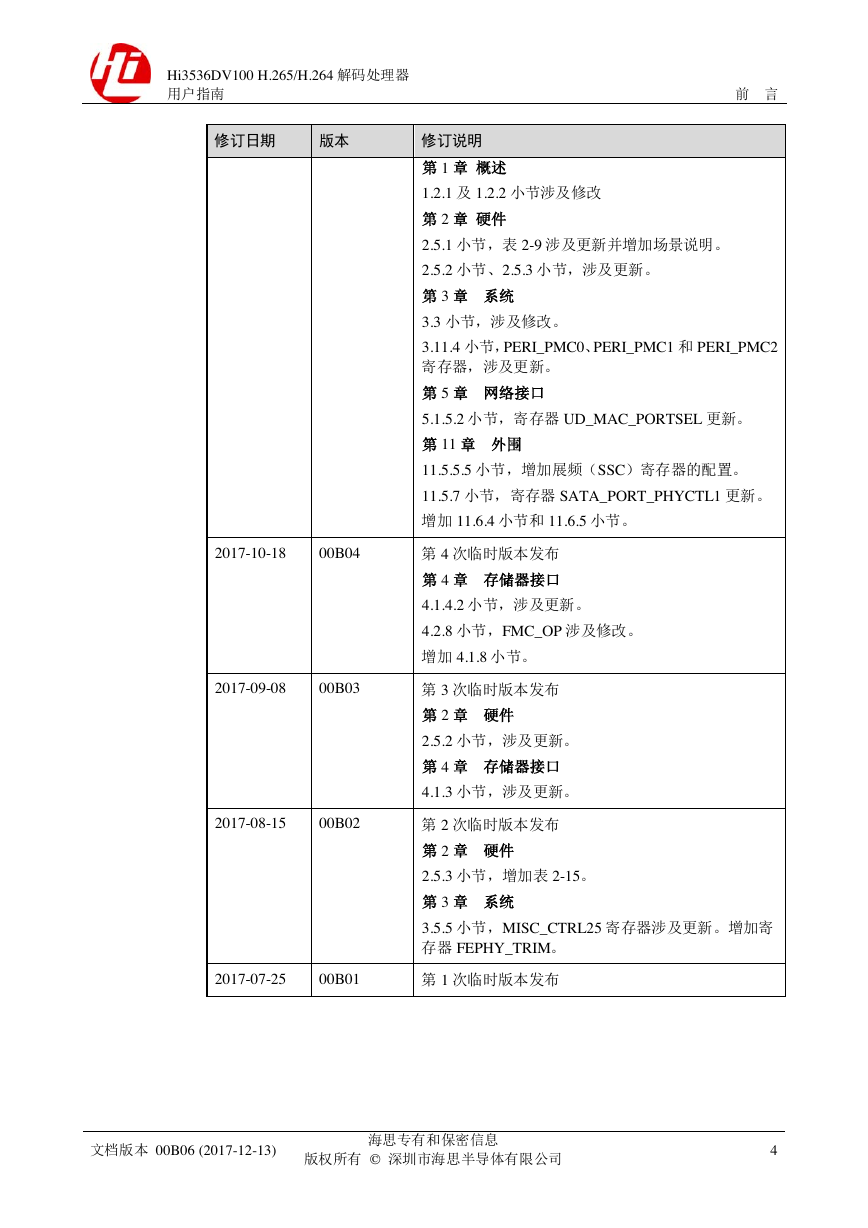

寄存器访问类型约定

数值单位约定

1 产品概述

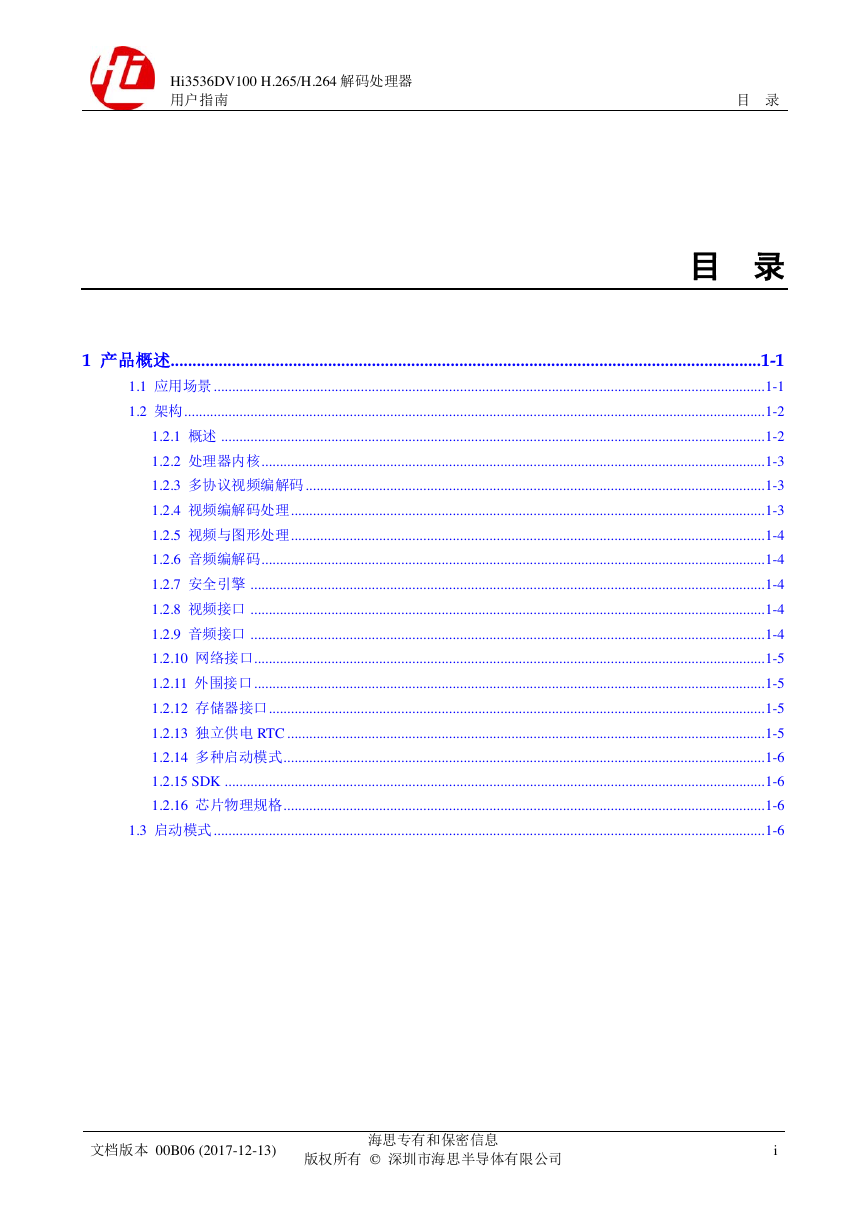

目 录

插图目录

表格目录

1.1 应用场景

1.2 架构

1.2.1 概述

1.2.2 处理器内核

1.2.3 多协议视频编解码

1.2.4 视频编解码处理

1.2.5 视频与图形处理

1.2.6 音频编解码

1.2.7 安全引擎

1.2.8 视频接口

1.2.9 音频接口

1.2.10 网络接口

1.2.11 外围接口

1.2.12 存储器接口

1.2.13 独立供电RTC

1.2.14 多种启动模式

1.2.15 SDK

1.2.16 芯片物理规格

1.3 启动模式

2 硬件特性

目 录

插图目录

表格目录

2.1 封装与管脚分布

2.1.1 封装

2.1.2 管脚分布

2.2 管脚信息描述

2.3 焊接工艺建议

2.3.1 无铅回流焊工艺参数要求

2.3.2 混合回流焊工艺参数要求

2.4 潮敏参数

2.4.1 海思产品防潮包装

2.4.1.1 包装信息

2.4.1.2 潮敏产品进料检验

2.4.2 存放与使用

2.4.3 重新烘烤

2.5 电性能参数

2.5.1 功耗参数

2.5.2 温度和热阻参数

2.5.3 工作条件

2.5.4 上下电顺序

2.5.5 DC/AC电气参数

2.6 接口时序

2.6.1 DDR接口时序

2.6.1.1 写操作时序

dqs_out相对于dq_out的写操作时序

dqs_out相对于ck的写操作时序

CS和ADDR/CMD相对于ck的写操作时序

2.6.1.2 读操作时序

命令和地址相对于ck的读操作时序

dqs_in相对于dq_in的读操作时序

2.6.1.3 时序参数

2.6.2 SPI Flash接口时序

2.6.3 Ethernet MAC接口时序

2.6.3.1 MII接口时序

2.6.3.2 RMII接口时序

2.6.3.3 MDIO接口时序

2.6.4 AIAO接口时序

2.6.4.1 I2S接口时序

2.6.4.2 PCM模式接口时序

2.6.5 I2C时序

3 系统

目 录

插图目录

表格目录

3.1 复位

3.1.1 概述

3.1.2 复位控制

3.1.3 复位配置

上电复位

系统复位

软复位

3.2 时钟

3.2.1 概述

3.2.2 功能框图

3.2.3 时钟资源分布

3.2.4 PLL配置

3.2.5 频率配置

A7/DDR/BUS频率配置

模块时钟频率配置

注意事项

3.2.6 CRG寄存器概览

PERI_CRG_PLL0

PERI_CRG_PLL1

PERI_CRG_PLL2

PERI_CRG_PLL3

PERI_CRG_PLL4

PERI_CRG_PLL5

PERI_CRG_PLL6

PERI_CRG_PLL7

PERI_CRG_PLL8

PERI_CRG_PLL9

PERI_CRG_PLL10

PERI_CRG_PLL11

PERI_CRG20

PERI_CRG21

PERI_CRG33

PERI_CRG34

PERI_CRG35

PERI_CRG36

PERI_CRG37

PERI_CRG38

PERI_CRG39

PERI_CRG40

PERI_CRG41

PERI_CRG42

PERI_CRG43

PERI_CRG44

PERI_CRG45

PERI_CRG46

PERI_CRG47

PERI_CRG48

PERI_CRG49

PERI_CRG50

PERI_CRG51

PERI_CRG52

PERI_CRG53

PERI_CRG54

PERI_CRG55

PERI_CRG56

PERI_CRG57

PERI_CRG58

PERI_CRG_PLL60

PERI_CRG_PLL61

3.3 处理器子系统

3.4 中断系统

3.5 系统控制器

3.5.1 概述

3.5.2 特点

3.5.3 功能描述

软复位控制

系统地址重映射控制

对关键寄存器的写保护

芯片的标识寄存器

3.5.4 系统控制器寄存器

3.5.4.1 系统控制器寄存器概览

3.5.4.2 系统控制器寄存器描述

SC_CTRL

SC_SYSRES

SOFTINT

SOFTTYPE

SC_LOCKEN

SYSSTAT

SCSYSID0

SCSYSID1

SCSYSID2

SCSYSID3

3.5.5 外设控制寄存器

3.5.5.1 外设控制寄存器概览

3.5.5.2 外设控制寄存器描述

MISC_CTRL2

MISC_CTRL20

MISC_CTRL21

MISC_CTRL24

MISC_CTRL25

MISC_CTRL30

MISC_CTRL31

MISC_CTRL32

MISC_CTRL33

MISC_CTRL34

MISC_CTRL35

FEPHY_TRIM

3.6 DMA控制器

3.6.1 概述

3.6.2 特点

3.6.3 功能描述

功能框图

工作流程

DMA链表

DMA与外设的连接关系

DMAC请求线

3.6.4 工作方式

时钟门控

初始化

启动通道

DMAC_Cn_CONTROL使用说明

DMAC_Cn_CONFIG使用说明

中断处理

3.6.5 DMAC寄存器概览

3.6.6 DMAC寄存器描述

DMAC_INT_STAT

DMAC_INT_TC_STAT

DMAC_INT_TC_CLR

DMAC_INT_ERR_STAT

DMAC_INT_ERR_CLR

DMAC_RAW_INT_TC_STAT

DMAC_RAW_INT_ERR_STAT

DMAC_ENABLED_CHNS

DMAC_SOFT_BREQ

DMAC_SOFT_SREQ

DMAC_SOFT_LBREQ

DMAC_SOFT_LSREQ

DMAC_CONFIG

DMAC_SYNC

DMAC_Cn_SRC_ADDR

DMAC_Cn_DEST_ADDR

DMAC_Cn_LLI

DMAC_Cn_CONTROL

DMAC_Cn_CONFIG

3.7 CIPHER

3.7.1 概述

3.7.2 特点

3.7.3 功能描述

3DES算法

ECB模式

CBC模式

CFB模式

OFB模式

CTR模式

3.7.4 工作方式

CIPHER的单分组操作流程

CIPHER的多分组操作流程

时钟门控

软复位

3.7.5 CIPHER寄存器概览

3.7.6 CIPHER寄存器描述

CHAN0_CIPHER_DOUT

CHAN0_CIPHER_IVOUT

CHAN_CIPHER_IVOUT

CIPHER_KEY

CHAN0_CIPHER_CTRL

CHAN0_CIPHER_IVIN

CHAN0_CIPHER_DIN

CHANn_IBUF_NUM

CHANn_IBUF_CNT

CHANn_IEMPTY_CNT

CHANn_INT_ICNTCFG

CHANn_CIPHER_CTRL

CHANn_SRC_LST_SADDR

CHANn_IAGE_TIMER

CHANn_OBUF_NUM

CHANn_OBUF_CNT

CHANn_OFULL_CNT

CHANn_INT_OCNTCFG

CHANn_DEST_LST_SADDR

CHANn_OAGE_TIMER

INT_STATUS

INT_EN

INT_RAW

RST_STATUS

CHAN0_CFG

3.8 定时器

3.8.1 概述

3.8.2 特点

3.8.3 功能描述

3.8.4 工作方式

初始化

中断处理

时钟选择

3.8.5 Timer寄存器概览

3.8.6 Timer寄存器描述

TIMERx_LOAD

TIMERx_VALUE

TIMERx_CONTROL

TIMERx_INTCLR

TIMERx_RIS

TIMERx_MIS

TIMERx_BGLOAD

3.9 看门狗

3.9.1 概述

3.9.2 特点

3.9.3 功能描述

应用框图

功能原理

3.9.4 工作方式

计数时钟频率配置

系统初始化配置

中断处理过程

关闭WatchDog

3.9.5 WDG寄存器概览

3.9.6 WDG寄存器描述

WDG_LOAD

WDG_VALUE

WDG_CONTROL

WDG_INTCLR

WDG_RIS

WDG_MIS

WDG_LOCK

3.10 实时时钟

3.10.1 概述

3.10.2 特点

3.10.3 功能描述

3.10.4 工作方式

3.10.4.1 计数时钟频率

3.10.4.2 软复位

3.10.4.3 RTC初始化

3.10.4.4 中断处理

3.10.4.5 RTC寄存器的访问

3.10.5 RTC寄存器概览

3.10.6 RTC寄存器描述

SPI_CLK_DIV

SPI_RW

3.10.7 RTC内部寄存器描述

RTC_10MS_COUNT

RTC_S_COUNT

RTC_M_COUNT

RTC_H_COUNT

RTC_D_COUNT_L

RTC_D_COUNT_H

RTC_MR_10MS

RTC_MR_S

RTC_MR_M

RTC_MR_H

RTC_MR_D_L

RTC_MR_D_H

RTC_LR_10MS

RTC_LR_S

RTC_LR_M

RTC_LR_H

RTC_LR_D_L

RTC_LR_D_H

RTC_LORD

RTC_IMSC

RTC_INT_CLR

RTC_MSC_INT

RTC_RAW_INT

RTC_CLK

RTC_POR_N

SDM_COEF_OUSIDE_H

SDM_COEF_OUSIDE_L

USER_REGISTER1

USER_REGISTER2

USER_REGISTER3

USER_REGISTER4

USER_REGISTER5

USER_REGISTER6

USER_REGISTER7

USER_REGISTER8

3.11 PMC

3.11.1 功能描述

3.11.2 工作方式

3.11.2.1 PWM输出

3.11.2.2 HPM控制

3.11.2.3 芯片内部温度检测

3.11.3 PMC寄存器概览

3.11.4 PMC寄存器描述

PERI_PMC0

PERI_PMC1

PERI_PMC2

PERI_PMC4

PERI_PMC10

PERI_PMC11

PERI_PMC12

PERI_PMC13

PERI_PMC14

PERI_PMC15

PERI_PMC16

PERI_PMC17

PERI_PMC30

PERI_PMC31

PERI_PMC68

PERI_PMC69

PERI_PMC70

PERI_PMC71

PERI_PMC72

PERI_PMC73

PERI_PMC74

3.12 电源管理与低功耗模式控制

3.12.1 概述

3.12.2 时钟门控和时钟频率调整

3.12.3 模块级低功耗控制

3.12.4 DDR低功耗控制

4 存储器接口

目 录

插图目录

表格目录

4.1 DDR控制器

4.1.1 概述

4.1.2 特点

4.1.3 功能描述

4.1.3.1 应用框图

4.1.3.2 功能原理

命令真值表

自动刷新

低功耗管理

仲裁机制

流量统计和命令latency统计功能

地址映射方式

4.1.4 工作方式

4.1.4.1 软复位

4.1.4.2 DDR3初始化配置流程

4.1.5 AXI寄存器

4.1.5.1 AXI寄存器概览

4.1.5.2 AXI寄存器描述

AXI_CFG_LOCK

AXI_CKG

AXI_ACTION

AXI_FLUX_STAT

AXI_REGION_MAP

AXI_REGION_ATTRIB

AXI_QOS_MAP

AXI_QOS_WRPRIn

AXI_QOS_RDPRIn

AXI_OSTD_PRTn

AXI_OSTD_PRT_STn

AXI_OSTD_GROUPn

AXI_OSTD_PRIn_0

AXI_OSTD_PRIn_1

AXI_OSTD_GROUP_STn

AXI_PUSH_WRMIDn

AXI_PUSH_RDMIDn

AXI_QOS_WRADPT_MID

AXI_QOS_RDADPT_MID

AXI_QOS_ADPT_CNT

AXI_STATUS

AXI_INT_STATUS

AXI_FLUX_STAT_RDn

AXI_FLUX_STAT_WRn

4.1.6 QOSBUF寄存器

4.1.6.1 QOSBUF寄存器概览

4.1.6.2 QOSBUF寄存器描述

QOSB_ADPT_CTRL

QOSB_BUF_BYP

QOSB_WRTOUT0

QOSB_WRTOUT1

QOSB_WRTOUT2

QOSB_WRTOUT3

QOSB_RDTOUT0

QOSB_RDTOUT1

QOSB_RDTOUT2

QOSB_RDTOUT3

QOSB_WRTOUT_MAP

QOSB_RDTOUT_MAP

QOSB_CKG_CFG

QOSB_DMC_LVL

QOSB_CFG_PERF

QOSB_CMD_SUM

QOSB_CMD_CNT

QOSB_RNK_CNT

QOSB_BNK_CNT0

QOSB_BNK_CNT1

QOSB_BNK_CNT2

QOSB_BNK_CNT3

QOSB_OSTD_CNT

QOSB_WR_CMD_SUM

QOSB_RD_CMD_SUM

QOSB_TIMEOUT_MODE

4.1.7 DDRC内DMC模块寄存器

4.1.7.1 DMC寄存器概览

4.1.7.2 DMC寄存器描述

DDRC_CTRL_SREF

DDRC_CTRL_SFC

DDRC_CTRL_PERF

DDRC_CFG_SREF

DDRC_CFG_PD

DDRC_CFG_AREF

DDRC_CFG_WORKMODE

DDRC_CFG_DDRMODE

DDRC_CFG_SCRAMB

DDRC_CFG_RNKVOL

DDRC_CFG_ODT

DDRC_CFG_TIMING0

DDRC_CFG_TIMING1

DDRC_CFG_TIMING2

DDRC_CFG_TIMING3

DDRC_CFG_TIMING4

DDRC_CFG_TIMING5

DDRC_CFG_TIMING6

DDRC_CFG_BLDATA

DDRC_CFG_DMCLVL

DDRC_CFG_DDRPHY

4.1.8 DDRC内DDRPHY寄存器

4.1.8.1 DDRPHY寄存器概览

4.1.8.2 DDRPHY寄存器描述

DRAMTIMER0

DRAMTIMER1

DRAMTIMER2

DRAMTIMER3

DRAMTIMER4

MODEREG01

MODEREG23

MISC

4.2 Flash Memory控制器

4.2.1 概述

4.2.2 特点

4.2.3 功能描述

4.2.3.1 接口框图

4.2.3.2 接口描述

Standard SPI模式

Dual-Output /Dual-Input SPI模式

Dual I/O SPI模式

Quad-Output /Quad-Input SPI

Quad I/O SPI模式

4.2.3.3 启动功能

4.2.3.4 寄存器方式操作

4.2.3.5 内置DMA操作方式

4.2.3.6 ECC校验功能

4.2.3.7 SPI接口时序说明

4.2.3.8 SPI NAND FALSH地址说明

4.2.4 工作流程

4.2.4.1 初始化流程

4.2.4.2 器件寄存器操作流程

4.2.4.3 读器件状态寄存器操作

4.2.4.4 SPI NOR Flash地址模式切换流程

4.2.4.5 擦除操作流程

4.2.4.6 内置DMA读操作流程

4.2.4.7 内置DMA写操作流程

4.2.4.8 其它注意事项

4.2.5 数据存储结构

无ECC模式

4.2.5.1 驱动软件中的数据结构

2KB page size

4KB page size

4.2.5.2 4bit ECC模式(纠错8bit/1KB)

2KB page size

4KB page size

4.2.5.3 8bit ECC模式(纠错16bit/1KB)

2KB page_size

4KB page_size

4.2.5.4 24bit ECC模式(纠错24bit/1KB)

2KB page size

4KB page size

4.2.5.5 28bit ECC模式(纠错28bit/1KB)

2KB page_size

4KB page_size

4.2.6 ECC模式选择说明

4.2.7 FMC寄存器概览

4.2.8 FMC寄存器描述

FMC_CFG

GLOBAL_CFG

TIMING_SPI_CFG

FMC_INT

FMC_INT_EN

FMC_INT_CLR

FMC_CMD

FMC_ADDRH

FMC_ADDRL

FMC_OP_CFG

FMC_DATA_NUM

FMC_OP

FMC_DMA_LEN

FMC_DMA_AHB_CTRL

FMC_DMA_SADDR_D0

FMC_DMA_SADDR_OOB

FMC_OP_CTRL

FMC_TIMEOUT_WR

FMC_OP_PARA

FMC_BOOT_SET

FMC_LP_CTRL

FMC_ERR_THD

FMC_STATUS

FMC_ERR_NUM0_BUF0

FMC_ERR_ALARM_ADDRH

FMC_ERR_ALARM_ADDRL

FMC_ECC_INVALID_ADDRH

FMC_ECC_INVALID_ADDRL

5 网络接口

目 录

插图目录

表格目录

5.1 ETH

5.1.1 概述

5.1.2 功能描述

5.1.3 工作方式

5.1.3.1 收帧过程

5.1.3.2 发帧过程

5.1.3.3 中断管理

中断状态寄存器

中断使能寄存器

原始中断状态寄存器

5.1.3.4 流量控制

5.1.4 寄存器概览

MDIO控制寄存器

MAC控制寄存器

全局控制寄存器

统计计数控制寄存器

统计结果寄存器

5.1.5 寄存器描述

5.1.5.1 MDIO控制寄存器

MDIO_RWCTRL

MDIO_RO_DATA

UD_MDIO_PHYADDR

UD_MDIO_RO_STAT

UD_MDIO_IRQENA

5.1.5.2 MAC控制寄存器

UD_MAC_PORTSEL

UD_MAC_RO_STAT

UD_MAC_PORTSET

UD_MAC_STAT_CHANGE

UD_MAC_SET

UD_MAC_EEE_INT

UD_MAC_EEE_INTEN

UD_MAC_EEE_ENA

UD_MAC_EEE_TIMER

UD_MAC_EEE_LINK_STATUS

UD_MAC_EEE_CLK_CNT

5.1.5.3 全局控制寄存器

GLB_HOSTMAC_L32

GLB_HOSTMAC_H16

GLB_SOFT_RESET

GLB_FWCTRL

GLB_MACTCTRL

GLB_ENDIAN_MOD

GLB_IRQ_STAT

GLB_IRQ_ENA

GLB_IRQ_RAW

GLB_MAC0_L32

GLB_MAC0_H16

GLB_MAC1_L32

GLB_MAC1_H16

GLB_MAC2_L32

GLB_MAC2_H16

GLB_MAC3_L32

GLB_MAC3_H16

GLB_MAC4_L32

GLB_MAC4_H16

GLB_MAC5_L32

GLB_MAC5_H16

GLB_MAC6_L32

GLB_MAC6_H16

GLB_MAC7_L32

GLB_MAC7_H16

UD_GLB_IRQN_SET

UD_GLB_QLEN_SET

UD_GLB_FC_LEVEL

UD_GLB_CAUSE

UD_GLB_RXFRM_SADDR

UD_GLB_IQFRM_DES

UD_GLB_IQ_ADDR

UD_GLB_BFC_STAT

UD_GLB_EQ_ADDR

UD_GLB_EQFRM_LEN

UD_GLB_QSTAT

UD_GLB_ADDRQ_STAT

UD_GLB_FC_TIMECTRL

UD_GLB_FC_RXLIMIT

UD_GLB_FC_DROPCTRL

UD_GLB_RX_COE_EN

5.1.5.4 统计计数控制寄存器

UD_STS_PORTCNT

UD_PORT2CPU_PKTS

UD_CPU2IQ_ADDRCNT

UD_RX_IRQCNT

UD_CPU2EQ_PKTS

5.1.5.5 统计结果寄存器

UD_RX_DVCNT

UD_RX_OCTS

UD_RX_RIGHTOCTS

UD_HOSTMAC_PKTS

UD_RX_RIGHTPKTS

UD_RX_BROADPKTS

UD_RX_MULTPKTS

UD_RX_UNIPKTS

UD_RX_ERRPKTS

UD_RX_CRCERR_PKTS

UD_RX_LENERR_PKTS

UD_RX_OCRCERR_PKTS

UD_RX_PAUSE_PKTS

UD_RF_OVERCNT

UD_FLUX_TOL_IPKTS

UD_FLUX_TOL_DPKTS

UD_MN2CPU_PKTS

UD_TX_PKTS

UD_TX_BROADPKTS

UD_TX_MULTPKTS

UD_TX_UNIPKTS

UD_TX_OCTS

UD_TX_PAUSE_PKTS

UD_TX_RETRYCNT

UD_TX_COLCNT

UD_TX_LC_PKTS

UD_TX_COLOK_PKTS

UD_TX_RETRY15_PKTS

UD_TX_RETRYN_PKTS

5.2 FEPHY

5.2.1 概述

5.2.2 功能特点

5.2.3 典型应用

5.2.4 使用配置

5.2.4.1 手动配置

5.2.4.2 自协商

速度、双工模式选择与优先级定义

并行检测

重启自协商

5.2.4.3 AUTO—MDIX

5.2.4.4 极性修正

5.2.4.5 PHY地址

5.2.4.6 MII Isolate

5.2.4.7 Power Down模式

5.2.4.8 拓展寄存器访问

专用拓展寄存器访问模式

Clause22拓展寄存器访问模式

5.2.5 FEPHY_BASE寄存器概览

5.2.6 FEPHY_BASE寄存器描述

BMCR

BMSR

OUI_1

OUI_2

ANAR

ANLPAR

ANER

MACR

MAADR

LINK_AN_SR

AUX_CTL

EXPMD

EXPMA

PHY_ADDRESS

6 视频编码

目 录

插图目录

6.1 总概述

6.2 JPGE

6.2.1 概述

6.2.2 特点

6.2.3 功能描述

7 视频解码

目 录

插图目录

表格目录

7.1 VDH

7.1.1 概述

7.1.2 功能描述

7.1.3 工作方式

7.2 JPGD

7.2.1 概述

7.2.2 功能描述

7.2.3 工作方式

7.2.3.1 软硬件划分

7.2.3.2 软硬件交互

8 视频及图形处理

目 录

8.1 VGS

8.1.1 概述

8.1.2 功能描述

8.2 TDE

8.2.1 概述

8.2.2 功能描述

9 视频接口

目 录

插图目录

表格目录

9.1 VDP

9.1.1 概述

9.1.2 功能描述

9.1.3 工作方式

9.1.3.1 时钟配置

9.1.3.2 复位

9.1.3.3 寄存器更新

寄存器更新

9.1.3.4 模拟输出接口

VGA接口

数字输出接口

HDMI接口

9.1.3.5 高清视频层功能

V3(主视频层)多区域读取功能

V1(PIP层)单区域读取功能

显示位置描述

420-422(垂直色度上采样)

IFIR:水平色度上采样

CSC:色彩空间转换

9.1.3.6 图形层功能

解压功能

CSC功能描述

alpha处理

Colorkey功能

预乘功能

G2(鼠标层)功能描述

9.1.3.7 图层叠加处理

9.1.3.8 高清接口处理功能

CLIP功能

H_SHARPEN功能

CSC:色彩空间转换

9.1.3.9 WBC_G4通道回写功能

9.1.3.10 压缩功能

9.1.3.11 中断

垂直时序中断

低带宽中断

图形压缩回写完成中断

无负载中断

9.1.4 寄存器概览

寄存器地址空间

视频层寄存器差异

图形层寄存器差异

接口处理寄存器差异

9.1.5 VDP寄存器描述

VOCTRL

VOINTSTA

VOMSKINTSTA

VOINTMSK

VOAXICTRL

VORDLATENCY

VOWRLATENCY

VOLOWPOWER_CTRL

VORDFRMLTC

VORDFRMCMD

VOWRFRMLTC

VOWRFRMCMD

VO_MUX

VO_MUX_DAC

VO_MUX_TESTSYNC

VO_MUX_TESTDATA

VO_DAC_CTRL

VO_DAC_R_CTRL

VO_DAC_G_CTRL

VO_DAC_B_CTRL

GDC_CORRESP

V3_CTRL

V3_UPD

V3_PRERD

V3_IRESO

V3_ORESO

V3_CBMPARA

V3_CSC_IDC

V3_CSC_ODC

V3_CSC_IODC

V3_CSC_P0

V3_CSC_P1

V3_CSC_P2

V3_CSC_P3

V3_CSC_P4

V3_VSP

V3_VSR

V3_VOFFSET

V3_VBOFFSET

V3_VCOEF0

V3_VCOEF1

V3_VCOEF2

V3_DFPOS

V3_DLPOS

V3_VFPOS

V3_VLPOS

V3_BK

V3_ALPHA

V3_RIMWIDTH

V3_RIMCOL0

V3_RIMCOL1

V3_IFIRCOEF01

V3_IFIRCOEF23

V3_IFIRCOEF45

V3_IFIRCOEF67

V3_P0RESO

V3_P0LADDR

V3_P0CADDR

V3_P0STRIDE

V3_P0VFPOS

V3_P0VLPOS

V3_P0CTRL

V3_MULTI_MODE

V3_FDRFIFOTHD

V3_MRGERRCLR

V3_MRG_ERR

G4_CTRL

G4_UPD

G4_ADDR

G4_STRIDE

G4_IRESO

G4_SFPOS

G4_CBMPARA

G4_CKEYMAX

G4_CKEYMIN

G4_CMASK

G4_DCMP_DBG

G4_DCMP_INTER

G4_DFPOS

G4_DLPOS

G4_CSC_IDC

G4_CSC_ODC

G4_CSC_IODC

G4_CSC_P0

G4_CSC_P1

G4_CSC_P2

G4_CSC_P3

G4_CSC_P4

WBC_G4_CTRL

WBC_G4_UPD

WBC_G4_ADDR

WBC_G4_STRIDE

WBC_G4_ORESO

WBC_G4_YCROP

WBC_G4_CSTR_ERR

WBC_G4_CLR_CSTR_ERR

WBC_G4_GLB_INFO

WBC_G4_FRAME_SIZE

WBC_G4_RC_CFG0

WBC_G4_RC_CFG1

WBC_G4_RC_CFG2

WBC_G4_RC_CFG3

WBC_G4_RC_CFG4

WBC_G4_RC_CFG5

WBC_G4_RC_CFG6

WBC_G4_RC_CFG7

WBC_G4_RC_CFG8

WBC_G4_RC_CFG9

WBC_G4_MAX_ROW_LEN

CBM_BKG2

CBM_MIX2

DHD1_CTRL

DHD1_VSYNC

DHD1_HSYNC1

DHD1_HSYNC2

DHD1_VPLUS

DHD1_PWR

DHD1_VTTHD3

DHD1_VTTHD

DHD1_AFFTHD

DHD1_ABUFTHD

DHD1_DACDET1

DHD1_DACDET2

DHD1_START_POS

DHD1_STATE

INTF_CTRL

INTF_SYNC_INV

INTF_CLIP0_L

INTF_CLIP0_H

INTF_CSC_IDC

INTF_CSC_ODC

INTF_CSC_IODC

INTF_CSC_P0

INTF_CSC_P1

INTF_CSC_P2

INTF_CSC_P3

INTF_CSC_P4

INTF_HSPCFG0

INTF_HSPCFG1

INTF_HSPCFG5

INTF_HSPCFG6

INTF_HSPCFG7

INTF_HSPCFG8

INTF_HSPCFG12

INTF_HSPCFG13

INTF_HSPCFG14

INTF_HSPCFG15

10 音频接口

目 录

插图目录

表格目录

10.1 AIAO

10.1.1 概述

10.1.2 特点

I2S接口

PCM接口

10.1.3 功能描述

典型应用

功能原理

10.1.4 工作方式

时钟门控及时钟配置

软复位

录音工作流程

播放工作流程

10.1.5 AIAO寄存器概览

10.1.6 AIAO寄存器描述

AIAO_INT_ENA

AIAO_INT_STATUS

AIAO_INT_RAW

AIAO_SWITCH_RX_BCLK

AIAO_SWITCH_TX_BCLK

VHB_OUTSTANDING

AIAO_RST_REQ

AIAO_RST_DONE

I2S_CRG_CFG0_00

I2S_CRG_CFG1_00

I2S_CRG_CFG0_08

I2S_CRG_CFG1_08

RX_IF_ATTRI

RX_DSP_CTRL

RX_BUFF_SADDR

RX_BUFF_SIZE

RX_BUFF_WPTR

RX_BUFF_RPTR

RX_BUFF_ALFULL_TH

RX_TRANS_SIZE

RX_WPTR_TMP

RX_INT_ENA

RX_INT_RAW

RX_INT_STATUS

RX_INT_CLR

TX_IF_ATTRI

TX_DSP_CTRL

TX_WS_CNT

TX_BCLK_CNT

TX_BUFF_SADDR

TX_BUFF_SIZE

TX_BUFF_WPTR

TX_BUFF_RPTR

TX_BUFF_ALEMPTY_TH

TX_TRANS_SIZE

TX_RPTR_TMP

TX_INT_ENA

TX_INT_RAW

TX_INT_STATUS

TX_INT_CLR

10.2 AUDIO DAC

10.2.1 功能描述

10.2.2 主要特性

10.2.3 功能描述

播放模式

10.2.1 AUDIO DAC寄存器概览

10.2.2 AUDIO DAC寄存器描述

AUDIO_DAC

AUDIO_DAC1

11 外围设备

目 录

插图目录

表格目录

11.1 I2C

11.1.1 概述

11.1.2 功能描述

11.1.3 功能框图

11.1.4 时序描述原理

标准时序----7bit寻址,写操作

标准时序----7bit寻址,直接读操作

标准时序----10bit寻址,写操作

标准时序----10bit寻址,组合读操作

非标准时序举例

11.1.5 工作方式

11.1.5.1 非DMA方式下的数据传输(中断方式写操作)

11.1.5.2 非DMA方式下的数据传输(查询方式写操作)

11.1.5.3 非DMA方式下的数据传输(中断方式读操作)

11.1.5.4 非DMA方式下的数据传输(查询方式读操作)

11.1.5.5 DMA方式下的数据传输(写操作)

11.1.5.6 DMA方式下的数据传输(读操作)

11.1.5.7 异常处理流程

11.1.6 I2C寄存器概览

11.1.7 I2C寄存器描述

I2C_GLB

I2C_HCNT

I2C_LCNT

I2C_DEV_ADDR

I2C_DATA_BUF

I2C_PATTERN_DATA1

I2C_PATTERN_DATA2

I2C_TX_FIFO

I2C_RX_FIFO

I2C_TIMING_CMD

I2C_LOOP1

I2C_DST1

I2C_LOOP2

I2C_DST2

I2C_LOOP3

I2C_DST3

I2C_TX_WATERMARK

I2C_RX_WATERMARK

I2C_CTRL1

I2C_FIFO_STAT

I2C_INTR_RAW

I2C_INTR_EN

I2C_INTR_STAT

11.2 UART

11.2.1 概述

11.2.2 特点

11.2.3 功能描述

应用框图

功能原理

11.2.4 工作方式

11.2.4.1 波特率配置

11.2.4.2 软复位

11.2.4.3 中断或查询方式下的数据传输

初始化

数据发送

数据接收

11.2.4.4 DMA方式下的数据传输

初始化

数据发送

数据接收

11.2.5 UART寄存器概览

11.2.6 UART寄存器描述

UART_DR

UART_RSR

UART_FR

UART_IBRD

UART_FBRD

UART_LCR_H

UART_CR

UART_IFLS

UART_IMSC

UART_RIS

UART_MIS

UART_ICR

UART_DMACR

11.3 红外接口

11.3.1 概述

11.3.2 特点

11.3.3 功能描述

11.3.3.1 NEC with simple repeat code数据格式

帧格式

码格式

11.3.3.2 NEC with full repeat code数据格式

帧格式

码格式

11.3.3.3 TC9012数据格式

帧格式

码格式

11.3.3.4 SONY的数据格式

帧格式

码格式

11.3.4 工作方式

软复位

寄存器配置实例

11.3.5 IR寄存器概览

11.3.6 IR寄存器描述

IR_EN

IR_CFG

IR_LEADS

IR_LEADE

IR_SLEADE

IR_B0

IR_B1

IR_BUSY

IR_DATAH

IR_DATAL

IR_INT_MASK

IR_INT_STATUS

IR_INT_CLR

IR_START

11.4 GPIO

11.4.1 概述

11.4.2 特点

11.4.3 工作方式

接口复位

通用输入输出

中断操作

11.4.4 GPIO寄存器概览

11.4.5 GPIO寄存器描述

GPIO_DATA

GPIO_DIR

GPIO_IS

GPIO_IBE

GPIO_IEV

GPIO_IE

GPIO_RIS

GPIO_MIS

GPIO_IC

11.5 SATA

11.5.1 概述

11.5.2 特点

11.5.3 信号描述

11.5.4 功能描述

11.5.5 工作方式

11.5.5.1 管脚复用配置

11.5.5.2 时钟门控

11.5.5.3 时钟配置

11.5.5.4 软复位

11.5.5.5 工作模式配置

初始化PHY

初始化协商

操作业务

展频(SSC)寄存器的配置

11.5.6 寄存器概览

SATA寄存器概览

SATA_PORT_CFG寄存器概览

11.5.7 寄存器描述

11.5.7.1 SATA寄存器描述

SATA_GHC_CAP1

SATA_GHC_GHC

SATA_GHC_IS

SATA_GHC_PI

SATA_GHC_VS

SATA_GHC_CCC_CTL

SATA_GHC_CCC_PORTS

SATA_GHC_CAP2

SATA_GHC_BOHC

SATA_PHY_CTL0

SATA_PHY_CTL1

SATA_OOB_CTL

11.5.7.2 SATA_PORT_CFG寄存器描述

SATA_PORT_CLB

SATA_PORT_FB

SATA_PORT_IS

SATA_PORT_IE

SATA_PORT_CMD

SATA_PORT_TFD

SATA_PORT_SIG

SATA_PORT_SSTS

SATA_PORT_SCTL

SATA_PORT_SERR

SATA_PORT_SACT

SATA_PORT_CI

SATA_PORT_SNTF

SATA_PORT_FBS

SATA_PORT_FIFOTH

SATA_PORT_PHYCTL1

SATA_PORT_PHYCTL

SATA_PORT_PHYSTS

SATA_PORT_OUTSTANDING

11.5.8 附录A SATA命令链表格式

11.6 USB 2.0

11.6.1 概述

11.6.2 功能描述

逻辑框图

典型应用

功能特点

工作原理

11.6.3 工作方式

管脚极性控制

时钟门控

撤消复位

工作过程中单独复位port

11.6.4 USB2.0 PHY寄存器

USB2.0 PHY眼图参数调试

USB2.0 PHY寄存器概览

11.6.5 USB2.0 PHY寄存器描述

USB2_PHY0_PRE_EMPHASIS_EN

USB2_PHY0_RCOMP

USB2_PHY1_PRE_EMPHASIS_EN

USB2_PHY1_RCOMP

USB2_PHY0_PRE_EMPHASIS_STRENGTH

USB2_PHY1_PRE_EMPHASIS_STRENGTH

11.6.6 USB 2.0寄存器概览

USB HOST寄存器概览

11.6.7 USB 2.0寄存器描述

11.6.7.1 EHCI寄存器描述

CAPVERSION

HCSPARAMS

HCCPARAMS

USBCMD

USBSTS

USBINTR

FRINDEX

PERIODICLISTBASE

ASYNCLISTBASE

CONFIGFLAG

PORTSC0

PORTSC1

INSNREG00

INSNREG01

INSNREG02

INSNREG03

INSNREG04

INSNREG05

INSNREG06

INSNREG07

11.6.7.2 OHCI寄存器描述

HCREVERSION

HCCONTROL

HCCMDSTS

HCINTSTS

HCINTENABLE

HCINTDISABLE

HCCA

PCED

CHED

CCED

BHED

BCED

DH

FSMPS

FMR

FMNR

PSR

LSTHRESHOLD

RHDA

RHDB

RHSTS

RHPORTSTS0

RHPORTSTS1

A 订购须知

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc