NOIP1SN1300A

PYTHON 1.3/0.5/0.3 MegaPixels

Global Shutter CMOS

Image Sensors

FEATURES

• Size Options:

♦ PYTHON 300: 640 x 480 Active Pixels, 1/4” Optical Format

♦ PYTHON 500: 800 x 600 Active Pixels, 1/3.6” Optical Format

♦ PYTHON 1300: 1280 x 1024 Active Pixels, 1/2” Optical Format

• Data Output Options:

♦ P1−SN/SE/FN: 4 LVDS Data Channels

♦ P2−SN/SE: 10 bit Parallel

♦ P3−SN/SE/FN: 2 LVDS Data Channels

• 4.8 mm x 4.8 mm Low Noise Global Shutter Pixels with In-pixel CDS

• Monochrome (SN), Color (SE) and NIR (FN)

• Zero Row Overhead Time (ZROT) Mode Enabling Higher Frame

• Frame Rate at Full Resolution, 4 LVDS Data Channels

Rate

www.onsemi.com

(P1−SN/SE/FN only)

♦ 210/165 frames per second @ SXGA (ZROT/NROT)

♦ 545/385 frames per second @ SVGA (ZROT/NROT)

♦ 815/545 frames per second @ VGA (ZROT/NROT)

Readout

Parallel CMOS Output

• Frames Rate at Full Resolution (CMOS)

♦ 50/43 Frames per Second @ SXGA (ZROT/NROT)

• On−chip 10−bit Analog−to−Digital Converter (ADC)

• Four/Two/One LVDS High Speed Serial Outputs or

• Random Programmable Region of Interest (ROI)

• Serial Peripheral Interface (SPI)

• Automatic Exposure Control (AEC)

• Phase Locked Loop (PLL)

• High Dynamic Range (HDR) Modes Possible

• Dual Power Supply (3.3 V and 1.8 V)

• −40°C to +85°C Operational Temperature Range

• 48−pin LCC

• Power Dissipation:

♦ 620 mW (P1, 4 LVDS, ZROT)

♦ 420 mW (P1, P3, 2 LVDS, NROT)

♦ 270 mW (P1, P3, 1 LVDS, NROT)

♦ 420 mW (P2, ZROT)

• These Devices are Pb−Free and are RoHS Compliant

APPLICATIONS

• Machine Vision

• Motion Monitoring

• Security

• Barcode Scanning (2D)

Figure 1. PYTHON 1300

DESCRIPTION

The PYTHON 300, PYTHON 500, and PYTHON 1300

image sensors utilize high sensitivity 4.8 mm x 4.8 mm pixels

that support low noise “pipelined” and “triggered” global

shutter readout modes. The sensors support correlated

double sampling (CDS) readout, reducing noise and

increasing dynamic range.

The image sensors have on−chip programmable gain

amplifiers and 10−bit A/D converters. The integration time

and gain parameters can be reconfigured without any visible

image artifact. Optionally the on−chip automatic exposure

control loop (AEC) controls these parameters dynamically.

The image’s black level is either calibrated automatically or

can be adjusted by adding a user programmable offset.

A high level of programmability using a four wire serial

peripheral interface enables the user to read out specific

regions of interest. Up to eight regions can be programmed,

achieving even higher frame rates.

for

in Zero ROT mode

The image data interface of the P1−SN/SE/FN devices

consists of four LVDS lanes, enabling frame rates up to 210

frames per second

the

PYTHON 1300. Each channel runs at 720 Mbps. A separate

synchronization channel containing payload information is

provided to facilitate the image reconstruction at the

receiving end. The P2−SN/SE devices provide a parallel

CMOS output interface at reduced frame rate. The

P3−SN/SE/FN devices are the same as the P1−SN/SE/FN

but with only two of the four LVDS data channels enabled,

facilitating frame rates of 90 frames per second in Normal

ROT for the PYTHON 1300.

© Semiconductor Components Industries, LLC, 2016

December, 2016 − Rev. 3

1

Publication Order Number:

NOIP1SN1300A/D

�

The devices are provided in a 48−pin LCC package and are available in monochrome, Bayer color, and extended

NOIP1SN1300A

near−infrared (NIR) configurations.

ORDERING INFORMATION

Part Number

PYTHON 1300

Description

Package

NOIP1SN1300A−QDI

1.3 Megapixel, Monochrome, LVDS Output

NOIP1SE1300A−QDI

1.3 Megapixel, Bayer Color, LVDS Output

NOIP1FN1300A−QDI

1.3 Megapixel, Monochrome with enhanced NIR, LVDS Output

NOIP2SN1300A−QDI

1.3 Megapixel, Monochrome, CMOS (parallel) Output

NOIP2SE1300A−QDI

1.3 Megapixel, Bayer Color, CMOS (parallel) Output

NOIP1SN1300A−QTI

1.3 Megapixel, Monochrome, LVDS Output, Protective Foil

NOIP1SE1300A−QTI

1.3 Megapixel, Bayer Color, LVDS Output, Protective Foil

NOIP1FN1300A−QTI

1.3 Megapixel, Monochrome with enhanced NIR, LVDS Output, Protective Foil

NOIP3SN1300A−QDI

1.3 Megapixel, 2 LVDS Outputs, Monochrome

NOIP3FN1300A−QDI

1.3 Megapixel, 2 LVDS Outputs, NIR enhanced Monochrome

NOIP3SE1300A−QDI

1.3 Megapixel, 2 LVDS Outputs, Color

NOIP3SN1300A−QTI

1.3 Megapixel, 2 LVDS Outputs, Monochrome, Protective Foil

NOIP3FN1300A−QTI

1.3 Megapixel, 2 LVDS Outputs, NIR enhanced Monochrome, Protective Foil

NOIP3SE1300A−QTI

1.3 Megapixel, 2 LVDS Outputs, Color, Protective Foil

PYTHON 500

NOIP1SN0500A−QDI

0.5 Megapixel, Monochrome, LVDS Output

NOIP1SE0500A−QDI

0.5 Megapixel, Bayer Color, LVDS Output

NOIP1FN0500A−QDI

0.5 Megapixel, Monochrome with enhanced NIR, LVDS Output

NOIP1SN0500A−QTI

0.5 Megapixel, Monochrome, LVDS Output, Protective Foil

NOIP1SE0500A−QTI

0.5 Megapixel, Bayer Color, LVDS Output, Protective Foil

NOIP1FN0500A−QTI

0.5 Megapixel, Monochrome with enhanced NIR, LVDS Output, Protective Foil

PYTHON 300

NOIP1SN0300A−QDI

0.3 Megapixel, Monochrome, LVDS Output

NOIP1SE0300A−QDI

0.3 Megapixel, Bayer Color, LVDS Output

NOIP1FN0300A−QDI

0.3 Megapixel, Monochrome with enhanced NIR, LVDS Output

NOIP1SN0300A−QTI

0.3 Megapixel, Monochrome, LVDS Output, Protective Foil

NOIP1SE0300A−QTI

0.3 Megapixel, Bayer Color, LVDS Output, Protective Foil

NOIP1FN0300A−QTI

0.3 Megapixel, Monochrome with enhanced NIR, LVDS Output, Protective Foil

48−pin LCC

48−pin LCC

48−pin LCC

The P1−SN/SE/FN base part references the mono, color and NIR enhanced versions of the 4 LVDS interface; the P2−SN/SE

base part references the mono and color versions of the CMOS interface; the P3−SN/SE/FN base part references the mono,

color and NIR enhanced version of the 2 LVDS interface. More details on the part number coding can be found at

http://www.onsemi.com/pub_link/Collateral/TND310−D.PDF

Production Package Mark

Line 1: NOIPyxxRRRRA where y is either “1” for 4 LVDS Outputs, “2” for CMOS Parallel Output, “3” for 2 LVDS Outputs,

where xx denotes mono micro lens (SN) or color micro lens (SE) or NIR micro lens (FN)

RRRR is the resolution (1300), (0500) or (0300)

Line 2: −QDI (without protective foil), −QTI (with protective foil)

Line 3: AWLYYWW where AWL is PRODUCTION lot traceability, YYWW is the 4−digit date code

www.onsemi.com

2

�

NOIP1SN1300A

SPECIFICATIONS

Key Specifications

Table 1. GENERAL SPECIFICATIONS

Table 2. ELECTRO−OPTICAL SPECIFICATIONS

Parameter

Pixel type

Shutter type

Frame rate

Zero ROT/

Normal ROT

mode

Master clock

Windowing

ADC resolution

LVDS outputs

CMOS outputs

Data rate

Power

dissipation

(10−bit mode)

Specification

In−pixel CDS. Global shutter pixel

architecture

Pipelined and triggered global shutter

P1−SN/SE/FN:

PYTHON 300: 815/545 fps

PYTHON 500: 545/385 fps

PYTHON 1300: 210/165 fps

P2−SN/SE: 50/43 fps

P3−SN/SE/FN: NA/90 fps

P1, P3−SN/SE/FN:

72 MHz when PLL is used,

360 MHz (10−bit) / 288 MHz (8−bit)

when PLL is not used

P2−SN/SE: 72 MHz

8 Randomly programmable windows. Nor-

mal, sub−sampled and binned readout

modes

10−bit, 8−bit (Note 1)

P1−SN/SE/FN: 4/2/1 data + sync + clock

P3−SN/SE/FN: 2/1 data + sync + clock

P2−SN/SE: 10−bit parallel output,

frame_valid, line_valid, clock

P1−SN/SE/FN:

4 x 720 Mbps (10−bit) /

4 x 576 Mbps (8−bit)

P2−SN/SE: 72 Mhz

P3−SN/SE/FN: 2 x 720 Mbps (10−bit)

P1−SN/SE/FN: 620 mW (4 data channels)

P1, P3−SN/SE/FN: 420 mW (2 data ch.)

P1, P3−SN/SE/FN: 270 mW (1 data ch.)

P2−SN/SE: 420 mW

Parameter

Active pixels

Pixel size

Conversion gain

Dark temporal noise

Responsivity

at 550 nm

Parasitic Light

Sensitivity (PLS)

Full Well Charge

Quantum Efficiency

at 550 nm

Pixel FPN

PRNU

MTF

PSNL at 20°C

Dark signal at 20°C

Dynamic Range

Signal to Noise Ratio

(SNR max)

Specification

PYTHON 300: 640 (H) x 480 (V)

PYTHON 500: 800 (H) x 600 (V)

PYTHON 1300: 1280 (H) x 1024 (V)

4.8 mm x 4.8 mm

0.096 LSB10/e−

140 mV/e−

< 9 e− (Normal ROT, 1x gain)

< 7 e− (Normal ROT, 2x gain)

7.7 V/lux.s

<1/8000

10000 e−

56%

< 1.0 LSB10

< 2% or 10 LSB10 on half scale

response of 525LSB10

68% @ 535 nm − X−dir & Y−dir

120 LSB10/s, 1200 e−/s

5 e−/s, 0.5 LSB10/s

> 60 dB in global shutter mode

40 dB

Package type

48−pin LCC

Table 3. RECOMMENDED OPERATING RATINGS (Note 2)

Symbol

TJ

Operating temperature range

Description

Min

−40

Max

85

Unit

°C

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond

the Recommended Operating Ranges limits may affect device reliability.

Table 4. ABSOLUTE MAXIMUM RATINGS (Notes 3 and 4)

Symbol

ABS (1.8 V supply group)

ABS (3.3 V supply group)

TS

Electrostatic discharge (ESD)

LU

Parameter

ABS rating for 1.8 V supply group

ABS rating for 3.3 V supply group

ABS storage temperature range

ABS storage humidity range at 85°C

Human Body Model (HBM): JS−001−2010

Charged Device Model (CDM): JESD22−C101

Latch−up: JESD−78

Min

–0.5

–0.5

−40

2000

500

100

Max

2.2

4.3

+150

85

Unit

V

V

°C

%RH

V

mA

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. The ADC is 11−bit, down−scaled to 10−bit. The PYTHON uses a larger word−length internally to provide 10−bit on the output.

2. Operating ratings are conditions in which operation of the device is intended to be functional.

3. ON Semiconductor recommends that customers become familiar with, and follow the procedures in JEDEC Standard JESD625−A. Refer

to Application Note AN52561. Long term exposure toward the maximum storage temperature will accelerate color filter degradation.

4. Caution needs to be taken to avoid dried stains on the underside of the glass due to condensation. The glass lid glue is permeable and can

absorb moisture if the sensor is placed in a high % RH environment.

www.onsemi.com

3

�

NOIP1SN1300A

Table 5. ELECTRICAL SPECIFICATIONS

Boldface limits apply for TJ = TMIN to TMAX, all other limits TJ = +30°C. (Notes 5, 6, 7, 8 and 9)

Parameter

Description

Min

Typ

Max

Unit

Power Supply Parameters − P1 − SN/SE/FN LVDS (ZROT)

(NOTE: All ground pins (gnd_18, gnd_33, gnd_colpc) should be connected to an external 0 V ground reference.)

vdd_33

Idd_33

vdd_18

Idd_18

vdd_pix

Idd_pix

Ptot

Supply voltage, 3.3 V

Current consumption 3.3 V supply

Supply voltage, 1.8 V

Current consumption 1.8 V supply

Supply voltage, pixel

Current consumption pixel supply

Total power consumption at vdd_33 = 3.3 V, vdd_18 = 1.8 V

P1−SN/SE/FN, 4 LVDS, ZROT

3.2

1.7

3.25

3.3

140

1.8

80

3.3

5

620

Pstby_lp

Power consumption in low power standby mode

Popt

Power consumption at lower pixel rates

Configurable

Power Supply Parameters − P3 − SN/SE/FN LVDS (NROT)

(NOTE: All ground pins (gnd_18, gnd_33, gnd_colpc) should be connected to an external 0 V ground reference.)

vdd_33

Idd_33

vdd_18

Idd_18

vdd_pix

Idd_pix

Ptot

Supply voltage, 3.3 V

Current consumption 3.3 V supply (2 / 1 LVDS)

Supply voltage, 1.8 V

Current consumption 1.8 V supply (2 / 1 LVDS)

Supply voltage, pixel

Current consumption pixel supply (2 / 1 LVDS)

Total power consumption at vdd_33 = 3.3 V, vdd_18 = 1.8 V

P3−SN/SE/FN, 2 LVDS, NROT

P3−SN/SE/FN, 1 LVDS, NROT

3.2

1.7

3.25

3.3

95 / 55

1.8

55 / 45

3.3

2 / 1

420

270

3.4

1.9

3.35

50

3.4

1.9

3.35

V

mA

V

mA

V

mA

mW

mW

V

mA

V

mA

V

mA

mW

Pstby_lp

Power consumption in low power standby mode

50

mW

Popt

Power consumption at lower pixel rates

Configurable

Power Supply Parameters − P2−SN/SE CMOS

vdd_33

Idd_33

vdd_18

Idd_18

vdd_pix

Idd_pix

Ptot

Supply voltage, 3.3 V

Current consumption 3.3 V supply

Supply voltage, 1.8 V

Current consumption 1.8 V supply

Supply voltage, pixel

Current consumption pixel supply

Total power consumption

Pstby_lp

Power consumption in low power standby mode

3.2

1.7

3.25

3.3

120

1.8

10

3.3

1

420

3.4

1.9

3.35

50

V

mA

V

mA

V

mA

mW

mW

Popt

Power consumption at lower pixel rates

Configurable

I/O − P1−SN/SE/FN, P3−SN/SE/FN LVDS (EIA/TIA−644): Conforming to standard/additional specifications and deviations listed

fserdata

Data rate on data channels

DDR signaling − 4 data channels, 1 synchronization channel

720

Mbps

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. All parameters are characterized for DC conditions after thermal equilibrium is established.

6. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is

recommended that normal precautions be taken to avoid application of any voltages higher than the maximum rated voltages to this high

impedance circuit.

7. Minimum and maximum limits are guaranteed through test and design.

8. Refer to ACSPYTHON1300 available at the Image Sensor Portal for detailed acceptance criteria specifications.

9. For power supply management recommendations, please refer to Application Note AND9158.

www.onsemi.com

4

�

NOIP1SN1300A

Table 5. ELECTRICAL SPECIFICATIONS

Boldface limits apply for TJ = TMIN to TMAX, all other limits TJ = +30°C. (Notes 5, 6, 7, 8 and 9)

Parameter

Description

Min

Typ

fserclock

Vicm

Tccsk

Clock rate of output clock

Clock output for mesochronous signaling

LVDS input common mode level

Channel to channel skew (Training pattern allows per channel

skew correction)

0.3

1.25

Max

360

1.8

50

I/O − P2−SN/SE CMOS (JEDEC− JESD8C−01): Conforming to standard/additional specifications and deviations listed

fpardata

Cout

tr

tf

Data rate on parallel channels (10−bit)

Output load (only capacitive load)

Rise time (10% to 90% of input signal)

Fall time (10% to 90% of input signal)

Electrical Interface − P1 − SN/SE/FN LVDS

fin

fin

tidc

tj

ratspi

(= fin/fspi)

Input clock rate when PLL used

Input clock when LVDS input used

Input clock duty cycle when PLL used

Input clock jitter

10−bit (4 LVDS channels), PLL used

10−bit (2 LVDS channels), PLL used

10−bit (1 LVDS channel), PLL used

10−bit (4 LVDS channels), LVDS input used

10−bit (2 LVDS channels), LVDS input used

10−bit (1 LVDS channel), LVDS input used

8−bit (4 LVDS channels), PLL used

8−bit (2 LVDS channels), PLL used

8−bit (1 LVDS channel), PLL used

8−bit (4 LVDS channels), LVDS input used

8−bit (2 LVDS channels), LVDS input used

8−bit (1 LVDS channel), LVDS input used

Electrical Interface − P2−SN/SE CMOS

fin

tidc

tj

ratspi

(= fin/fspi)

Input clock rate

Input clock duty cycle

Input clock jitter

10−bit, PLL bypassed

Electrical Interface − P3 − SN/SE/FN LVDS

fin

fin

tidc

tj

Input clock rate when PLL used

Input clock when LVDS input used

Input clock duty cycle when PLL used

Input clock jitter

4.5

3.5

50

50

2.5

2

45

6

12

24

30

60

120

6

12

24

24

48

96

45

24

45

50

72

10

6.5

5

72

360

55

20

72

55

20

72

360

55

20

Unit

MHz

V

ps

Mbps

pF

ns

ns

MHz

MHz

%

ps

MHz

%

ps

MHz

MHz

%

ps

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. All parameters are characterized for DC conditions after thermal equilibrium is established.

6. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is

recommended that normal precautions be taken to avoid application of any voltages higher than the maximum rated voltages to this high

impedance circuit.

7. Minimum and maximum limits are guaranteed through test and design.

8. Refer to ACSPYTHON1300 available at the Image Sensor Portal for detailed acceptance criteria specifications.

9. For power supply management recommendations, please refer to Application Note AND9158.

www.onsemi.com

5

�

NOIP1SN1300A

Table 5. ELECTRICAL SPECIFICATIONS

Boldface limits apply for TJ = TMIN to TMAX, all other limits TJ = +30°C. (Notes 5, 6, 7, 8 and 9)

Parameter

Description

Min

Typ

Max

Unit

ratspi

(= fin/fspi)

10−bit (2 LVDS channels), PLL used

10−bit (1 LVDS channel), PLL used

10−bit (2 LVDS channels), LVDS input used

10−bit (1 LVDS channel), LVDS input used

Frame Specifications − P1−SN/SE/FN−LVDS (ZROT)

12

24

60

120

Frame rate at full resolution

Xres x Yres = 1024 x 1024

Xres x Yres = 800 x 600

Xres x Yres = 640 x 480

Xres x Yres = 512 x 512

Xres x Yres = 256 x 256

Maximum

Normal ROT

Zero ROT

Max

165

195

385

545

580

210

260

545

815

925

1400

2235

Units

fps

fps

fps

fps

fps

fps

Pixel rate (4 channels at 72 Mpix/s)

288

Mpix/s

fps

fps_roi1

fps_roi2

fps_roi3

fps_roi4

fps_roi5

fpix

Frame Specifications − P2−SN/SE CMOS

fps

Frame rate at full resolution

Frame Specifications − P3−SN/SE/FN LVDS (NROT)

fps

fps_roi1

fps_roi2

fps_roi3

fps_roi4

fps_roi5

fpix

Frame rate at full resolution

Xres x Yres = 1024 x 1024

Xres x Yres = 800 x 600

Xres x Yres = 640 x 480

Xres x Yres = 512 x 512

Xres x Yres = 256 x 256

Maximum

Normal ROT

Zero ROT

43

50

Maximum

2 LVDS

1 LVDS

Max

90

110

230

340

375

1110

45

55

120

185

205

660

Units

fps

Units

fps

fps

fps

fps

fps

fps

Pixel rate (4 channels at 72 Mpix/s)

144

Mpix/s

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. All parameters are characterized for DC conditions after thermal equilibrium is established.

6. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is

recommended that normal precautions be taken to avoid application of any voltages higher than the maximum rated voltages to this high

impedance circuit.

7. Minimum and maximum limits are guaranteed through test and design.

8. Refer to ACSPYTHON1300 available at the Image Sensor Portal for detailed acceptance criteria specifications.

9. For power supply management recommendations, please refer to Application Note AND9158.

www.onsemi.com

6

�

NOIP1SN1300A

Color Filter Array

The PYTHON color sensors are processed with a Bayer RGB color pattern as shown in Figure 2. Pixel (0,0) has a red filter

situated to the bottom left.

Y

Gb

Gr

pixel (0;0)

X

Figure 2. Color Filter Array for the Pixel Array

Quantum Efficiency

]

%

[

E

Q

Red

Gr

Gb

Blue

Mono

60.0%

50.0%

40.0%

30.0%

20.0%

10.0%

0.0%

300

400

500

600

700

800

900

1000

1100

Wavelength [nm]

Figure 3. Quantum Efficiency Curve for Mono and Color

www.onsemi.com

7

�

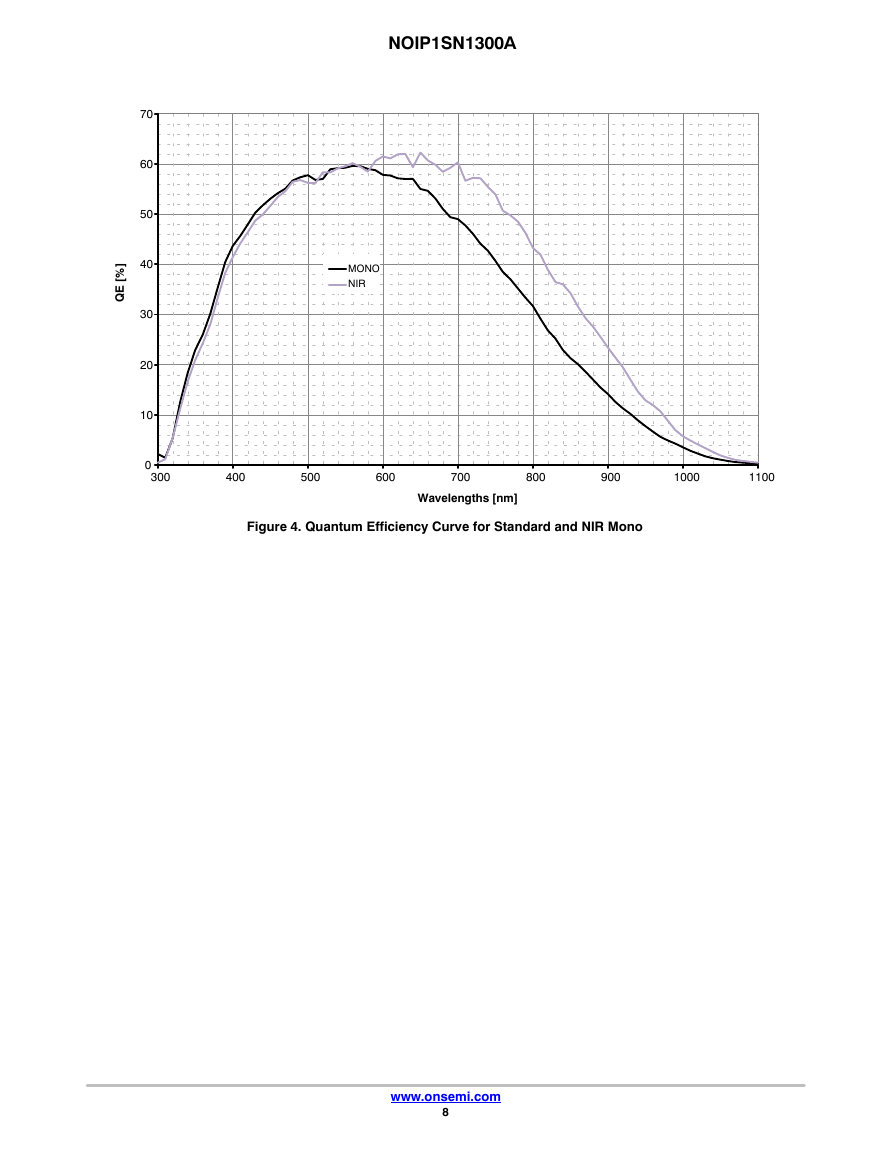

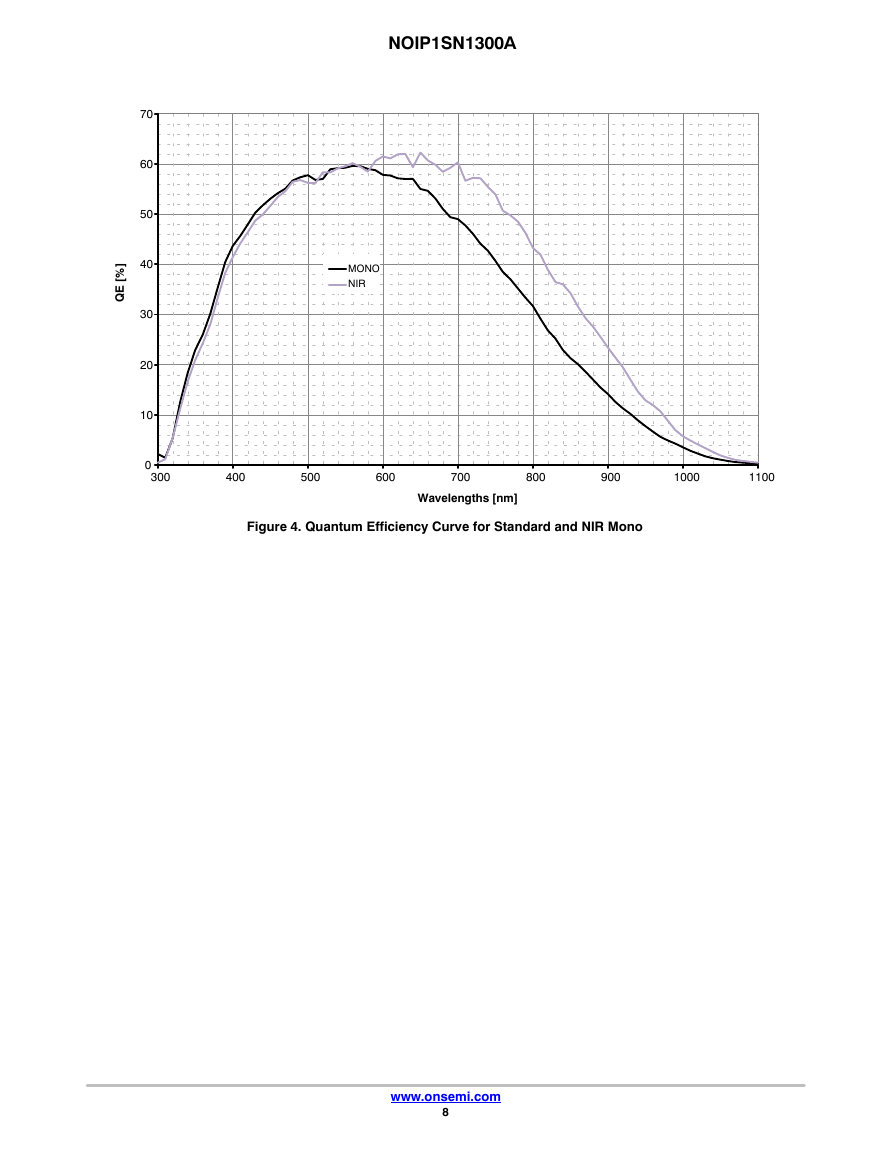

]

%

[

E

Q

70

60

50

40

30

20

10

0

300

NOIP1SN1300A

MONO

NIR

400

500

600

700

800

900

1000

1100

Wavelengths [nm]

Figure 4. Quantum Efficiency Curve for Standard and NIR Mono

www.onsemi.com

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc