中国科技论文在线

http://www.paper.edu.cn

基于 FPGA 的 HDB3 编译码器设计

吴京京*

(中国矿业大学信息与电气工程学院,江苏 徐州 221008)

摘要:为了实现在 FPGA 中对 HDB3 编译码器的设计,本文采用插 V、补 B 方法以及单极

性变双极性控制模块实现了编码器部分,并采用双极性变单极性以及扣 V、扣 B 方法实现

了译码器部分。通过在 CD74HC4052 芯片中进行仿真,不仅实现了 HDB3 编译码功能,而

且还能实现基带信号在基带信道中直接传输与提取,同时能很好地提取定时信号。仿真结果

表明了该设计的可行性、稳定性以及可靠性。

关键词: 电子信息;FPGA;HDB3;编译码

中图分类号:TN9

Design of a HDB3 Encoder and Decoder Based on FPGA

(Information and Electrical Engineer School,China University of Mining and Technology, Jiangsu

WU Jingjing

Xuzhou 221008)

Abstract: In order to achieve the design of a HDB3 encoder and decoder based on FPGA. This thesis

realizes the encoder part using insert V, complement B method and unipolar-bipolar conversion. And it

also realizes the decoder part using bipolar -unipolar conversion and deduct V, deduct B method. By

CD74HC4052 chip simulation, it not only realizes the HDB3 encoding and decoding functions, but

also achieves the directly transmission and extraction of the baseband signal in the baseband channel, at

the same time can well extract the timing signal. The simulation results show that the design is stable,

reliable and feasible.

Key words: Electronic Information;FPGA;HDB3;Encoding;Decoding

0 引言

数字基带信号的传输是数字通信系统的重要组成部分。在数字通信中,有些场合可不经

过载波调制和解调过程,而对基带信号进行直接传输。和常用的 NRZ 码(Non—Return Zero,

非归零码)相比,HDB3 码消除了直流成分,具有时钟恢复和更好的抗干扰性能,这使它更

适合于长距离信道传输。同时,HDB3 码具有较强的检错能力,当数据序列用 HDB3 码传输

时,若传输过程中出现单个误码,其极性交替变化规律将受到破坏,因而在接收端根据 HDB3

码这一独特规律特性,可检出错误并纠正错误。如果采用 AMI 码的信号交替反转,可能出

现四连零现象,这不利于接收端的定时信号提取。而 HDB3 码因其无直流成份、低频成份

少和连 0 个数最多不超过三个等特点,对定时信号的恢复十分有利,并已成为 CCITT 协会

推荐使用的基带传输码型之一。目前,HDB3 码主要由专用集成电路及相应匹配的外围中小

规模集成芯片来实现。 本文提供了一种利用现代 EDA 技术,以 CD74HC4052 为硬件平台,

以 Max+plusII 为软件平台,以 VHDL 为开发工具,适合于 FPGA 实现的 HDB3 编码器的设

计方案。

作者简介:吴京京(1986),女,硕士研究生,通信与信息系统. E-mail: sakurawjj@163.com

- 1 -

�

中国科技论文在线

1 HDB3 编码器的 FPGA 设计

1.1 HDB3 编码器的设计流程

http://www.paper.edu.cn

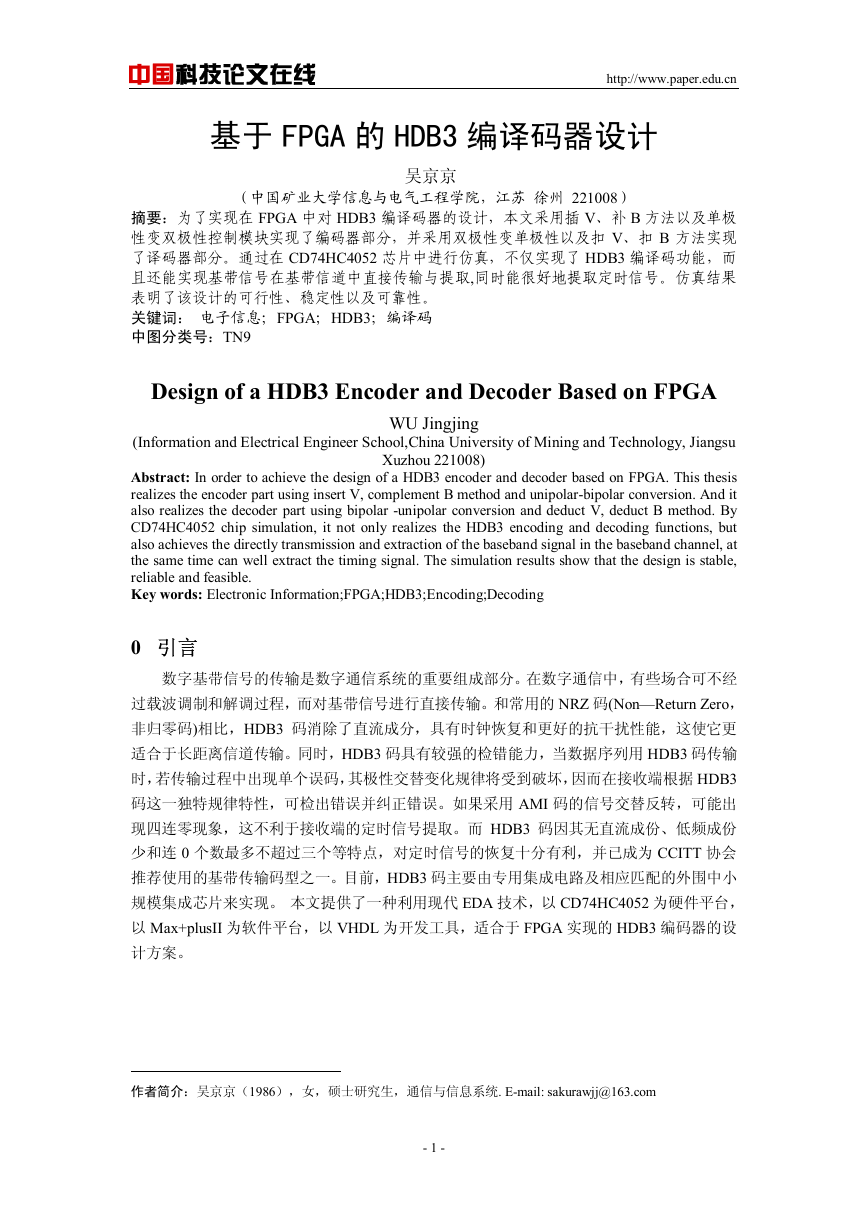

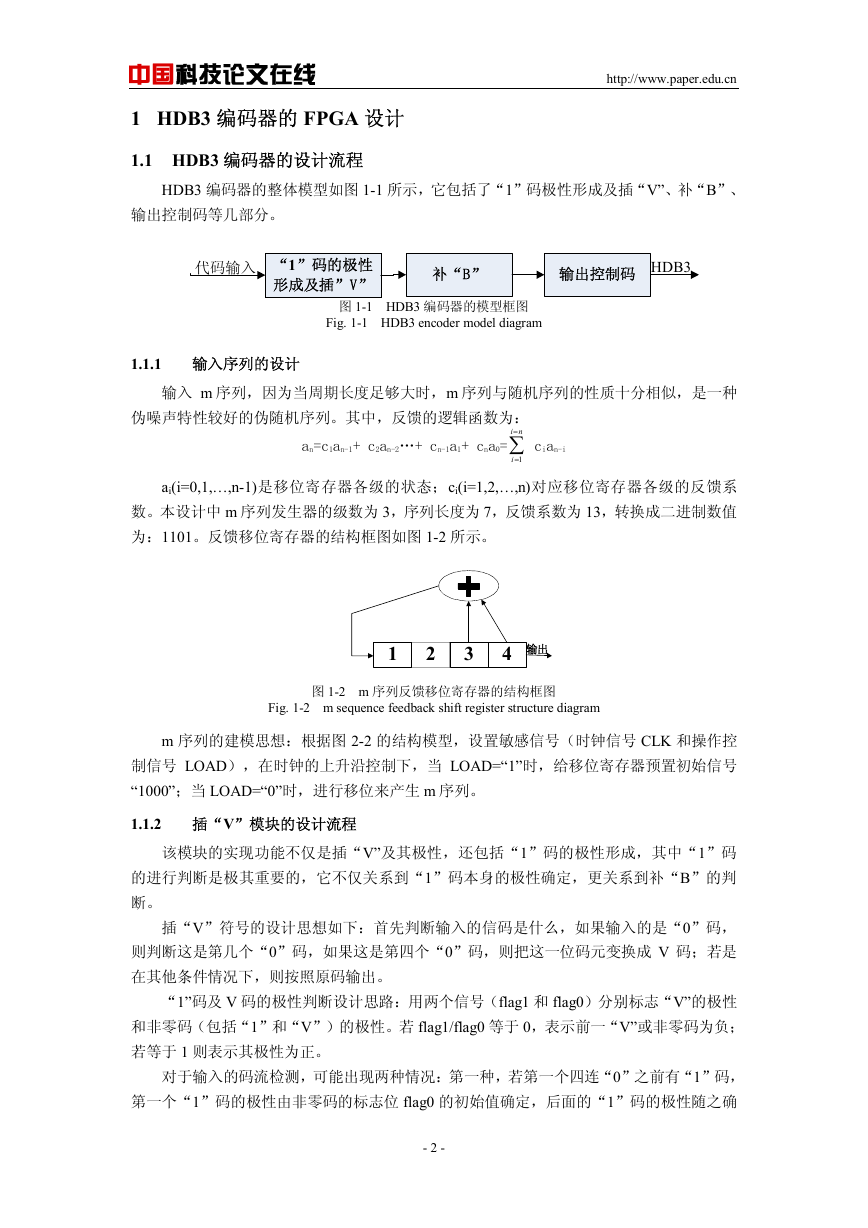

HDB3 编码器的整体模型如图 1-1 所示,它包括了“1”码极性形成及插“V”、补“B”、

输出控制码等几部分。

代码输入

“1”码的极性

形成及插”V”

补“B”

输出控制码

图 1-1 HDB3 编码器的模型框图

Fig. 1-1 HDB3 encoder model diagram

HDB3

1.1.1 输入序列的设计

输入 m 序列,因为当周期长度足够大时,m 序列与随机序列的性质十分相似,是一种

伪噪声特性较好的伪随机序列。其中,反馈的逻辑函数为:

an=c1an-1+ c2an-2…+ cn-1a1+ cna0=∑=

ni

i 1

=

cian-i

ai(i=0,1,…,n-1)是移位寄存器各级的状态;ci(i=1,2,…,n)对应移位寄存器各级的反馈系

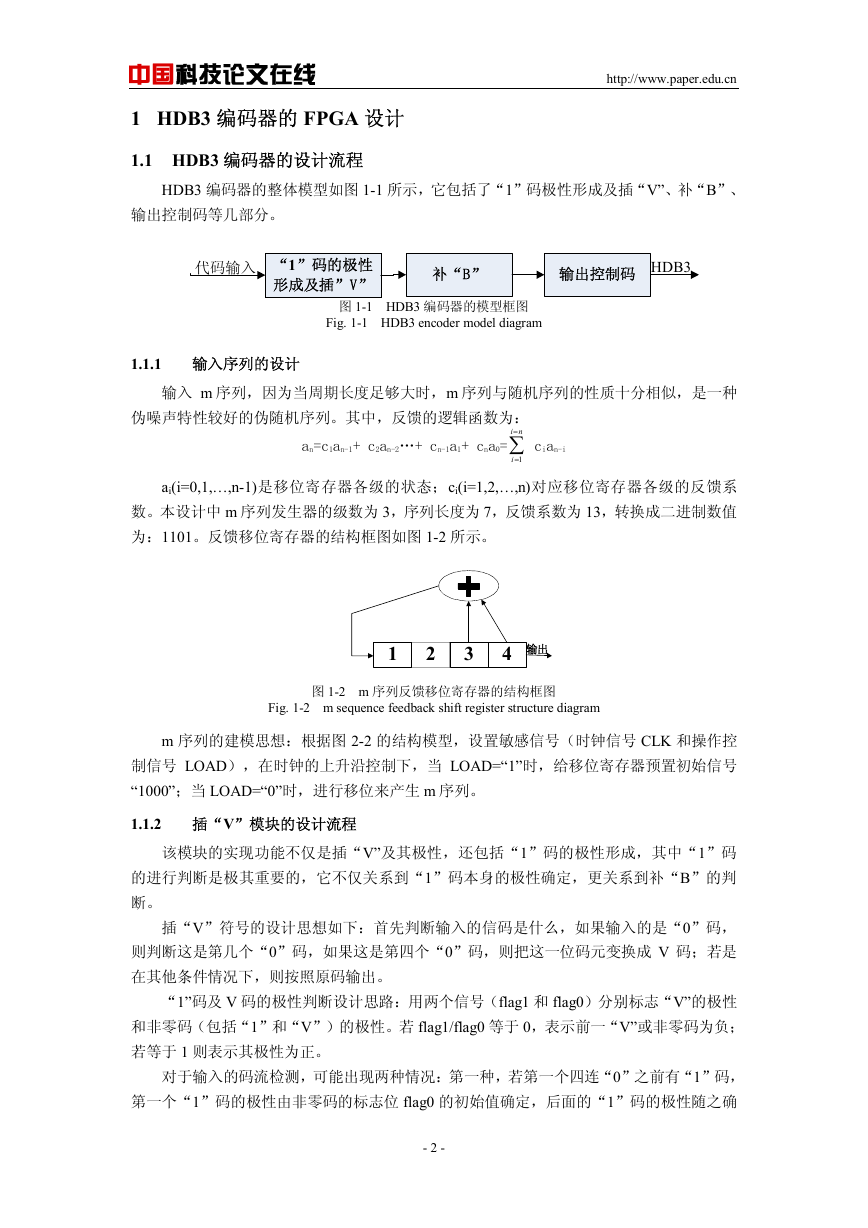

数。本设计中 m 序列发生器的级数为 3,序列长度为 7,反馈系数为 13,转换成二进制数值

为:1101。反馈移位寄存器的结构框图如图 1-2 所示。

3

4 输出

1

2

图 1-2 m 序列反馈移位寄存器的结构框图

Fig. 1-2 m sequence feedback shift register structure diagram

m 序列的建模思想:根据图 2-2 的结构模型,设置敏感信号(时钟信号 CLK 和操作控

制信号 LOAD),在时钟的上升沿控制下,当 LOAD=“1”时,给移位寄存器预置初始信号

“1000”;当 LOAD=“0”时,进行移位来产生 m 序列。

1.1.2 插“V”模块的设计流程

该模块的实现功能不仅是插“V”及其极性,还包括“1”码的极性形成,其中“1”码

的进行判断是极其重要的,它不仅关系到“1”码本身的极性确定,更关系到补“B”的判

断。

插“V”符号的设计思想如下:首先判断输入的信码是什么,如果输入的是“0”码,

则判断这是第几个“0”码,如果这是第四个“0”码,则把这一位码元变换成 V 码;若是

在其他条件情况下,则按照原码输出。

“1”码及 V 码的极性判断设计思路:用两个信号(flag1 和 flag0)分别标志“V”的极性

和非零码(包括“1”和“V”)的极性。若 flag1/flag0 等于 0,表示前一“V”或非零码为负;

若等于 1 则表示其极性为正。

对于输入的码流检测,可能出现两种情况:第一种,若第一个四连“0”之前有“1”码,

第一个“1”码的极性由非零码的标志位 flag0 的初始值确定,后面的“1”码的极性随之确

- 2 -

�

中国科技论文在线

http://www.paper.edu.cn

定,第一个“V”的极性由前“-1”码的极性决定,由于 V 码的极性是自行交替的,所以后

面 V 码的极性均可确定。第二种,若第一个四连 0 前没有“1”码,则第一个 V 码的极性由

它的标识信号的初始值确定。后边出现的“1”码和 V 码的极性均由第一个 V 码的极性确定。

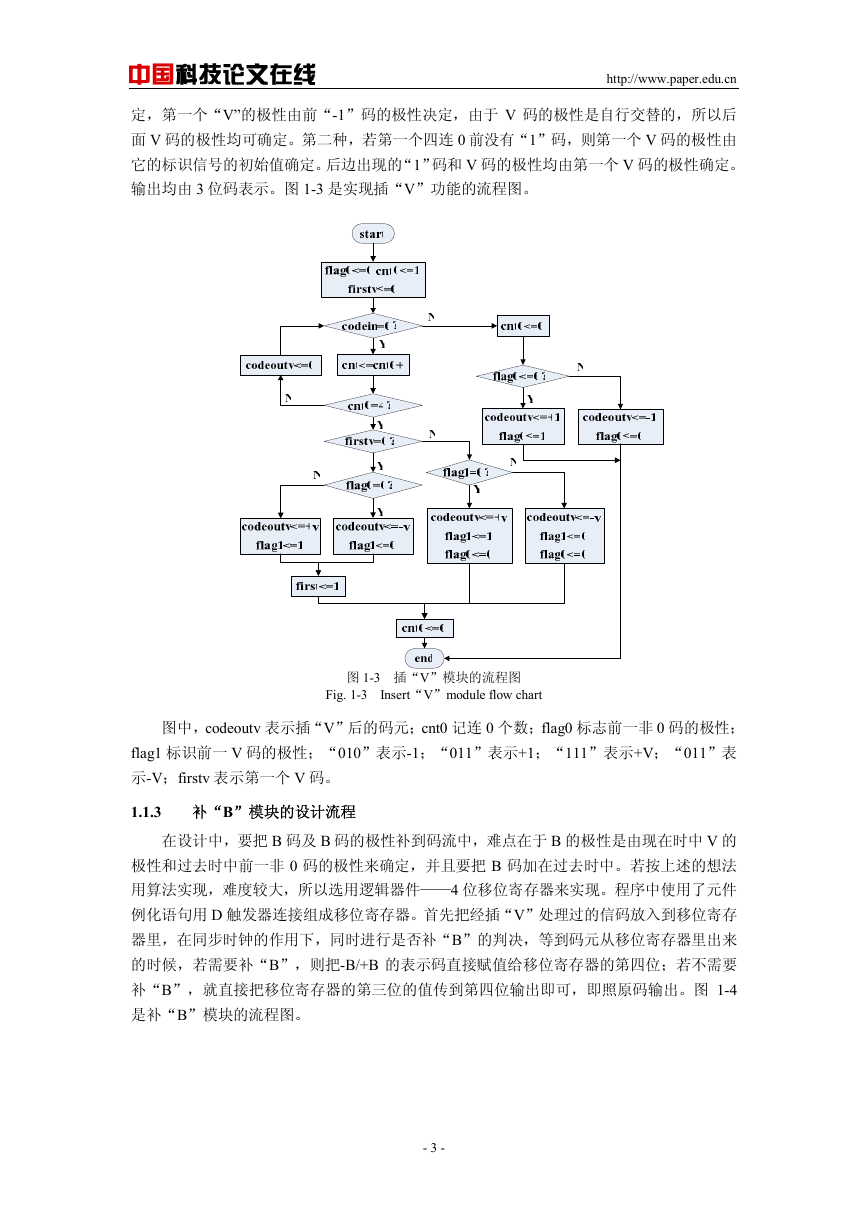

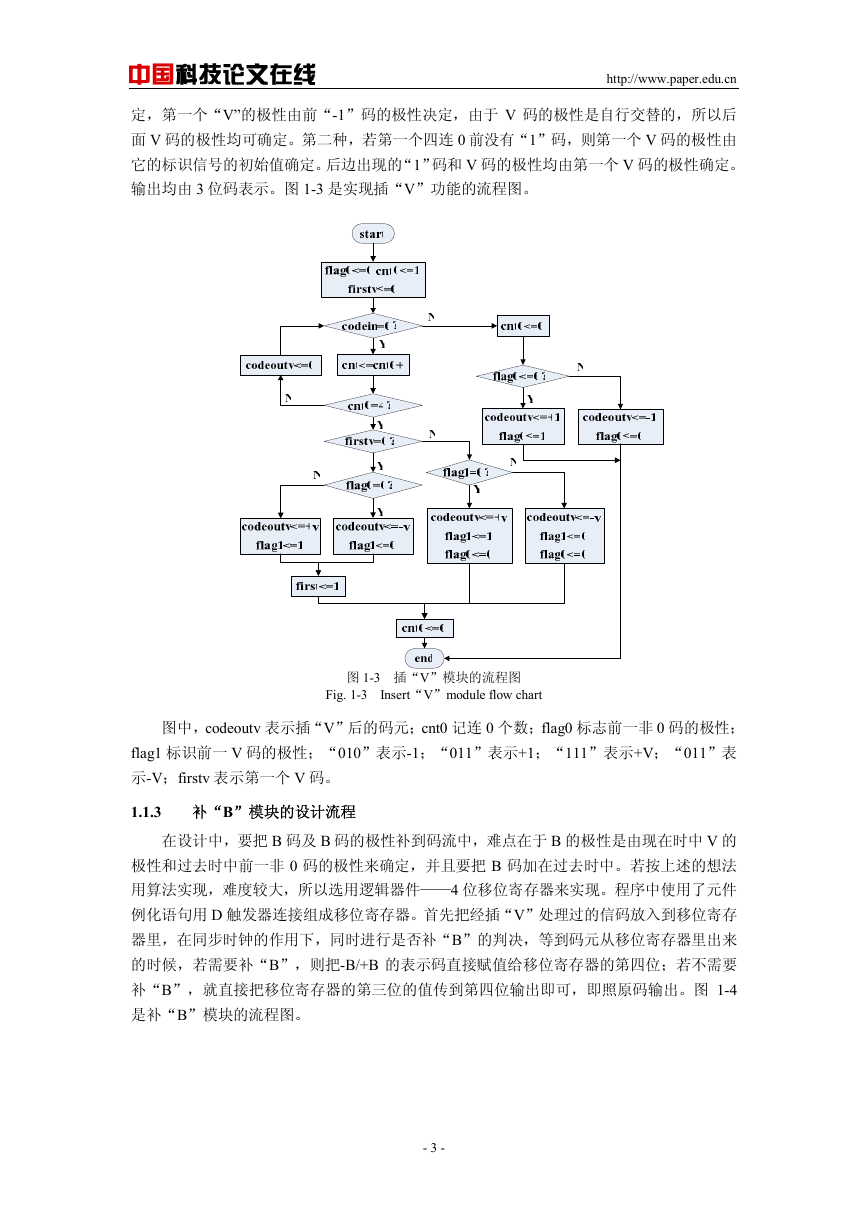

输出均由 3 位码表示。图 1-3 是实现插“V”功能的流程图。

图 1-3 插“V”模块的流程图

Fig. 1-3 Insert“V”module flow chart

图中,codeoutv 表示插“V”后的码元;cnt0 记连 0 个数;flag0 标志前一非 0 码的极性;

flag1 标识前一 V 码的极性;“010”表示-1;“011”表示+1;“111”表示+V;“011”表

示-V;firstv 表示第一个 V 码。

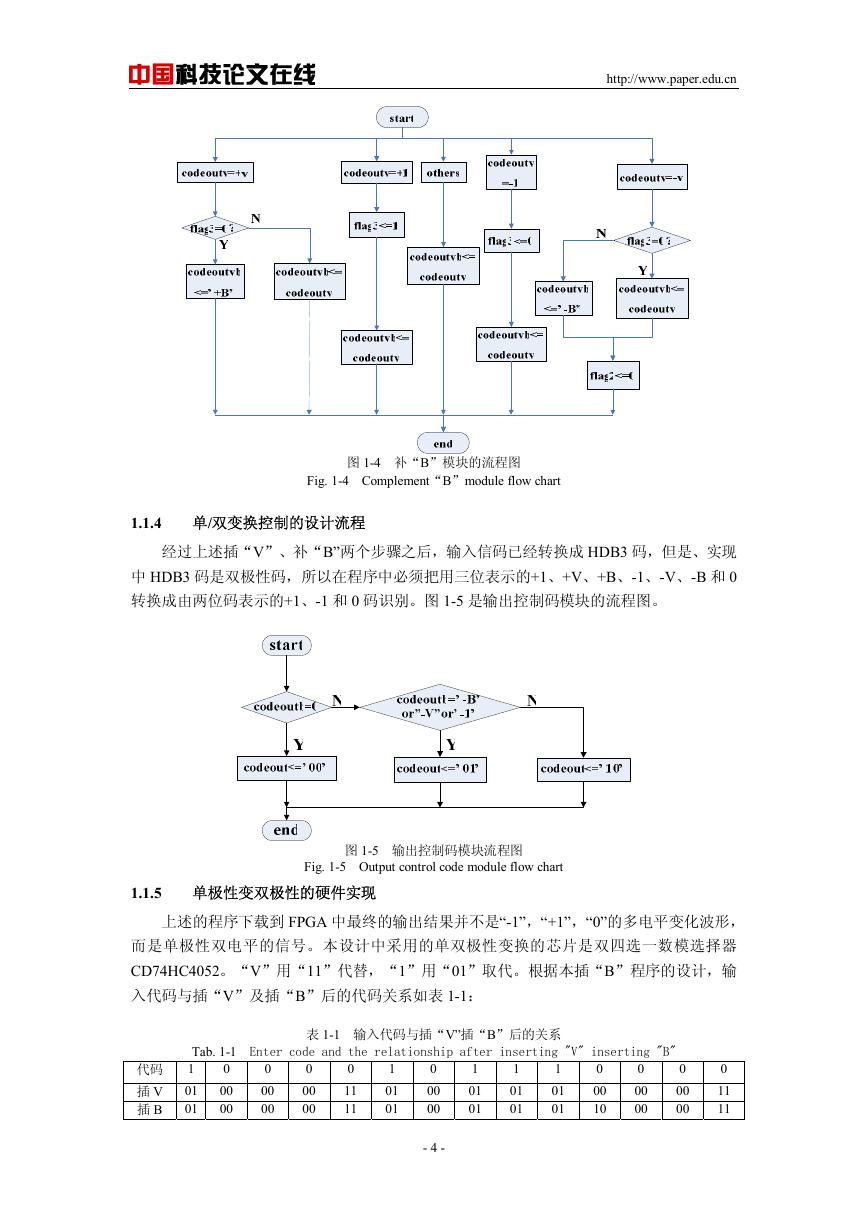

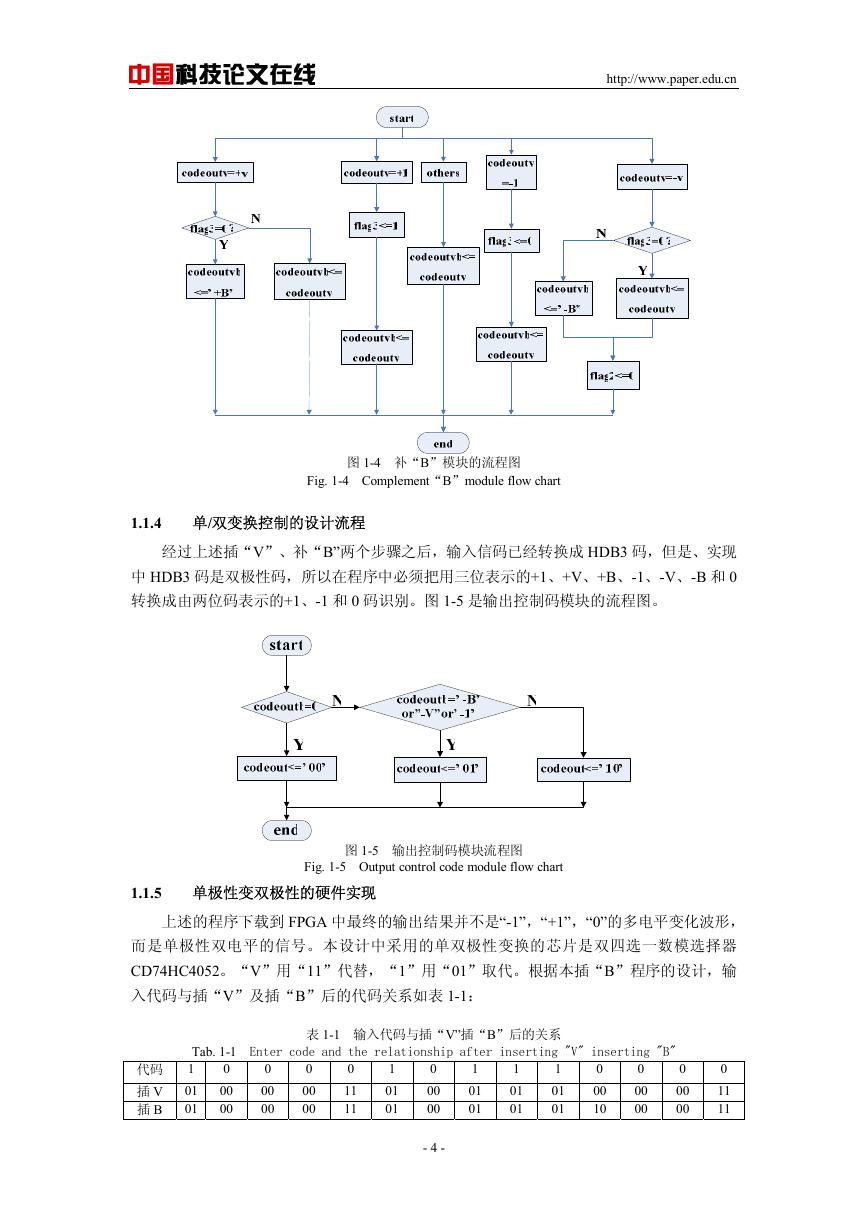

1.1.3 补“B”模块的设计流程

在设计中,要把 B 码及 B 码的极性补到码流中,难点在于 B 的极性是由现在时中 V 的

极性和过去时中前一非 0 码的极性来确定,并且要把 B 码加在过去时中。若按上述的想法

用算法实现,难度较大,所以选用逻辑器件——4 位移位寄存器来实现。程序中使用了元件

例化语句用 D 触发器连接组成移位寄存器。首先把经插“V”处理过的信码放入到移位寄存

器里,在同步时钟的作用下,同时进行是否补“B”的判决,等到码元从移位寄存器里出来

的时候,若需要补“B”,则把-B/+B 的表示码直接赋值给移位寄存器的第四位;若不需要

补“B”,就直接把移位寄存器的第三位的值传到第四位输出即可,即照原码输出。图 1-4

是补“B”模块的流程图。

- 3 -

�

中国科技论文在线

http://www.paper.edu.cn

图 1-4 补“B”模块的流程图

Fig. 1-4 Complement“B”module flow chart

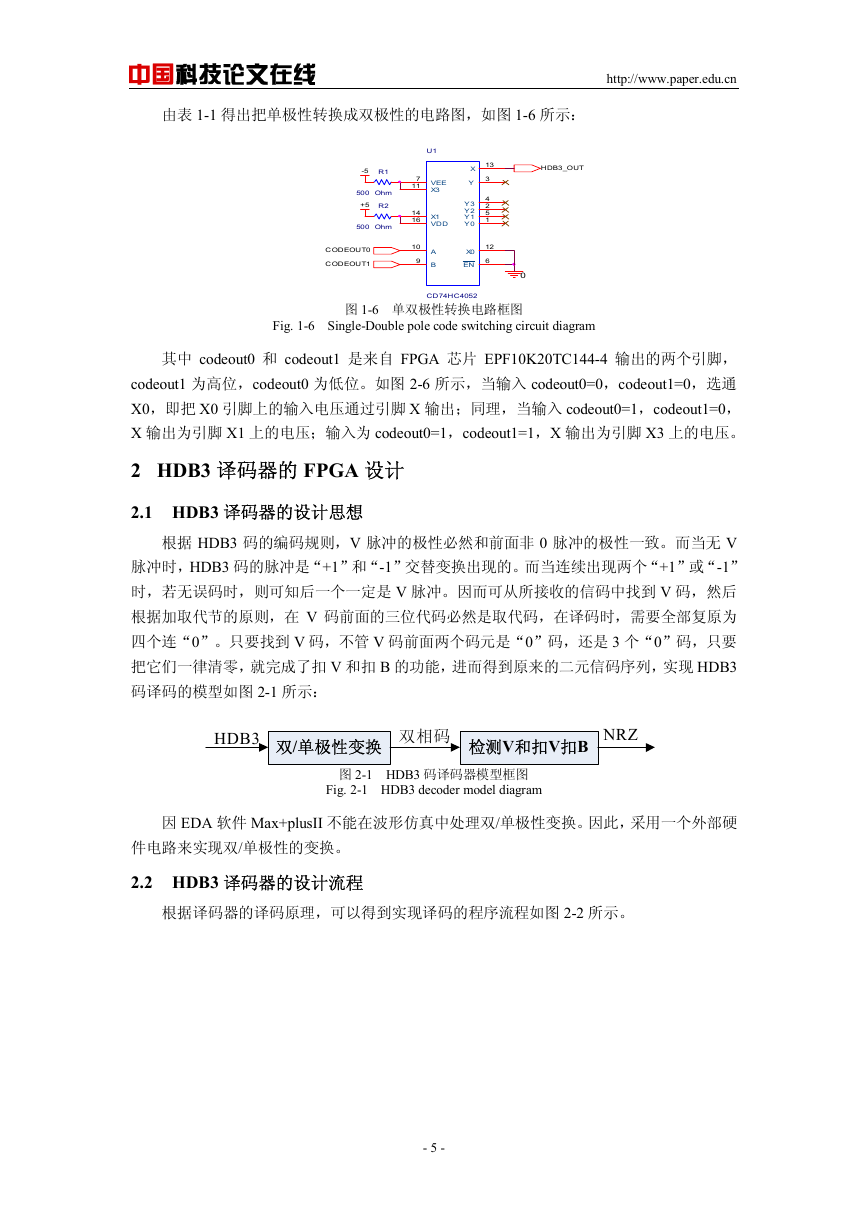

1.1.4 单/双变换控制的设计流程

经过上述插“V”、补“B”两个步骤之后,输入信码已经转换成 HDB3 码,但是、实现

中 HDB3 码是双极性码,所以在程序中必须把用三位表示的+1、+V、+B、-1、-V、-B 和 0

转换成由两位码表示的+1、-1 和 0 码识别。图 1-5 是输出控制码模块的流程图。

图 1-5 输出控制码模块流程图

Fig. 1-5 Output control code module flow chart

1.1.5 单极性变双极性的硬件实现

上述的程序下载到 FPGA 中最终的输出结果并不是“-1”,“+1”,“0”的多电平变化波形,

而是单极性双电平的信号。本设计中采用的单双极性变换的芯片是双四选一数模选择器

CD74HC4052。“V”用“11”代替,“1”用“01”取代。根据本插“B”程序的设计,输

入代码与插“V”及插“B”后的代码关系如表 1-1:

表 1-1 输入代码与插“V”插“B”后的关系

- 4 -

Tab. 1-1 Enter code and the relationship after inserting "V" inserting "B"

1

01

01

0

00

00

0

00

00

0

11

11

0

00

00

0

00

00

1

01

01

1

01

01

0

00

10

0

00

00

1

01

01

代码

插 V

插 B

1

01

01

0

00

00

0

11

11

�

中国科技论文在线

http://www.paper.edu.cn

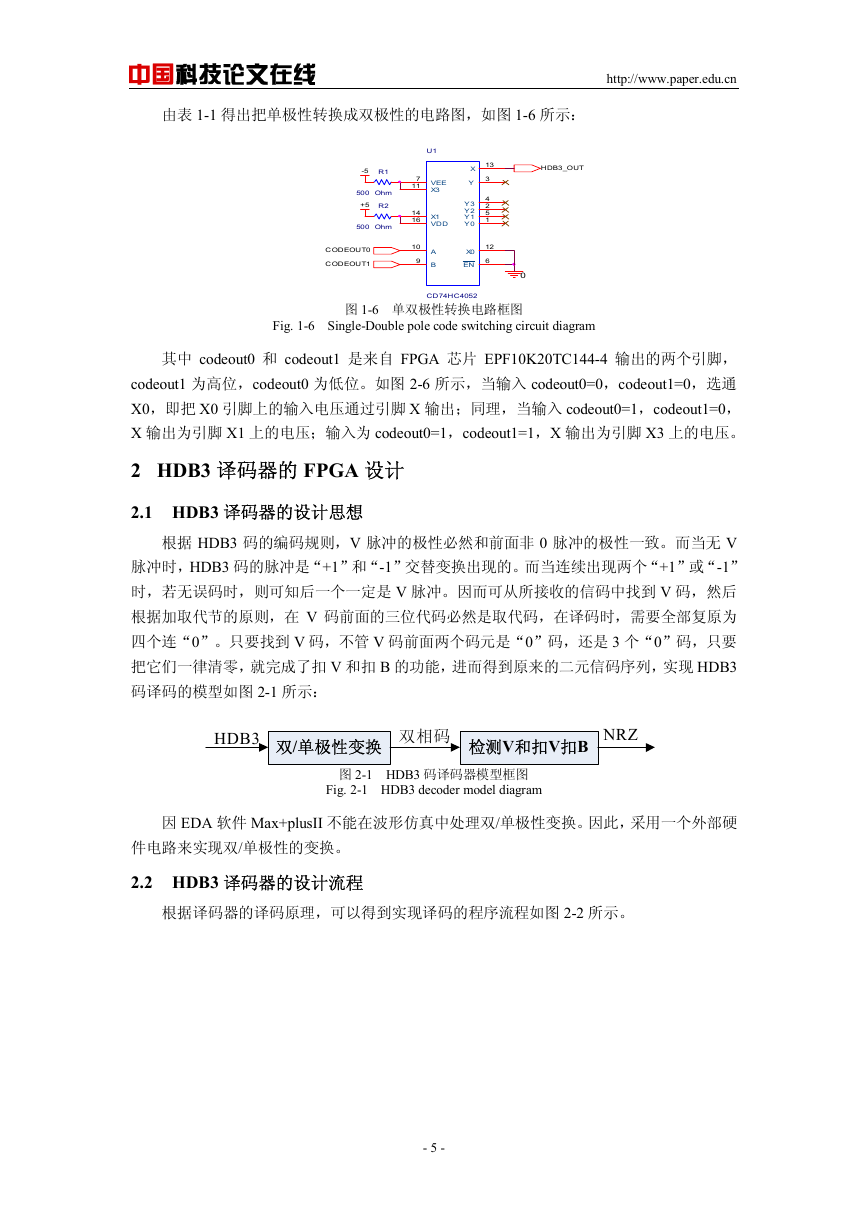

由表 1-1 得出把单极性转换成双极性的电路图,如图 1-6 所示:

U1

-5

R1

500 Ohm

+5

R2

500 Ohm

7

11

14

16

VEE

X3

X1

VDD

13

3

4

2

5

1

X

Y

Y3

Y2

Y1

Y0

CODEOUT0

CODEOUT1

10

A

B9

12

X0

EN 6

0

CD74HC4052

图 1-6 单双极性转换电路框图

HDB3_OUT

Fig. 1-6 Single-Double pole code switching circuit diagram

其中 codeout0 和 codeout1 是来自 FPGA 芯片 EPF10K20TC144-4 输出的两个引脚,

codeout1 为高位,codeout0 为低位。如图 2-6 所示,当输入 codeout0=0,codeout1=0,选通

X0,即把 X0 引脚上的输入电压通过引脚 X 输出;同理,当输入 codeout0=1,codeout1=0,

X 输出为引脚 X1 上的电压;输入为 codeout0=1,codeout1=1,X 输出为引脚 X3 上的电压。

2 HDB3 译码器的 FPGA 设计

2.1 HDB3 译码器的设计思想

根据 HDB3 码的编码规则,V 脉冲的极性必然和前面非 0 脉冲的极性一致。而当无 V

脉冲时,HDB3 码的脉冲是“+1”和“-1”交替变换出现的。而当连续出现两个“+1”或“-1”

时,若无误码时,则可知后一个一定是 V 脉冲。因而可从所接收的信码中找到 V 码,然后

根据加取代节的原则,在 V 码前面的三位代码必然是取代码,在译码时,需要全部复原为

四个连“0”。只要找到 V 码,不管 V 码前面两个码元是“0”码,还是 3 个“0”码,只要

把它们一律清零,就完成了扣 V 和扣 B 的功能,进而得到原来的二元信码序列,实现 HDB3

码译码的模型如图 2-1 所示:

HDB3

双/单极性变换

双相码

检测V和扣V扣B

NRZ

图 2-1 HDB3 码译码器模型框图

Fig. 2-1 HDB3 decoder model diagram

因 EDA 软件 Max+plusII 不能在波形仿真中处理双/单极性变换。因此,采用一个外部硬

件电路来实现双/单极性的变换。

2.2 HDB3 译码器的设计流程

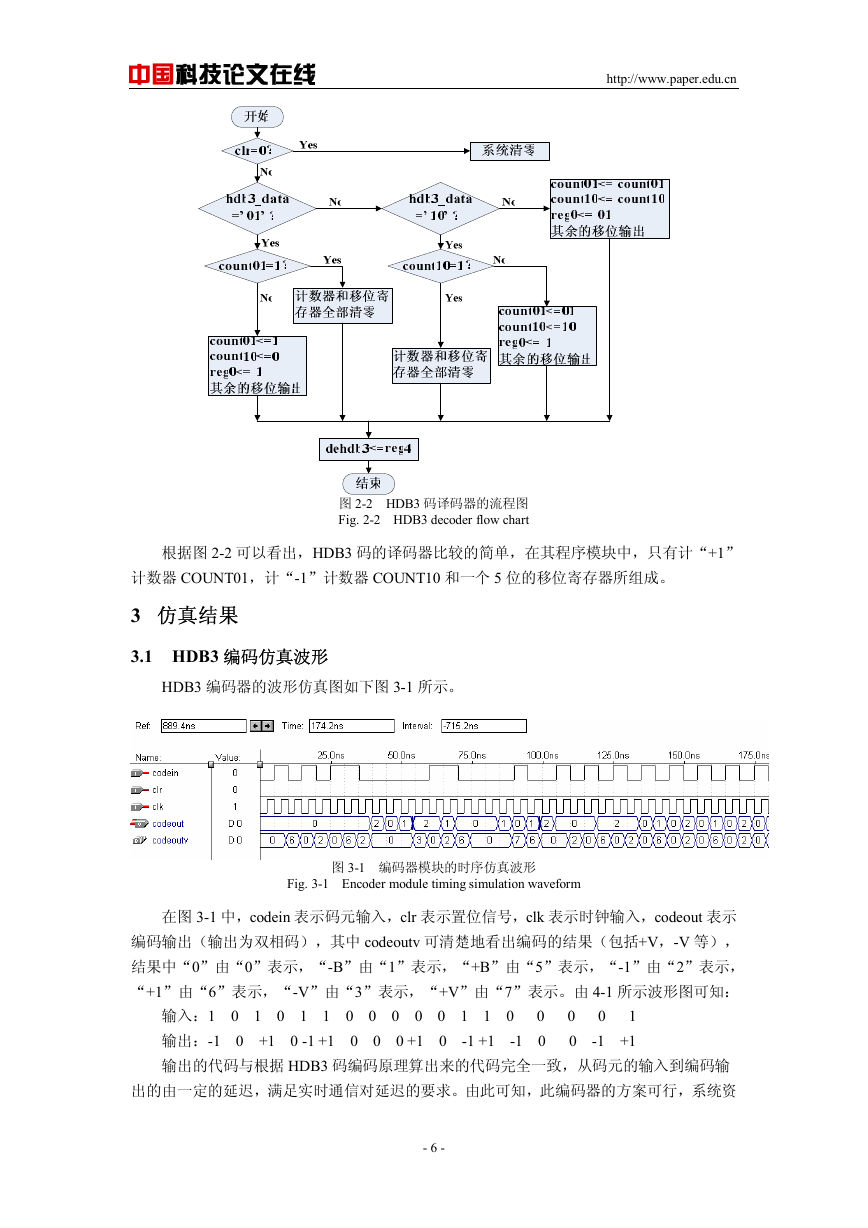

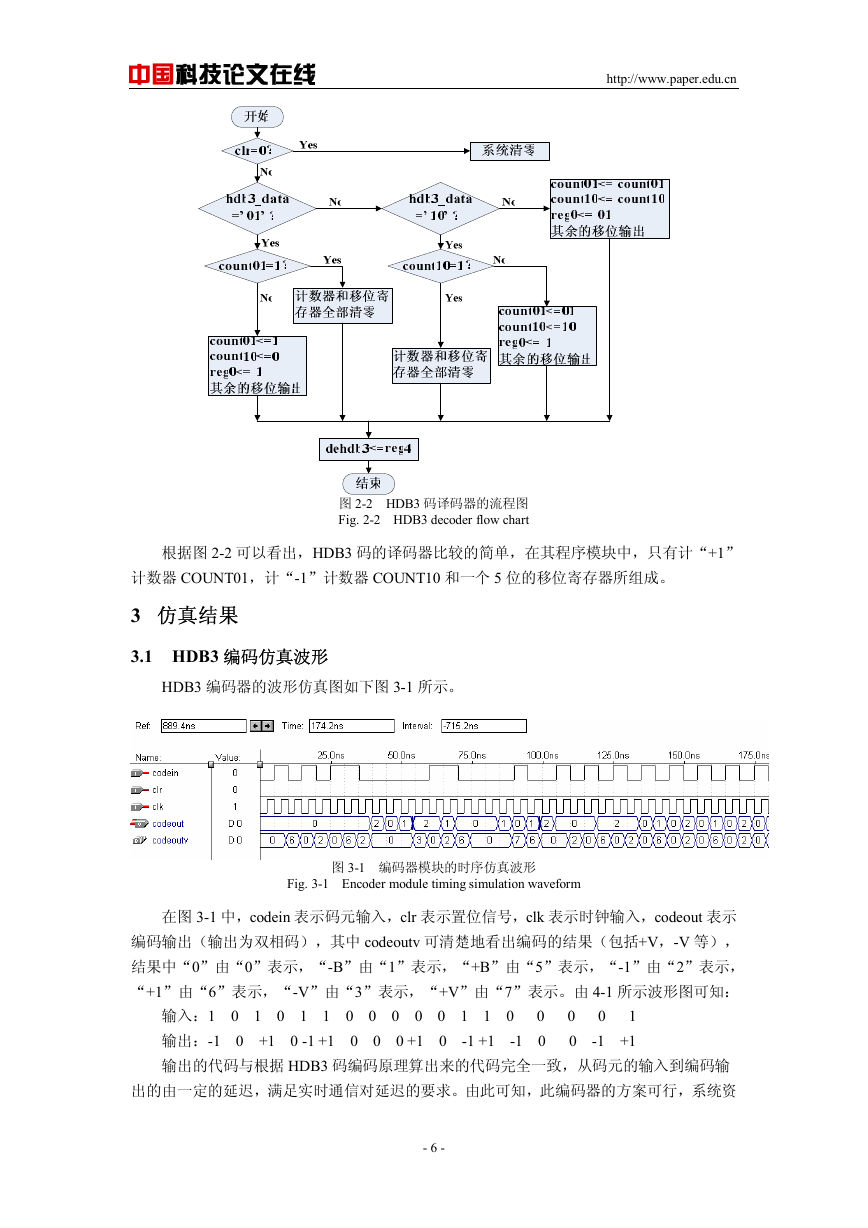

根据译码器的译码原理,可以得到实现译码的程序流程如图 2-2 所示。

- 5 -

�

中国科技论文在线

http://www.paper.edu.cn

图 2-2 HDB3 码译码器的流程图

Fig. 2-2 HDB3 decoder flow chart

根据图 2-2 可以看出,HDB3 码的译码器比较的简单,在其程序模块中,只有计“+1”

计数器 COUNT01,计“-1”计数器 COUNT10 和一个 5 位的移位寄存器所组成。

3 仿真结果

3.1 HDB3 编码仿真波形

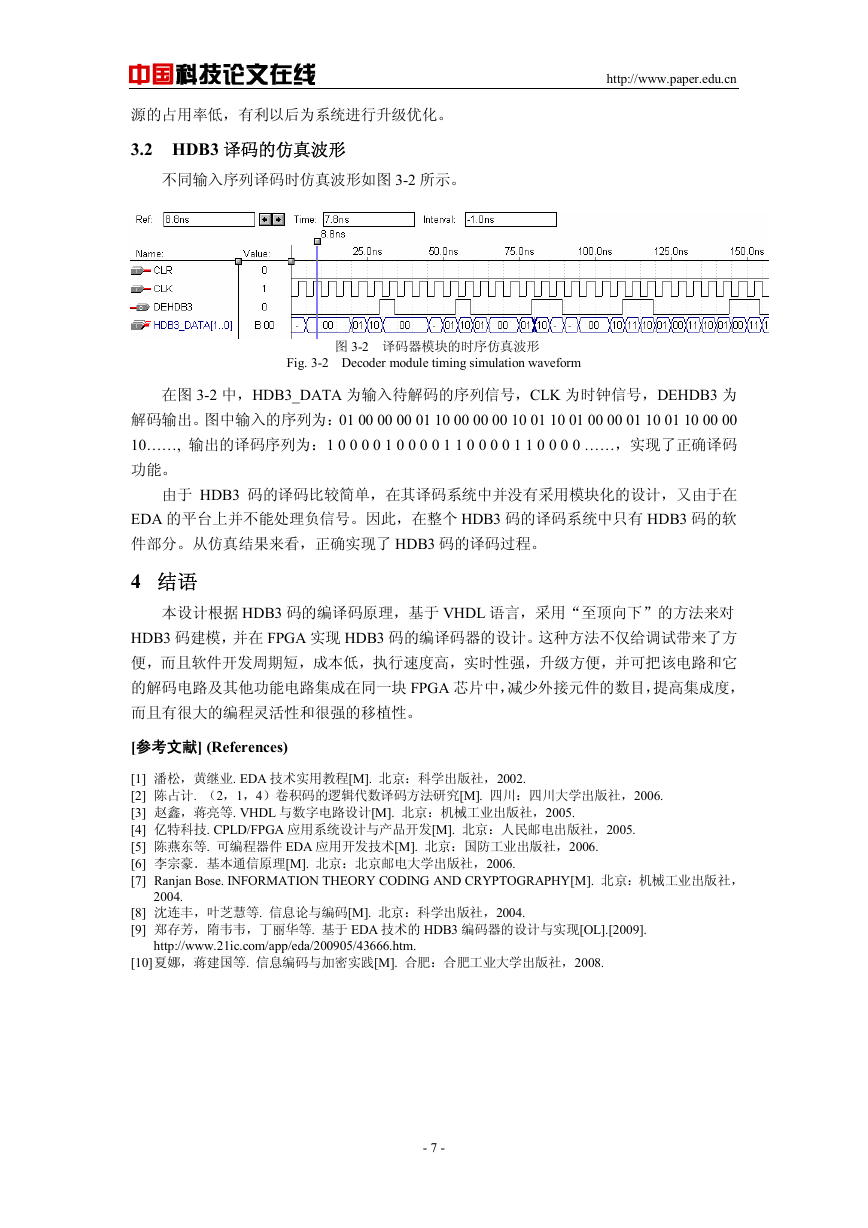

HDB3 编码器的波形仿真图如下图 3-1 所示。

图 3-1 编码器模块的时序仿真波形

Fig. 3-1 Encoder module timing simulation waveform

在图 3-1 中,codein 表示码元输入,clr 表示置位信号,clk 表示时钟输入,codeout 表示

编码输出(输出为双相码),其中 codeoutv 可清楚地看出编码的结果(包括+V,-V 等),

结果中“0”由“0”表示,“-B”由“1”表示,“+B”由“5”表示,“-1”由“2”表示,

“+1”由“6”表示,“-V”由“3”表示,“+V”由“7”表示。由 4-1 所示波形图可知:

输入:1 0 1 0 1 1 0 0 0 0 0 1 1 0 0 0 0 1

输出:-1 0 +1 0 -1 +1 0 0 0 +1 0 -1 +1 -1 0 0 -1 +1

输出的代码与根据 HDB3 码编码原理算出来的代码完全一致,从码元的输入到编码输

出的由一定的延迟,满足实时通信对延迟的要求。由此可知,此编码器的方案可行,系统资

- 6 -

�

中国科技论文在线

http://www.paper.edu.cn

源的占用率低,有利以后为系统进行升级优化。

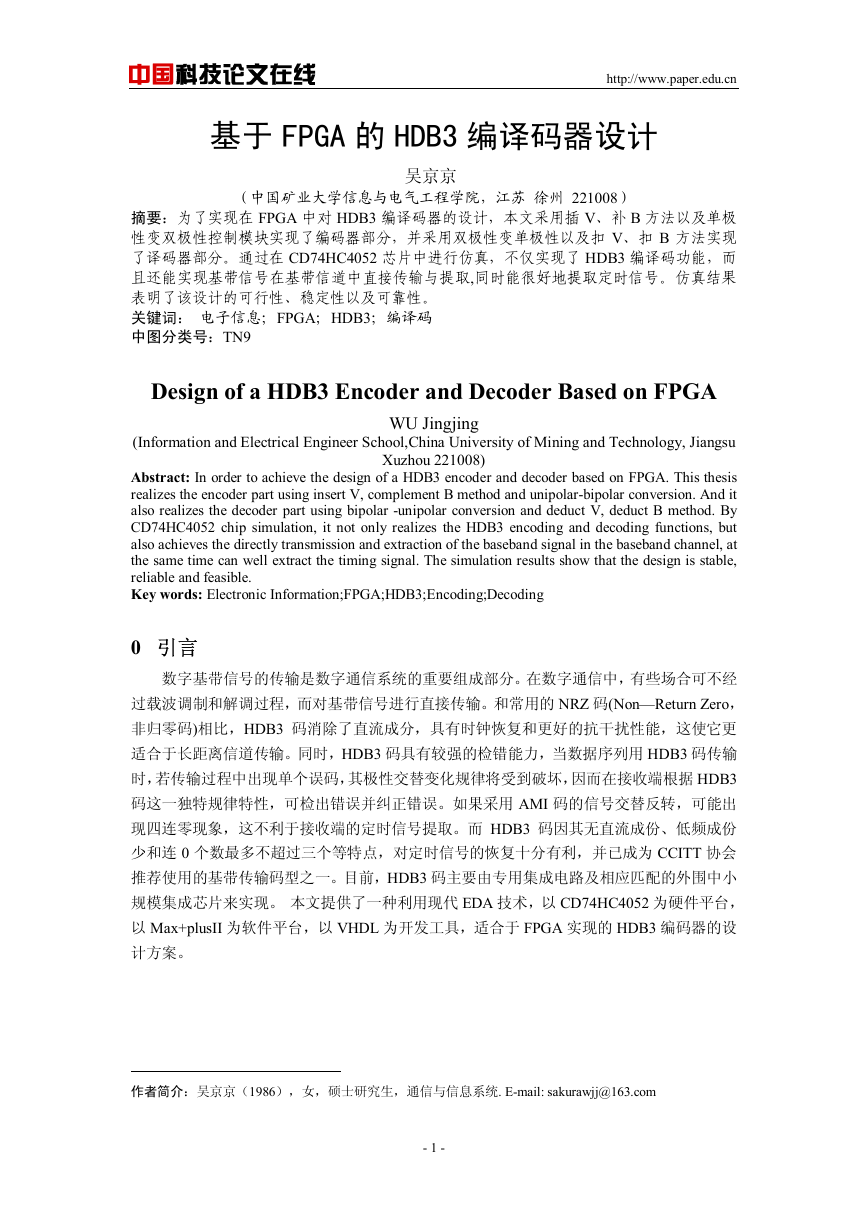

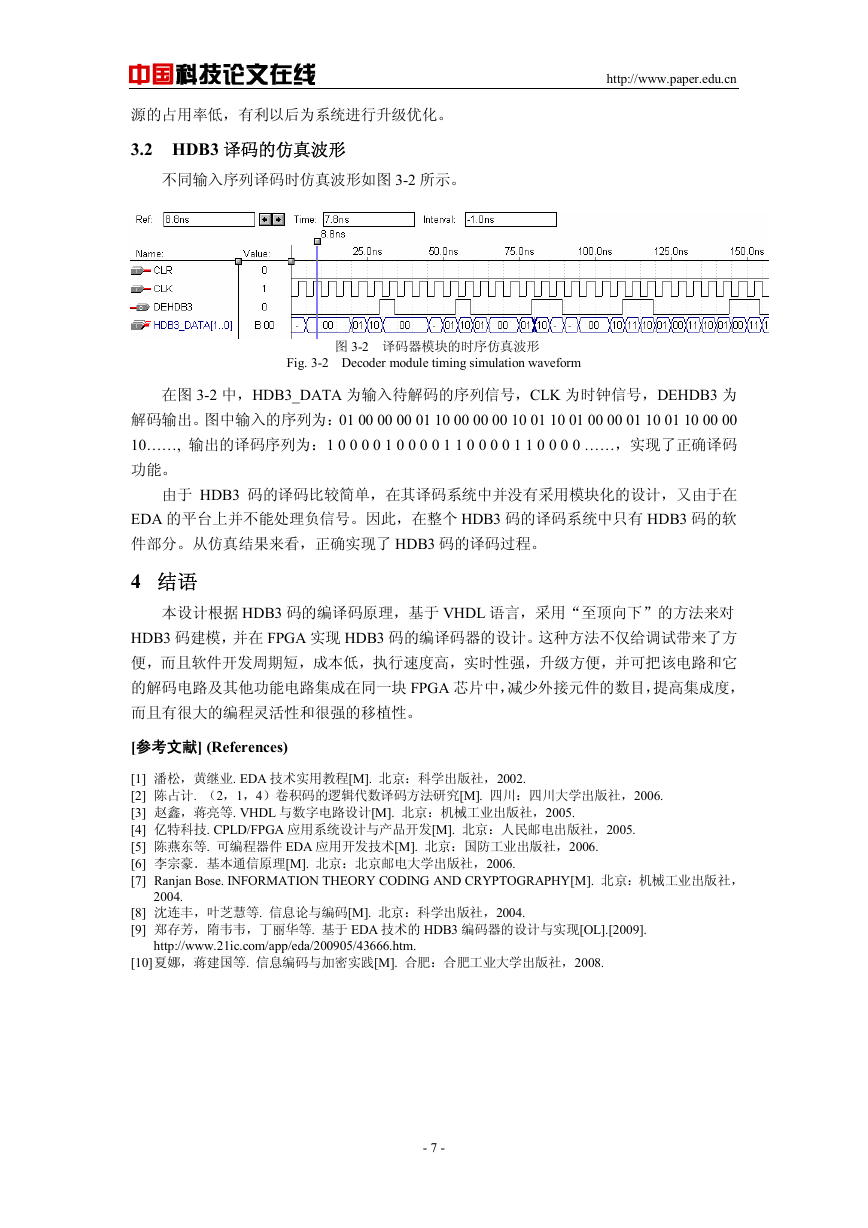

3.2 HDB3 译码的仿真波形

不同输入序列译码时仿真波形如图 3-2 所示。

图 3-2 译码器模块的时序仿真波形

Fig. 3-2 Decoder module timing simulation waveform

在图 3-2 中,HDB3_DATA 为输入待解码的序列信号,CLK 为时钟信号,DEHDB3 为

解码输出。图中输入的序列为:01 00 00 00 01 10 00 00 00 10 01 10 01 00 00 01 10 01 10 00 00

10……, 输出的译码序列为:1 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 ……,实现了正确译码

功能。

由于 HDB3 码的译码比较简单,在其译码系统中并没有采用模块化的设计,又由于在

EDA 的平台上并不能处理负信号。因此,在整个 HDB3 码的译码系统中只有 HDB3 码的软

件部分。从仿真结果来看,正确实现了 HDB3 码的译码过程。

4 结语

本设计根据 HDB3 码的编译码原理,基于 VHDL 语言,采用“至顶向下”的方法来对

HDB3 码建模,并在 FPGA 实现 HDB3 码的编译码器的设计。这种方法不仅给调试带来了方

便,而且软件开发周期短,成本低,执行速度高,实时性强,升级方便,并可把该电路和它

的解码电路及其他功能电路集成在同一块 FPGA 芯片中,减少外接元件的数目,提高集成度,

而且有很大的编程灵活性和很强的移植性。

[参考文献] (References)

[1] 潘松,黄继业. EDA 技术实用教程[M]. 北京:科学出版社,2002.

[2] 陈占计. (2,1,4)卷积码的逻辑代数译码方法研究[M]. 四川:四川大学出版社,2006.

[3] 赵鑫,蒋亮等. VHDL 与数字电路设计[M]. 北京:机械工业出版社,2005.

[4] 亿特科技. CPLD/FPGA 应用系统设计与产品开发[M]. 北京:人民邮电出版社,2005.

[5] 陈燕东等. 可编程器件 EDA 应用开发技术[M]. 北京:国防工业出版社,2006.

[6] 李宗豪.基本通信原理[M]. 北京:北京邮电大学出版社,2006.

[7] Ranjan Bose. INFORMATION THEORY CODING AND CRYPTOGRAPHY[M]. 北京:机械工业出版社,

2004.

[8] 沈连丰,叶芝慧等. 信息论与编码[M]. 北京:科学出版社,2004.

[9] 郑存芳,隋韦韦,丁丽华等. 基于 EDA 技术的 HDB3 编码器的设计与实现[OL].[2009].

http://www.21ic.com/app/eda/200905/43666.htm.

[10] 夏娜,蒋建国等. 信息编码与加密实践[M]. 合肥:合肥工业大学出版社,2008.

- 7 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc