Sign In (/plugins/common/feature/saml/doauth/post?

Browse

oamProtectedResource=rh=https%3A%2F%2Fforums.xilinx.com%2Ft5%2FSpartan-Family-FPGAs-Archived%2Funderstanding-

This board

Search Search all content

Search all content

Search all content

BITSLIP-one-more-time%2Ftd-p%2F105327) Help (/t5/help/faqpage)

Turn on suggestions (https://forums.xilinx.com/t5/forums/v4/forumtopicpage.enableautocomplete:enableautocomplete?t:ac=board-

id/Spartan/thread-id/8055&t:cp=action/contributions/searchactions&ticket=aRTcIdwnd7Ip_-1)

cancel

Showing results for

Search instead for

Did you mean:

Community Forums (/)

:

Forums (/t5/Forums/ct-p/XlnxProd)

:

Programmable Devices (Archive) (/t5/Programmable-Devices-Archive/ct-p/SILICON)

:

Spartan® Family FPGAs (Archived) (/t5/Spartan-Family-FPGAs-Archived/bd-p/Spartan)

understanding BITSLIP (one more time)

:

Options

Subscribe to RSS Feed (/xlnx/rss/message?board.id=Spartan&message.id=8055)

Mark Topic as New

Mark Topic as Read

Float this Topic for Current User

Bookmark

Subscribe

Mute

Printer Friendly Page (/t5/forums/forumtopicprintpage/board-id/Spartan/message-id/8055/print-single-message/false/page/1)

(/t5/user/viewprofilepage/user-id/9908)

eteam00 (https://forums.xilinx.com/t5/user/viewprofilepage/user-id/9908)

Instructor

Mark as New

Bookmark

Subscribe

Mute

Subscribe to RSS Feed (https://forums.xilinx.com/rss/message?board.id=Spartan&message.id=8055)

Permalink (/t5/Spartan-Family-FPGAs-Archived/understanding-BITSLIP-one-more-time/m-p/105327/highlight/true#M8055)

Print (/t5/forums/forumtopicprintpage/board-id/Spartan/message-id/8055/print-single-message/true/page/1)

Email to a Friend

Report Inappropriate Content (/t5/notifications/notifymoderatorpage/message-uid/105327)

11-17-2010 07:57 AM - edited 12-16-2010 11:29 PM

18,465 Views

Registered: 07-21-2009

understanding BITSLIP (one more time)

�

UPDATED 02-dec-2010: Replaced all references to DIVCLK with CLKDIV. Both terms are used in UG382 (Clocking Resources), but

only CLKDIV is used in UG381 (SelectIO Resources) and DS162 (Datasheet). All my other posts in this thread have been updated as

well.

This is my latest attempt to make sense of the Spartan 6 ISERDES2 BITSLIP function. It probably isn't all that complicated, but its

simplicity is obscured by inconsistencies and omissions in the Xilinx documentation, plus Xilinx' reluctance to provide details of the

BITSLIP function logic. Even the webcase support on BITSLIP function has been clouded by an uneven understanding of the function

by the support team. Roy (as in roym) has an understanding of ISERDES2 and BITSLIP which is as deep and thorough as anyone

else I've engaged on the Xilinx team.

So, here is my unofficial and unsanctioned description of the BITSLIP function.

Comments, additions, corrections, and questions are welcome.

- Bob Elkind

Diagrams:

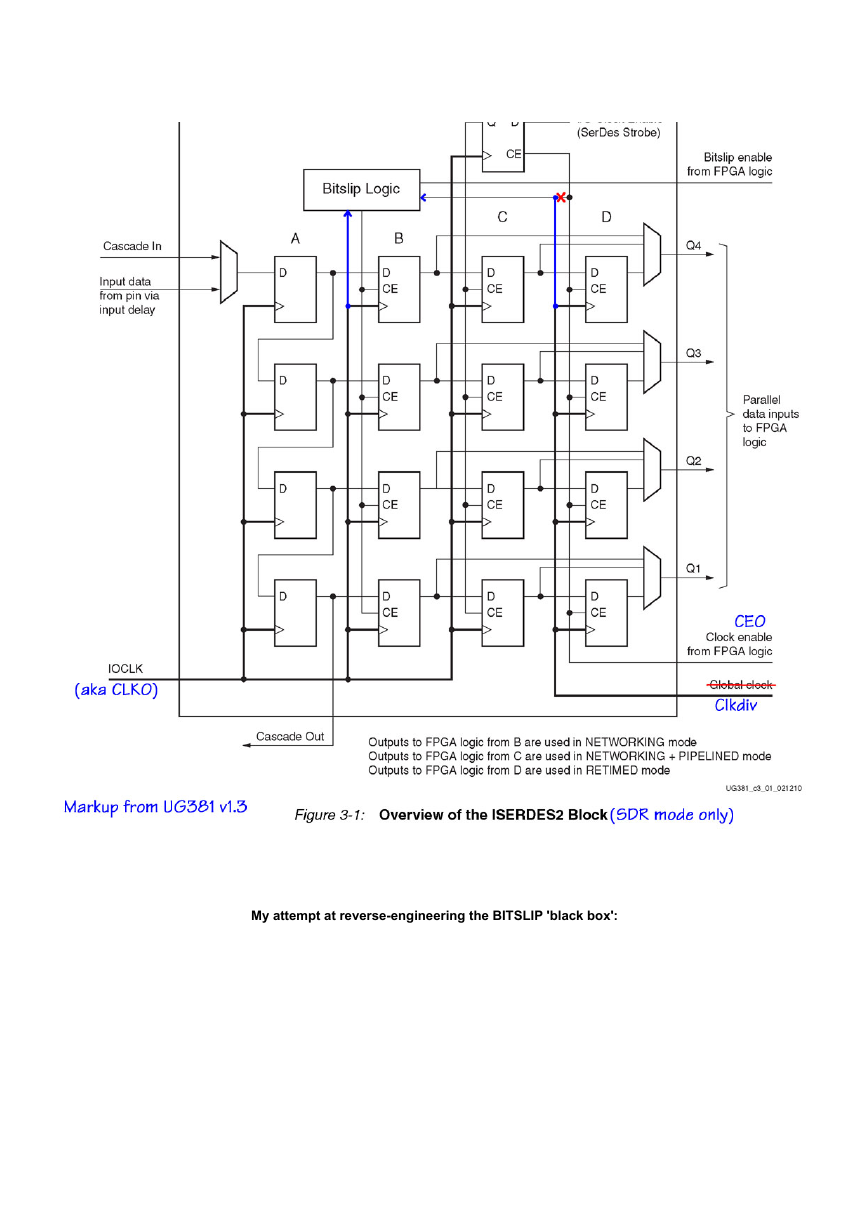

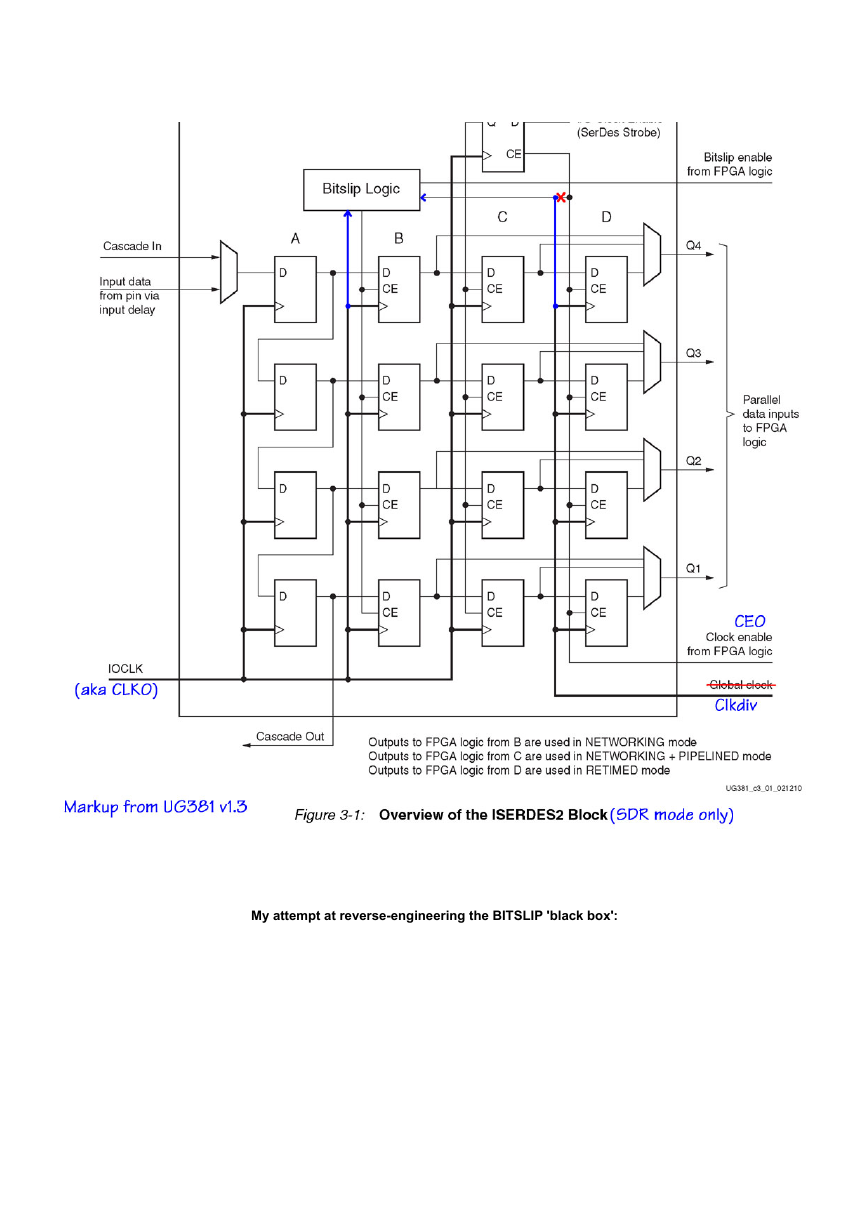

my corrections (markups) to UG381 Figure 3-1:

�

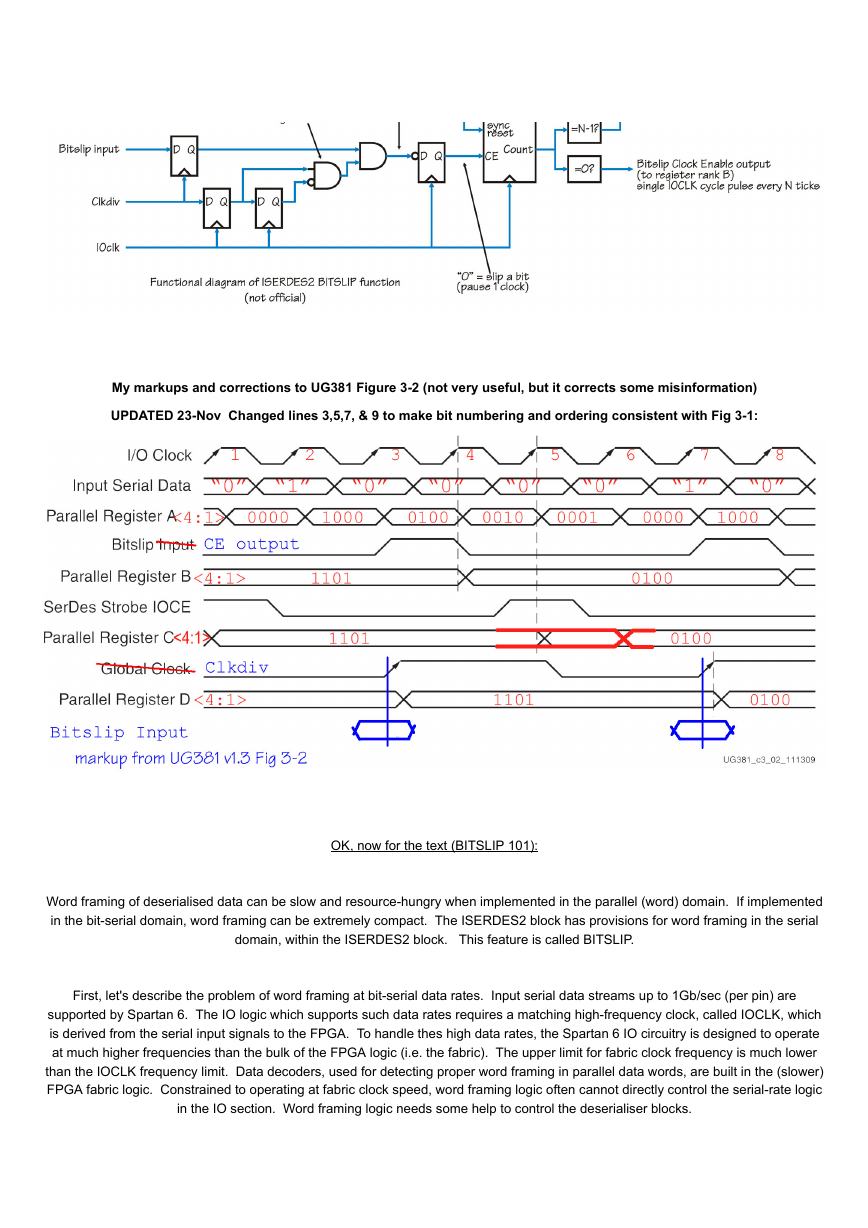

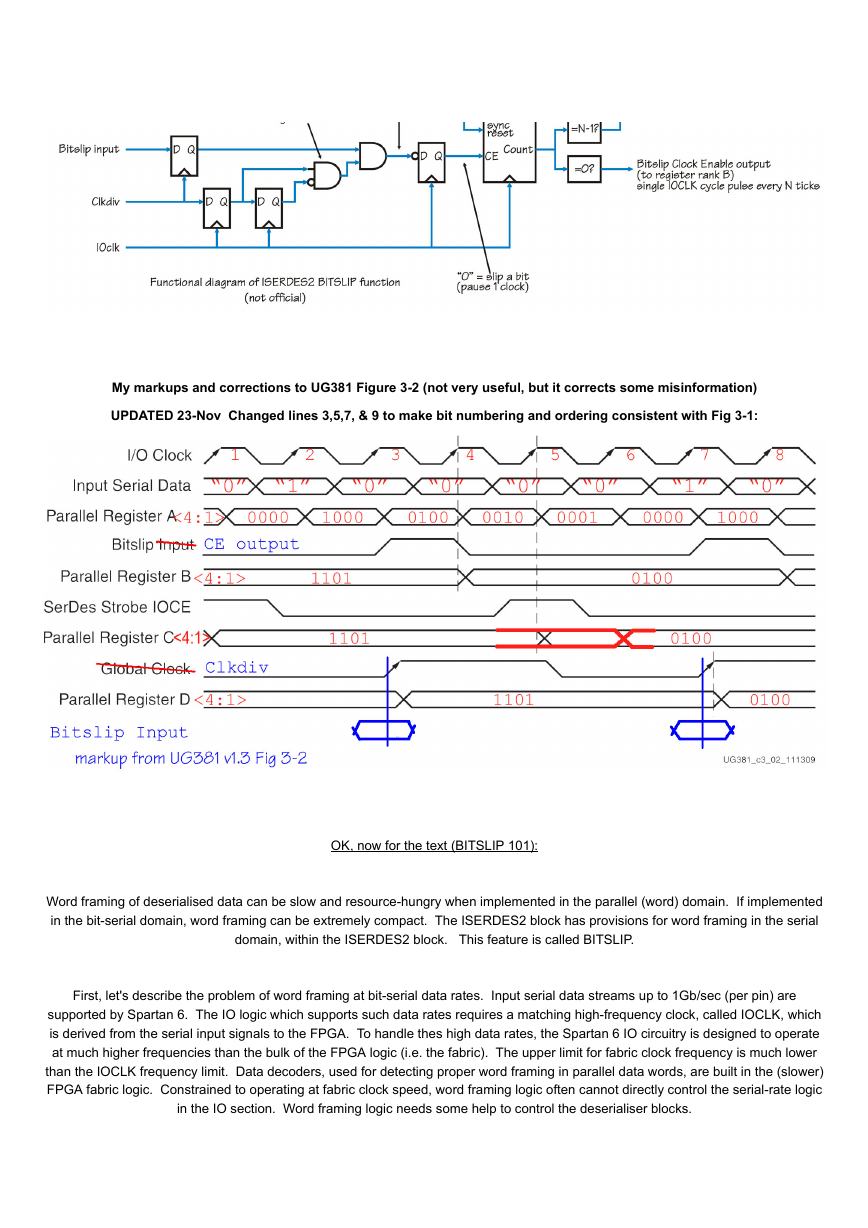

My attempt at reverse-engineering the BITSLIP 'black box':

�

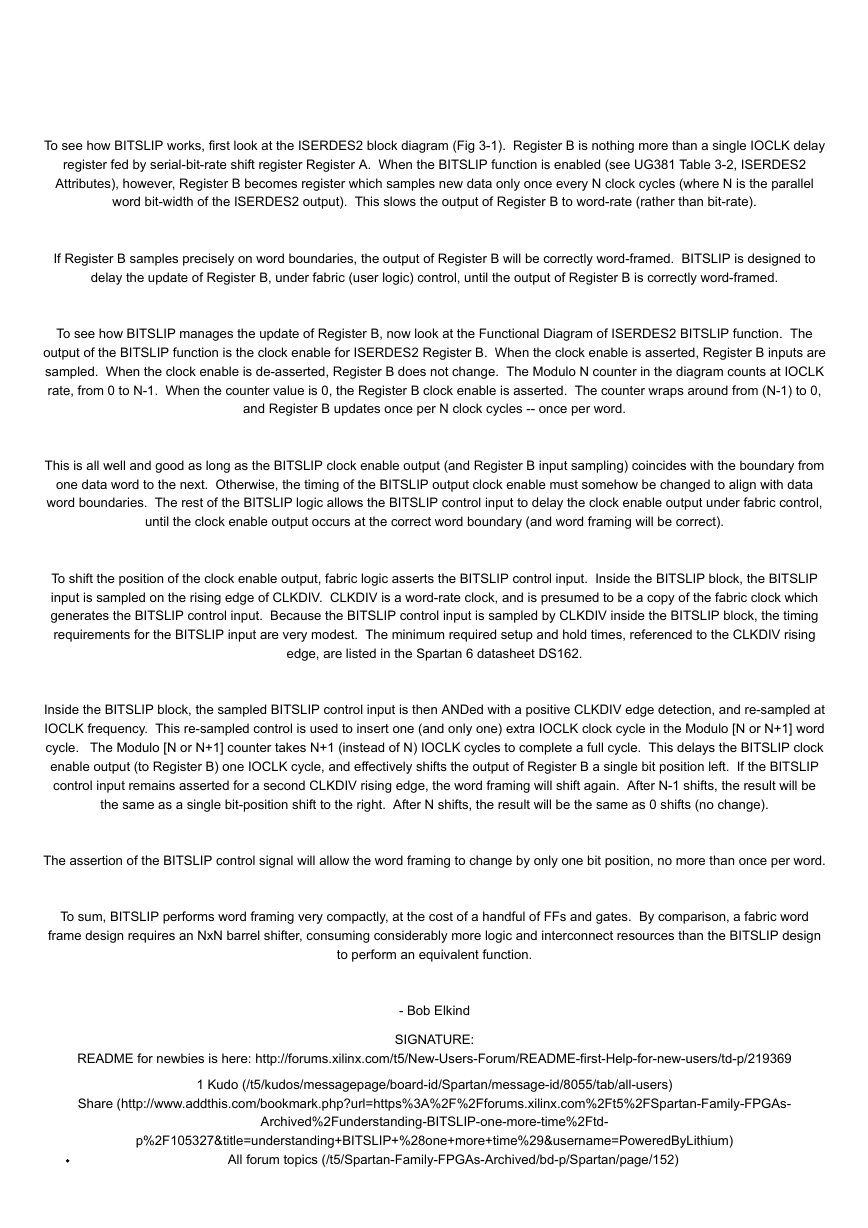

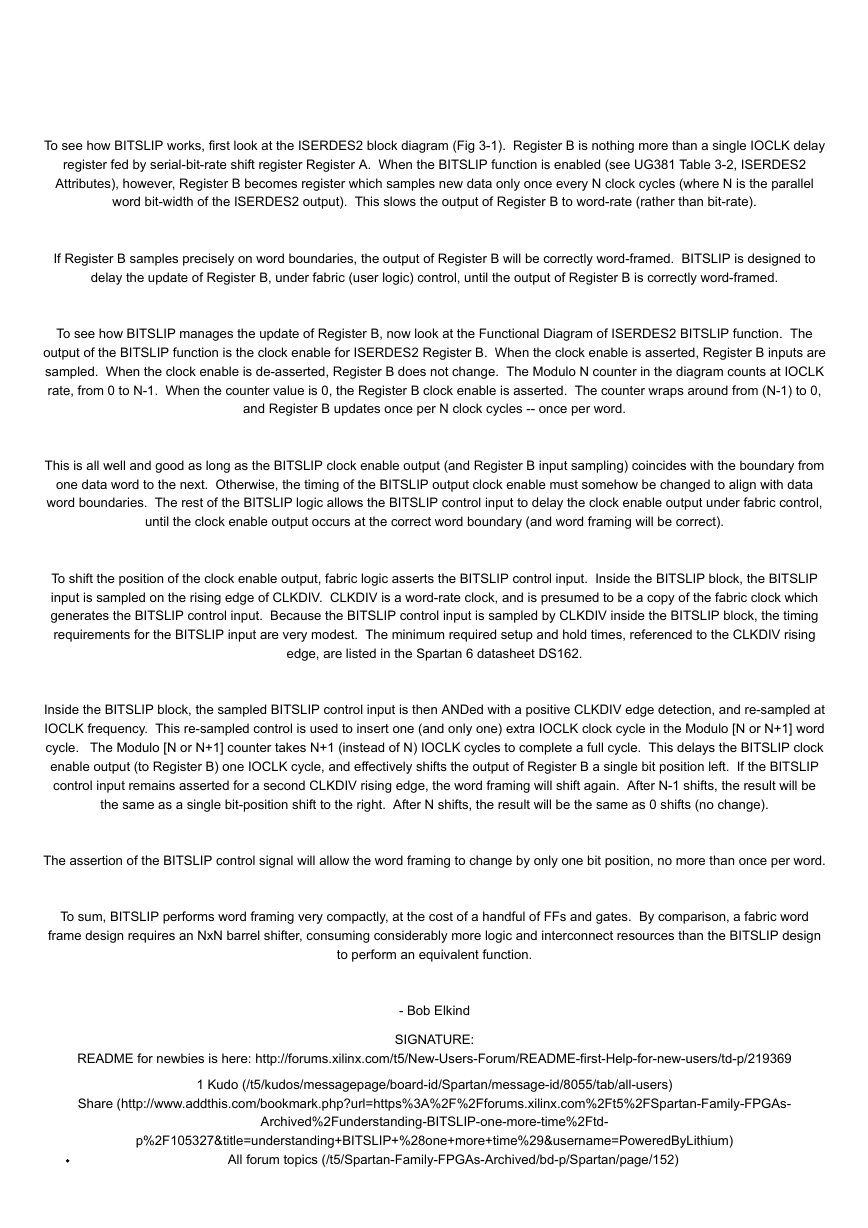

My markups and corrections to UG381 Figure 3-2 (not very useful, but it corrects some misinformation)

UPDATED 23-Nov Changed lines 3,5,7, & 9 to make bit numbering and ordering consistent with Fig 3-1:

OK, now for the text (BITSLIP 101):

Word framing of deserialised data can be slow and resource-hungry when implemented in the parallel (word) domain. If implemented

in the bit-serial domain, word framing can be extremely compact. The ISERDES2 block has provisions for word framing in the serial

domain, within the ISERDES2 block. This feature is called BITSLIP.

First, let's describe the problem of word framing at bit-serial data rates. Input serial data streams up to 1Gb/sec (per pin) are

supported by Spartan 6. The IO logic which supports such data rates requires a matching high-frequency clock, called IOCLK, which

is derived from the serial input signals to the FPGA. To handle thes high data rates, the Spartan 6 IO circuitry is designed to operate

at much higher frequencies than the bulk of the FPGA logic (i.e. the fabric). The upper limit for fabric clock frequency is much lower

than the IOCLK frequency limit. Data decoders, used for detecting proper word framing in parallel data words, are built in the (slower)

FPGA fabric logic. Constrained to operating at fabric clock speed, word framing logic often cannot directly control the serial-rate logic

in the IO section. Word framing logic needs some help to control the deserialiser blocks.

�

The BITSLIP function includes logic to accept a control signal generated in the FPGA fabric by parallel word logic running at parallel

word clock rates. Inside the BITSLIP function, the slow input control signal is synchronised to the IOCLK (bit rate) clock, and is used

to accomplish word framing.

To see how BITSLIP works, first look at the ISERDES2 block diagram (Fig 3-1). Register B is nothing more than a single IOCLK delay

register fed by serial-bit-rate shift register Register A. When the BITSLIP function is enabled (see UG381 Table 3-2, ISERDES2

Attributes), however, Register B becomes register which samples new data only once every N clock cycles (where N is the parallel

word bit-width of the ISERDES2 output). This slows the output of Register B to word-rate (rather than bit-rate).

If Register B samples precisely on word boundaries, the output of Register B will be correctly word-framed. BITSLIP is designed to

delay the update of Register B, under fabric (user logic) control, until the output of Register B is correctly word-framed.

To see how BITSLIP manages the update of Register B, now look at the Functional Diagram of ISERDES2 BITSLIP function. The

output of the BITSLIP function is the clock enable for ISERDES2 Register B. When the clock enable is asserted, Register B inputs are

sampled. When the clock enable is de-asserted, Register B does not change. The Modulo N counter in the diagram counts at IOCLK

rate, from 0 to N-1. When the counter value is 0, the Register B clock enable is asserted. The counter wraps around from (N-1) to 0,

and Register B updates once per N clock cycles -- once per word.

This is all well and good as long as the BITSLIP clock enable output (and Register B input sampling) coincides with the boundary from

one data word to the next. Otherwise, the timing of the BITSLIP output clock enable must somehow be changed to align with data

word boundaries. The rest of the BITSLIP logic allows the BITSLIP control input to delay the clock enable output under fabric control,

until the clock enable output occurs at the correct word boundary (and word framing will be correct).

To shift the position of the clock enable output, fabric logic asserts the BITSLIP control input. Inside the BITSLIP block, the BITSLIP

input is sampled on the rising edge of CLKDIV. CLKDIV is a word-rate clock, and is presumed to be a copy of the fabric clock which

generates the BITSLIP control input. Because the BITSLIP control input is sampled by CLKDIV inside the BITSLIP block, the timing

requirements for the BITSLIP input are very modest. The minimum required setup and hold times, referenced to the CLKDIV rising

edge, are listed in the Spartan 6 datasheet DS162.

Inside the BITSLIP block, the sampled BITSLIP control input is then ANDed with a positive CLKDIV edge detection, and re-sampled at

IOCLK frequency. This re-sampled control is used to insert one (and only one) extra IOCLK clock cycle in the Modulo [N or N+1] word

cycle. The Modulo [N or N+1] counter takes N+1 (instead of N) IOCLK cycles to complete a full cycle. This delays the BITSLIP clock

enable output (to Register B) one IOCLK cycle, and effectively shifts the output of Register B a single bit position left. If the BITSLIP

control input remains asserted for a second CLKDIV rising edge, the word framing will shift again. After N-1 shifts, the result will be

the same as a single bit-position shift to the right. After N shifts, the result will be the same as 0 shifts (no change).

The assertion of the BITSLIP control signal will allow the word framing to change by only one bit position, no more than once per word.

To sum, BITSLIP performs word framing very compactly, at the cost of a handful of FFs and gates. By comparison, a fabric word

frame design requires an NxN barrel shifter, consuming considerably more logic and interconnect resources than the BITSLIP design

to perform an equivalent function.

- Bob Elkind

SIGNATURE:

README for newbies is here: http://forums.xilinx.com/t5/New-Users-Forum/README-first-Help-for-new-users/td-p/219369

Share (http://www.addthis.com/bookmark.php?url=https%3A%2F%2Fforums.xilinx.com%2Ft5%2FSpartan-Family-FPGAs-

1 Kudo (/t5/kudos/messagepage/board-id/Spartan/message-id/8055/tab/all-users)

Archived%2Funderstanding-BITSLIP-one-more-time%2Ftd-

p%2F105327&title=understanding+BITSLIP+%28one+more+time%29&username=PoweredByLithium)

All forum topics (/t5/Spartan-Family-FPGAs-Archived/bd-p/Spartan/page/152)

�

Previous Topic (/t5/Spartan-Family-FPGAs-Archived/not-getting-Clock-of-25-MHZ-for-Ethernet-in-Spatran-3E-starter/td-

Next Topic (/t5/Spartan-Family-FPGAs-Archived/Slave-SelectMap-Spartan-6-iMX35/td-p/113852)

p/116014)

18 Replies

(/t5/user/viewprofilepage/user-id/10)

roym (https://forums.xilinx.com/t5/user/viewprofilepage/user-id/10)

Moderator

Mark as New

Bookmark

Subscribe

Mute

Subscribe to RSS Feed (https://forums.xilinx.com/rss/message?board.id=Spartan&message.id=8080)

Permalink (/t5/Spartan-Family-FPGAs-Archived/understanding-BITSLIP-one-more-time/m-p/105675/highlight/true#M8080)

Print (/t5/forums/forumtopicprintpage/board-id/Spartan/message-id/8080/print-single-message/true/page/1)

Email to a Friend

Report Inappropriate Content (/t5/notifications/notifymoderatorpage/message-uid/105675)

11-18-2010 08:44 AM

18,404 Views

Registered: 07-30-2007

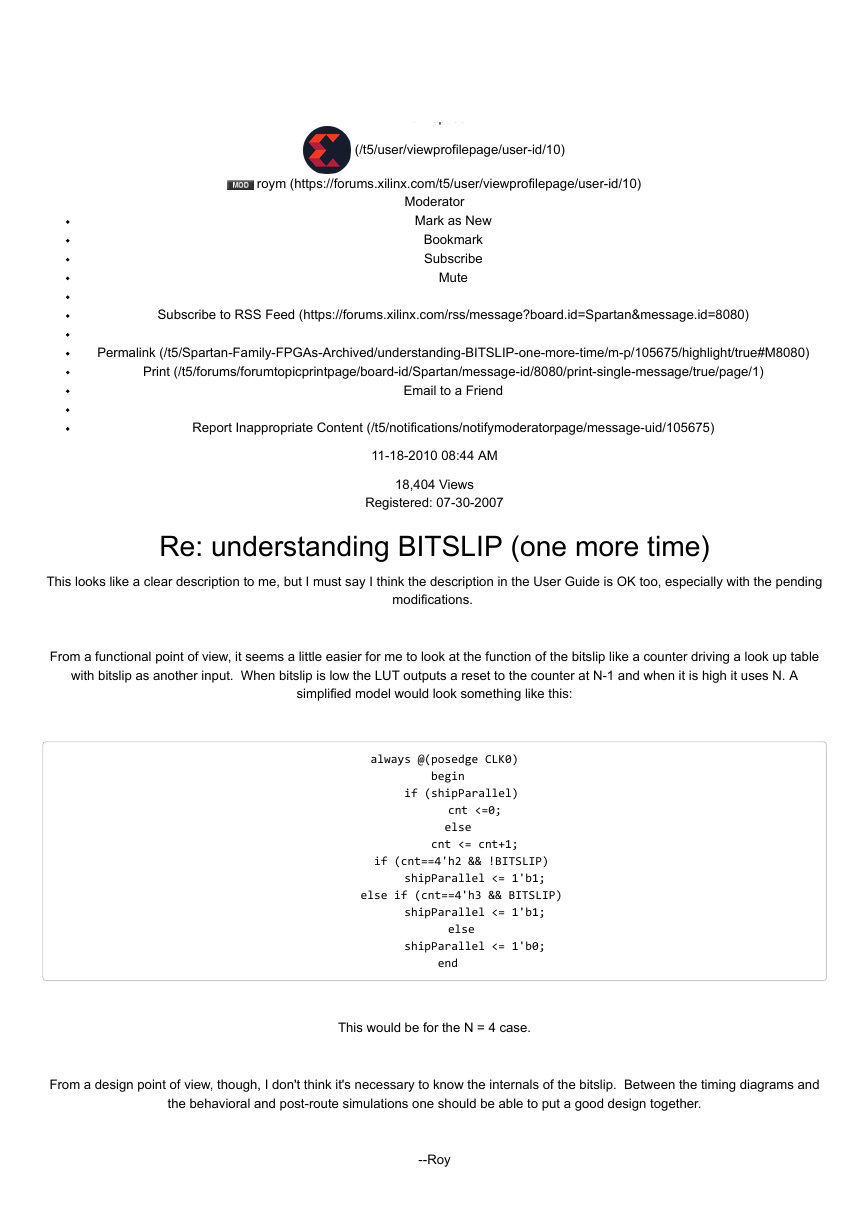

Re: understanding BITSLIP (one more time)

This looks like a clear description to me, but I must say I think the description in the User Guide is OK too, especially with the pending

modifications.

From a functional point of view, it seems a little easier for me to look at the function of the bitslip like a counter driving a look up table

with bitslip as another input. When bitslip is low the LUT outputs a reset to the counter at N-1 and when it is high it uses N. A

simplified model would look something like this:

always @(posedge CLK0)

begin

if (shipParallel)

cnt <=0;

else

cnt <= cnt+1;

if (cnt==4'h2 && !BITSLIP)

shipParallel <= 1'b1;

else if (cnt==4'h3 && BITSLIP)

shipParallel <= 1'b1;

else

shipParallel <= 1'b0;

end

This would be for the N = 4 case.

From a design point of view, though, I don't think it's necessary to know the internals of the bitslip. Between the timing diagrams and

the behavioral and post-route simulations one should be able to put a good design together.

--Roy

�

----------------------------------------------------------------------------

Don't forget to reply, kudo, and accept as solution

----------------------------------------------------------------------------

Share (http://www.addthis.com/bookmark.php?url=https%3A%2F%2Fforums.xilinx.com%2Ft5%2FSpartan-Family-FPGAs-

p%2F105327&title=Re%3A+understanding+BITSLIP+%28one+more+time%29&username=PoweredByLithium)

Archived%2Funderstanding-BITSLIP-one-more-time%2Ftd-

0 Kudos

(/t5/user/viewprofilepage/user-id/9908)

eteam00 (https://forums.xilinx.com/t5/user/viewprofilepage/user-id/9908)

Instructor

Mark as New

Bookmark

Subscribe

Mute

Subscribe to RSS Feed (https://forums.xilinx.com/rss/message?board.id=Spartan&message.id=8089)

Permalink (/t5/Spartan-Family-FPGAs-Archived/understanding-BITSLIP-one-more-time/m-p/105779/highlight/true#M8089)

Print (/t5/forums/forumtopicprintpage/board-id/Spartan/message-id/8089/print-single-message/true/page/1)

Email to a Friend

Report Inappropriate Content (/t5/notifications/notifymoderatorpage/message-uid/105779)

11-18-2010 12:19 PM - edited 12-02-2010 10:08 AM

18,385 Views

Registered: 07-21-2009

CORRECTED: understanding BITSLIP (one more time)

Roy,

1. A problem with your 'simplified model' is that it suggests BITSLIP is sampled by CLK0 (IOCLK). This contradicts the datasheet,

which expresses BITSLIP setup/hold timing requirements referenced to CLKDIV (not IOCLK). Fabric logic would have a difficult time

ensuring setup and hold time relative to CLK0 (i.e. IOCLK). If your example code is correct, you've just opened a nasty can of

worms.

1.a Your example code generates a one-time displacement of 'shipParallel'. This will result in a shipParallel pulse 5 cycles

from the previous pulse and 3 cycles from the following pulse. In order to work correctly, BITSLIP must force the cnt counter to

extend to a value of 4 (rather than 3) before wrapping back to 0.

CORRECTION: My reading of Roy's code was incorrect on this point. Please disregard "1.a". - Bob

1.b Your example code is likely to occasionally generate either 0 shipParallel pulses or a double pulse (2 consecutive IOCLK

cycles), depending on the timing of BITSLIP from the fabric with respect to the cnt cycle.

�

2. If you look at the markups to UG381 Figures 3-1 and 3-2, those markups (hopefully) correct a few instances of fundamentally

misleading information. The current BITSLIP description in the User Guide is vague enough to let these two diagrams (with the

misleading information) seem plausible. The combination of misleading diagrams and non-concise text description is (my opinion)

'fatal'.

3. When I raised the concerns I had in a webcase, I was given incorrect information. It wasn't until I referred to the webcase response

in a forum posting (http://forums.xilinx.com/t5/Spartan-Family-FPGAs/Spartan-6-ISERDES2-BITSLIP-warning/m-p/73496) that you

caught the error and corrected it, for which I am quite grateful. That forum exchange was 5 months ago.

4. We users can't comment on the pending modifications to the User Guide, of course, based on either content or timing of its

availability. Which is one of the biggest reasons for my posting this thread.

Between the timing diagrams and the behavioral and post-route simulations one should be able to put

a good design together.

5.a As already mentioned, the diagrams (timing and block) in UG381 v1.3 are incorrect.

5.b There is no timing diagram or block diagram for ISERDES2 in DDR mode (yet).

5.c We could have a lively debate on the principle of depending on logic models (and simulation) as first-line user documentation.

Let's put it this way: simulation is only as good as the models, the user, and the scope/breadth of the testbench. Knowing in advance

where to focus your (simulation) attention is a big part of successful testbench/simulation. Depending on behavioural model and

simulation is arguably the same as placing a very small needle in a very large haystack without so much as a prior warning to look for

a needle in the first place.

I respect your knowledge and technical insight. In this case, however, our differing perspectives remain a point of respectful

disagreement.

-- Bob Elkind

SIGNATURE:

README for newbies is here: http://forums.xilinx.com/t5/New-Users-Forum/README-first-Help-for-new-users/td-p/219369

Share (http://www.addthis.com/bookmark.php?url=https%3A%2F%2Fforums.xilinx.com%2Ft5%2FSpartan-Family-FPGAs-

Archived%2Funderstanding-BITSLIP-one-more-time%2Ftd-

p%2F105327&title=CORRECTED%3A+understanding+BITSLIP+%28one+more+time%29&username=PoweredByLithium)

0 Kudos

(/t5/user/viewprofilepage/user-id/10)

roym (https://forums.xilinx.com/t5/user/viewprofilepage/user-id/10)

Moderator

Mark as New

Bookmark

Subscribe

Mute

Subscribe to RSS Feed (https://forums.xilinx.com/rss/message?board.id=Spartan&message.id=8092)

Permalink (/t5/Spartan-Family-FPGAs-Archived/understanding-BITSLIP-one-more-time/m-p/105815/highlight/true#M8092)

Print (/t5/forums/forumtopicprintpage/board-id/Spartan/message-id/8092/print-single-message/true/page/1)

Email to a Friend

Report Inappropriate Content (/t5/notifications/notifymoderatorpage/message-uid/105815)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc