RISC-V 指令集手册

卷 2:特权体系结构(Privileged Architecture)

特权体系结构 1.7 版

文档版本 1.7 版

(翻译:要你命 3000@EETOP 翻译版本 1.0)

警告!这个规范的初稿在成为标准之前,可能会被修改,因此基于此规范

初稿的实现,可能与未来的标准规范并不相符。

Andrew Waterman, Yunsup Lee, Rimas Avižienis, David Patterson, Krste Asanović

CS Division, EECS Department, University of California, Berkeley

{waterman|yunsup|rimas|pattrsn|krste}@eecs.berkeley.edu

2015 年 5 月 9 日

该文档同时也是 UCB/EECS-2015-49 技术报告

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

i

�

目录

第 1 章 介绍 ............................................................................................................................... 1

RISC-V 硬件平台术语 ................................................................................................... 1

1.1

RISC-V 特权软件栈术语 ............................................................................................... 2

1.2

1.3 特权级 ........................................................................................................................... 3

第 2 章 控制和状态寄存器(CSR) ......................................................................................... 5

2.1 访问 CSR 的指令........................................................................................................... 5

CSR 地址映射约定 ........................................................................................................ 6

2.2

CSR 列表 ....................................................................................................................... 7

2.3

第 3 章 机器级 ISA .................................................................................................................. 12

3.1 机器级 CSR ................................................................................................................. 12

CPU ID 寄存器 mcpuid .................................................................................... 12

3.1.1

3.1.2 实现 ID 寄存器 mimpid .................................................................................. 13

3.1.3 硬件线程 ID 寄存器 mhartid ......................................................................... 14

3.1.4 机器状态寄存器(mstatus) ........................................................................ 14

mstatus 寄存器中的特权和全局中断使能栈 ............................................... 15

3.1.5

mstatus 寄存器中的虚拟化管理字段 ........................................................... 16

3.1.6

mstatus 寄存器中的存储器特权 ................................................................... 17

3.1.7

mstatus 寄存器中的扩展上下文状况 ........................................................... 17

3.1.8

3.1.9 机器自陷向量基址寄存器(mtvex) ........................................................... 20

3.1.10 机器自陷转移寄存器(mtdeleg) ................................................................ 21

3.1.11 机器中断寄存器(mip 和 mie) ................................................................... 22

3.1.12 机器定时器寄存器(mtime、mtimecmp) ................................................. 23

3.1.13 机器 Scratch 寄存器(mscratch) ................................................................ 24

3.1.14 机器异常程序计数器(mepc) .................................................................... 25

3.1.15 机器原因寄存器(mcause) ........................................................................ 25

3.1.16 机器坏地址寄存器(mbadaddr) ................................................................ 26

3.2 机器模式特权指令 ..................................................................................................... 27

3.2.1 改变特权级的指令 ......................................................................................... 27

3.2.2 自陷重定向指令 ............................................................................................. 27

3.2.3 等待中断 ......................................................................................................... 28

3.3 物理存储器属性 ......................................................................................................... 29

3.4 物理存储器访问控制 ................................................................................................. 29

3.5 Mbare 寻址环境 ......................................................................................................... 30

3.6 基址-边界环境 ........................................................................................................... 30

Mbb:单个基址-边界寄存器(mbase,mbound) .................................... 30

Mbbid:分离的指令和数据基址-边界寄存器 ............................................. 31

第 4 章 管理员级 ISA............................................................................................................... 33

4.1 管理员 CSR ................................................................................................................. 33

4.1.1 管理员状态寄存器(sstatus) ...................................................................... 33

sstatus 寄存器中的存储器特权 ..................................................................... 34

4.1.2

4.1.3 管理员中断寄存器(sip 和 sie) .................................................................. 34

4.1.4 管理员定时器寄存器(stime,stimecmp) ................................................ 35

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

3.6.1

3.6.2

ii

�

4.1.5 管理员 scratch 寄存器(sscratch) .............................................................. 35

4.1.6 管理员异常程序计数器(sepc) .................................................................. 35

4.1.7 管理员原因寄存器(scause) ...................................................................... 36

4.1.8 管理员坏地址寄存器(sbadaddr) .............................................................. 36

4.1.9 管理员页表基址寄存器(sptbr) ................................................................ 37

4.1.10 管理员地址空间 ID 寄存器(sasid) ........................................................... 37

4.2 管理员指令 ................................................................................................................. 38

4.2.1 管理员存储器管理栅栏指令 ......................................................................... 38

4.3 管理员在 Mbare 环境中的操作 ................................................................................ 39

4.4 管理员在基址边界环境中的操作 ............................................................................. 39

Sv32:基于页面的 32 位虚拟存储器系统 ............................................................... 39

4.5

4.5.1 寻址和存储器保护 ......................................................................................... 39

4.5.2 虚拟地址翻译过程 ......................................................................................... 41

Sv39:基于页面的 39 位虚拟存储器系统 ............................................................... 42

4.6.1 寻址和存储器保护 ......................................................................................... 42

Sv48:基于页面的 48 位虚拟存储器系统 ............................................................... 43

4.7.1 寻址和存储器保护 ......................................................................................... 43

Hypervisor 级 ISA ........................................................................................................ 44

第 5 章

第 6 章

RISC-V 特权指令集列表 ............................................................................................. 45

第 7 章 历史 ............................................................................................................................. 46

7.1 资助 ............................................................................................................................. 46

参考文献......................................................................................................................................... 47

4.6

4.7

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

iii

�

第1章 介绍

这是一个 RISC-V 特权体系结构描述文档的初始版本。这个版本与我们当

前的实现并不相符。欢迎反馈。在最终发布版本之前,可能会修改。

本文档描述了 RISC-V 特权体系结构,它覆盖了除了用户级 ISA 之外所有的 RISC-V 其他

方面的内容,包括特权指令、运行操作系统所需的额外功能、接入外部设备。

我们的设计考虑,将出现在类似的文本段落内,如果读者只关心规范,则

可以跳过这些段落。

我们清楚地知道,本文档所描述的整个特权级设计,可以被完全不同的另

外一个特权级设计所替代,而不需要修改用户级 ISA,甚至不需要改变 ABI。

特别地,整个特权级规范被设计成用于运行现有的操作系统,包含了一个传统

的基于层次的保护模型。其他的特权规范可以包含其他某些更为灵活的保护域

模型。

1.1 RISC-V 硬件平台术语

一个 RISC-V 硬件平台可以包含一个或者多个 RISC-V 兼容的核心、其他非 RISC-V 兼容的

核心、固定功能的加速器、各种物理存储器结构、I/O 设备以及一个允许这些部件相互通信

的互联结构。

一个部件被称为“核心(core)”,如果它包含了一个独立的指令取指单元。一个 RISC-V

兼容核心可能通过多线程技术支持多个 RISC-V 兼容硬件线程,或者 harts。

一个 RISC-V 核心可能有额外的专有指令集扩展或者一个增加的协处理器(coprocessor)。

我们使用术语协处理器,指的是一个接入到 RISC-V 核心的单元,绝大部分时间被 RISC-V 指

令流序列化,但它包含了一些额外的体系结构状态和指令集扩展,并有可能相对于主要的

RISC-V 指令流来说,有一定的自治。

我们使用术语加速器(accelerator),指的是一个要么不能编程的固定功能单元,要么

是一个可以自治工作、但专门用于某项任务的核心。在 RISC-V 系统中,我们预期许多可编

程加速器将会是基于 RISC-V 核心的,包含专门的指令集扩展,和/或定制化的协处理器。一

类重要的 RISC-V 加速器是 I/O 加速器,它将 I/O 处理任务从主要应用核心上卸载负载(offload)。

RISC-V 硬件平台的系统级组织结构,可以从单个核心的微控制器,到一个拥有共享存储

器众核(manycore)服务器作为节点的数千个节点的集群系统。即使是小型的片上系统

(System on a chip)也可能是结构化的,包含层次化的多个计算机和/或多个处理器,以便

能够模块化设计研发或者在不同的子系统之间提供安全隔离。

本文档重点关注运行在一个单处理器或者一个共享存储器多处理器中的每一个 hart(硬

件线程)可以看到的特权体系结构。

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

1

�

1.2 RISC-V 特权软件栈术语

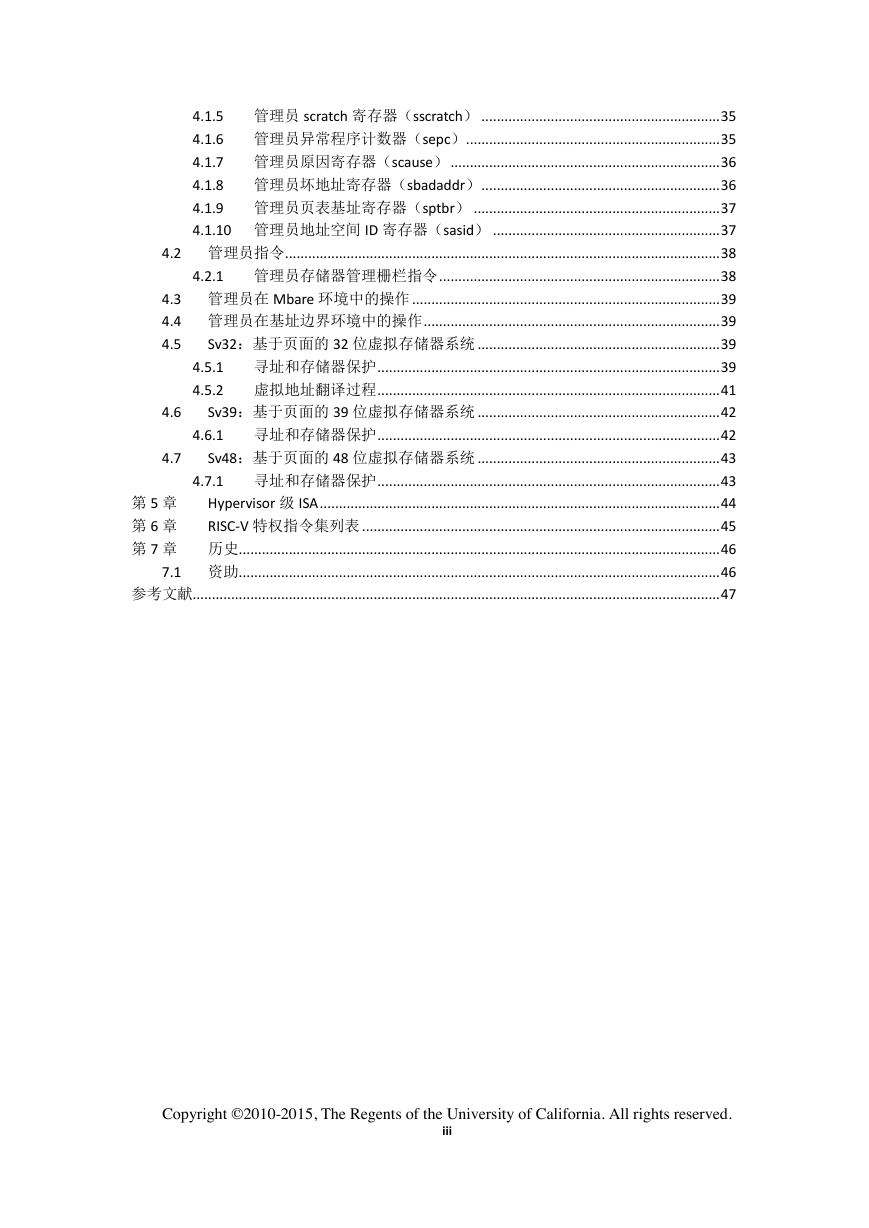

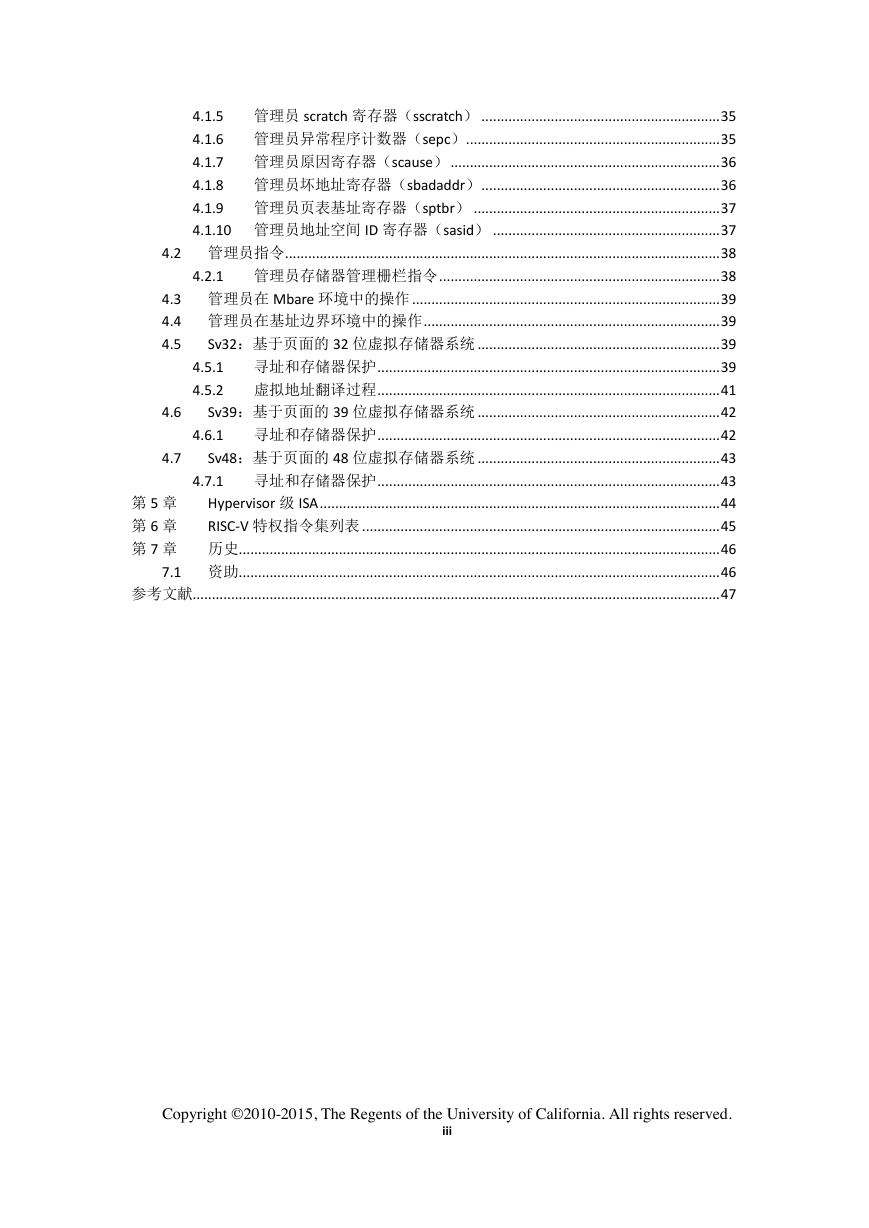

本节描述我们用于描述 RISC-V 各种各样可能的特权软件栈中的部件术语。

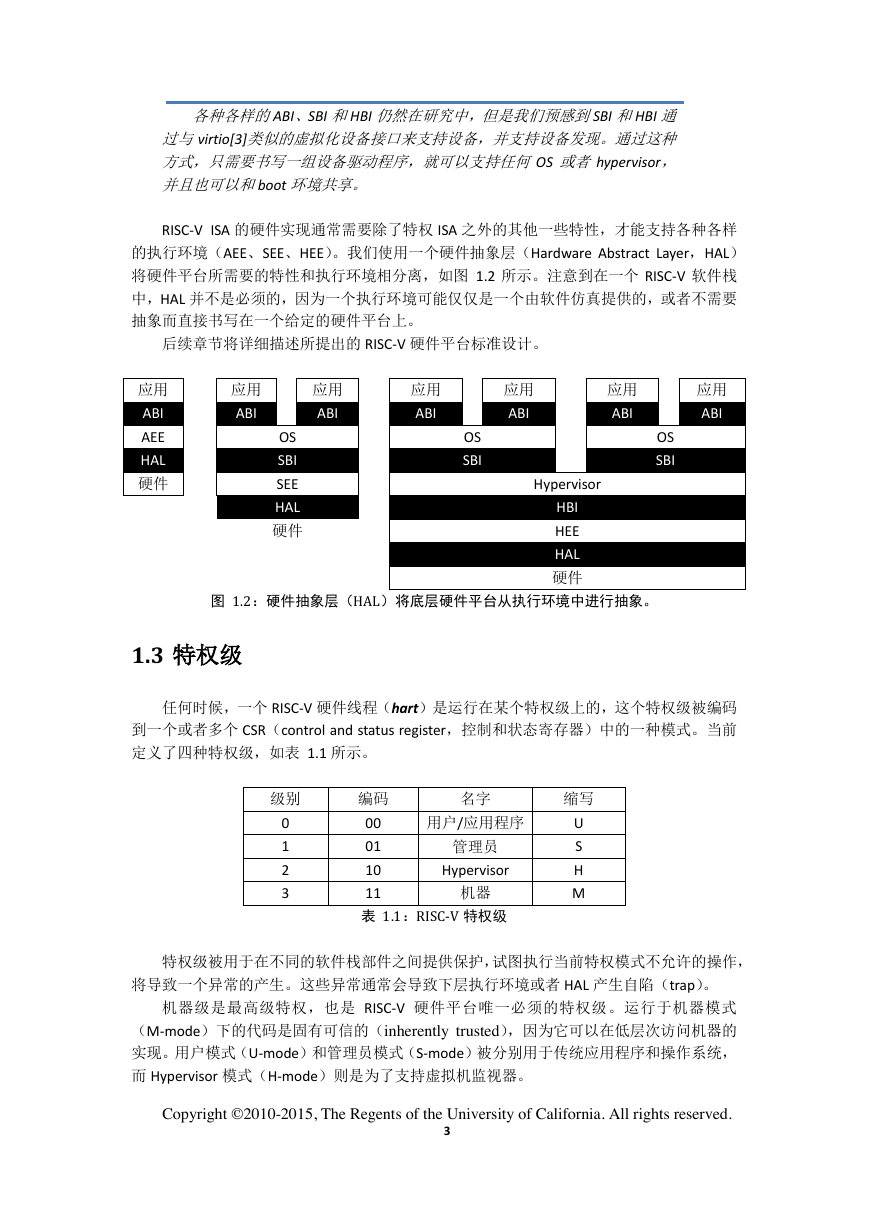

图 1.1 给出了 RISC-V 体系结构支持的可能的软件栈。最左边的图给出了一个简单的系

统,它只支持单个应用程序运行在一个应用执行环境(Application Execution Environment, AEE)

上。这个应用程序被编码为与一个特定的应用程序二进制接口(Application Binary Interface,

ABI)运行。这个 ABI 包含所支持的用户级 ISA,加上一堆与 AEE 交互的 ABI 调用。ABI 对应

用程序隐藏了 AEE 的细节,使得实现 AEE 具有更大的灵活性。同样的 ABI 可被直接实现在多

个不同的主机操作系统上,或者被一个用户模式下的仿真环境支持,这个仿真环境运行在一

个不同的 ISA 机器上。(译者注:就像虚拟机,或者指令模拟器)

应用

ABI

应用

ABI

OS

SBI

SEE

应用

ABI

应用

ABI

OS

SBI

应用

ABI

应用

ABI

OS

SBI

Hypervisor

HBI

HEE

图 1.1:不同实现的栈,支持各种形式的特权执行

应用

ABI

AEE

在我们的图形表示中,用黑底白字表示抽象接口,将它们与实现接口的具

体部件实例相区分开来。

中间的配置显示了一个传统的操作系统(OS),可支持多个应用程序的多道运行。每个

应用程序通过 ABI 与 OS 通信,OS 提供了 AEE。正如同应用程序通过 ABI 与 AEE 通信一样,

RISC-V 操作系统通过一个管理员二进制接口(Supervisor Binary Interface,SBI)与管理员执

行环境(Supervisor Execution Environment,SEE)通信。一个 SBI 包含了用户级和管理员级

ISA,以及一堆 SBI 函数调用。在所有 SEE 实现中,使用单一的 SBI,允许单一的 OS 二进制

镜像运行于任何 SEE 之上。在低端的硬件平台上,SEE 可以只是一个简单的 boot loader 和

BIOS 类型的 IO 系统,在高端服务器上,SEE 可以是一个提供 hypervisor 的虚拟机,或者在

一个体系结构仿真环境中,SEE 可以是一个运行在主机操作系统上的“很薄的”转换层。

绝大多数管理员级ISA 定义,并没有将SBI 和执行环境和/或硬件平台进行

区分,使得虚拟化和开发新的硬件平台变得复杂化。

最右侧的配置显示了一个虚拟机监视器配置,此处由一个单一的 hypervisor 支持多个多

道操作系统。每个 OS 通过一个 SBI 与 hypervisor 通信,hypervisor 提供了 SEE。Hypervisor

使用一个 hypervisor 二进制接口(Hypervisor Binary Interface,HBI)与 hypervisor 执行环境

(Hypervisor Execution Environment,HEE)通信,这将把 hypervisor 与具体的硬件平台细节

相隔离。

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

2

�

各种各样的ABI、SBI 和HBI 仍然在研究中,但是我们预感到SBI 和HBI 通

过与virtio[3]类似的虚拟化设备接口来支持设备,并支持设备发现。通过这种

方式,只需要书写一组设备驱动程序,就可以支持任何 OS 或者 hypervisor,

并且也可以和boot 环境共享。

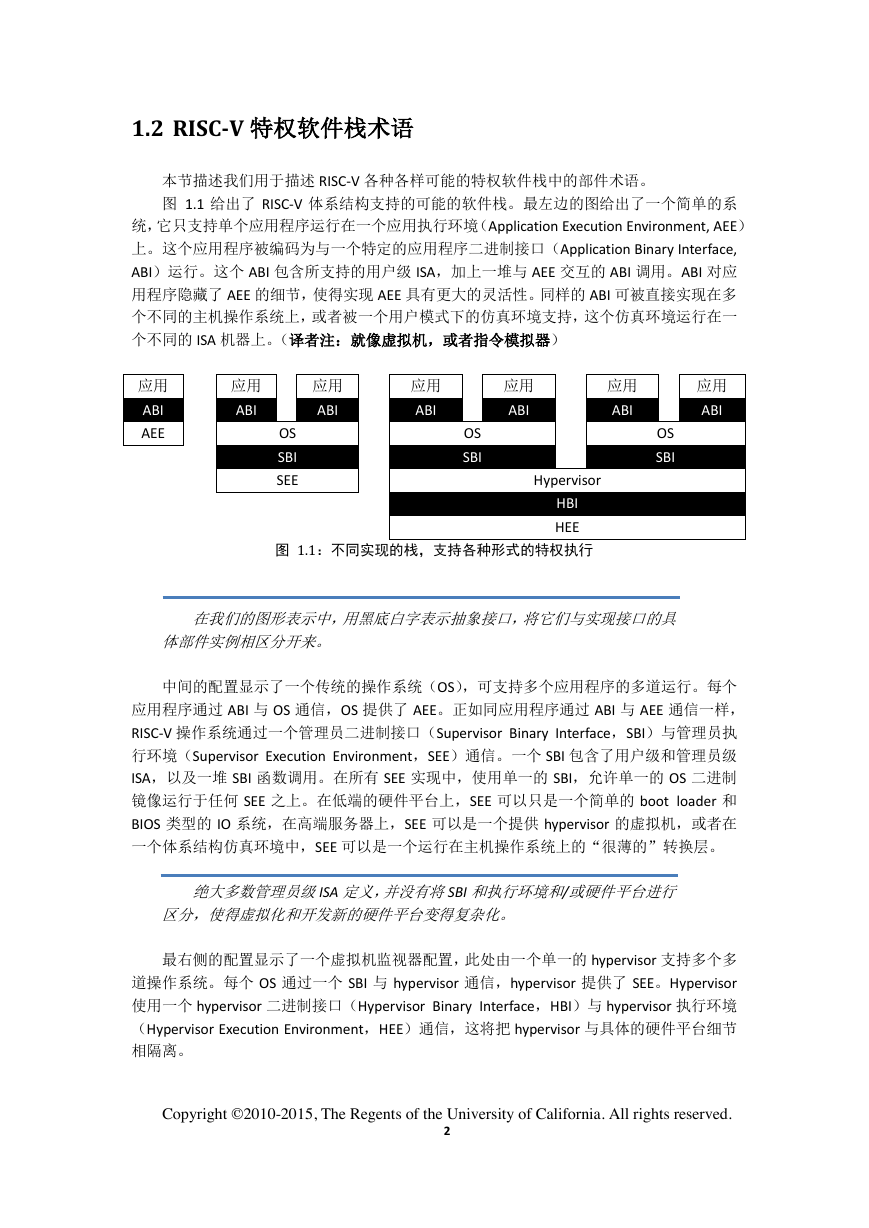

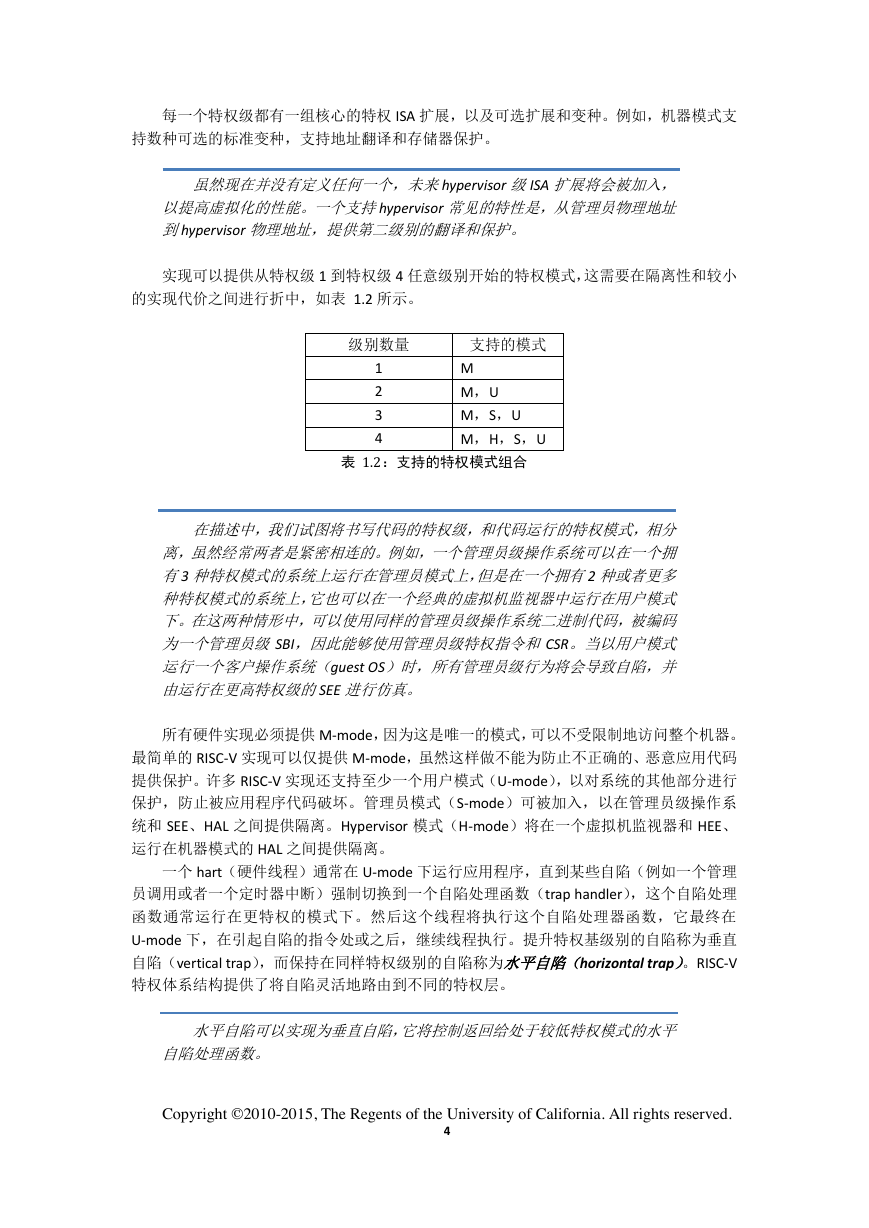

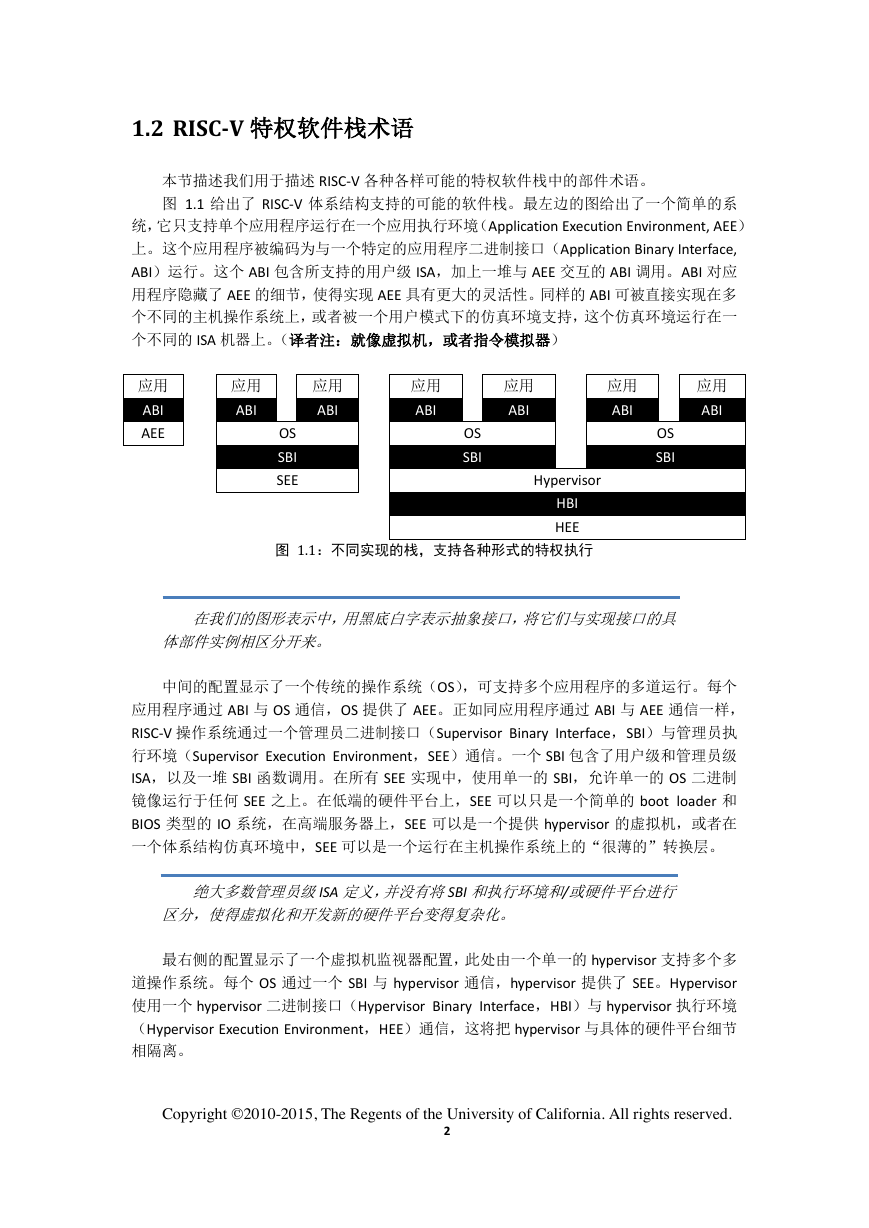

RISC-V ISA 的硬件实现通常需要除了特权 ISA 之外的其他一些特性,才能支持各种各样

的执行环境(AEE、SEE、HEE)。我们使用一个硬件抽象层(Hardware Abstract Layer,HAL)

将硬件平台所需要的特性和执行环境相分离,如图 1.2 所示。注意到在一个 RISC-V 软件栈

中,HAL 并不是必须的,因为一个执行环境可能仅仅是一个由软件仿真提供的,或者不需要

抽象而直接书写在一个给定的硬件平台上。

后续章节将详细描述所提出的 RISC-V 硬件平台标准设计。

应用

ABI

AEE

HAL

硬件

应用

ABI

应用

ABI

OS

SBI

SEE

HAL

硬件

应用

ABI

应用

ABI

OS

SBI

应用

ABI

应用

ABI

OS

SBI

Hypervisor

HBI

HEE

HAL

硬件

图 1.2:硬件抽象层(HAL)将底层硬件平台从执行环境中进行抽象。

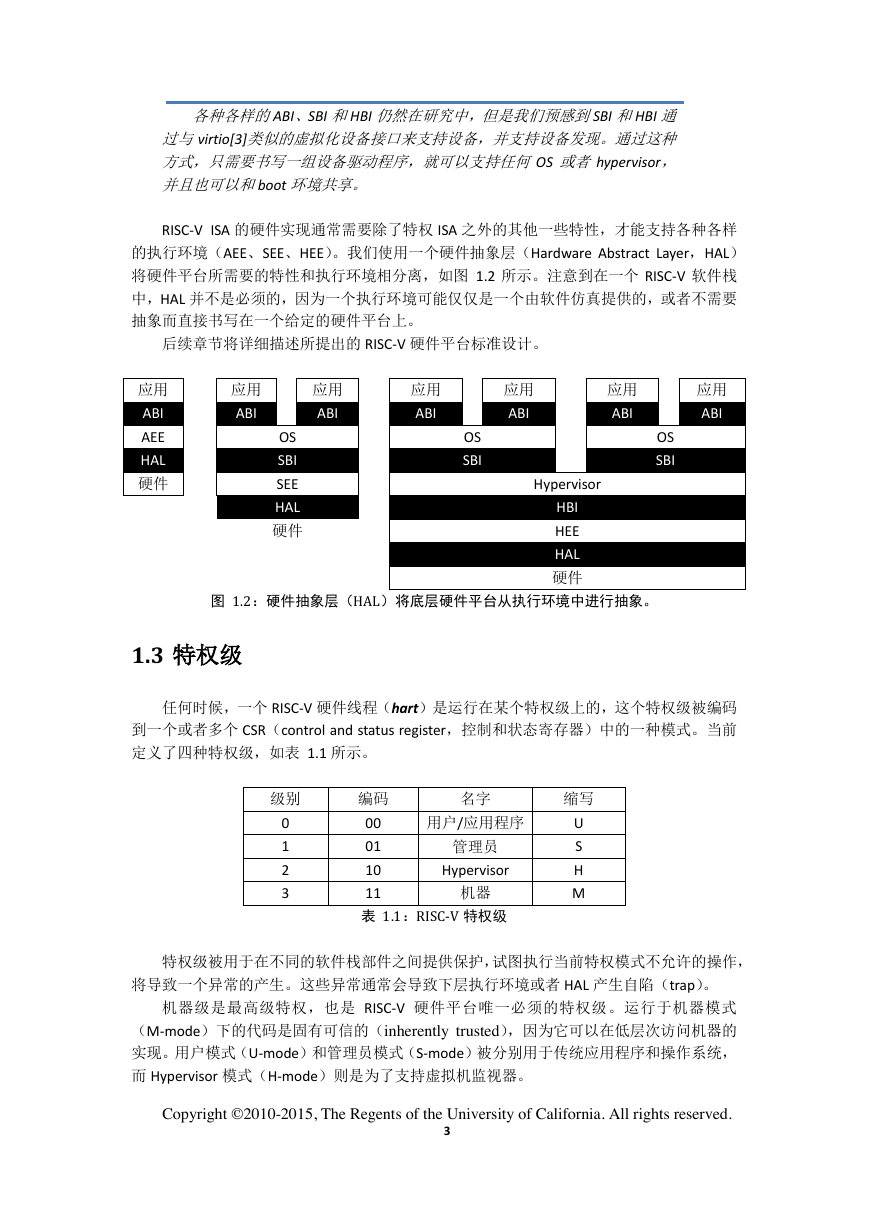

1.3 特权级

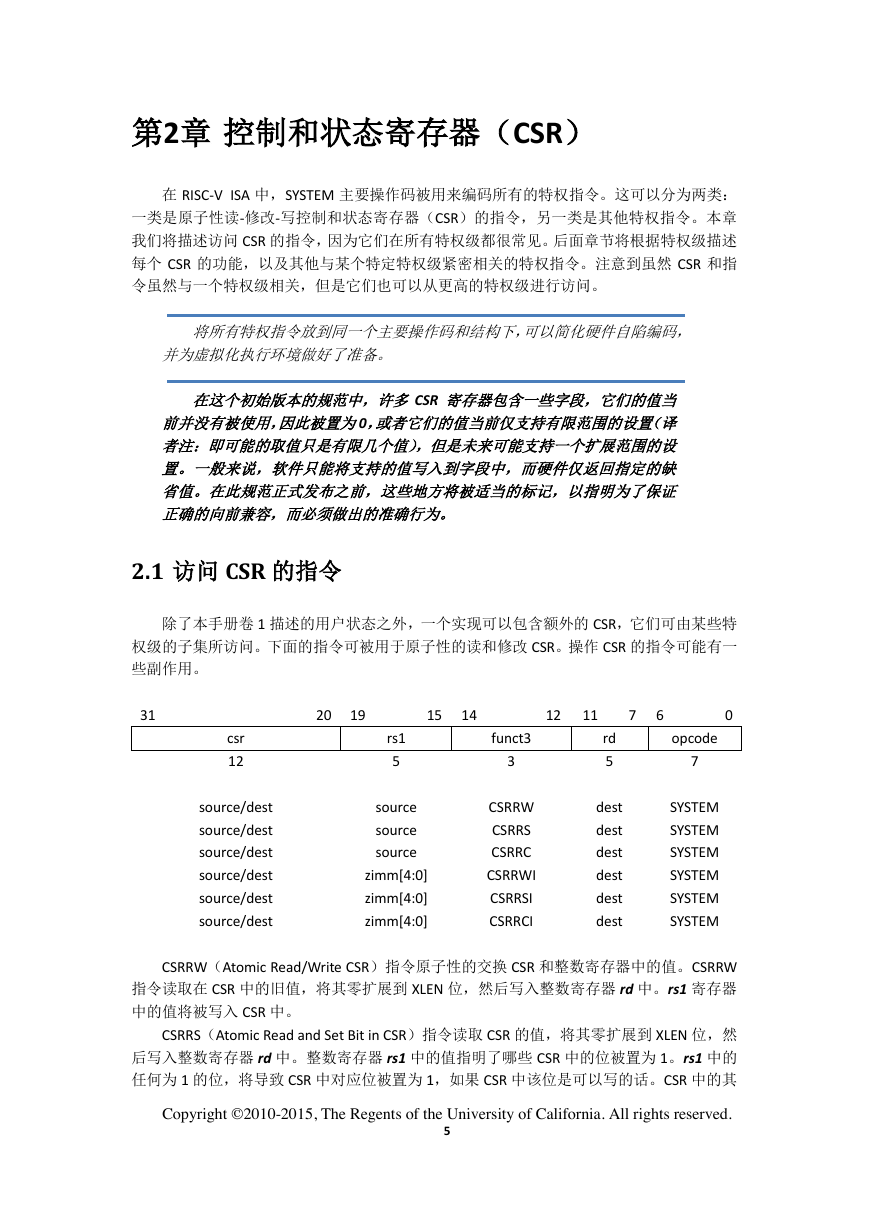

任何时候,一个 RISC-V 硬件线程(hart)是运行在某个特权级上的,这个特权级被编码

到一个或者多个 CSR(control and status register,控制和状态寄存器)中的一种模式。当前

定义了四种特权级,如表 1.1 所示。

级别

0

1

2

3

编码

00

01

10

用户/应用程序

管理员

Hypervisor

11

表 1.1:RISC-V 特权级

机器

名字

缩写

U

S

H

M

特权级被用于在不同的软件栈部件之间提供保护,试图执行当前特权模式不允许的操作,

将导致一个异常的产生。这些异常通常会导致下层执行环境或者 HAL 产生自陷(trap)。

机器级是最高级特权,也是 RISC-V 硬件平台唯一必须的特权级。运行于机器模式

(M-mode)下的代码是固有可信的(inherently trusted),因为它可以在低层次访问机器的

实现。用户模式(U-mode)和管理员模式(S-mode)被分别用于传统应用程序和操作系统,

而 Hypervisor 模式(H-mode)则是为了支持虚拟机监视器。

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

3

�

每一个特权级都有一组核心的特权 ISA 扩展,以及可选扩展和变种。例如,机器模式支

持数种可选的标准变种,支持地址翻译和存储器保护。

虽然现在并没有定义任何一个,未来hypervisor 级ISA 扩展将会被加入,

以提高虚拟化的性能。一个支持hypervisor 常见的特性是,从管理员物理地址

到hypervisor 物理地址,提供第二级别的翻译和保护。

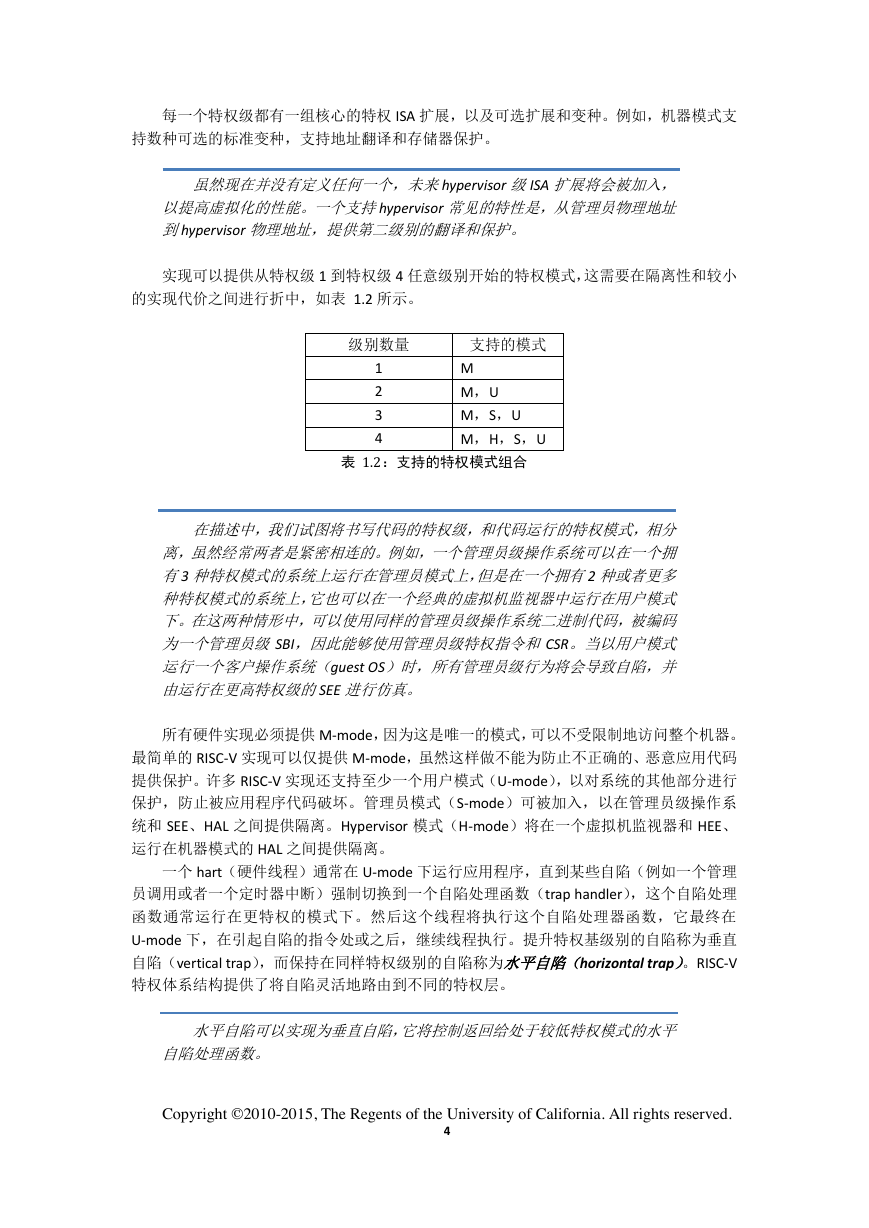

实现可以提供从特权级 1 到特权级 4 任意级别开始的特权模式,这需要在隔离性和较小

的实现代价之间进行折中,如表 1.2 所示。

级别数量

1

2

3

4

支持的模式

M

M,U

M,S,U

M,H,S,U

表 1.2:支持的特权模式组合

在描述中,我们试图将书写代码的特权级,和代码运行的特权模式,相分

离,虽然经常两者是紧密相连的。例如,一个管理员级操作系统可以在一个拥

有3 种特权模式的系统上运行在管理员模式上,但是在一个拥有2 种或者更多

种特权模式的系统上,它也可以在一个经典的虚拟机监视器中运行在用户模式

下。在这两种情形中,可以使用同样的管理员级操作系统二进制代码,被编码

为一个管理员级SBI,因此能够使用管理员级特权指令和CSR。当以用户模式

运行一个客户操作系统(guest OS)时,所有管理员级行为将会导致自陷,并

由运行在更高特权级的SEE 进行仿真。

所有硬件实现必须提供 M-mode,因为这是唯一的模式,可以不受限制地访问整个机器。

最简单的 RISC-V 实现可以仅提供 M-mode,虽然这样做不能为防止不正确的、恶意应用代码

提供保护。许多 RISC-V 实现还支持至少一个用户模式(U-mode),以对系统的其他部分进行

保护,防止被应用程序代码破坏。管理员模式(S-mode)可被加入,以在管理员级操作系

统和 SEE、HAL 之间提供隔离。Hypervisor 模式(H-mode)将在一个虚拟机监视器和 HEE、

运行在机器模式的 HAL 之间提供隔离。

一个 hart(硬件线程)通常在 U-mode 下运行应用程序,直到某些自陷(例如一个管理

员调用或者一个定时器中断)强制切换到一个自陷处理函数(trap handler),这个自陷处理

函数通常运行在更特权的模式下。然后这个线程将执行这个自陷处理器函数,它最终在

U-mode 下,在引起自陷的指令处或之后,继续线程执行。提升特权基级别的自陷称为垂直

自陷(vertical trap),而保持在同样特权级别的自陷称为水平自陷(horizontal trap)。RISC-V

特权体系结构提供了将自陷灵活地路由到不同的特权层。

水平自陷可以实现为垂直自陷,它将控制返回给处于较低特权模式的水平

自陷处理函数。

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

4

�

第2章 控制和状态寄存器(CSR)

在 RISC-V ISA 中,SYSTEM 主要操作码被用来编码所有的特权指令。这可以分为两类:

一类是原子性读-修改-写控制和状态寄存器(CSR)的指令,另一类是其他特权指令。本章

我们将描述访问 CSR 的指令,因为它们在所有特权级都很常见。后面章节将根据特权级描述

每个 CSR 的功能,以及其他与某个特定特权级紧密相关的特权指令。注意到虽然 CSR 和指

令虽然与一个特权级相关,但是它们也可以从更高的特权级进行访问。

将所有特权指令放到同一个主要操作码和结构下,可以简化硬件自陷编码,

并为虚拟化执行环境做好了准备。

在这个初始版本的规范中,许多 CSR 寄存器包含一些字段,它们的值当

前并没有被使用,因此被置为0,或者它们的值当前仅支持有限范围的设置(译

者注:即可能的取值只是有限几个值),但是未来可能支持一个扩展范围的设

置。一般来说,软件只能将支持的值写入到字段中,而硬件仅返回指定的缺

省值。在此规范正式发布之前,这些地方将被适当的标记,以指明为了保证

正确的向前兼容,而必须做出的准确行为。

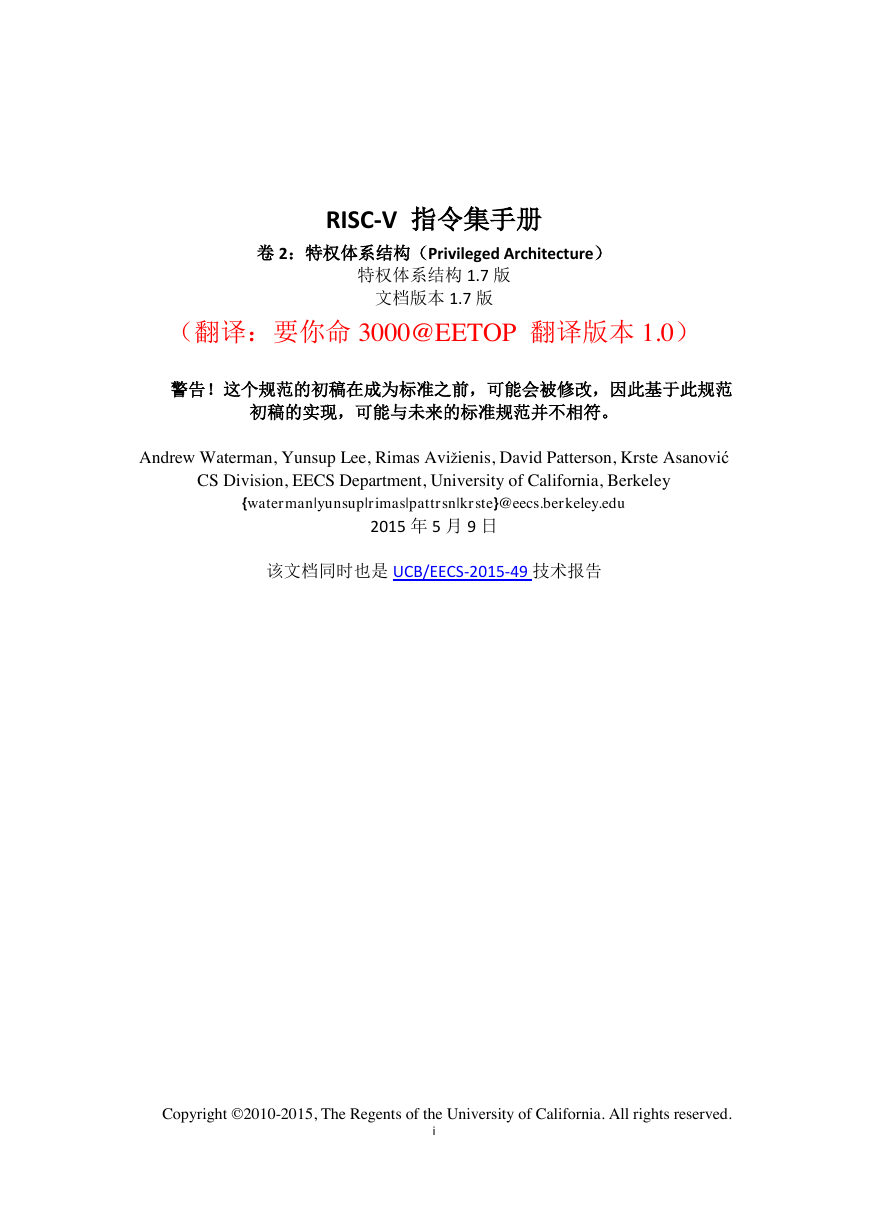

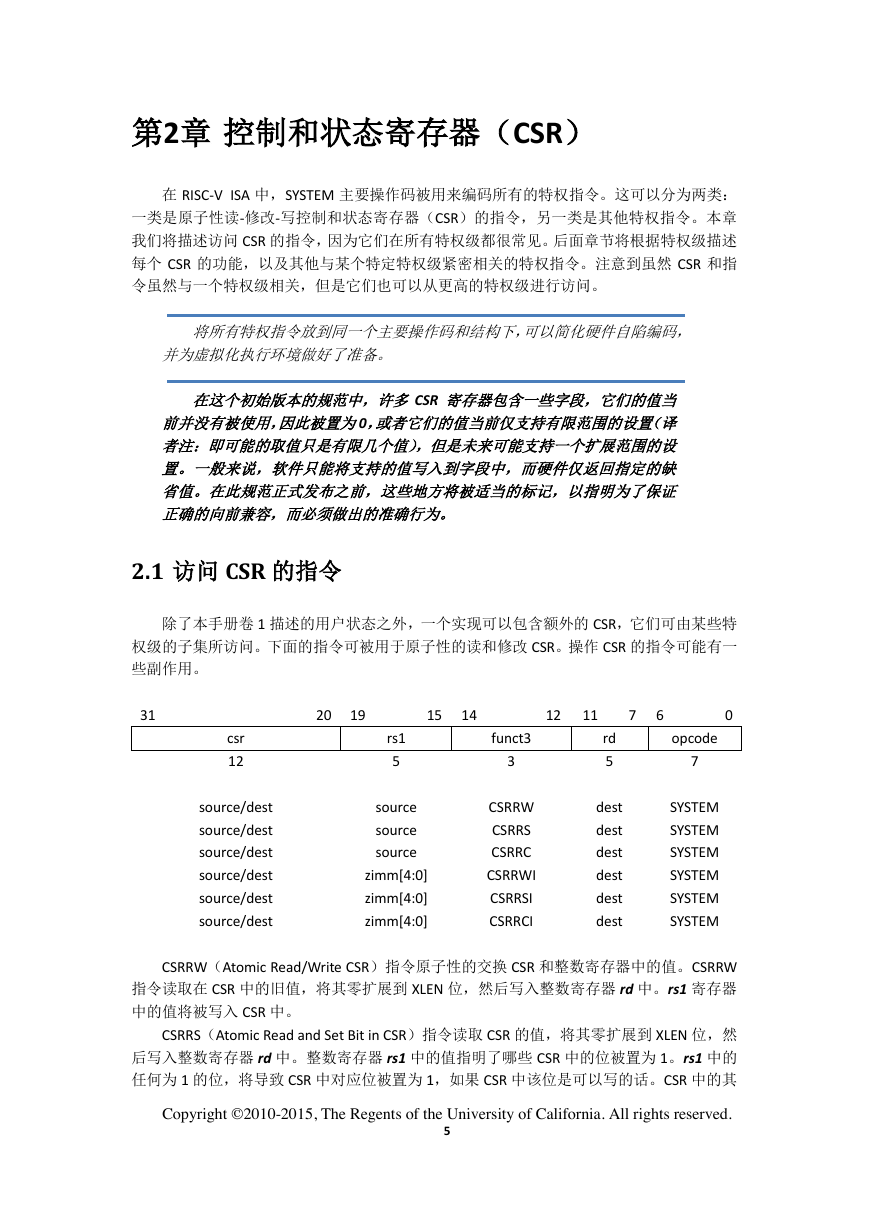

2.1 访问 CSR 的指令

除了本手册卷 1 描述的用户状态之外,一个实现可以包含额外的 CSR,它们可由某些特

权级的子集所访问。下面的指令可被用于原子性的读和修改 CSR。操作 CSR 的指令可能有一

些副作用。

31 20 19 15 14 12

11 7

6 0

csr

12

source/dest

source/dest

source/dest

source/dest

source/dest

source/dest

rs1

5

source

source

source

zimm[4:0]

zimm[4:0]

zimm[4:0]

funct3

3

CSRRW

CSRRS

CSRRC

CSRRWI

CSRRSI

CSRRCI

rd

5

dest

dest

dest

dest

dest

dest

opcode

7

SYSTEM

SYSTEM

SYSTEM

SYSTEM

SYSTEM

SYSTEM

CSRRW(Atomic Read/Write CSR)指令原子性的交换 CSR 和整数寄存器中的值。CSRRW

指令读取在 CSR 中的旧值,将其零扩展到 XLEN 位,然后写入整数寄存器 rd 中。rs1 寄存器

中的值将被写入 CSR 中。

CSRRS(Atomic Read and Set Bit in CSR)指令读取 CSR 的值,将其零扩展到 XLEN 位,然

后写入整数寄存器 rd 中。整数寄存器 rs1 中的值指明了哪些 CSR 中的位被置为 1。rs1 中的

任何为 1 的位,将导致 CSR 中对应位被置为 1,如果 CSR 中该位是可以写的话。CSR 中的其

Copyright ©2010-2015, The Regents of the University of California. All rights reserved.

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc