Quartus II 调用 ModelSim 仿真

下面是基于在 Altera Quartus II 下如何调用 ModelSim 进行仿真的一个实例。

不能否认,Quartus II(我用的 7.0)无法像 ISE 那样方便的直接调用 ModelSim,

而是需要额外的做一些工作。这确实给我们的仿真调试带来了一些不便。特权同

学也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让

大家少走一些弯路。

1、 打开 Quartus II,新建一个工程,工程代码如下(只是做一个简单的二分

频电路):

module modelsim_test(

input clk;

clk,rst_n,div

);

//系统时钟

input rst_n;

//复位信号,低有效

output div;

//2 分频信号

reg div;

always @ (posedge clk or negedge rst_n)

if(!rst_n) div <= 1'b0;

else div <= ~div;

endmodule

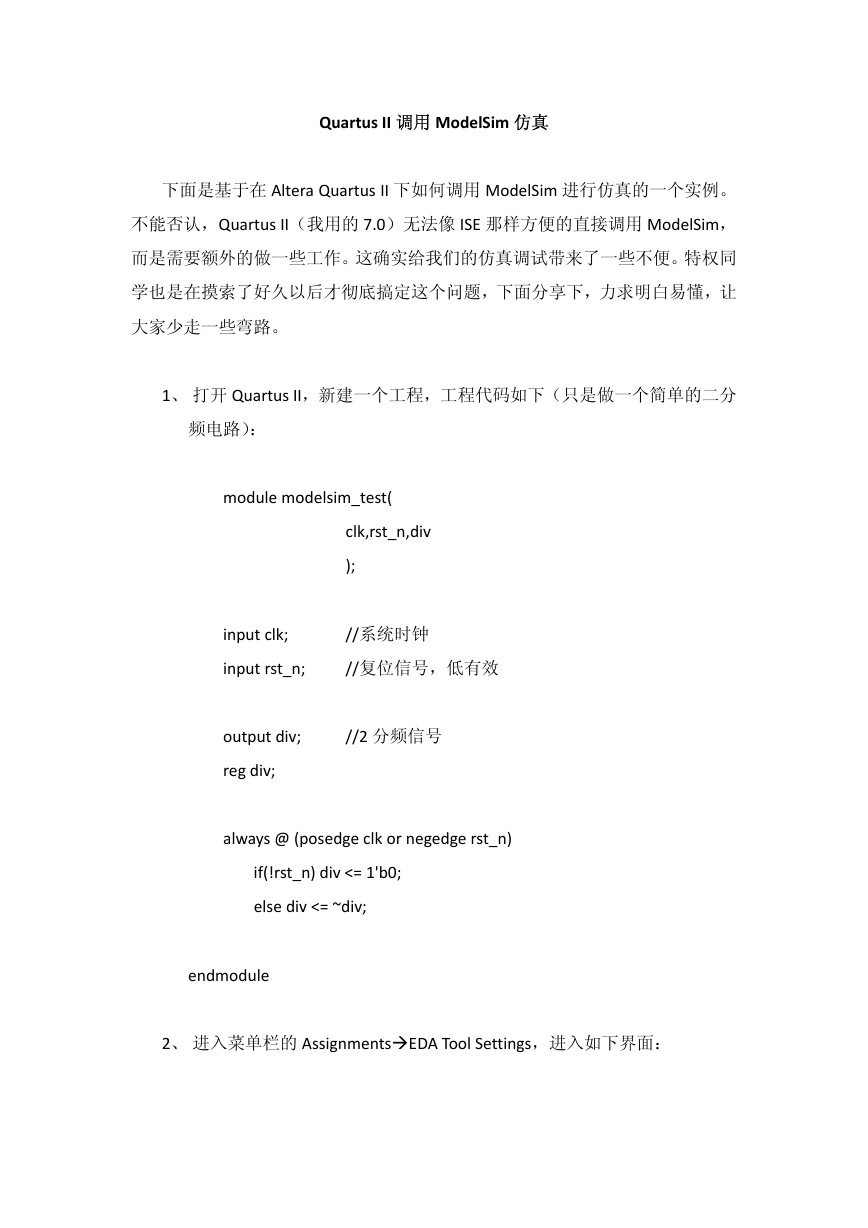

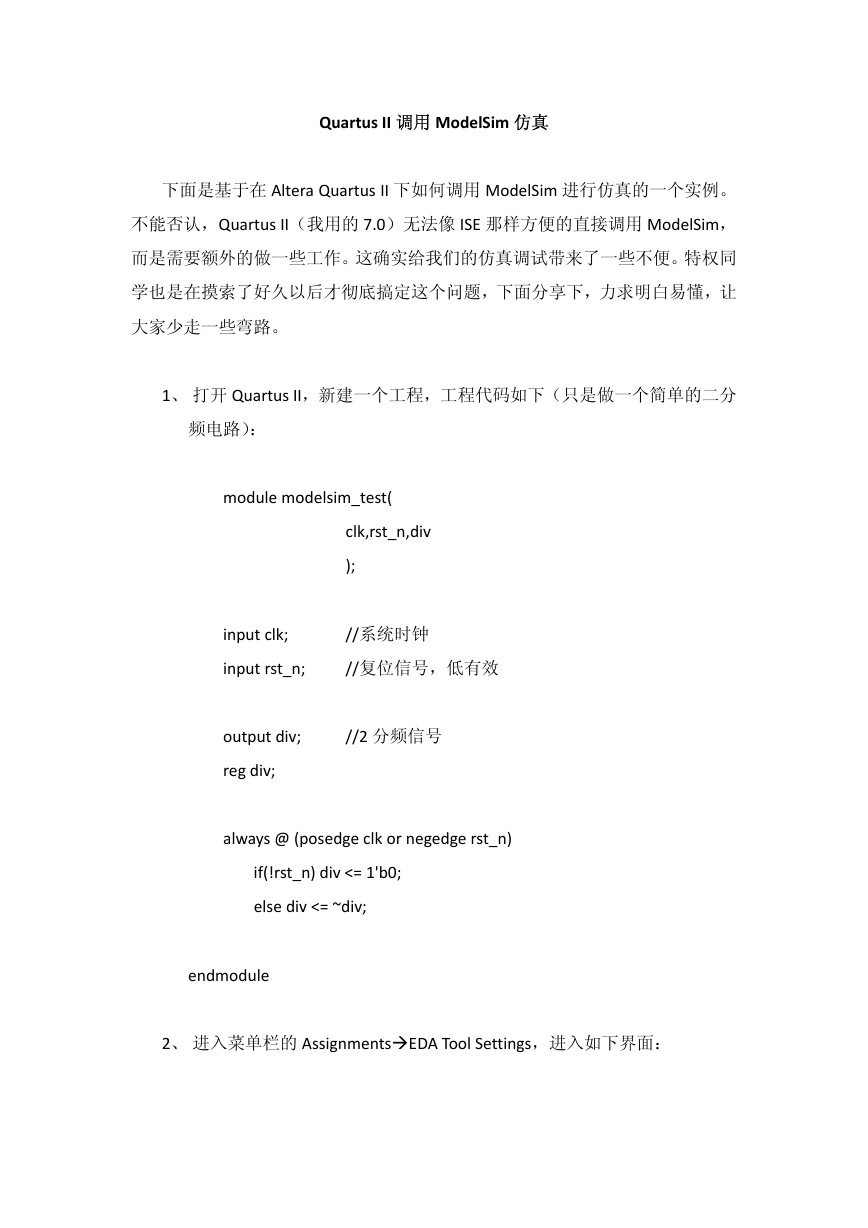

2、 进入菜单栏的 AssignmentsEDA Tool Settings,进入如下界面:

�

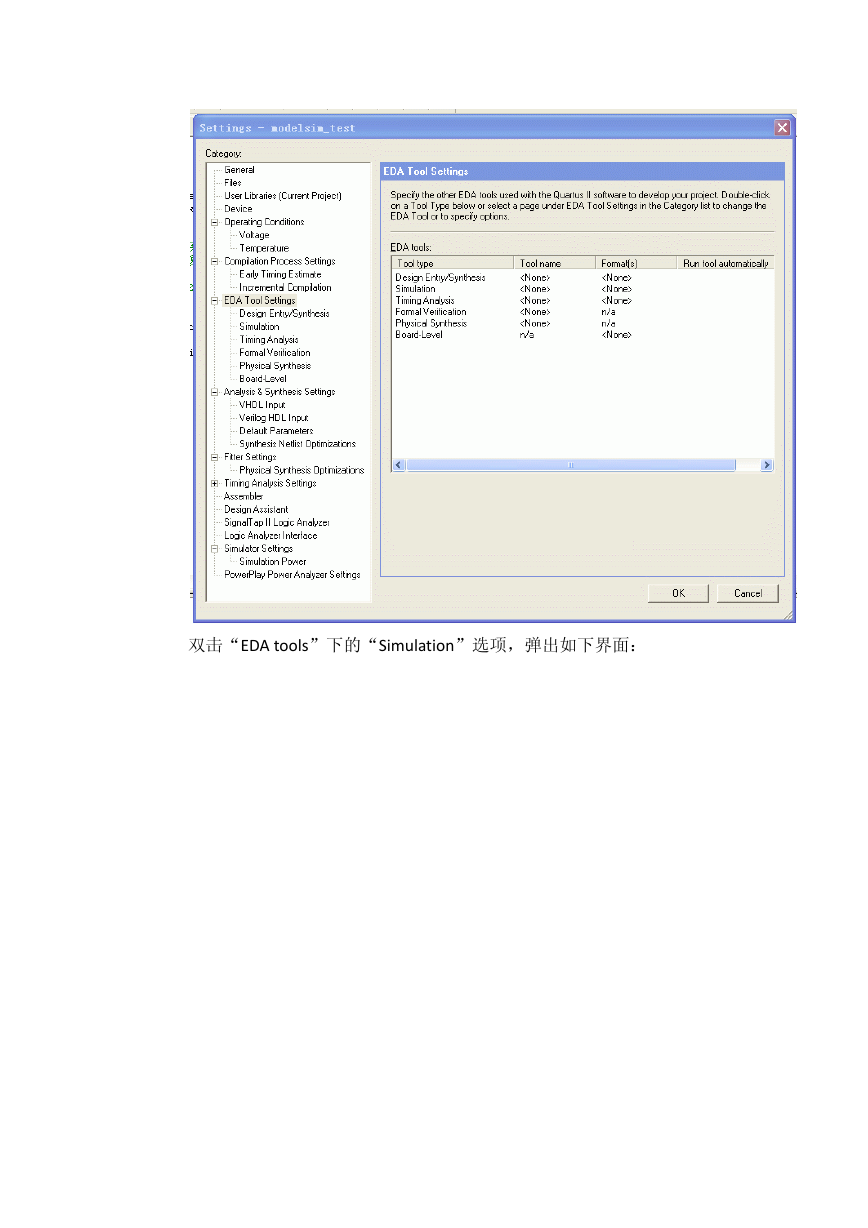

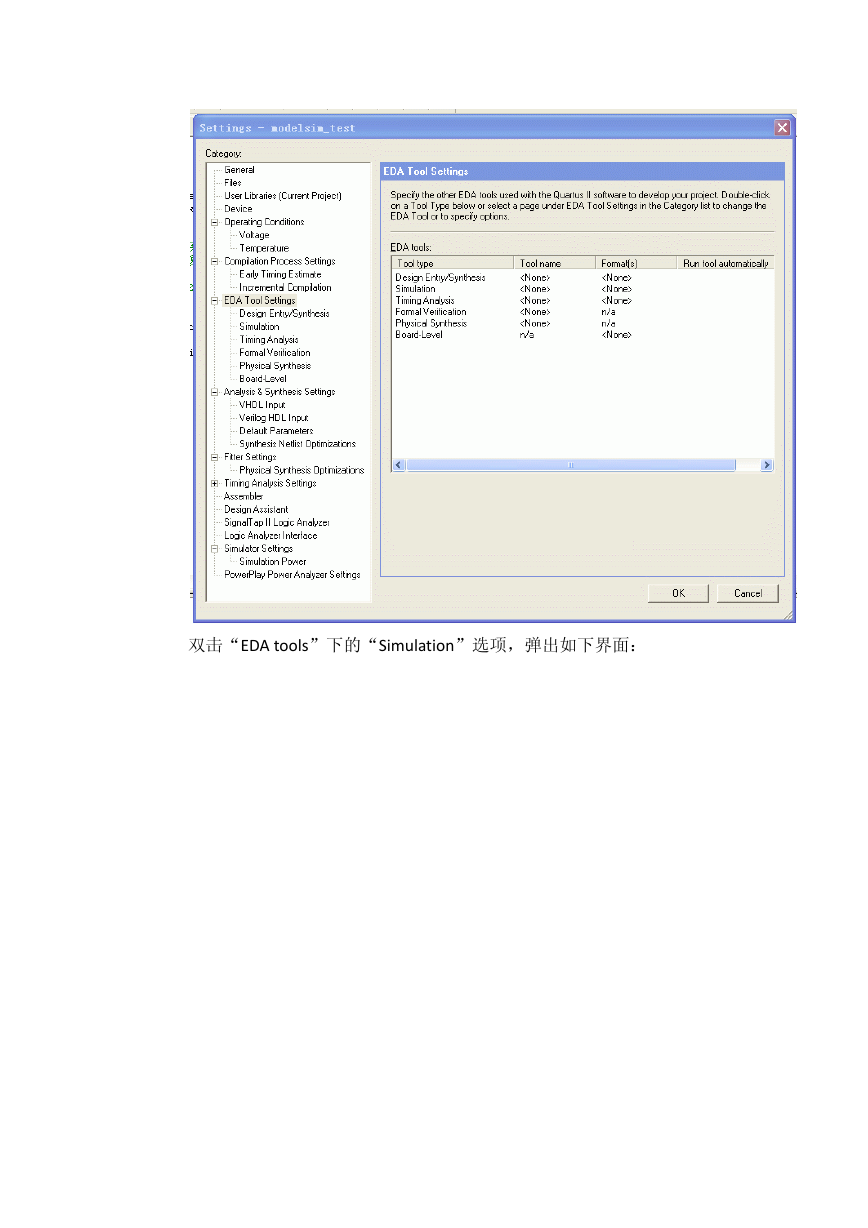

双击“EDA tools”下的“Simulation”选项,弹出如下界面:

�

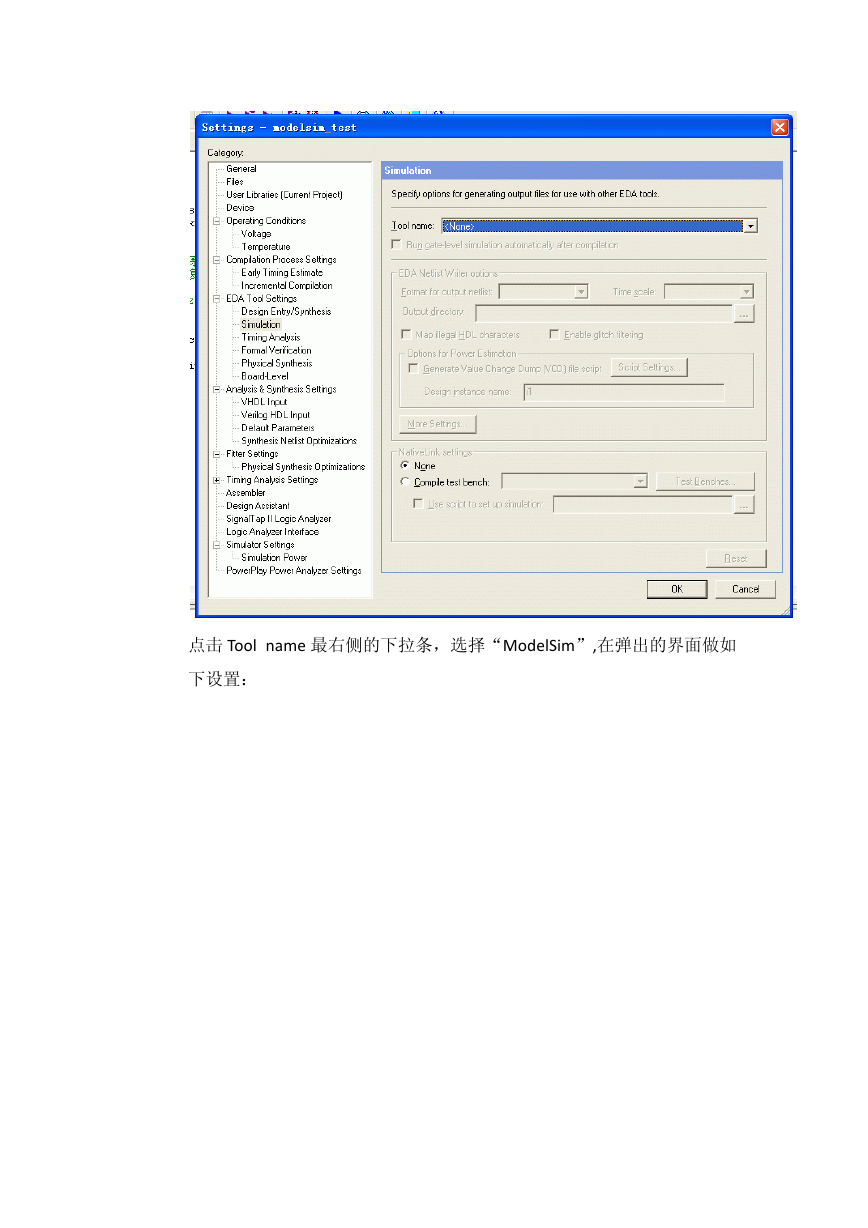

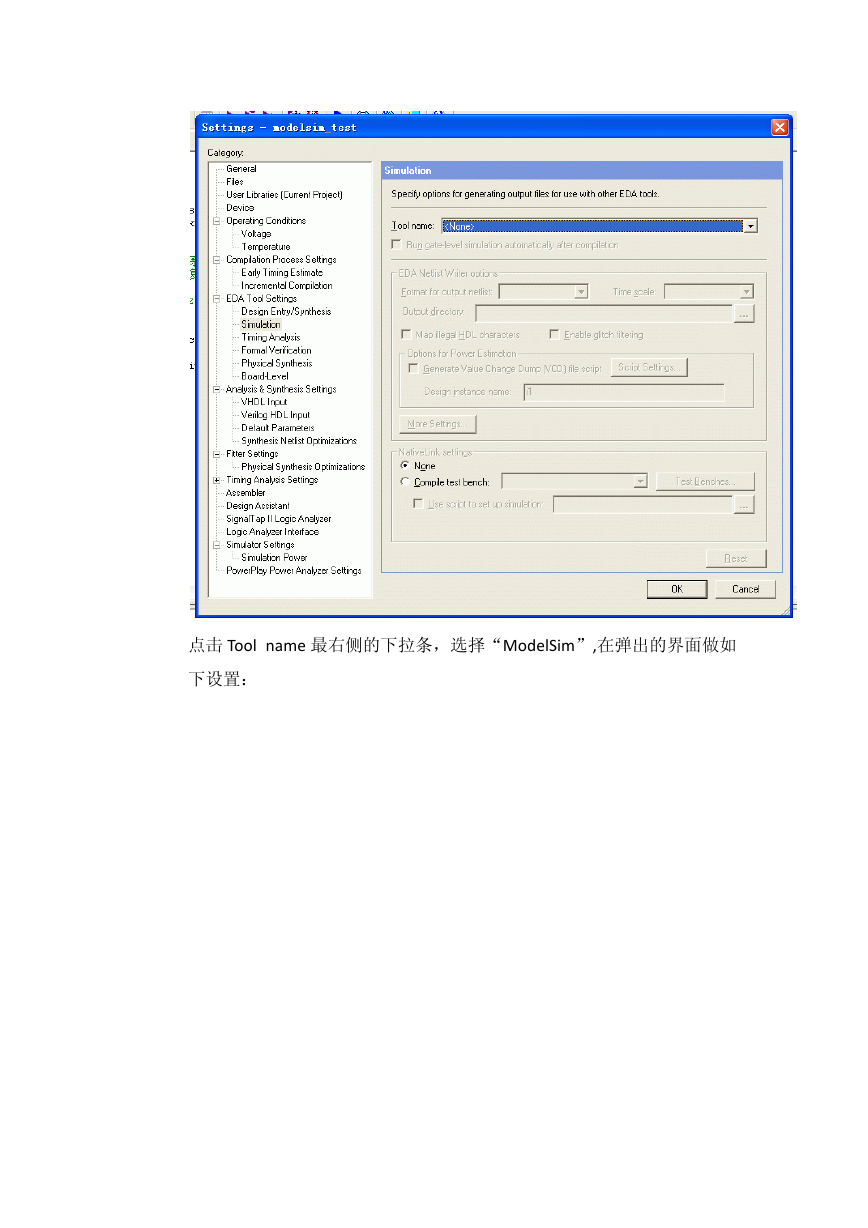

点击 Tool name 最右侧的下拉条,选择“ModelSim”,在弹出的界面做如

下设置:

�

3、 以上设置完成,重新编译工程。打开工程目录,看到多了一个“simulation”

文件夹,再打开该文件夹下的“modelsim”文件夹。看到有三个文件,

其中.vo 文件就是我们的代码布局布线信息。仿真还需要几个文件,我们

把它们都拷贝到该目录下。

4、 打开“C:\altera\70\quartus\eda\sim_lib”(具体 quartus 软件安装文件的

根目录视您的实际情况而定,大体路径都一样),因为我们用的是 MAX II

器件,所以把“maxii_atoms.v”拷贝到 3 中提到的目录下,这个文件是仿

真元件库。

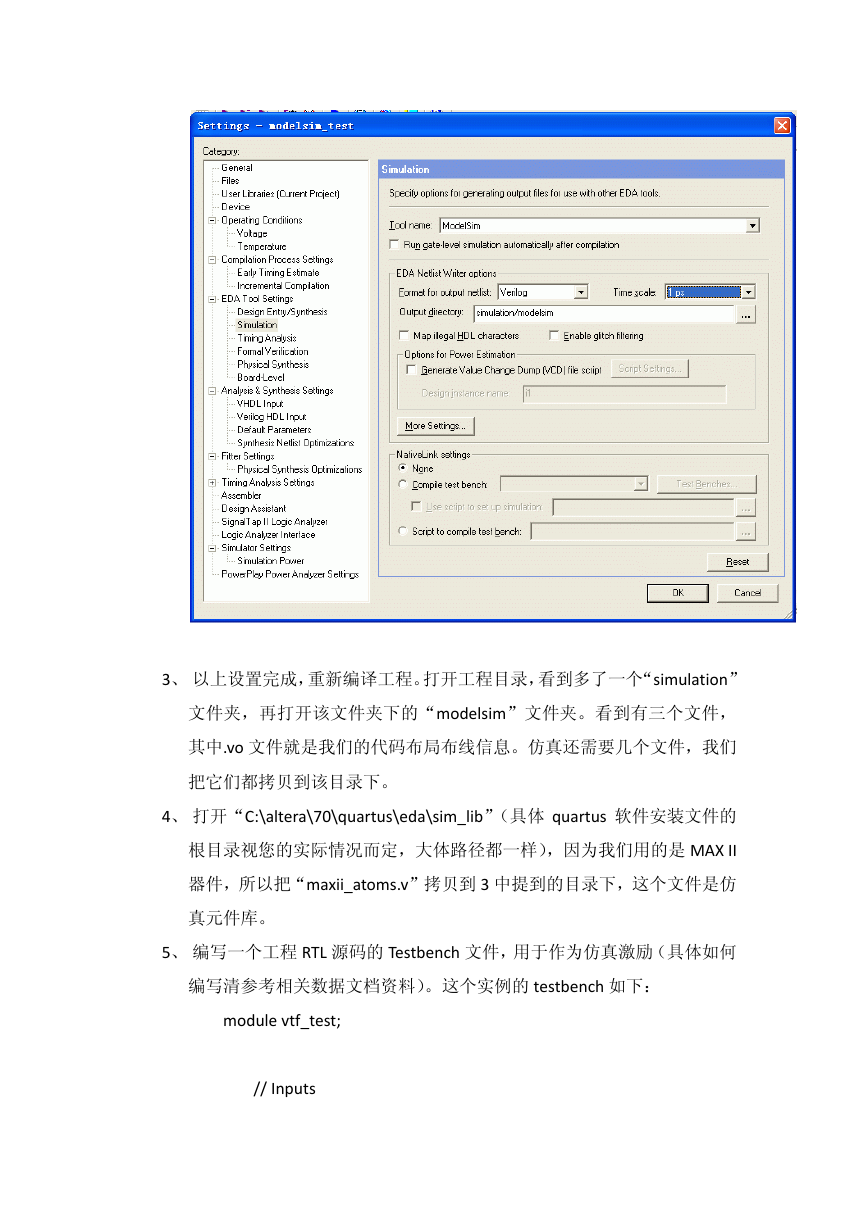

5、 编写一个工程 RTL 源码的 Testbench 文件,用于作为仿真激励(具体如何

编写清参考相关数据文档资料)。这个实例的 testbench 如下:

module vtf_test;

// Inputs

�

reg clk;

reg rst_n;

// Output

wire div;

modelsim_test

u1(

.clk(clk),

.rst_n(rst_n),

.div(div)

);

initial begin

clk = 0;

forever

#10 clk = ~clk;

//产生 50MHz 的时钟

end

initial begin

rst_n = 0;

#1000 rst_n = 1; //上电后 1us 复位信号

#1000;

$stop;

end

endmodule

将该文件命名为 tb_test.v,保存到 3 提到的文件夹下。

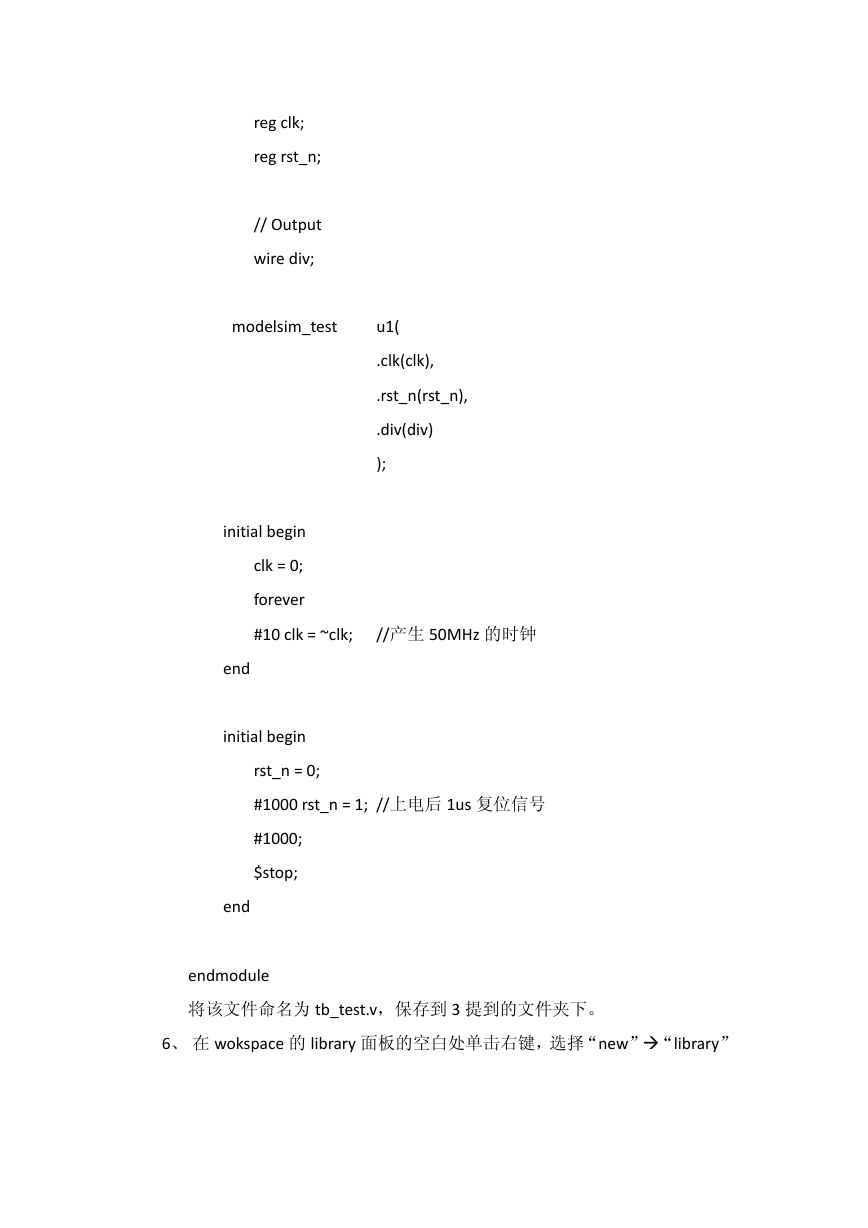

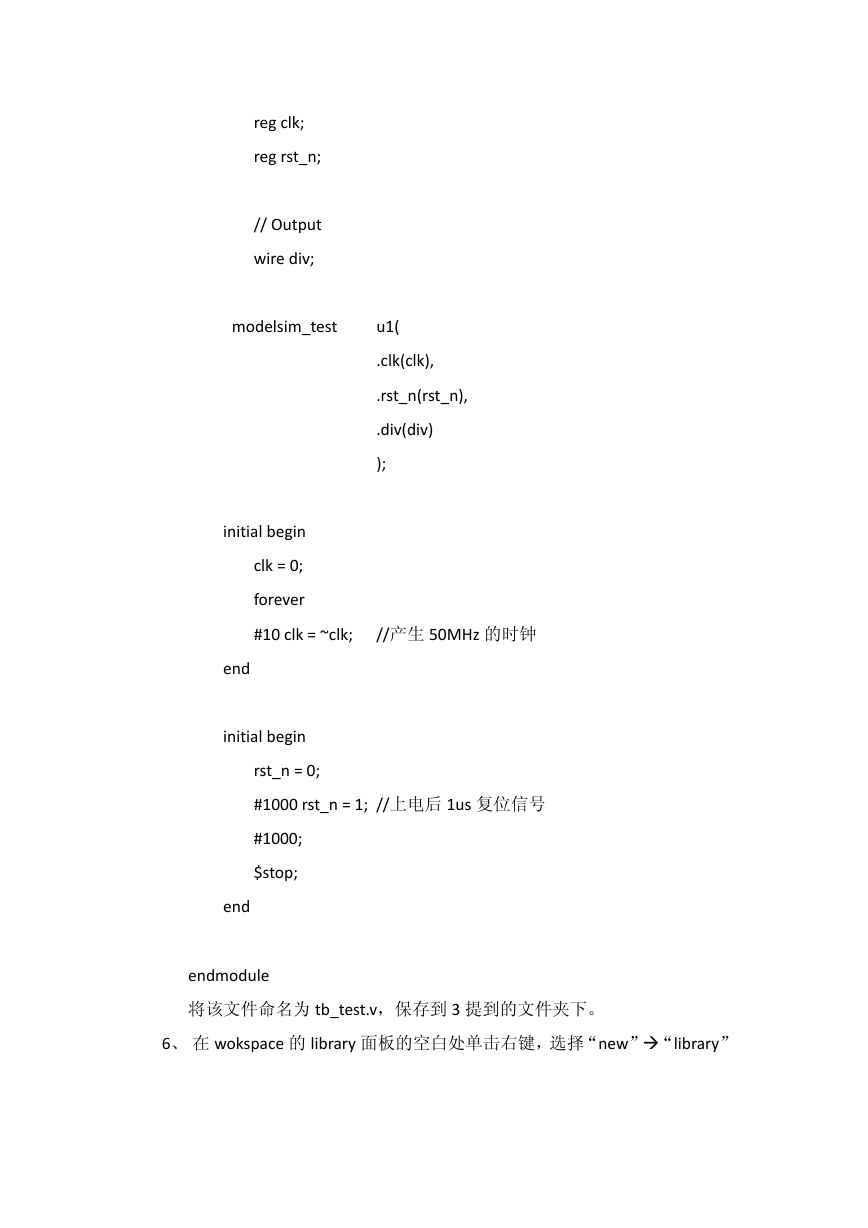

6、 在 wokspace 的 library 面板的空白处单击右键,选择“new”“library”

�

在新弹出界面中做如下设置,然后点击“OK”。

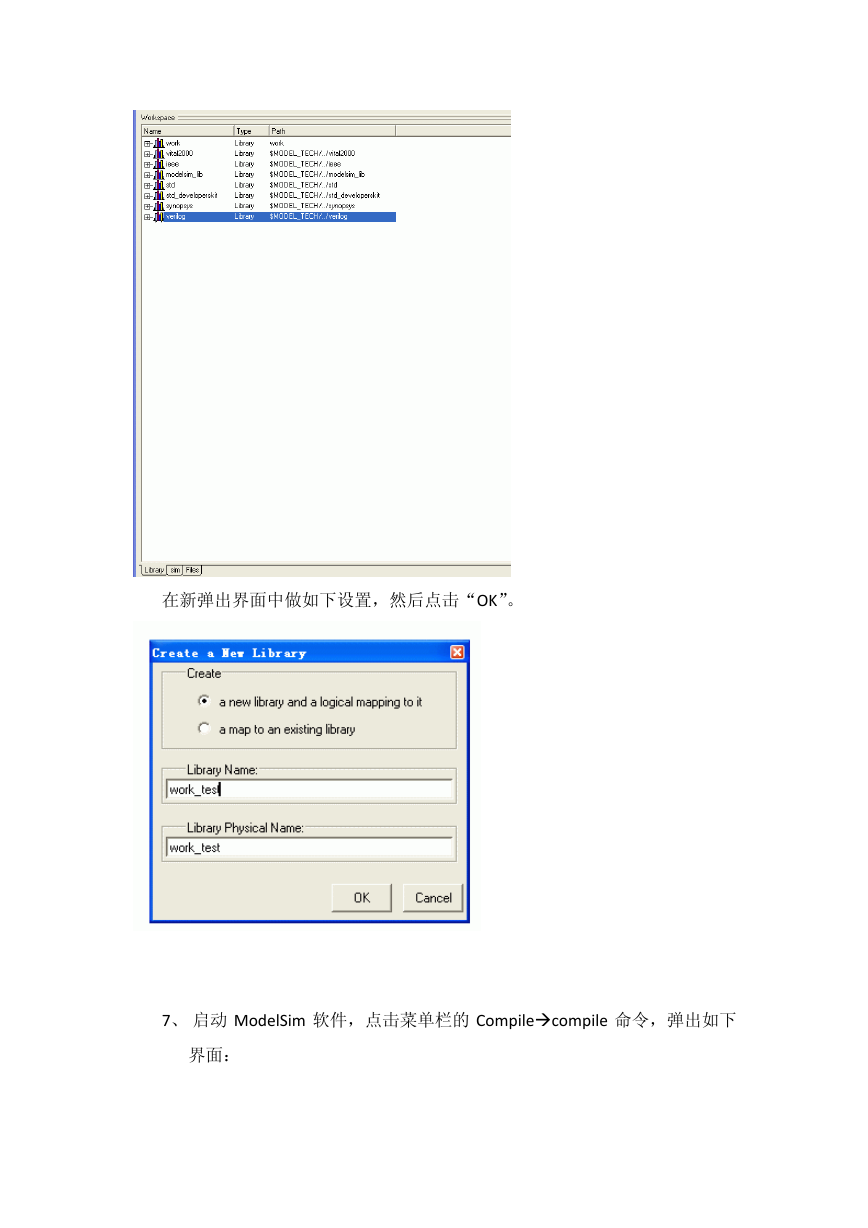

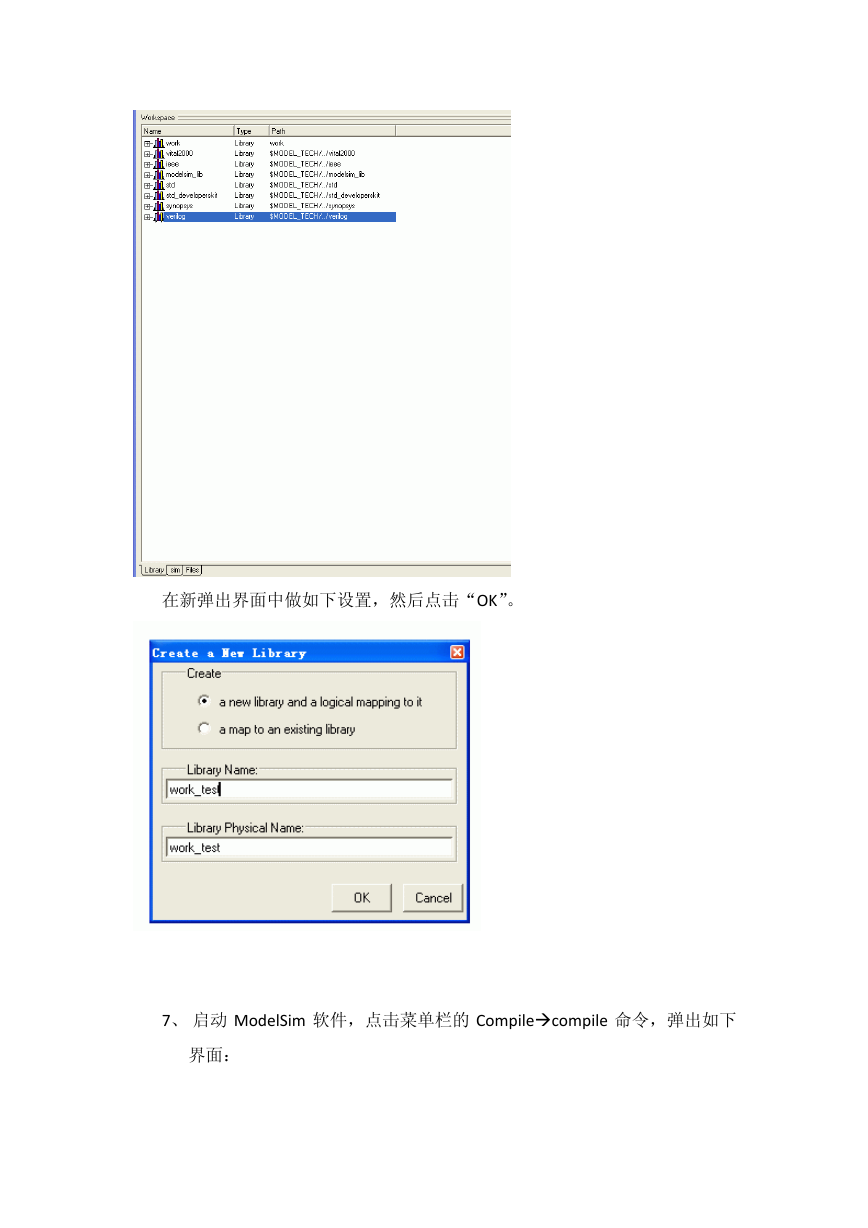

7、 启动 ModelSim 软件,点击菜单栏的 Compilecompile 命令,弹出如下

界面:

�

Library 选择刚才新建的“work_test”,查找范围定位到我们 3 提到的文件

夹下。全选在该目录下可以看到的文件,点击 Compile(注意该文件夹必

须在全英文/数字路径下,否则会出错无法编译)。

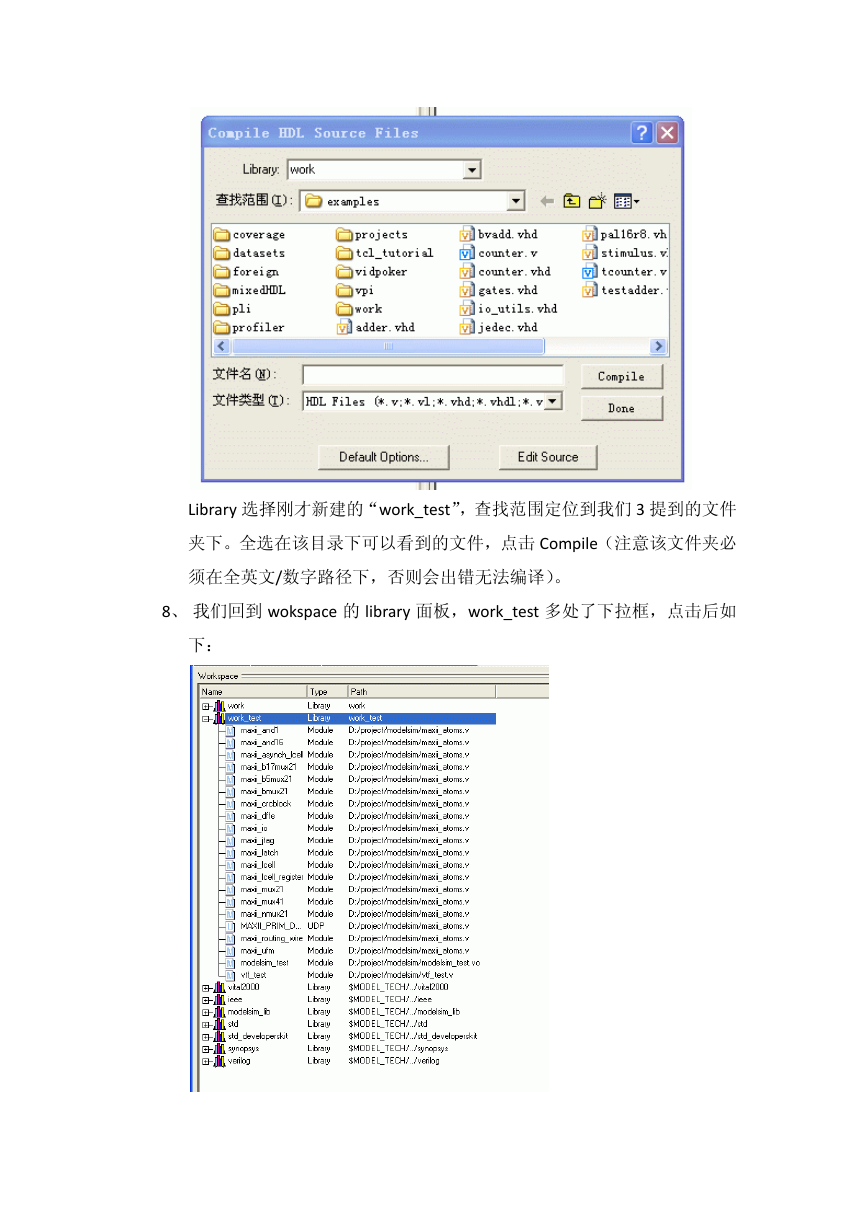

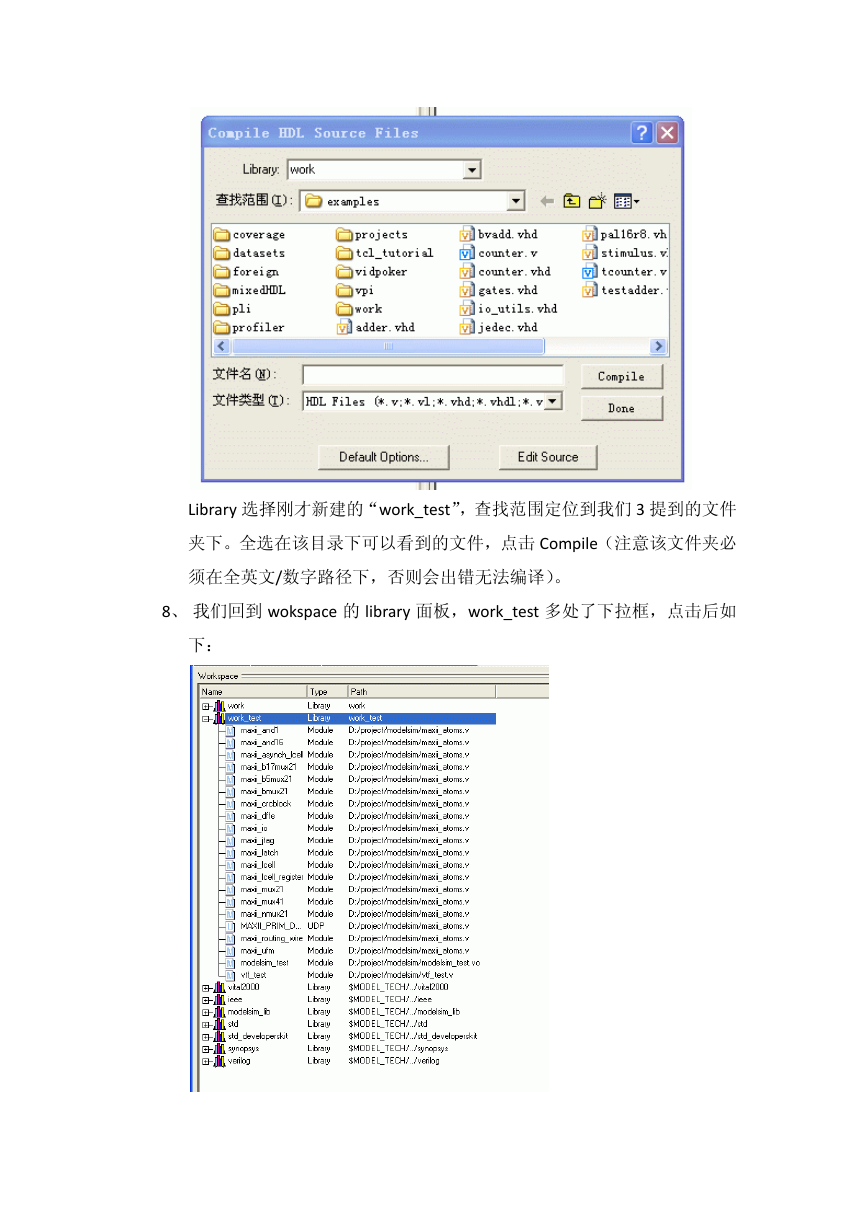

8、 我们回到 wokspace 的 library 面板,work_test 多处了下拉框,点击后如

下:

�

我们右键单击 vtf_test 文件,在弹出的菜单中选择 Simulation

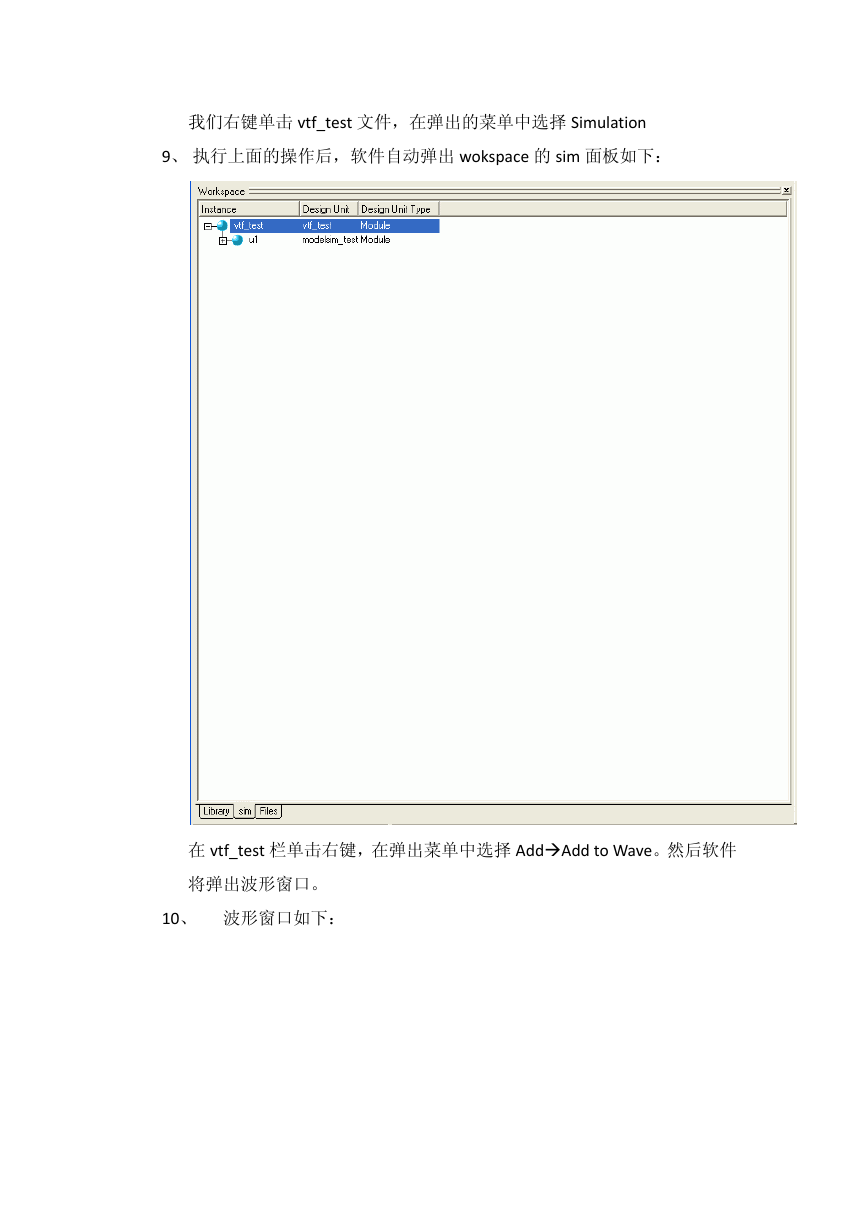

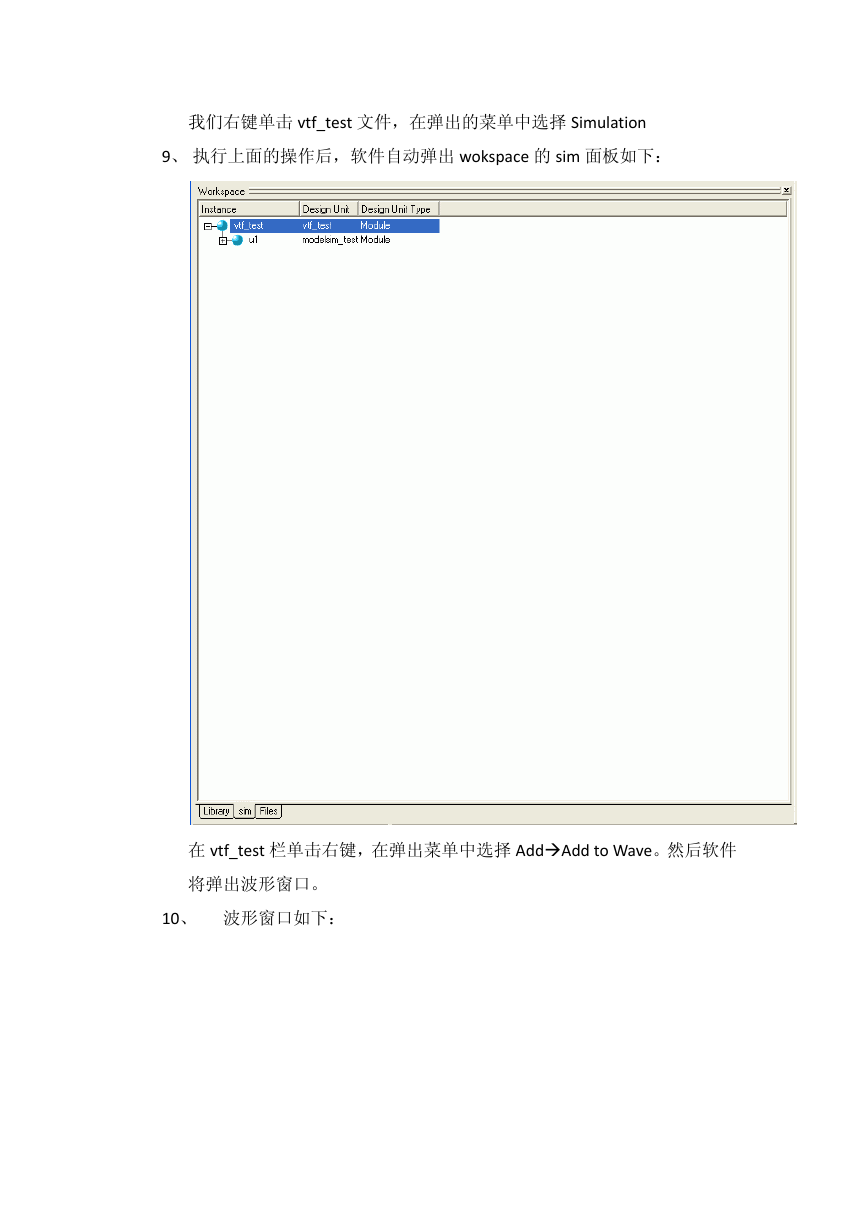

9、 执行上面的操作后,软件自动弹出 wokspace 的 sim 面板如下:

在 vtf_test 栏单击右键,在弹出菜单中选择 AddAdd to Wave。然后软件

将弹出波形窗口。

10、 波形窗口如下:

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc