BCM2711 ARM Peripherals

Colophon

Legal Disclaimer Notice

Table of Contents

Chapter 1. Introduction

1.1. Overview

1.2. Address map

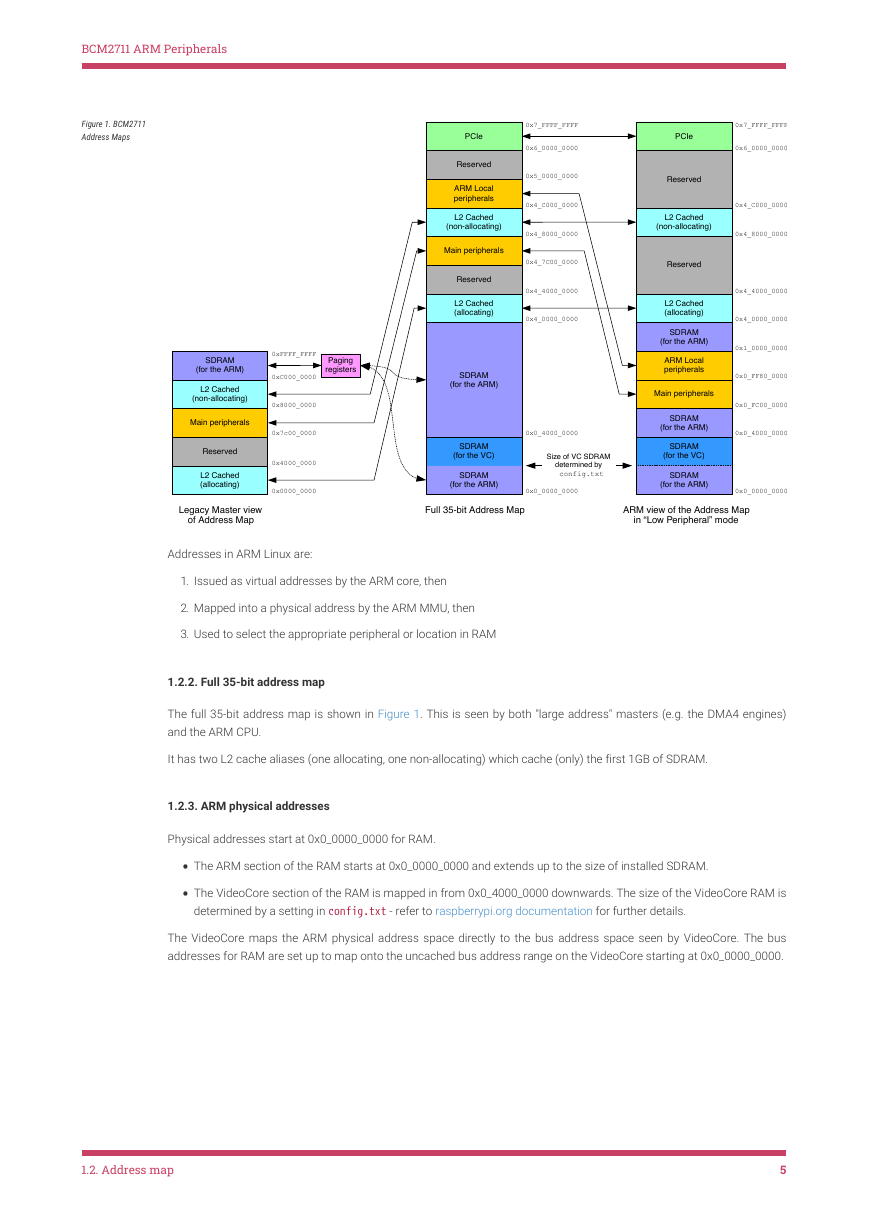

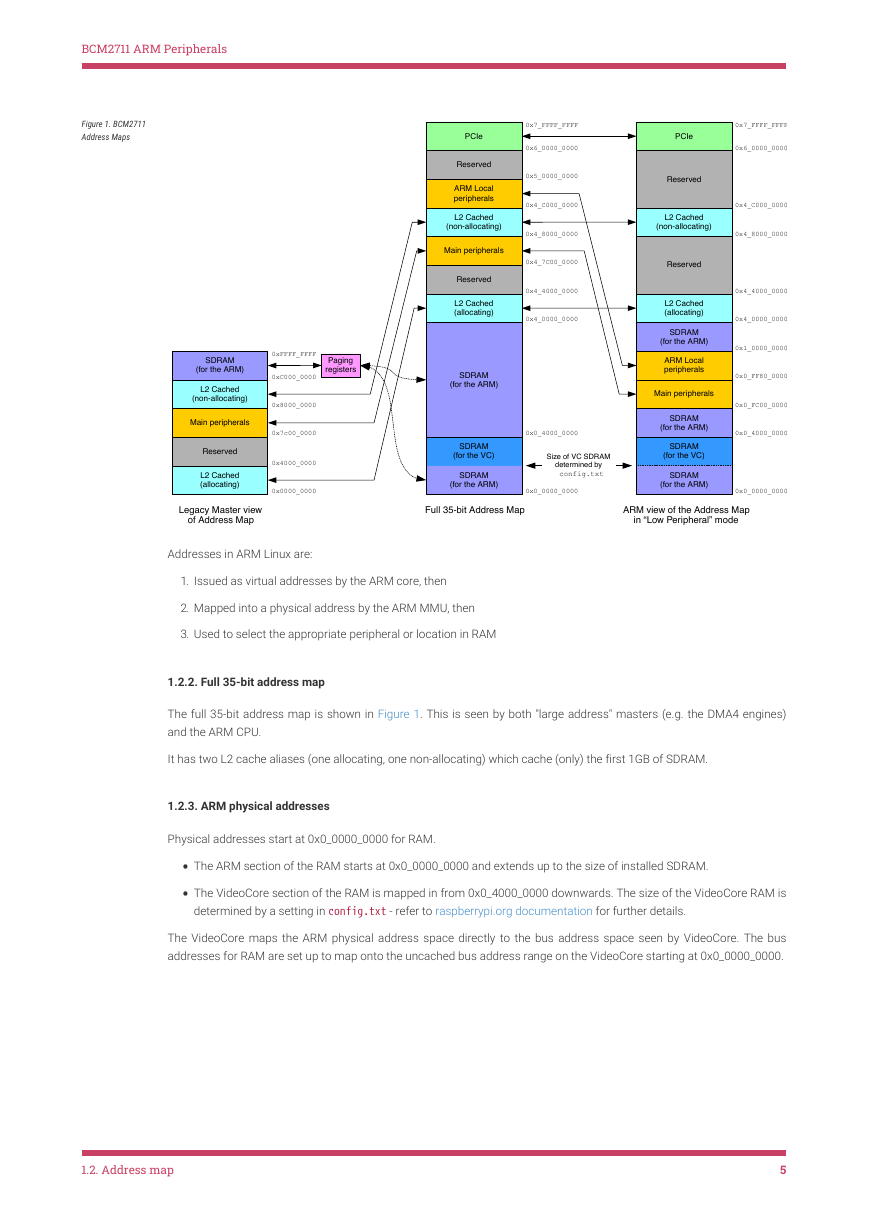

1.2.1. Diagrammatic overview

1.2.2. Full 35-bit address map

1.2.3. ARM physical addresses

1.2.4. Legacy master addresses

1.3. Peripheral access precautions for correct memory ordering

Chapter 2. Auxiliaries: UART1, SPI1 & SPI2

2.1. Overview

2.1.1. AUX registers

2.2. Mini UART

2.2.1. Mini UART implementation details

2.2.2. Mini UART register details

2.3. Universal SPI Master (2x)

2.3.1. SPI implementation details

2.3.2. Interrupts

2.3.3. Long bit streams

2.3.4. SPI register details

Chapter 3. BSC

3.1. Overview

3.2. Register View

3.3. 10-Bit Addressing

3.3.1. Writing

3.3.2. Reading

Chapter 4. DMA Controller

4.1. Overview

4.2. DMA Controller Registers

4.2.1. DMA Channel Register Address Map

4.2.1.1. Control Block Data Structure

4.2.1.2. Register Map

4.2.1.3. Peripheral DREQ Signals

4.3. AXI Bursts

4.4. Error Handling

4.5. DMA LITE Engines

4.6. DMA4 Engines

Chapter 5. General Purpose I/O (GPIO)

5.1. Overview

5.2. Register View

5.3. Alternative Function Assignments

5.4. General Purpose GPIO Clocks

5.4.1. Operating Frequency

5.4.2. Register Definitions

Chapter 6. Interrupts

6.1. Overview

6.2. Interrupt sources

6.2.1. ARM Core n interrupts

6.2.2. ARM_LOCAL interrupts

6.2.3. ARMC interrupts

6.2.4. VideoCore interrupts

6.2.5. ETH_PCIe interrupts

6.3. GIC-400 interrupt controller

6.4. Legacy interrupt controller

6.5. Registers

6.5.1. GIC-400

6.5.2. ARM_LOCAL

6.5.3. ARMC

Chapter 7. PCM / I2S Audio

7.1. Overview

7.2. Block Diagram

7.3. Typical Timing

7.4. Operation

7.5. Software Operation

7.5.1. Operating in Polled mode

7.5.2. Operating in Interrupt mode

7.5.3. DMA

7.6. Error Handling

7.7. PDM Input Mode Operation

7.8. GRAY Code Input Mode Operation

7.9. PCM Register Map

Chapter 8. Pulse Width Modulator

8.1. Overview

8.2. Block Diagram

8.3. PWM Implementation

8.4. Modes of Operation

8.5. Quick Reference

8.6. Control and Status Registers

Chapter 9. SPI

9.1. Overview

9.2. SPI Master Mode

9.2.1. Standard mode

9.2.2. Bidirectional mode

9.3. LoSSI mode

9.3.1. Command write

9.3.2. Parameter write

9.3.3. Byte read commands

9.3.4. 24-bit read command

9.3.5. 32-bit read command

9.4. Block Diagram

9.5. SPI Register Map

9.6. Software Operation

9.6.1. Polled

9.6.2. Interrupt

9.6.3. DMA

9.6.4. Notes

Chapter 10. System Timer

10.1. Overview

10.2. System Timer Registers

Chapter 11. UART

11.1. Overview

11.2. Variations from the 16C650 UART

11.3. Primary UART Inputs and Outputs

11.4. UART Interrupts

11.5. Register View

Chapter 12. Timer (ARM side)

12.1. Overview

12.2. Timer Registers

Chapter 13. ARM Mailboxes

13.1. Overview

13.2. Registers

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc