毕业设计说明书

基于 VHDL 语言的 8 位 RISC-CPU 的设计

学

专

院:

业:

学生姓名:

学

号:

指导教师:

201 年 月

�

中 文 摘 要

摘 要

RISC 即精简指令集计算机(Reduced Instruction Set Computer)的缩写。

RISC-CPU 与一般的 CPU 相比,通过简化指令系统使计算机的结构更加简单合

理,从而提高了运算速度。本文对 RISC-CPU 的架构进行了分析,并使用 VHDL

语言设计了 8 位 RISC-CPU IP 软核。

RISC-CPU 由八大基本模块构成:时钟发生器、指令寄存器、累加器、算术

逻辑单元、数据输出控制器、地址多路器、程序计数器、状态控制器。本设计中

借助 MAX+PLUSⅡ软件平台对各模块进行时序仿真,并最终给出了指令执行的

仿真波形,验证了 CPU 的功能。

设计仿真结果表明,该 8 位 RISC-CPU 能够完成既定的任务指标,而且在运

行效率上有一定程度改善。

关键词:RISC-CPU、VHDL、MAX+PLUSⅡ、IP 软核、时序仿真

I

�

Abstract

Abstract

RISC reduced instruction set computer that (Reduced Instruction Set Computer)

acronym. RISC-CPU and CPU in general compared to instruction by simplifying the

structure of

thereby increasing

processing speed. In this paper, RISC-CPU architecture is analyzed, and by using the

VHDL language, I designed an 8-bit RISC-CPU IP soft core.

is more simple and reasonable,

the computer

RISC-CPU is based on 8 modules: clock generator,

instruction register,

accumulator, arithmetic logic unit, data output controller, address multiplexer,

program counter, state controller. In the design, each module are timing simulated on

MAX+PLUSⅡ software platform, and finally the simulated waveform of instruction

execution that verifies the CPU features is given.

Design and simulation results show that the 8-bit RISC-CPU can complete the

tasks, and also has a certain degree of improvement on operational efficiency.

Keywords: RISC-CPU, VHDL, MAX+PLUSⅡ, IP soft core, Timing Simulation

II

�

目 录

目 录

摘 要..................................................................................................................................................I

ABSTRACT(英文摘要)........................................................................................................II

目 录...............................................................................................................................................III

第一章 引言...................................................................................................................................1

1.1 课题背景与发展现状.......................................................................................................1

1.1.1 课题背景.......................................................................................................................1

1.1.2 RISC-CPU 的发展现状.............................................................................................1

1.2 RISC-CPU 优势与现实意义...........................................................................................1

1.2.1 RISC-CPU 具备的优势.............................................................................................1

1.2.2 本课题的现实意义.................................................................................................... 2

1.3 本设计的主要内容............................................................................................................2

第二章 RISC-CPU 的架构设计...............................................................................................3

2.1 RISC-CPU 基本架构.........................................................................................................3

2.2 RISC-CPU 模块的划分.................................................................................................... 4

第三章 八位 RISC-CPU 各模块设计与仿真.......................................................................6

3.1 时钟发生器..........................................................................................................................6

3.2 指令寄存器..........................................................................................................................7

3.3 累加器................................................................................................................................ 10

3.4 算术逻辑单元...................................................................................................................11

3.5 数据输出控制器..............................................................................................................13

3.6 地址多路器....................................................................................................................... 14

3.7 程序计数器....................................................................................................................... 15

3.8 状态控制器....................................................................................................................... 17

第四章 RISC-CPU 的综合及操作时序...............................................................................25

4.1 RISC-CPU 各模块综合..................................................................................................25

4.2 CPU 复位启动操作时序................................................................................................29

结论.................................................................................................................................................30

III

�

目 录

参考文献....................................................................................................................................... 31

致谢.................................................................................................................................................32

IV

�

第 一 章 引 言

第一章 引 言

1.1 题背景与发展现状

1.1.1 课题背景

CPU 是 Central Processing Unit——中央处理器的缩写,它是计算机中最重要

的一个部分。CPU 由运算器和控制器组成,其内部结构归纳起来可以分为控制

单元、逻辑单元和存储单元三大部分,这三个部分相互协调,便可以进行分析,

判断、运算并控制计算机各部分协调工作。CPU 从最初发展至今已经有几十年

的历史了,这期间,按照其处理信息的字长,CPU 可以分为:四位微处理器、

八位微处理器、十六位微处理器、三十二位微处理器以及六十四位微处理器。而

RISC 处理器的出现标志着计算机体系结构中的一个根本性变革。

RISC 即精简指令集计算机(Reduced Instruction Set Computer)的缩写。从实现

的途径看,RISC-CPU 与一般的 CPU 的不同处在于:它的时序控制信号形成部

件是用硬布线逻辑实现的而不是采用微程序控制的方式。所谓硬布线逻辑也就是

用触发器和逻辑门直接连线所构成的状态机和组合逻辑,故产生控制序列的速度

比用微程序控制方式快得多,因为这样做省去了读取微指令的时间。

1.1.2 RISC-CPU的发展现状

IBM 公司在 1975 年成功开发出第一款 RISC 处理器,从此 RISC 架构开始走

进超级计算机中。由于指令高度简约,RISC 处理器的晶体管规模普遍都很小而

性能强大,深受超级计算机厂商所青睐。很快,许多厂商都开发出了自己的 RISC

指令系统,除了 IBM 的 Power 和 PowerPC 外,还有 DEC 的 Alpha、SUN 的 SPARC、

HP 的 PA-RISC、MIPS 技术公司的 MIPS、ARM 公司的 ARM 等。它的应用范围

也远比 X86 来得广泛,大到各种超级计算机、工作站、高阶服务器,小到各类

嵌入式设备、家用游戏机、消费电子产品、工业控制计算机,都可以看到 RISC

的身影。

1.2 RISC-CPU 优势与现实意义

1.2.1 RISC-CPU具备的优势

RISC 有一套优化过的指令架构,它是根据著名的 80/20 法则所订立。早在

上个世纪 60 年代,计算机科学家们发现,计算机中 80%的任务只是动用了大约

20%的指令,而剩下 20%的任务才有机会使用到其他 80%的指令。如果对指令系

统作相应的优化,就可以从根本上快速提高处理器的执行效率。

- 1 -

�

第 一 章 引 言

RISC 与 CISC(一般指普通的 X86CPU)比较,有以下优势:

指令简单而且少;指令系统选用那些使用频度高的简单指令和一些实用的但

不十分复杂的指令,一般指令不超过 100 条;指令字长固定,寻址方式一般不超

过四种,指令格式也不超过四种;所有指令(几乎所有指令)均在单指令周期完成;

指令系统中只允许存(STORE)和取(LOAD)指令访问主存,其它指令均在寄存器

之间进行;CPU 中设置大量的寄存器,称作寄存器堆;指令的运行采用高效的

流水线方式;以硬布线控制逻辑为主,不用或少用微码;优化的编译程序,简单

有效地支持高级语言;超低功耗。

1.2.2 本课题的现实意义

本课题的设计具有重要的意义:

(1) 从 IP 设计技术层面看,本课题按照自顶向下(Top-Down)的设计方法,从

系统级结构和模块划分到硬件描述、综合、仿真灯,研究了 Altera 公司的

MAX+plusII 工具的使用,掌握了 IP 正向设计的基本方法,积累了宝贵经验。

(2) 从 RISC-CPU 设计技术层面看,通过本课题的设计过程,了解掌握了

MIPS 指令系统 CPU 体系结构设计的关键技术。

(3) 从嵌入式系统设计技术层面看,集成电路发展已进入 IP core 复用的 SoC

时代,8 位嵌入式微处理器发展的一个重要特点是片上系统 SoC 化。本课题也为

基于 IP 核的嵌入式系统设计积累了宝贵经验。

(4) 从市场应用层面看,8 位 RISC-CPU 是目前市场上同类产品占市场份额

最大的一块,符合我国集成电路当前的设计水平,以它作为参与市场竞争的突破

口,来提高企业的市场竞争能力和技术创新能力,是一个切实可行的方案。

1.3 本设计的主要内容

本文对 RISC-CPU 的架构进行了探讨,介绍了如何设计 RISC-CPU,并且立

足于八位的 RISC-CPU 设计实例,应用硬件描述语言 VHDL 语言实现 8 位简化

RISC-CPU IP 软核的设计,通过对 RISC-CPU 结构和指令执行的分析将整个系统

划分为各个功能模块,并阐明各模块间的接口信号,给出了每个模块内部设计实

现的详细叙述,最后介绍对设计的综合和验证工作,给出了仿真验证数据以及时

序图。设计需要实现的这个简化的 8 位 RISC-CPU 采用 MIPS 的部分指令集,同

时对 MIPS CPU 的结构进行一定的修改。

- 2 -

�

第 二 章 RISC-CPU的架构设计

第二章 RISC-CPU的架构设计

2.1 RISC-CPU 基本架构

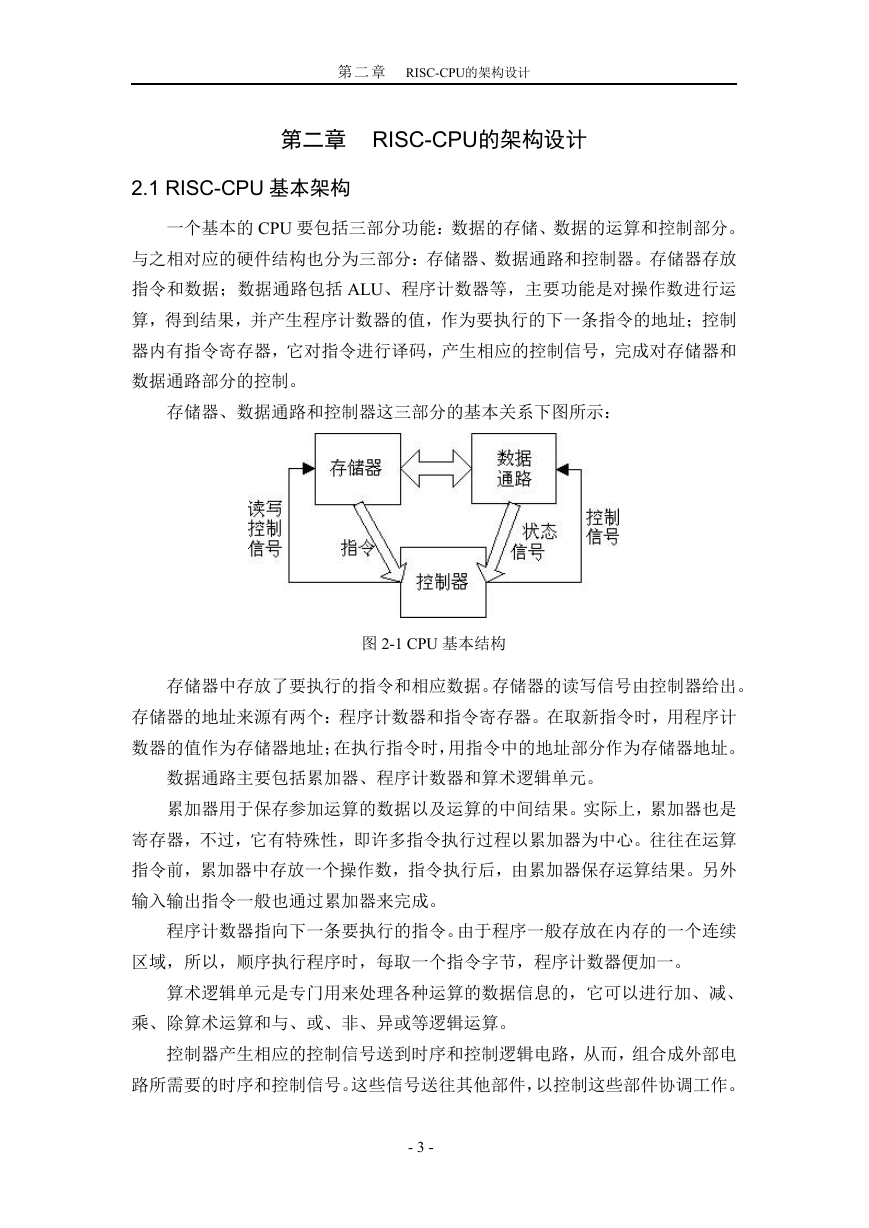

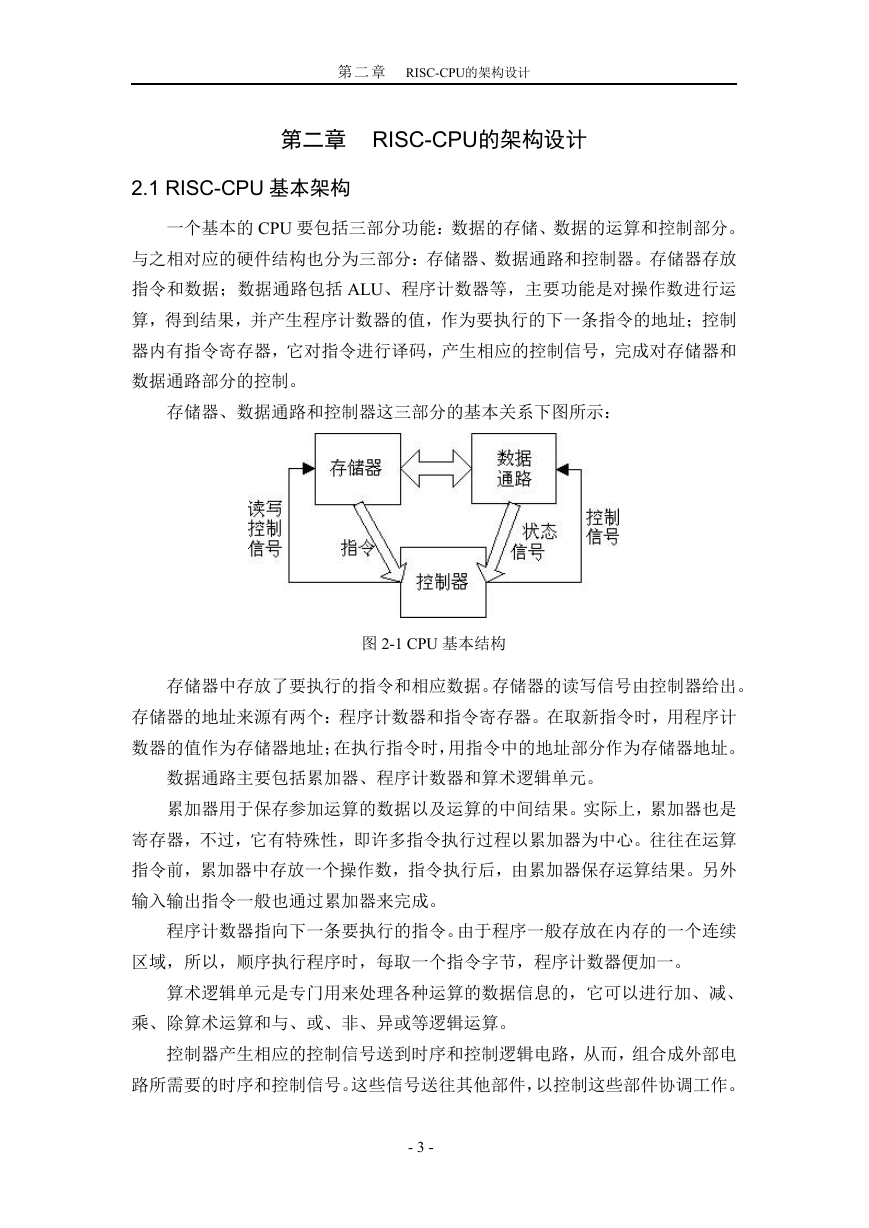

一个基本的 CPU 要包括三部分功能:数据的存储、数据的运算和控制部分。

与之相对应的硬件结构也分为三部分:存储器、数据通路和控制器。存储器存放

指令和数据;数据通路包括 ALU、程序计数器等,主要功能是对操作数进行运

算,得到结果,并产生程序计数器的值,作为要执行的下一条指令的地址;控制

器内有指令寄存器,它对指令进行译码,产生相应的控制信号,完成对存储器和

数据通路部分的控制。

存储器、数据通路和控制器这三部分的基本关系下图所示:

图 2-1 CPU 基本结构

存储器中存放了要执行的指令和相应数据。存储器的读写信号由控制器给出。

存储器的地址来源有两个:程序计数器和指令寄存器。在取新指令时,用程序计

数器的值作为存储器地址;在执行指令时,用指令中的地址部分作为存储器地址。

数据通路主要包括累加器、程序计数器和算术逻辑单元。

累加器用于保存参加运算的数据以及运算的中间结果。实际上,累加器也是

寄存器,不过,它有特殊性,即许多指令执行过程以累加器为中心。往往在运算

指令前,累加器中存放一个操作数,指令执行后,由累加器保存运算结果。另外

输入输出指令一般也通过累加器来完成。

程序计数器指向下一条要执行的指令。由于程序一般存放在内存的一个连续

区域,所以,顺序执行程序时,每取一个指令字节,程序计数器便加一。

算术逻辑单元是专门用来处理各种运算的数据信息的,它可以进行加、减、

乘、除算术运算和与、或、非、异或等逻辑运算。

控制器产生相应的控制信号送到时序和控制逻辑电路,从而,组合成外部电

路所需要的时序和控制信号。这些信号送往其他部件,以控制这些部件协调工作。

- 3 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc