ARM 体系结构课程设计

题目:基于 ARM 处理器的温度控制系统

学院:

专业:

班级:

学号:2

姓名:

�

ARM 平台的智能温控系统设计

ARM9 嵌入式微控制器 AT91RM920T 和 Linux 操作系统相结合的嵌入式温度控制系统,

温度控制系统的硬件系统,主要包含 CPU 模块、模拟电路模块、存储模块和通信模块四个

部分:在对温度控制系统的软件部分的设计中,主要是针对 Boot-Loader 的移植、Linux 内核

移植、根文件系统的定制、驱动程序的编写和应用程序的编写五部分进行设计。

1.温度控制系统总体方案设计

1.1 系统概述

该温度系统主要由模拟电路、主控制电路,数据存储模块、输入输出模块、通讯模块等组成。

主控制电路由 ARM 及其外围电路组成,是温度控制系统的核心部分,完成整个系统的控制,

数据传输与存储和信号的处理等工作处理器对模拟电路采集进来的模拟量进行 A/D 转换得

到实时温度数据,由控制算法对数据进行处理,得到的数字控制量进行 D/A 转换后通过输出

电路对温度进行控制。处理器在数据处理过程中会将历史数据存入 NandFlash 中,并可通过

网络介质与其他 PC 机通讯进行数据的传输。

1.2 系统的总体架构

1.2.1 硬件系统的设计原则

(1)稳定性和可靠性:工业现场环境比较恶劣,模拟量参数处理的性能直接影响系统的技

术指标,必须从一开始就充分考虑应用现场的各种环境状况,采用抗干扰措施,选择适当的

元器件类型和参数,防止串扰和误差积累。设计要充分考虑硬件电路的简化,使用集成度高

的元器件,提高系统抗干扰恩呢公路,提高稳定性和可靠性。

(2)速度与精度:根据允许误差限值,按一定规则分配各个部件模块锁允许的误差,系统

设计过程中根据分配的允许误差选择位数较高的转换芯片,提高转换精度,选定电路结构。

(3)功耗以及数据存储:Arm9lRM9200 自身具有低功耗的特点,VDDCORE 电流为 30.4mA

,待机模式电流为 3.1mA,并具有低速的时钟操作模式和软件功耗优化能力,非常适合于能

耗敏感的场合。采用低功耗器件和铁普安封装元器件,可有效降低功耗,减小 PCB 面积,

提高电路本身的抗干扰能力。为保证数据的存储空间和安全保证,系统采用了一片 32M 的

NandFlash 作为数据和程序存储区,保证了大容量数据存储的需要。

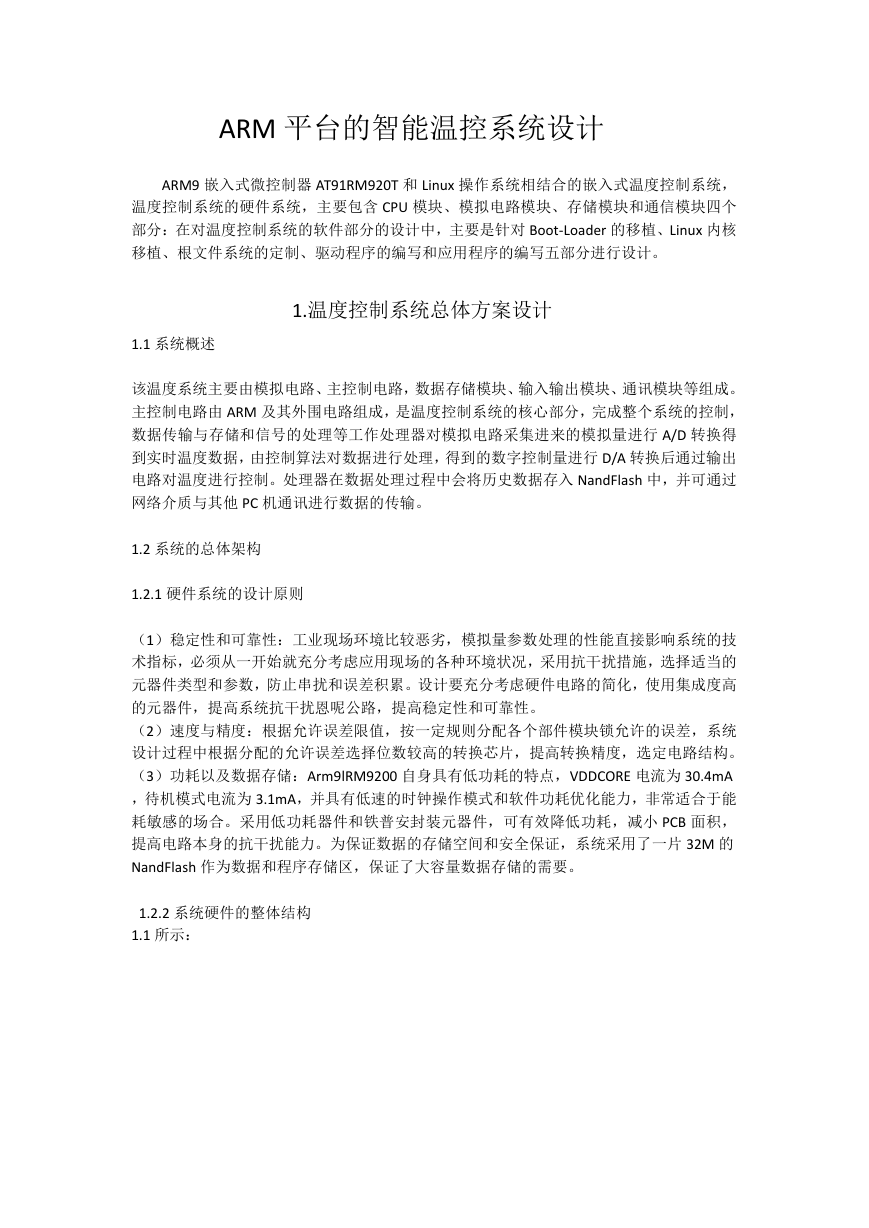

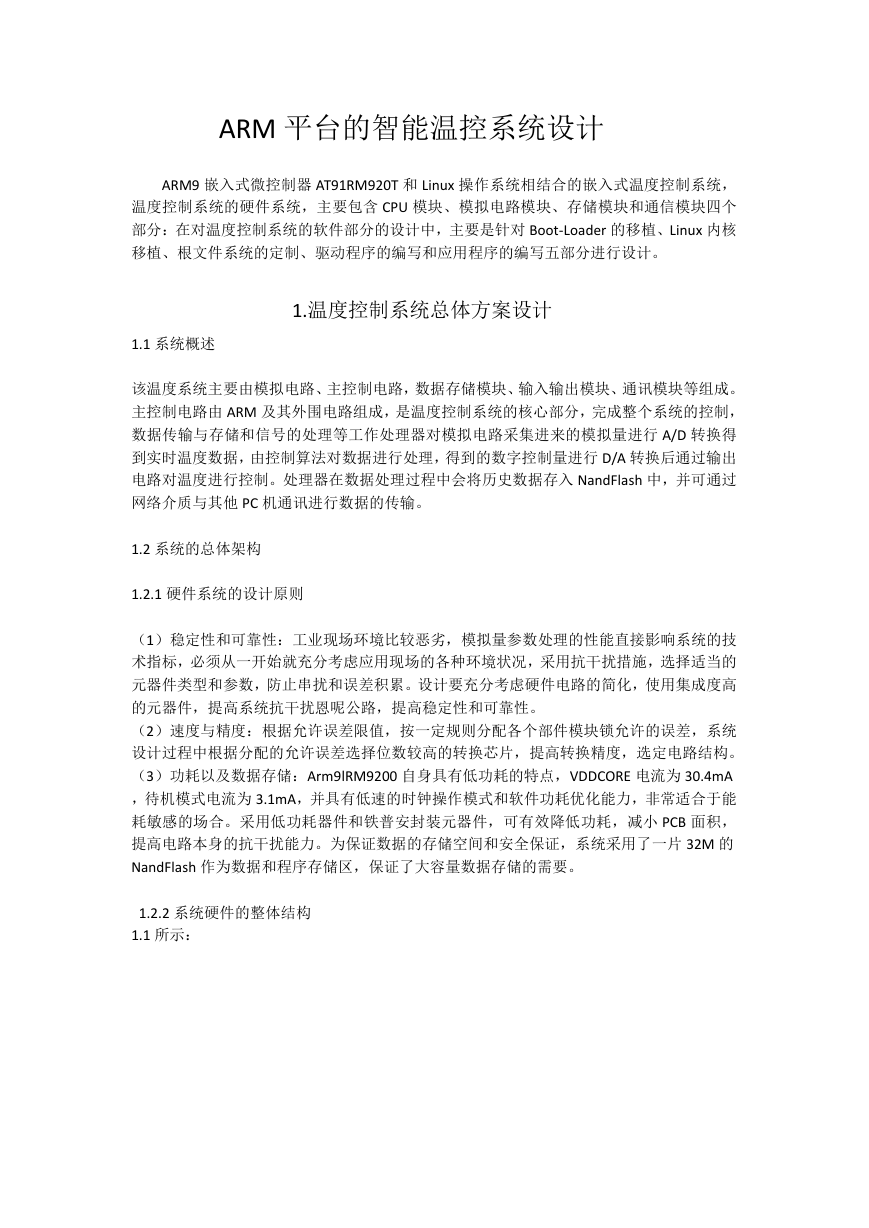

1.2.2 系统硬件的整体结构

1.1 所示:

�

1.1 系统整体框图

(1)CPU 核心模块:主要由 CPU 以及外围电路组成,是系统的主控制电路。CPU 选用 Atme 公

司的基于 920TARM Thumb 处理器 AT9lItM9200,对数据进行处理,存储,通讯等功能

(2)模拟电路:主要包括信号处理电路和信号输出电路。其中信号处理电路主要完成模拟输

入信号的放大和滤波,得到满足模数转换电路输入范围的值,信号输入电路将算法处理后的

数字量转换成相应的模拟信号输入,实现对被控对象的控制。

(3)存储模块:主要由 NorFlash、SDRAM、NandFlash 三部分组成。其中,NorFlash 用来存储

系统启动程序和系统内核:SDRAM 是操作系统和应用程序的运行空间;NandFlash 主要存储

采集的数据以及应用程序。

(4)通讯模块:主要由串行口电路,JTAG 电路,以太网接口电路三部分组成,串行口电路和 JTAG

电路用来下载和调试程序,以太网接口电路用来和其他 PC 机或设备进行通讯,实现数据的

交换。

1.2.3 系统软件的整体结构

ARM 嵌入式软件的开发流程一般是:设计目标硬件板,建立嵌入式 Linux 开发环境,编写、

测试 Boot-Loader,编写、调试 Linux 内核,编写、调试应用程序,调试 ARM 板。

Linux 系统可以分为以下 4 个层次:

(1)引导和加载 Linux 内核程序,主要是编制 Boot.Loader 程序。Boot-Loader 相当于 PC 的 BIOS,

在硬件板一加电后就开始运行,主要完成硬件初始化,同时设置 Linux 启动时所需的参数,

然后跳到 Linux 内核启动代码的第一个字节开始引导 Linux。它要用串行电缆把 PC 与硬件开

发板连接起来,在 PC 端编译程序,生成 bin 文件,然后烧写到 Flash 中。

(2)Linux 内核。主要工作是为特定的嵌入式硬件系统板定制内核以及内核的启动参数,为实

现 Linux 内核的移植,需要把编译生成的 Boot-loader、KernelImage(内核)、Root Filsystem(根

文件系统)烧写到 Flash 中。在编译内核的时候,可以根据需要选择网络协议,例如 TFTP、FTP、

DHJP 等。

�

(3)和 Linux 内核配合使用的根文件系统,包括建立根文件系统和建立于 Flash 设备上的文件

系统

(4)用户应用程序。主要是针对采集的数据类型,进行相应的数据处理,以完成温度控制和

数据通讯的目的。本章从总体上对该系统的组成以及各部分的功能做了简单的介绍,部分的

具体功能和步骤将在后面的几章作详细的阐述。

2.温度控制系统的硬件设计

2.1 AT91RM9200 芯片介绍

AT91RM9200 是完全围绕 ARM920T ARM Thumb 处理器构建的系统。它有丰富的系统与应

用外设以及标准的接口,提供了一种低功耗、低成本、高性能的微控制器解决方案。

2.1.1 ARM9TDMI RISC 整数 ARM920T 处理器概述

高速缓存处理器是 ARM9 Thumb 系列中高性能的 32 位单片系统处理器。

它提供高性能 CPU 子系统:

RM9TDMI RISC 整数 CPU

16-K 字节指令与 16-K 字节数据缓存

指令与数据存储器管理单元(MMUs)

写缓冲器

高级微处理器总线架构(AMBA)总线接口

OETM(内置追踪宏单元)接口

2.1.2 ARM920T 的存储器格式

ARM920T 支持字节(8 位)、半字(16 位)、字(32 位)三种数据类型,其中字需要 4 字节对齐,

半字需要 2 字节对齐。ARM920T 体系结构将存储器看作是从零地址开始的字节的线性组合。

从 O 字节到 3 字节放置第一个存储的字数据,从 4 字节到 7 字节放置第二个存储的字数据,

依次排列,作为 32 位的微处理器,ARM920T 体系结构所支持的最大寻址空间为 4GB(2 字节)。

ARM920T 体系结构可以用两种方法存储字数据,大端格式和小端格式。

2.2 外围电路设计

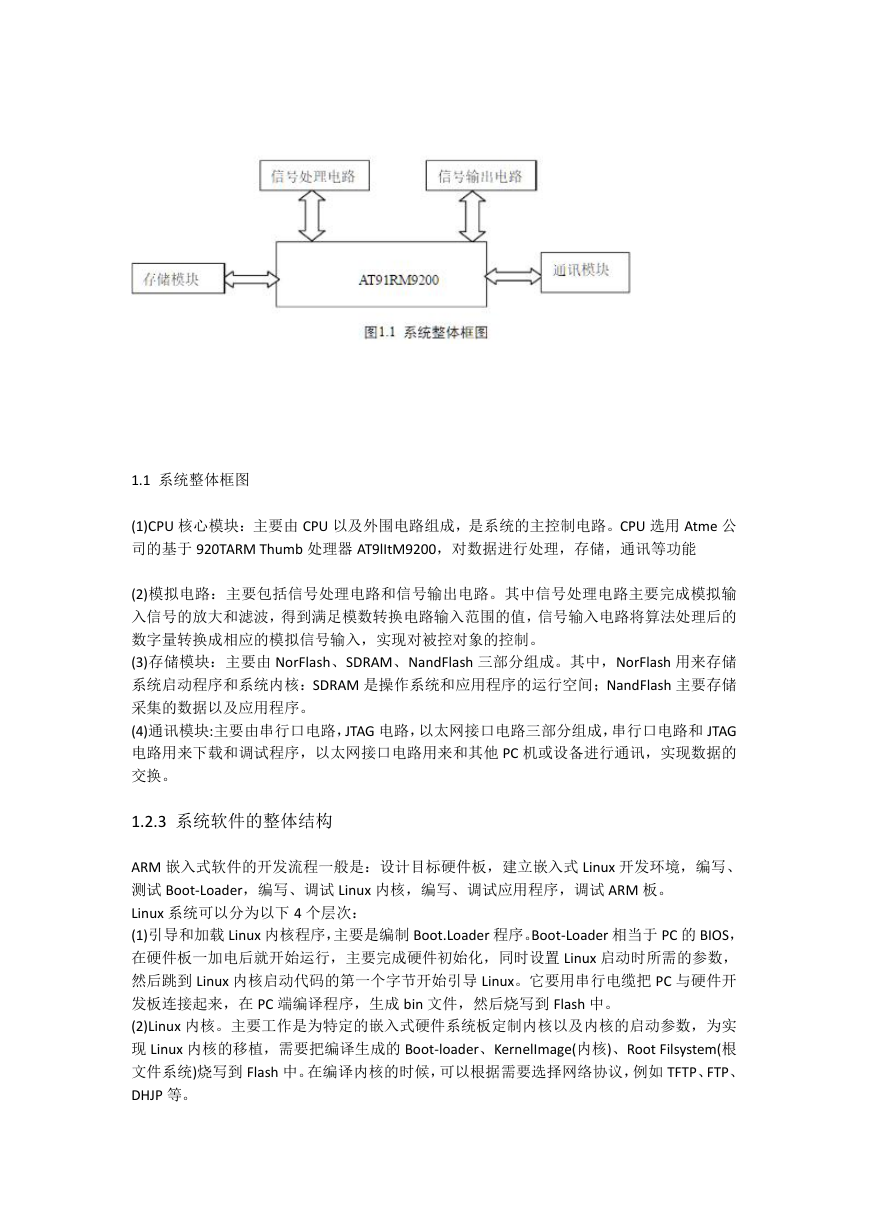

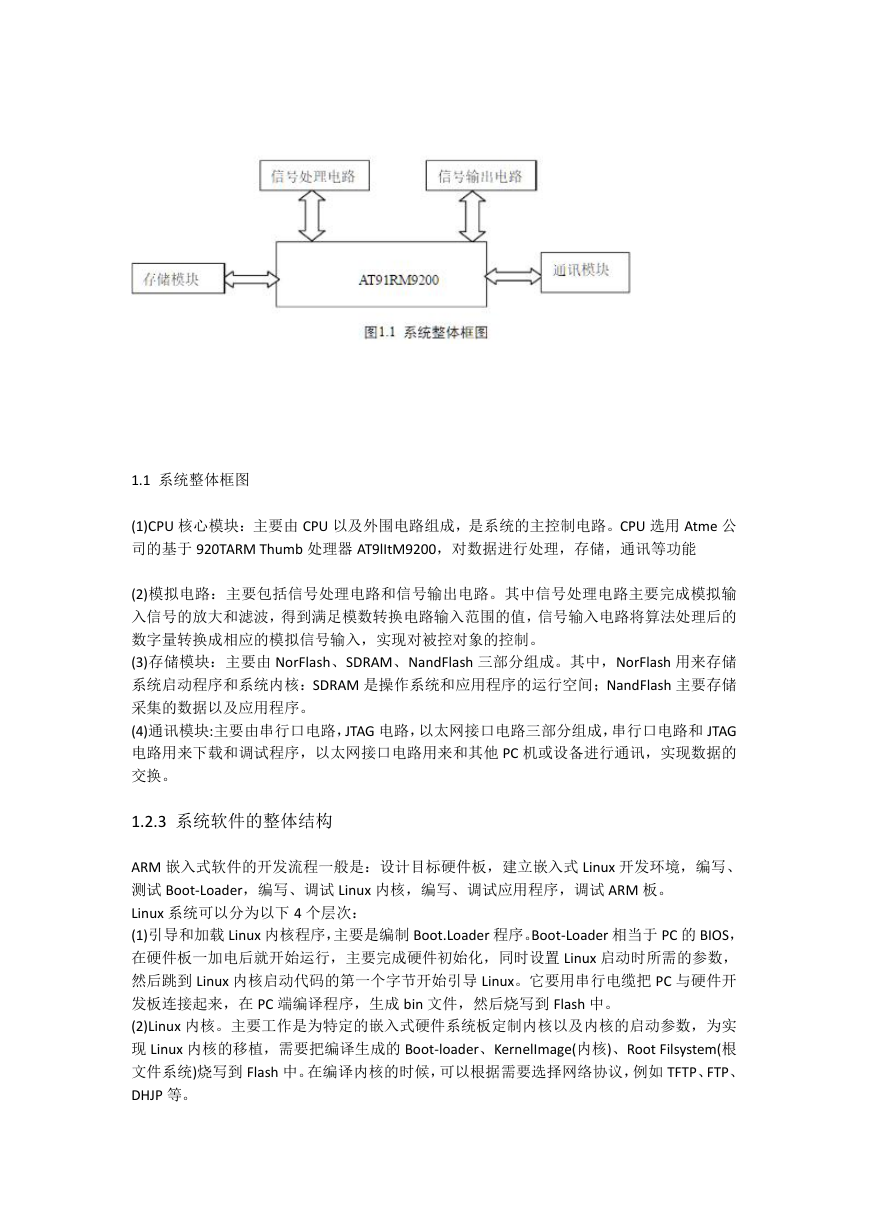

2.2.1 AT91RM9200 相关接口和控制器

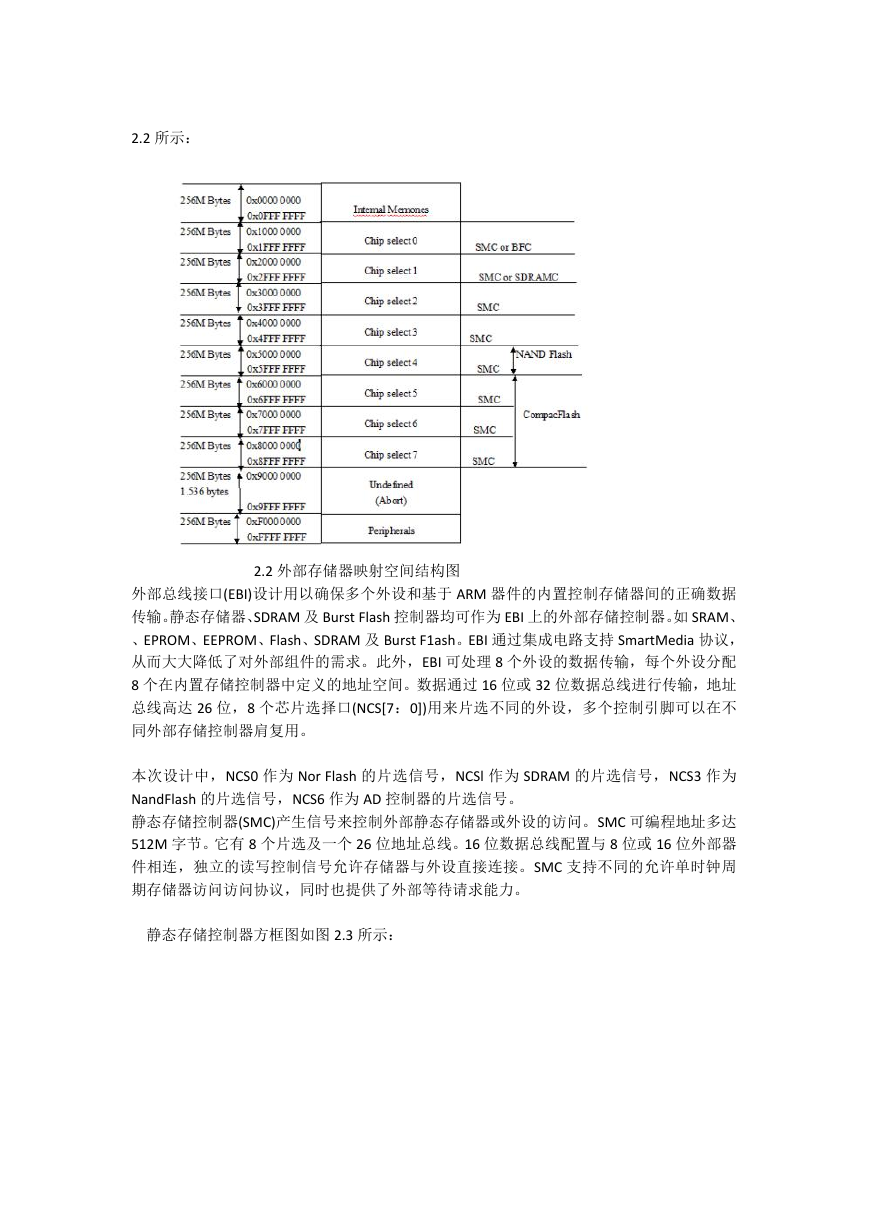

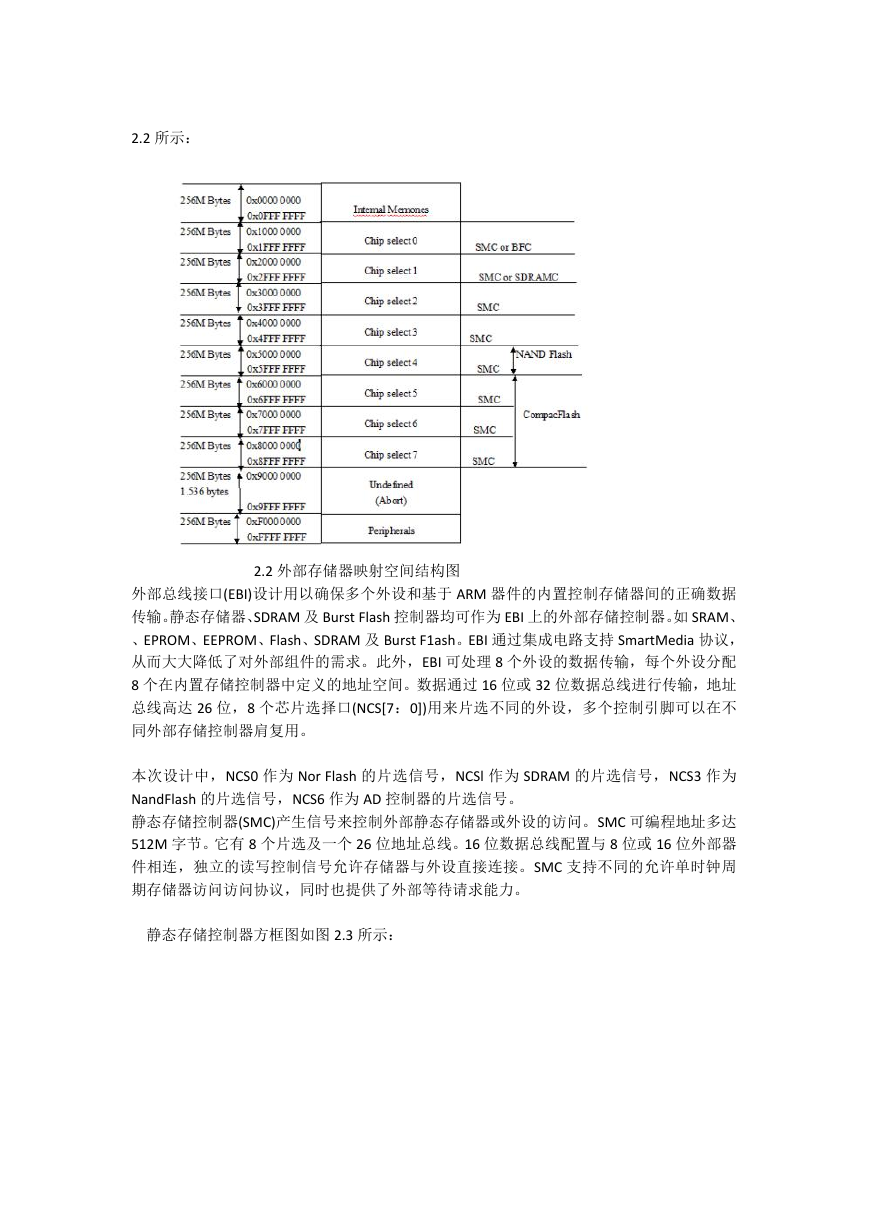

AT91RM9200 的第一级译码由存储控制器执行,即由具有附加功能的高级系统总线执行。译

码将 4G 的地址空间分为 16 个 256MB 的区域。区域 l~8 对应 EBI,和外部片选 NCS0-NCS7

相对应。区域 0 为内部存储器地址,第二级译码提供 1M 字节的内部存储空间。区域 15 为

外设地址,并且提供了对高级外设总线(APB)的访问其他区域未使用,使用他们进行访问时,

需要向发出访问请求的主机发出异常中断。

�

2.2 所示:

2.2 外部存储器映射空间结构图

外部总线接口(EBI)设计用以确保多个外设和基于 ARM 器件的内置控制存储器间的正确数据

传输。静态存储器、SDRAM 及 Burst Flash 控制器均可作为 EBI 上的外部存储控制器。如 SRAM、

、EPROM、EEPROM、Flash、SDRAM 及 Burst F1ash。EBI 通过集成电路支持 SmartMedia 协议,

从而大大降低了对外部组件的需求。此外,EBI 可处理 8 个外设的数据传输,每个外设分配

8 个在内置存储控制器中定义的地址空间。数据通过 16 位或 32 位数据总线进行传输,地址

总线高达 26 位,8 个芯片选择口(NCS[7:0])用来片选不同的外设,多个控制引脚可以在不

同外部存储控制器肩复用。

本次设计中,NCS0 作为 Nor Flash 的片选信号,NCSl 作为 SDRAM 的片选信号,NCS3 作为

NandFlash 的片选信号,NCS6 作为 AD 控制器的片选信号。

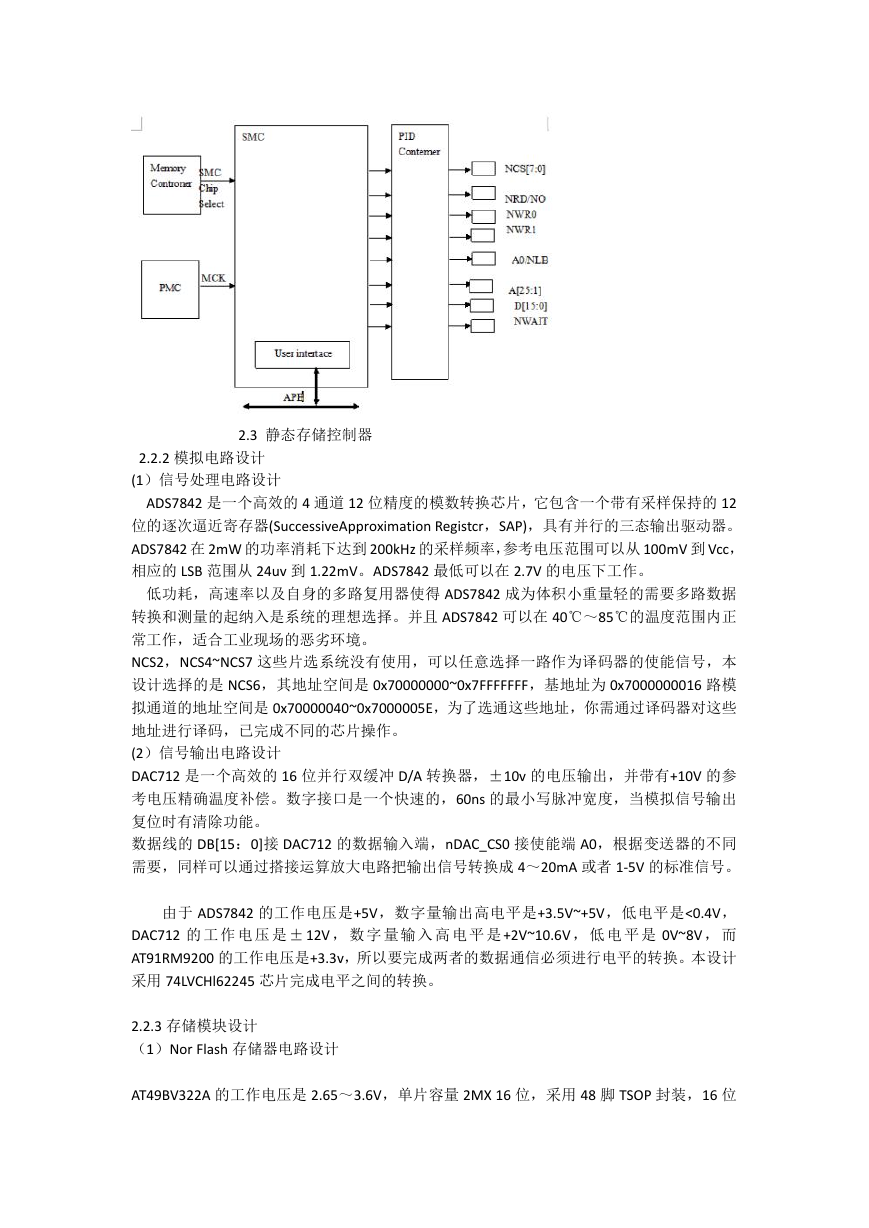

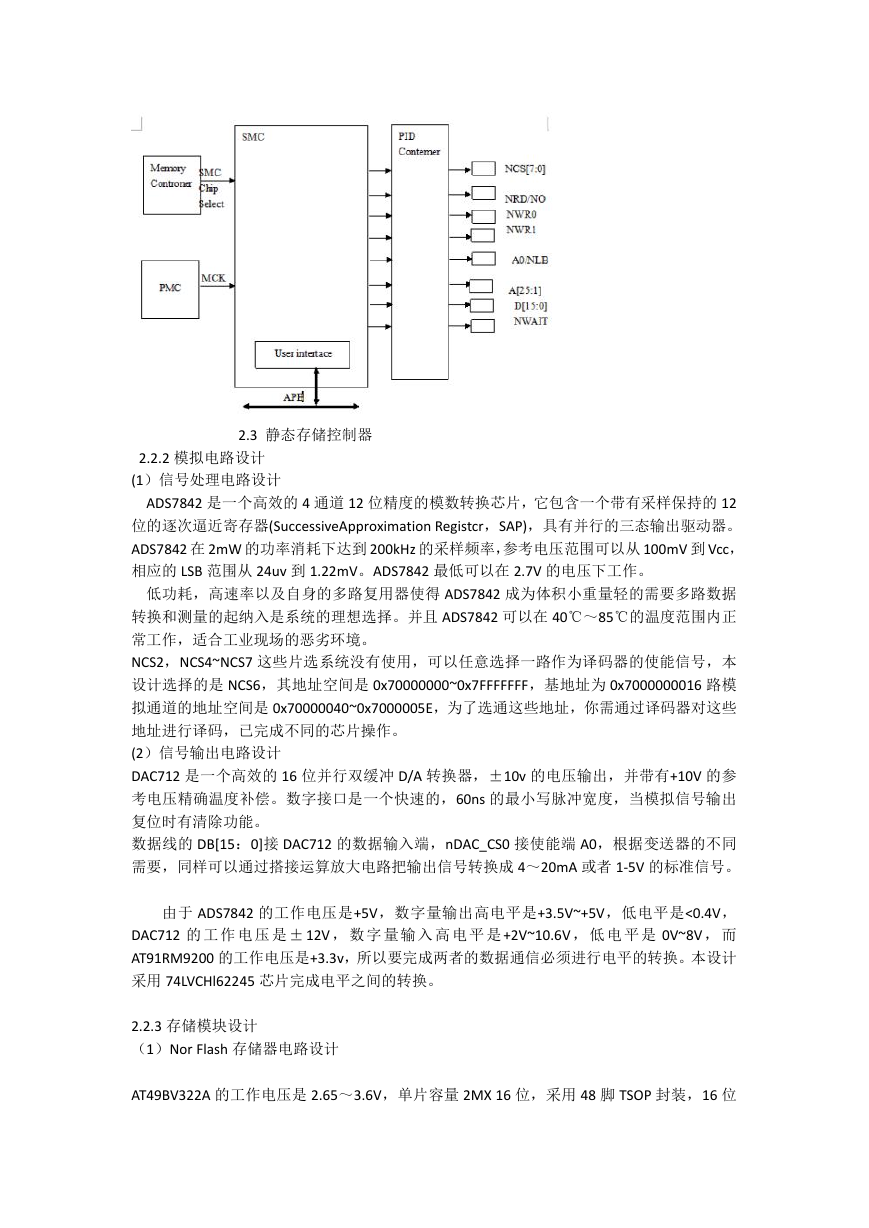

静态存储控制器(SMC)产生信号来控制外部静态存储器或外设的访问。SMC 可编程地址多达

512M 字节。它有 8 个片选及一个 26 位地址总线。16 位数据总线配置与 8 位或 16 位外部器

件相连,独立的读写控制信号允许存储器与外设直接连接。SMC 支持不同的允许单时钟周

期存储器访问访问协议,同时也提供了外部等待请求能力。

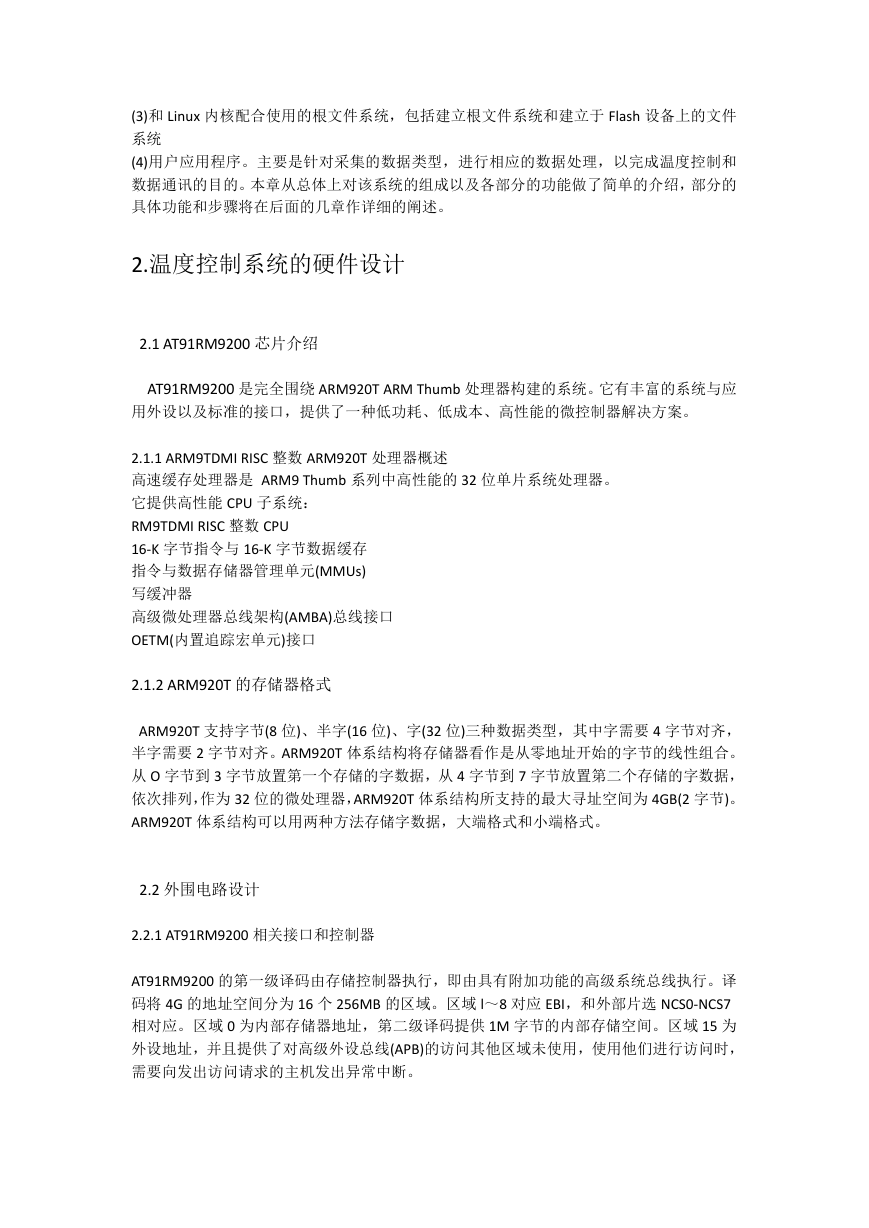

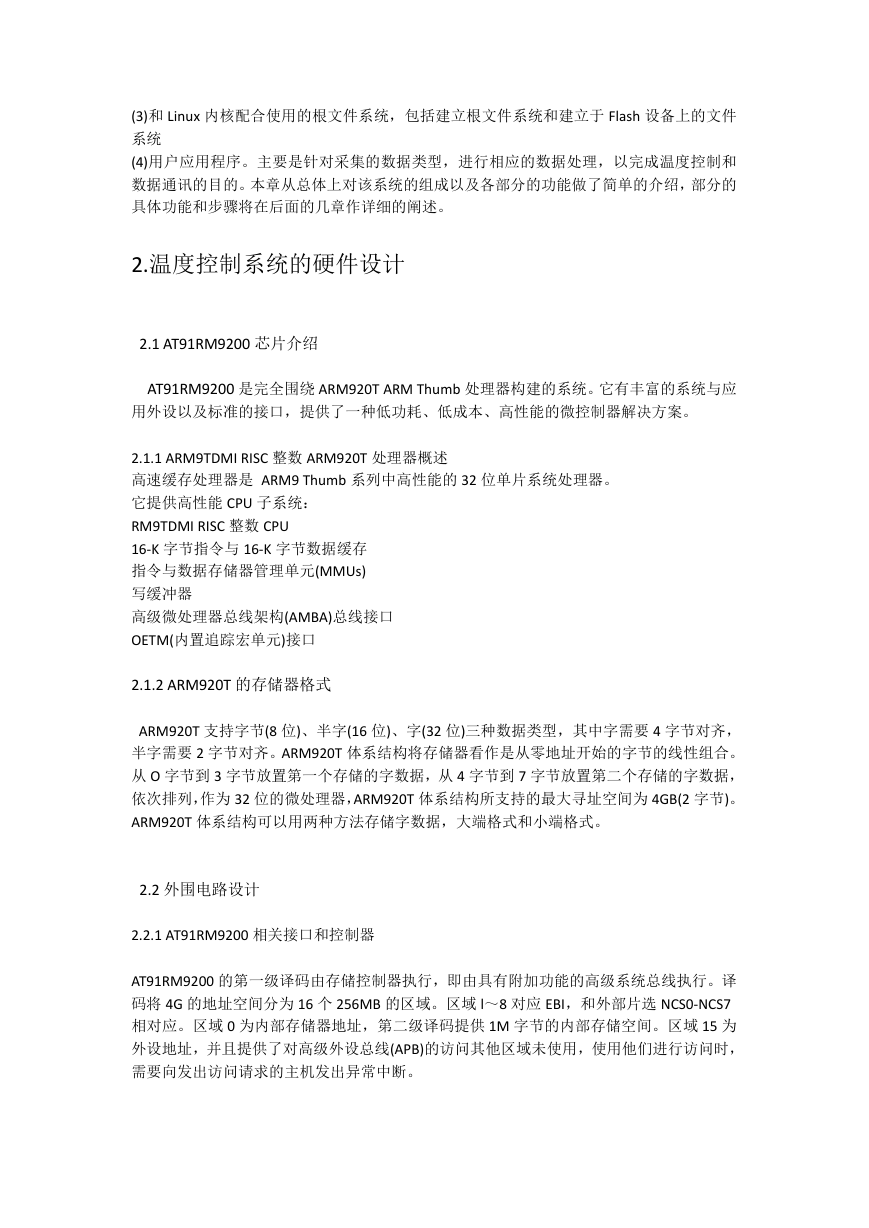

静态存储控制器方框图如图 2.3 所示:

�

2.3 静态存储控制器

2.2.2 模拟电路设计

(1)信号处理电路设计

ADS7842 是一个高效的 4 通道 12 位精度的模数转换芯片,它包含一个带有采样保持的 12

位的逐次逼近寄存器(SuccessiveApproximation Registcr,SAP),具有并行的三态输出驱动器。

ADS7842 在 2mW 的功率消耗下达到 200kHz 的采样频率,参考电压范围可以从 100mV 到 Vcc,

相应的 LSB 范围从 24uv 到 1.22mV。ADS7842 最低可以在 2.7V 的电压下工作。

低功耗,高速率以及自身的多路复用器使得 ADS7842 成为体积小重量轻的需要多路数据

转换和测量的起纳入是系统的理想选择。并且 ADS7842 可以在 40℃~85℃的温度范围内正

常工作,适合工业现场的恶劣环境。

NCS2,NCS4~NCS7 这些片选系统没有使用,可以任意选择一路作为译码器的使能信号,本

设计选择的是 NCS6,其地址空间是 0x70000000~0x7FFFFFFF,基地址为 0x7000000016 路模

拟通道的地址空间是 0x70000040~0x7000005E,为了选通这些地址,你需通过译码器对这些

地址进行译码,已完成不同的芯片操作。

(2)信号输出电路设计

DAC712 是一个高效的 16 位并行双缓冲 D/A 转换器,±10v 的电压输出,并带有+10V 的参

考电压精确温度补偿。数字接口是一个快速的,60ns 的最小写脉冲宽度,当模拟信号输出

复位时有清除功能。

数据线的 DB[15:0]接 DAC712 的数据输入端,nDAC_CS0 接使能端 A0,根据变送器的不同

需要,同样可以通过搭接运算放大电路把输出信号转换成 4~20mA 或者 1-5V 的标准信号。

由于 ADS7842 的工作电压是+5V,数字量输出高电平是+3.5V~+5V,低电平是<0.4V,

DAC712 的 工 作 电 压 是 ±12V , 数 字 量 输 入 高 电 平 是+2V~10.6V , 低 电 平 是 0V~8V , 而

AT91RM9200 的工作电压是+3.3v,所以要完成两者的数据通信必须进行电平的转换。本设计

采用 74LVCHl62245 芯片完成电平之间的转换。

2.2.3 存储模块设计

(1)Nor Flash 存储器电路设计

AT49BV322A 的工作电压是 2.65~3.6V,单片容量 2MX 16 位,采用 48 脚 TSOP 封装,16 位

�

数据宽度,可以 8 位字节数据宽度工作。Flash 分成 71 个扇区,通过对其内部的命令寄存器

写入标准的命令序列,可对 Flash 完成编程、整片擦除、按扇区擦除以及其他操作。

Flash 中主要存放程序代码、系统内核、常量表等等,选用一片 16 位的 Flash 存储器构建 Flash

存储系统已经足够,本设计采用一片 2MXl6 位的 AT49BV322A 作为 Flash 存储系统,容量为

4MB。由于 Flash 的特殊性,系统上电或复位后从此处获取指令并开始执行,因此,应将存

有程序代码的 Flash 存储器配置到 Chipselect0 上。即将 NCS0 连至 AT49BV322A 的/CE 端。

AT91RM9200 的 NCS0 连接/CE 端,起始地址为 0xl0000000;AT91RM9200 的 NRD 接/OE

端;NWRO 接/VIE 端;地址总线 A[20:1]连接地址端口 A[l9:0],数据总线 DB[15:0]连接

数据端口 DQ[15:0]。

(2) SDRAM 电路设计

与 Flash 不同,SDRAM 不具有掉电保持数据的特性,但其存取速度大大高于 Flash 存储器,

因此 SDRAM 在系统中主要用于程序的运行空间,数据及堆栈区,当系统启动时,CPU 首先

从复位地址 0x0 处读取启动代码,在完成系统的初始化后,程序代码一般调入 SDRAM 中运

行,以提高系统的运行速度,同时,系统及用户堆栈、运行数据也都放在 SDRAM 中。

SDRAM 的存储单元可以理解为一个电容,总是倾向于放电,为避免数据丢失,必须定时刷

新(充电)。因此要在系统中使用 SDRAM,就要求微处理器具有刷新控制逻辑,或是在系统中

另外加入刷新控制逻辑电路。AT91RM9200 芯片在片内具有独立的 SDRAM 刷新控制逻辑,

可方便地与 SDRAM 接口。

AT91RM9200 芯片在片内具有独立的 SDRAM 刷新控制逻辑,可方便地与 SDRAM 接口。

本设计采用的 HY57V281620H,单片容量为 4BanksX 2MX16 位,工作电压 3.3V,采用

54 脚 TSOP,兼容 LⅣTTL 接口,支持自动刷新(Auto-Refresh)和自刷新(Self-Refresh),单片为

16 位 数 据 宽 度 , 适 用 于 要 求 内 存 密 度 大 和 高 带 宽 的 场 合 。 本 设 计 选 用 2 片 16 位 的

HY57V281620H 构成 32 位 SDRAM 存储系统,满足嵌入式操作系统以及各种复杂的算法运行

要求 SDRAM 的控制信号比较多,连接电路也相对复杂。AT91RM9200 的 NCSl 分别接两片的

/CS 端;AT91RM9200 的 SDWE 分别接两片的/WE 端;HY57V281620H 的 DQML 和 AQMH 是

高低字节选择信号,AT91RM9200 的 A0/NBS0 接片 1 的 DQML,NwRl 肘 BS1/CFIOw 接片 1

的 DQMH,同理,A1/NBS2 接片 2 的 DQML,NwR3/NBs3/CFIOw 接 DQMH。BA0 和 BAl 是 SDRAM

的选择信号,AT91RM9200 的 A16/BA0 和 A17/BAl 分别接两片的 BA0 和 BAl,SDCKE 和 SDCK

分别接两片的 CKE 和 CLK,作为 SDRAM 的时钟使能和时钟,地址总线的 A[13:2]接两片的

A[11:0],数据总线的 D[15:0]接片 1 的 DQ[15:0],D[31:16]接片 2 的 DQ[15:0],组成

32 位数据。

3)NandFlash 存储器电路设计

Nand 结构 Flash 数据存储器是超大容量数据存储的理想选择,电源电压 1.7~3.6V,体积小,

功耗低,按页进行读写,通过 I/O 口分时复用作为命令/地址/数据接口。在本设计中,采用

Samsung 公司的 K9F1208UOM 存储数据,容量为 64M×8 位。

该器件 4096 个块组成,每个块有 32 个页,每页由 512 字节的数据和 1 字节的备用空间

(用来存储纠错码、坏块信息和文件系统的相关的数据)组成。这 528 字节分成 A、B、C 三个

区。对每一页的寻址需要通过 I/O 口送出三个地址,第二、三行地址指明寻址到某一页

,其中 00H 选择 A 区,01H 选择 B 区,50H 选择 c 区。选定区的内部寻址是由第一个列

A0~A7 最大寻址 256 字节。

由于 NandFlash 对数据的读写操作都是以页为单位的,擦除则是以块为单位的,因此一次擦

出的最小空间 0x4000(214)字节。对芯片的读写以及擦除命令的写入都是通过置高 CLE 引脚

同时向 I/O0~I/O7 写入命令代码字节来完成的,地址的写入则是通过置高 ALE 引脚同时写入

地址字节完成。

�

3.温度控制系统应用程序的设计

3.1.1 主程序功能与实现

Int semid start;

MainCreatChildProcess0;

Semid_start=semget(SEM_START,I,IPC_CREAT|0666);

signal(SIGTERM,my_exit);//安装信号,处理退出前的收尾工作

While(1)

//创建子进程

{

Int dead= mainChildOneStakeOut(); //监视子进程,若子进程死亡则重新创建

}

Return 0;

3.1.2 AD 数据采集程序功能与实现

无需使用很高的采集频率,在 AD 数据采集程序中设定每隔 1 秒钟采集一次通道,根据接

收的模式确定手动自动,并把数据写入 AD 共享内存或 DA 共享内存中。程序中调用非阻塞

的 selectoffl 数,解决如果通道无法采集时,系统停止在数据采集语句上的问题,避免了系

统阻塞,防止浪费系统资源。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc