中国科技论文在线

http://www.paper.edu.cn

RS(204,188)编码模块的设计与实现

高松1,陈钢2,谢志军2*

(1. 重庆邮电大学通信学院,重庆 400065;

2. 四川师范大学成都学院,成都 611745)

摘要:本文详细介绍了 RS 编码器的工作原理,介绍了有限域常数乘法器的实现方法;首先,

通过编写 M 文件实现 RS(204,188)编码器并在 MATLAB 中对其进行模拟仿真,然后,采用 VHDL

语言编写 RS 编码器的 RTL 代码并在 MODELSIM 中对其进行功能仿真,最后,对两种测试环境

下的仿真结果进行了对比和分析,并给出了仿真结果图;通过 Quartus II 编译之后,最终

在 FPGA 上实现。

关键词:RS 编码器;有限域;MODELSIM;FPGA

中图分类号:TN941.4

the design and implementation of RS (204,188) encoder

module

Gao Song1, Chen Gang2, Xie Zhijun2

(1. Chongqing University of Posts and Telecommunication, ChongQing 400065;

2. Chengdu College of Sichuan Normal University, ChengDu 611745)

Abstract: This paper describes the working principle of RS encoder, and realization methods of the

finite field constant multiplier; first of all, the RS (204,188) encoder is implemented by using M files

simulated in MATLAB; second, RTL code is made by VHDL and is simulated in MODELSIM, finally,

results are compared and analyzed between the two simulation environments, and the simulation

Figures are in show; it is finally implemented in the FPGA after Quartus II compilation.

Keywords:RS encoder;finite field;MODELSIM;FPGA

0 引言

Reed-Solomon 码是一类具有很强纠错能力的 BCH 码,已经被用在各种通信系统中,如

深空通信、数字用户环路、无线通信等。RS 译码器用于纠正数字信号中产生的错误,以降

低信号传输过程中对信噪比的要求。数字电视广播中 DVB 和 ATSC 标准都采用了 RS 码,

在 DVB-C 系统中采用了缩短码-RS(204,188)码[1],对于(N,K)RS 码,以 N 为码长,K

为信息符号的个数,2t=N-K 为校验符号的个数,RS 码具有良好的纠错能力,既能纠正突发

性的错误,也能纠正随机性的错误,RS 码的纠错能力为 t。DVB-C 系统中的 RS 纠错能力

为 8,一个码字中有 16 个校验码元。

1 RS 编码原理

2)

GF

域上的信息码元多项式为

RS 码是码元取自GF(q)(

q ≠ 上的 BCH 码,码元的符号域与根域是一致的。在(n,k)RS

码中,输入的信息分成 k m⋅ 比特一组,每组包括 k 个符号,每个符号由 m 个比特组成[2]。

m x m

m x

假定 (2 )m

+

+

+

;将移

k

0

2

C x m x x

r x

( )

( )

位后的信息多项式与生成多项式 g(x)相除,就可以得到: ( )

n k

−

r(x)=

作者简介:高松,(1985-),男,硕士生,研究方向为移动通信. E-mail: sungkao1985@163.com

是移位后的信息多项式被 g(x)除后的余式,它的次数低于 n-k,r(x)

tx m x

2

( )modg(x)

m x m x

1

−

( )

=

;其中

1

+

k

1

−

+

k

−

2

=

k

−

- 1 -

�

中国科技论文在线

http://www.paper.edu.cn

被称为校验多项式[3]。用矢量的形式表示编码后的码字 c(x)为:

r r

c(x)=( , ,

0 1

…,

r m m

,

,

……, ,

t

2 1

1

−

m

)

k

1

−

,

0

可以看出,编码后的码字中,信息码元可以清晰地与校验码元分开,这种码我们称之为系统

码。以 DVB-C 系统中的 RS(204,188)为例,

8(2 )

1

+ ;码生成多项式为

GF

域上的本原多项式为

x a

g x

( )

)

−

x a

−

)(

=

(

p x

( )

=

8

x

+

4

x

+

3

x

+

2

x

0

−

x a

15

(

)

,其

中 a 是本原元。下图为 RS 编码器结构图。

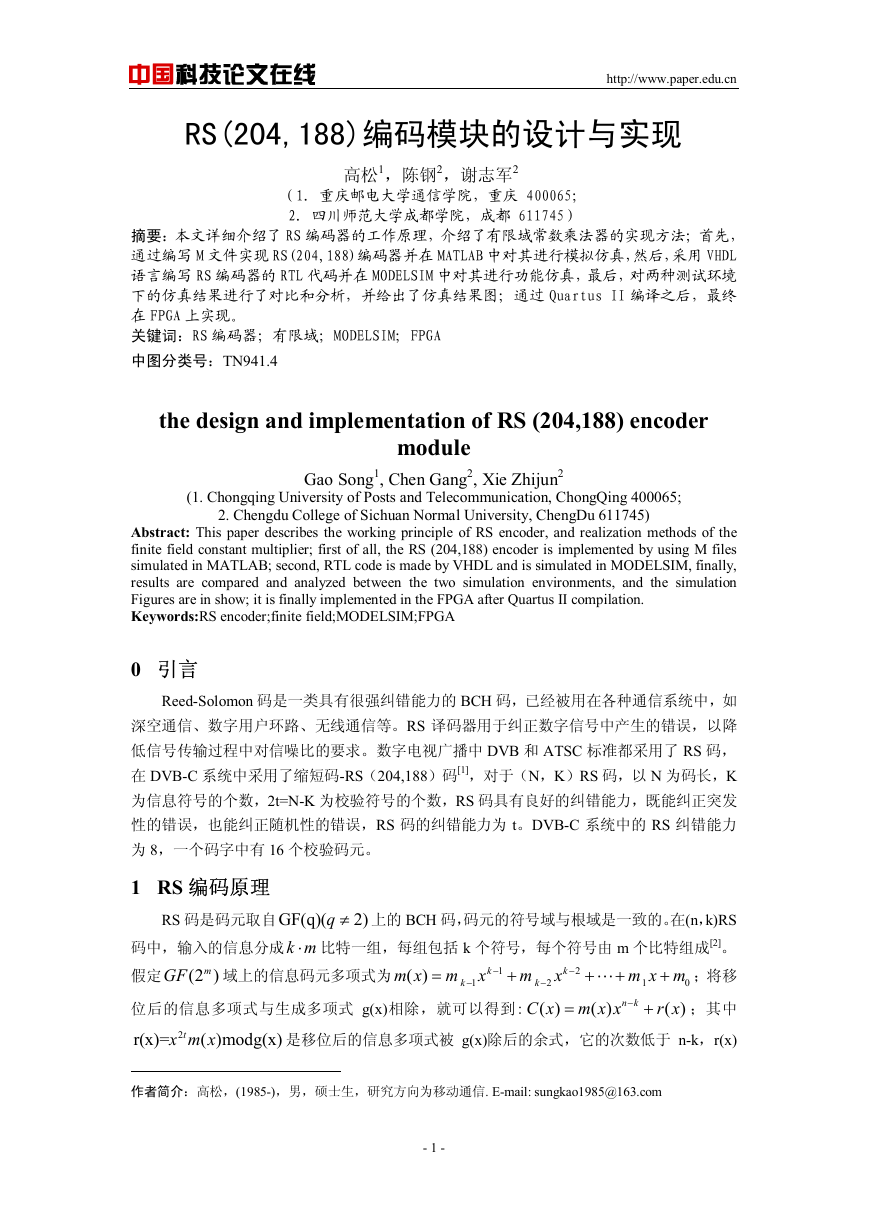

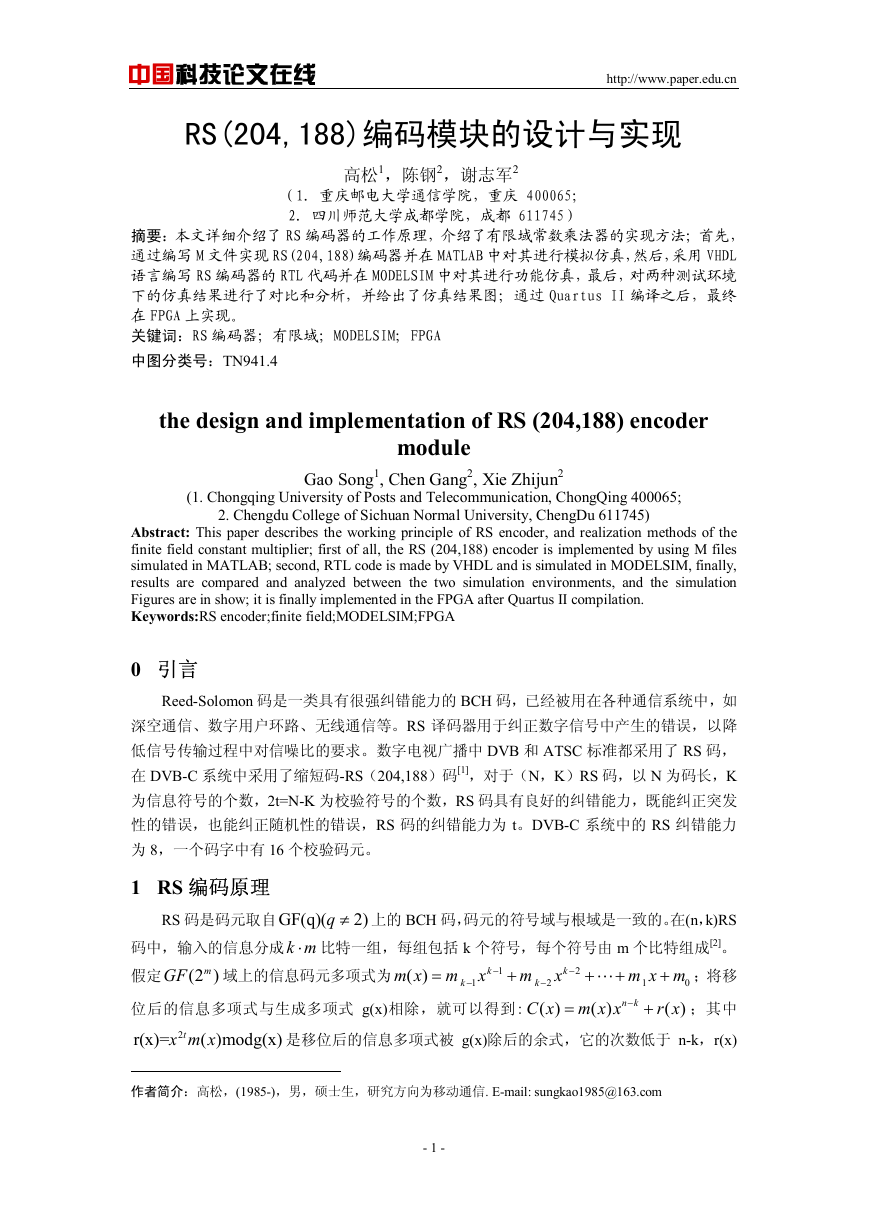

图 1 RS 编码器的结构图

工作原理如下:(1)首先,寄存器的状态全部被清零,开关 K 接通 gate3;在时钟的

作用下,信息码元 m(x)一方面直接输出,另一方面移位进入上面的除法电路。(2)当信息

码元全部输出完毕后,此时移位寄存器保存的数据就是校验码元 r(x)。(3)接下来,将开

关 K 接通 gate2,在时钟的作用下,依次输出效验码元,这样就完成了一次编码过程。(4)

重复(1)、(2)、(3)对下一组码字进行编码。

2 编码器的设计

笔者在 MATLAB7.0 中通过编写 M 文件实现了 RS 编码器方便后面对 RTL 代码的验证,

g 分别为 59 ,36,

首先需要求出码生成多项式的系数,通过编写一个小程序求得: 0

50, 98,229,41,65,163,8,30,209,68,189,104,13,59。取一段待编码信息如

1~188 输入到笔者设计的编码函数 y=rs_encoder(x)中,运算得到的码字为 y=[1,2,3,…,

187,188,195,231,90,194,142,112,85,171,63,242,251,154,1,82,33,222],

通过大量的测试可知笔者设计的编码函数是正确的。编码函数的部分代码如下所示。

15~g

r=zeros(1,n-k);

for i=1:k

feedback=rs_add(m_xi(i),r(n-k)) ;

for j=n-k:-1:2

if (gx(j)~=0)

r(j) =rs_add(r(j-1),rs_mul(gx(j),feedback,alpha_to,index_of));

else

r(j) = r(j-1) ;

end;

end;

r(1) = rs_mul(gx(1),feedback,alpha_to,index_of);

end;

- 2 -

�

中国科技论文在线

http://www.paper.edu.cn

由图 1 可知,编码器电路涉及到大量的有限域乘法器和加法器运算,其中加法器的实现

比较简单,可以由异或门来实现;乘法器比较复杂、延迟大,在某种程度上影响着电路的性

能。有限域乘法器的设计可分为:标准基乘法器、正规基乘法器和对偶基乘法器。正规基表

示是由 Massey 和 Omura 发明的,所以正规基乘法器通常也称为 MO(Massey-Omura)乘法器

[4][5]。它最大优势是平方运算可以通过简单的右移实现。对偶基乘法器将被乘数和乘积项用

对偶基表示,而乘数用标准基表示,这样能显著降低乘法器的硬件复杂度。然而,对偶基乘

法器和 MO 乘法器在运算时都需要进行基的转换,或多或少增加资源耗费和运算延迟。因

此,在实际应用中主要还是采用标准基乘法器,该类型乘法器不需要进行基转换,而且在资

8(2 )

源耗费和延迟方面也占有一定的优势。标准基乘法器还可以进一步分为比特串行、比特并行

和串并混合 3 个类型。本文采用比特并行的 Mastrovito 乘法器,因为生成多项式的系数是固

定的,所以最终的实现形式是有限域常数乘法器。下面详细介绍 Mastrovito 乘法器[6],以

p x

GF

( )

表示域上的元素 A 和 B,

那么有,

C x

( )

=

GF

8(2 )

1

+ 是

a x a

+

+

+

1

的本原多项式,并用多项式基来

( )B x b x b x

6

6

+

bx b

+ +

1

0

+ + + +

x

=

( )A x

x

+

a x

7

7

x

+

a x

6

为例,假设

,计算得

)mod(

+ +

x

+

+

=

a x a b x

7

1

7

bx b

+

1

0

b x

6

6

x

4

x

3

x

2

x

8

)(

0

1)

7

+

,

0

2

6

=

7

+

8

4

3

+

,

+ +

到 C(x)各项的系数如下:

a x

(

7

7

a x

6

6

+

b a

3 5

a

+

5

b a

b a

(

+

+

4 4

5

3

a

a

)

+

+

6

7

+

a

7

)

b a

b a

b a

+

+

+

3 6

2 7

4 5

b a

a

a

(

)

+

+

7

2

6

7

+

b a

5 4

b a

(

2

0

a

+

4

b a

(

2

1

b a

(

6

2

b a

(

2

2

a

+

3

+

+

a

6

a

6

b a

a

(

)

+

+

5

3

7

a

b a

(

)

+

+

7

7

1

b a

)

(

+

4

4

a

a

+

+

3

5

+

+

a

6

a

6

)

)

+

+

a

6

a

3

+

+

a

7

a

5

b a

a

(

)

+

+

0

3

5

a

b a

(

)

+

+

6

7

1

+

+

a

6

a

2

b a

)

(

+

4

4

a

a

+

+

4

5

+

)

a

5

+

a

7

)

+

+

a

+

6

a

)

+

4

a

)

+

7

b a

(

7

1

b a

(

3

1

a

+

2

+

+

a

5

a

3

+

+

a

+

6

a

)

7

a

7

)

+

b a

(

4

0

+

a

4

+

a

5

+

a

6

)

+

)

b a

0 2

+

b a

0 0

+

b a

+

2 6

b a

(

+

7

1

a

)

+

+

7

b a

(

)

+

6

2

0x 的系数:

b a

c

+

=

1 7

0

b a

a

a

(

+

+

7

6

6

2

1x 的系数:

c

b a

b a

=

+

1 0

0 1

1

b a

a

(

)

+

+

+

6

3

7

2x 的系数:

b a

c

(

+

=

1

1

2

a

a

b a

(

+

+

7

5

5

3

3x 的系数:

c

b a

(

+

=

3

1

2

a

b a

a

(

+

+

4

5

3

6

4x 的系数:

b a

a

c

(

)

+

+

+

=

1

3

7

4

b a

b a

a

a

)

(

(

+

+

+

5

6

2

4

5

3

5x 的系数:

b a

c

+

=

1 4

5

b a

a

a

(

+

+

5

4

5

0

6x 的系数:

c

+

=

6

a

b a

(

+

5

5

1

b a

+

2 4

a

)

+

7

b a

1 5

a

+

6

b a

0 4

+

b a

0 3

+

b a

0 5

+

b a

0 6

+

a

7

a

7

+

+

+

+

)

)

a

b a

)

(

+

+

7

3

2

b a

a

(

)

+

+

6

3

6

b a

(

+

3

2

a

+

+

4

+

a

5

a

a

)

+

7

6

b a

(

)

+

7

2

b a

(

+

4

1

a

+

+

3

a

5

)

+

a

4

+

a

6

+

a

7

)

b a

(

+

3

3

b a

(

+

6

0

+

+

a

7

a

4

b a

)

(

+

4

2

a

a

+

+

5

6

a

a

+

+

6

7

b a

(

)

+

7

3

)

+

a

4

+

a

5

)

- 3 -

�

中国科技论文在线

http://www.paper.edu.cn

7x 的系数:

b a

c

+

=

1 6

7

a

a

b a

(

+

+

2

7

6

5

g = ,根据以上步骤计算,我们可以写出 0g 对应的有限域常数乘法器的 VHDL

59

a

)

7

b a

)

(

+

7

0

b a

(

+

3

4

a

+

+

6

b a

+

2 5

b a

(

+

6

1

b a

3 4

a

+

5

b a

0 7

+

+

a

7

例如 0

+

a

4

+

a

5

+

)

+

a

6

)

语言描述,如下所示:

mux0(0)<=feedback(0) xor feedback(3) xor feedback(4) xor feedback(5) ;

mux0(1)<=feedback(0) xor feedback(1) xor feedback(4) xor feedback(5) xor feedback(6);

mux0(2)<=feedback(1) xor feedback(2) xor feedback(3) xor feedback(4) xor feedback(6) xor

feedback(7);

mux0(3)<=feedback(0) xor feedback(2) xor feedback(7);

mux0(4)<=feedback(0) xor feedback(1) xor feedback(4) xor feedback(5);

mux0(5)<=feedback(0) xor feedback(1) xor feedback(2) xor feedback(5) xor feedback(6);

mux0(6)<=feedback(1) xor feedback(2) xor feedback(3) xor feedback(6) xor feedback(7);

mux0(7)<=feedback(2) xor feedback(3) xor feedback(4) xor feedback(7);

其它 15 个有限域常数乘法器可采用相同的方法求出。

3 仿真与测试

本文采用 VHDL 语言完成 RTL 代码的编写,然后在 Mentor 公司的 ModelSim SE 6.2b

仿真验证工具下编写 testbench 测试文件。首先,借助 MATLAB 平台,通过编写 M 文件产

生仿真所需要的数据源文件 ts.dat 来模拟 MPEG 包,之后经过 RS 编码之后保存为 rs_test.dat;

然后,VHDL 测试代码读入 ts.dat 文件,经过本文设计的 RS 编码器编码后输出到 rs_rtl.dat

文件。最后,将 rs_test.dat 与 rs_rtl.dat 中的数据进行比较,除了最后几个码元因为编码器输

出的延迟作用未能读入到 rs_rtl.dat 文件,前面的数据完全相同。仿真结果如图 2、3、4 所

示:

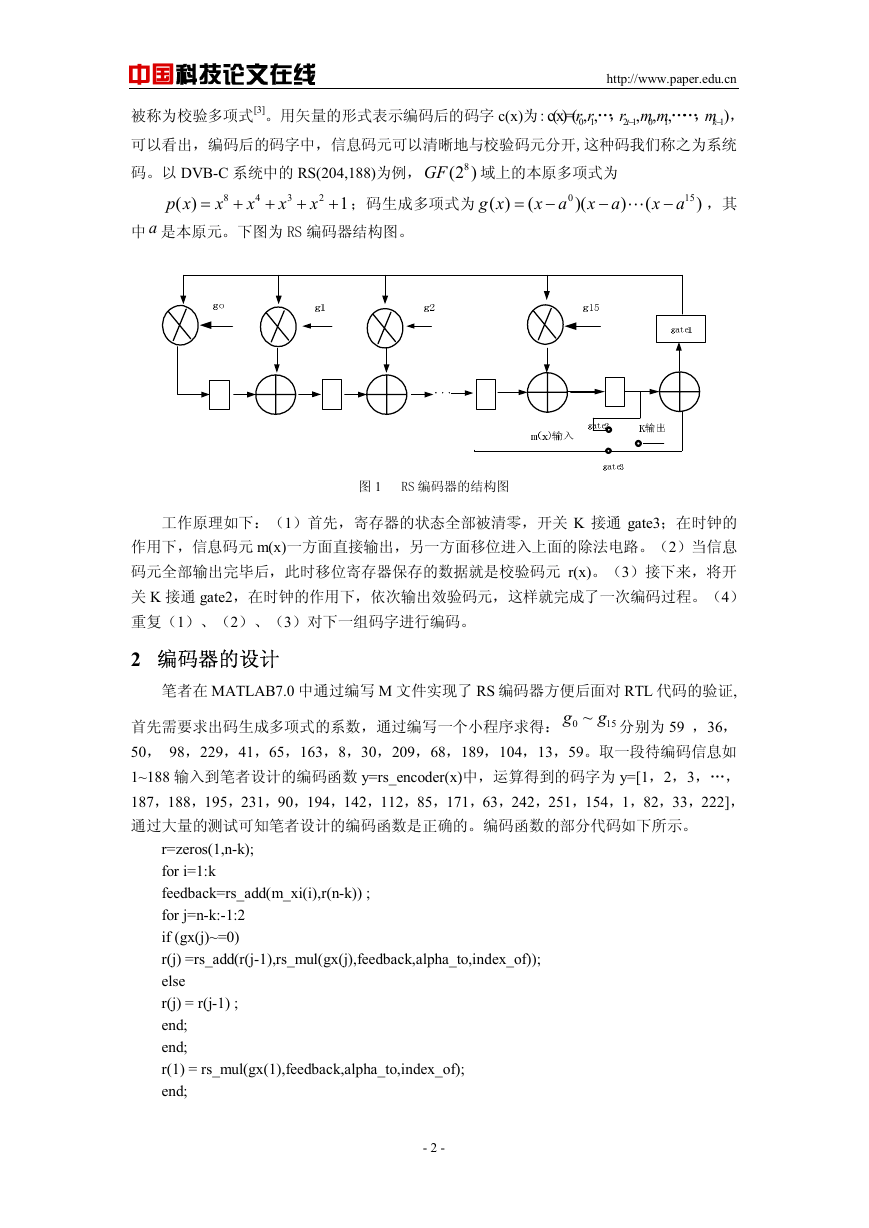

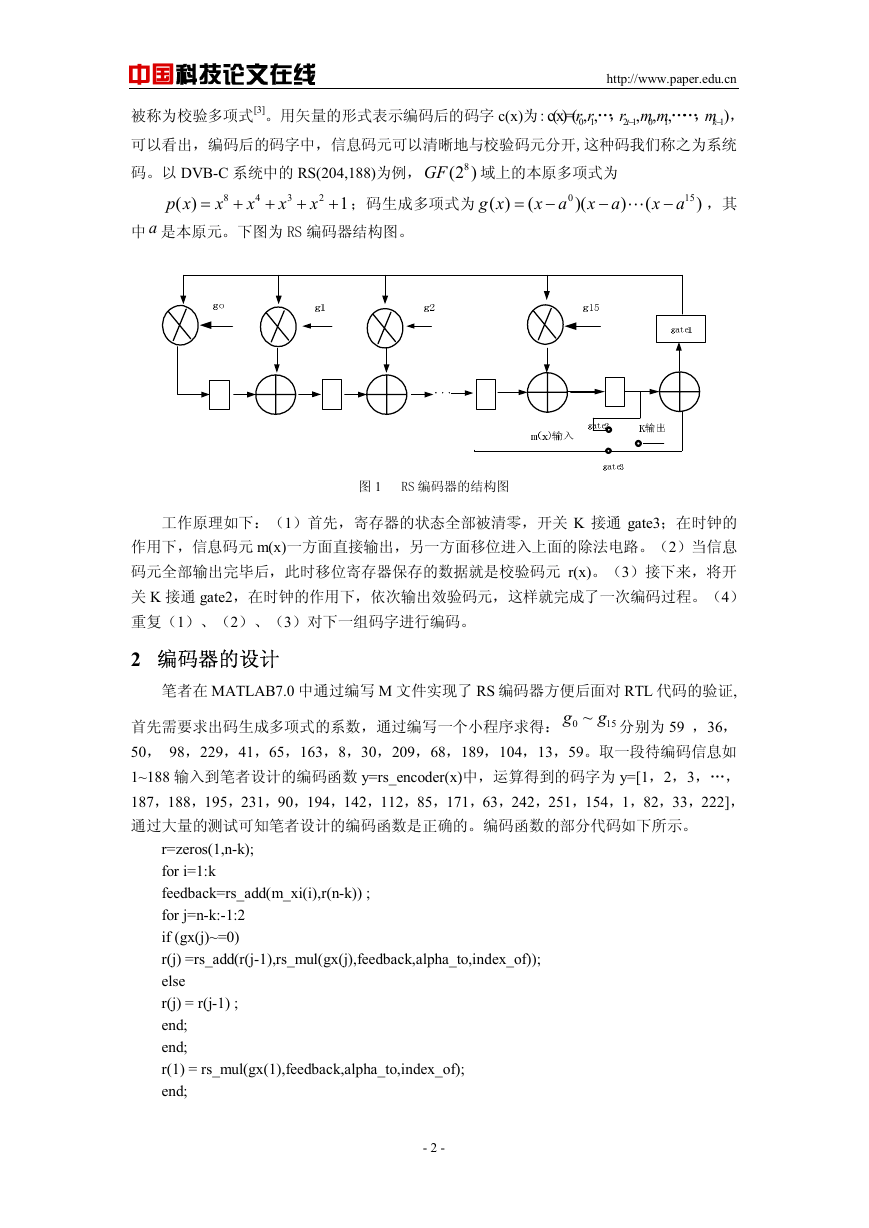

图 2 100 组码字的编码结果

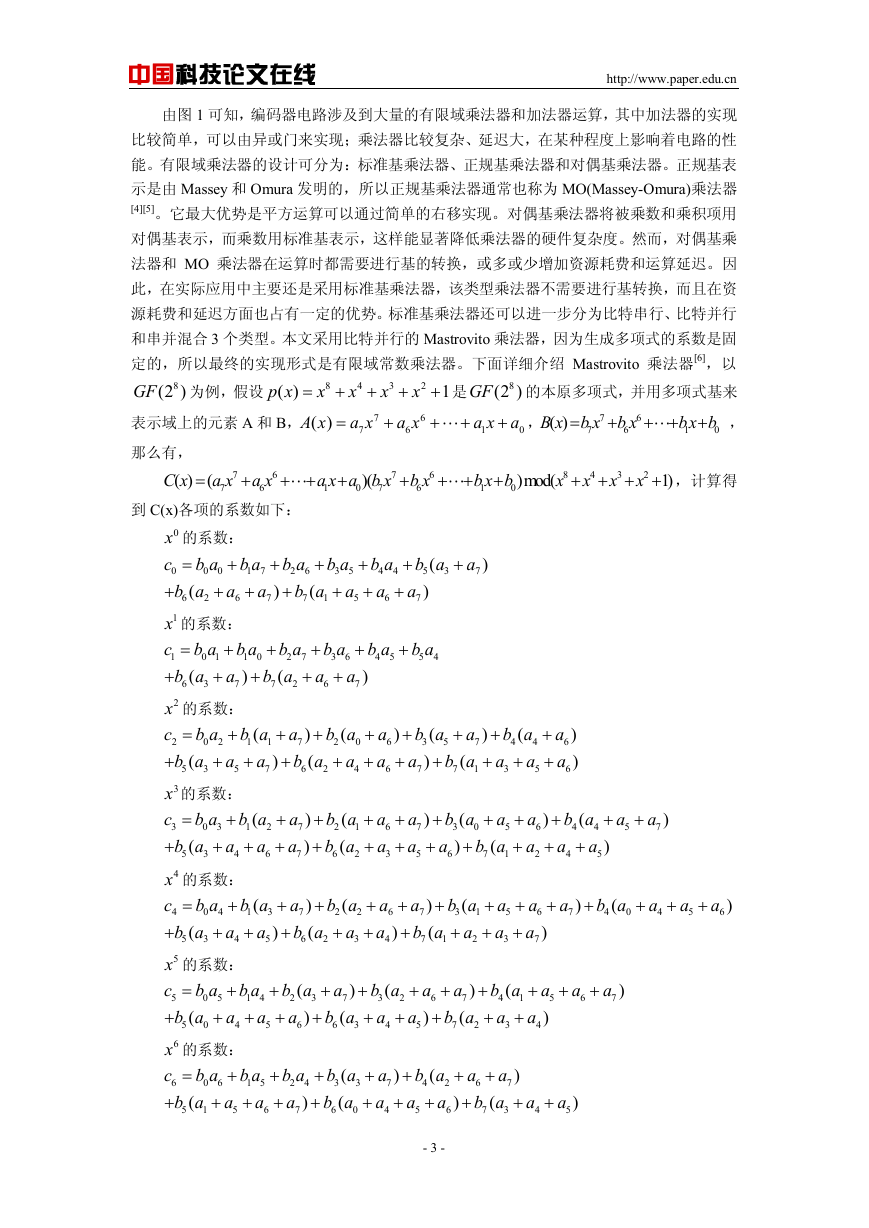

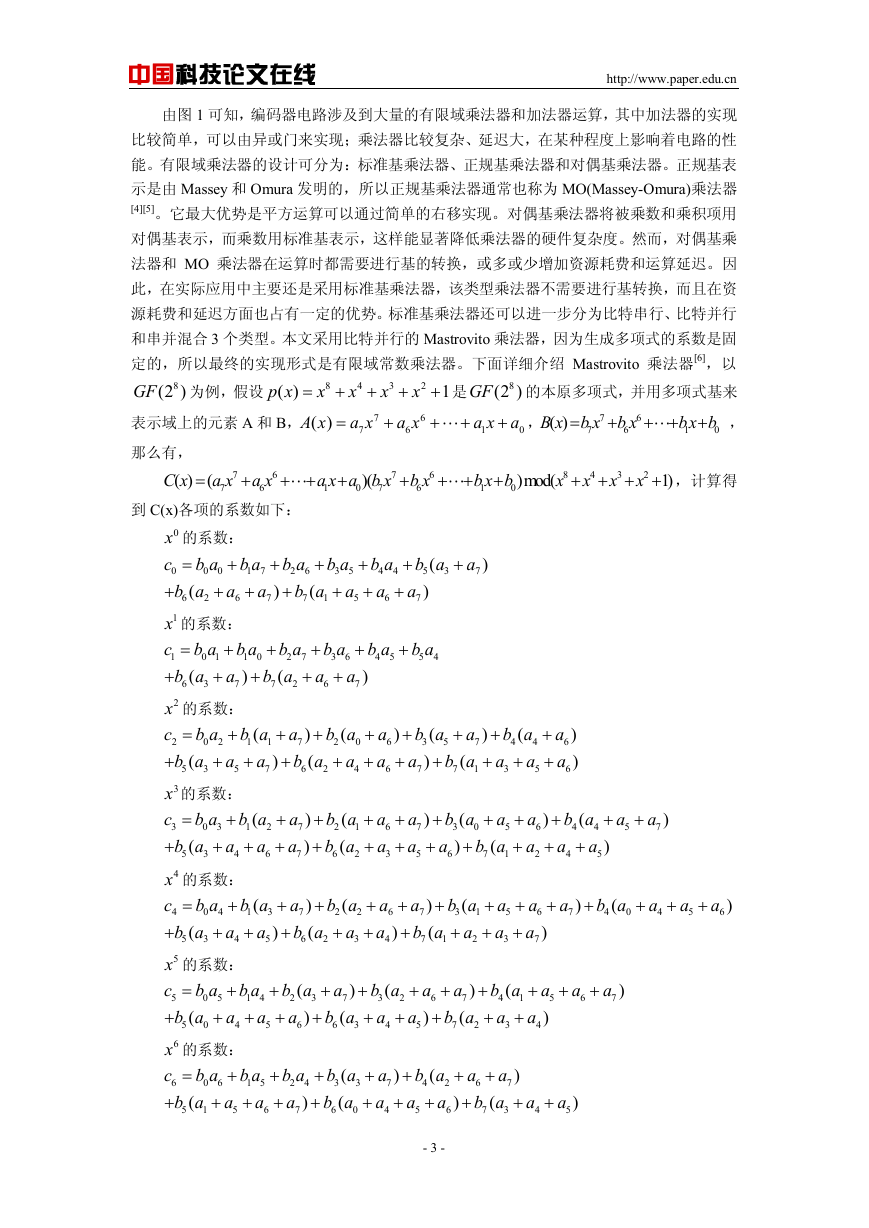

图 3 单组码字的编码结果 1

- 4 -

�

中国科技论文在线

http://www.paper.edu.cn

图 4 单组码字的编码结果 2

经过 MATLAB 仿真之后保存的文件 rs_test.dat 大小为 92KB,即 100 组码字;图 2 为这

100 组码字在 modelsim6.2b 中的仿真图,图 3、4 分别为第 9 组码字的信息码元部分和校验

码元部分。

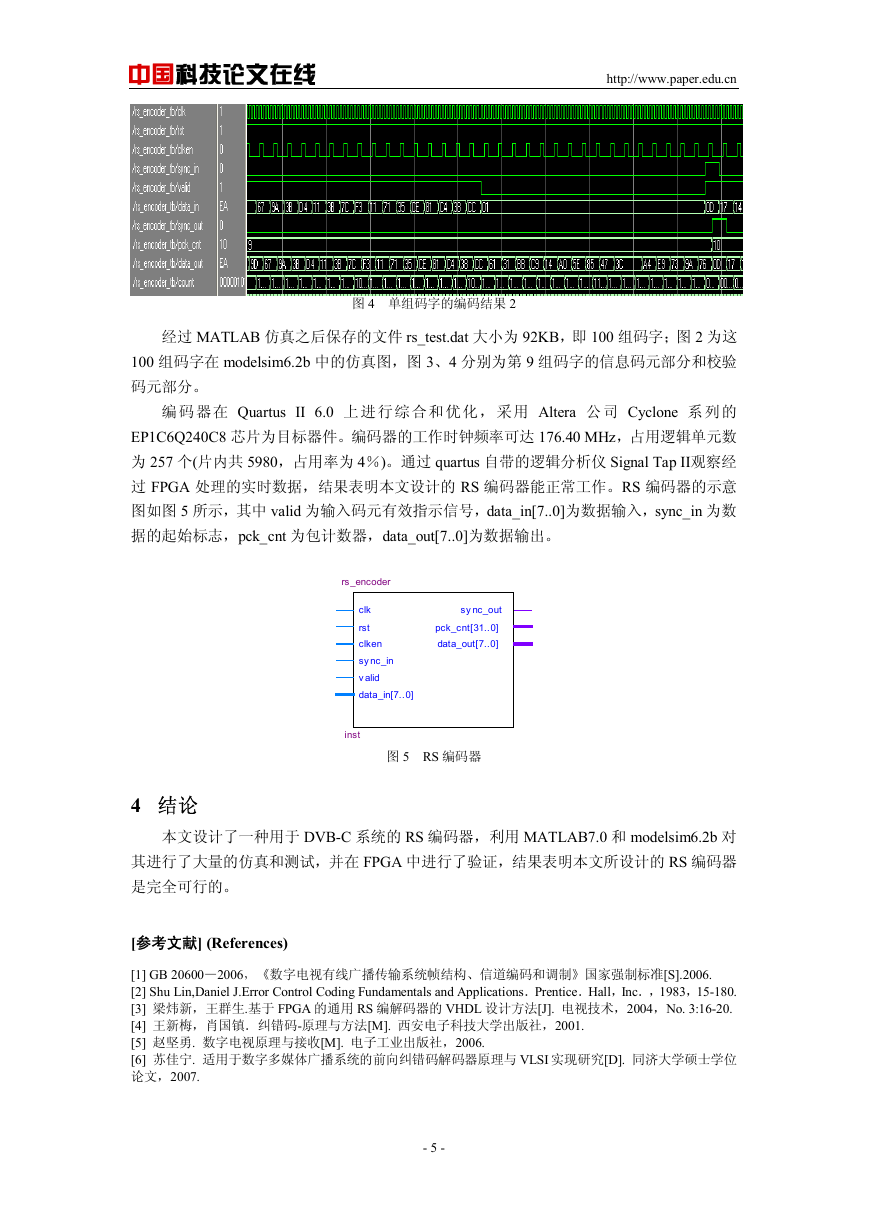

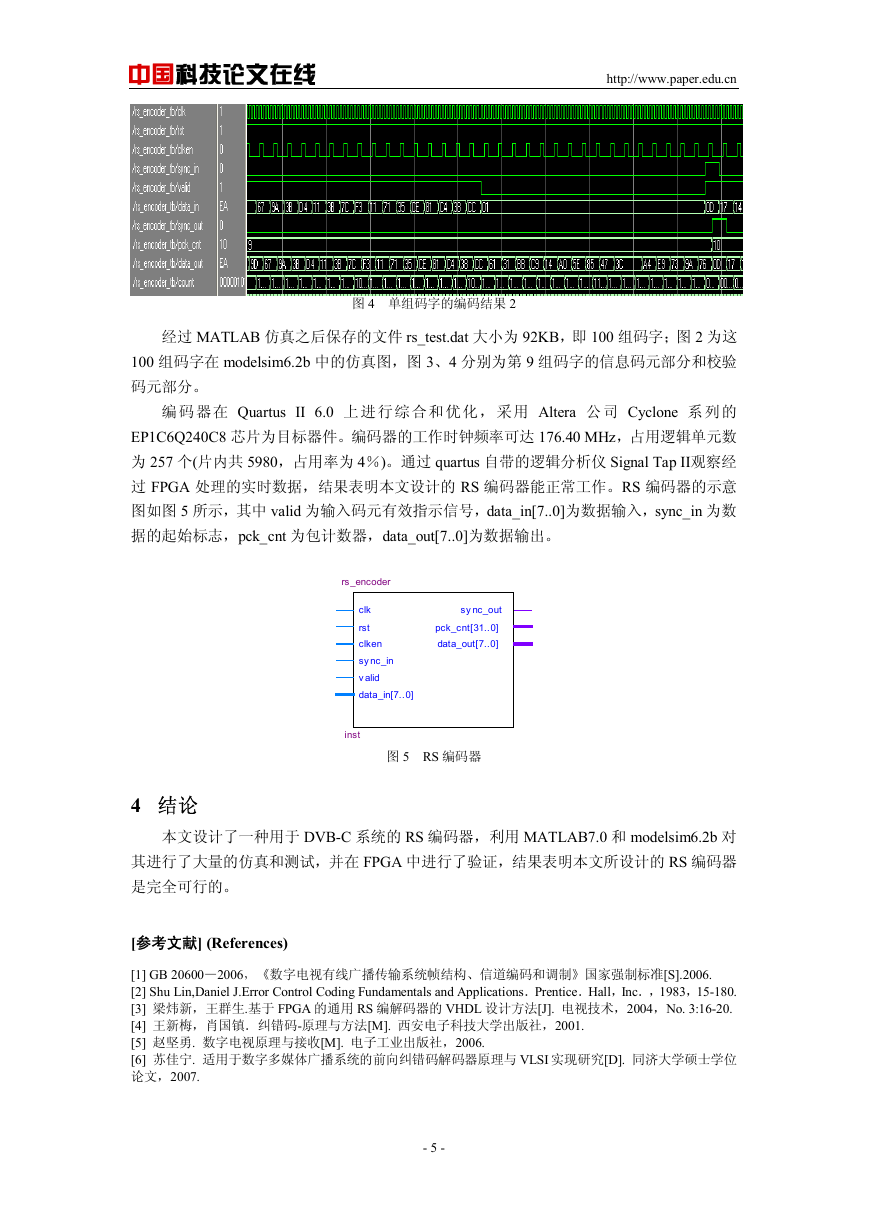

编 码 器在 Quartus II 6.0 上 进 行综 合和 优 化, 采用 Altera 公 司 Cyclone 系 列 的

EP1C6Q240C8 芯片为目标器件。编码器的工作时钟频率可达 176.40 MHz,占用逻辑单元数

为 257 个(片内共 5980,占用率为 4%)。通过 quartus 自带的逻辑分析仪 Signal Tap II观察经

过 FPGA 处理的实时数据,结果表明本文设计的 RS 编码器能正常工作。RS 编码器的示意

图如图 5 所示,其中 valid 为输入码元有效指示信号,data_in[7..0]为数据输入,sync_in 为数

据的起始标志,pck_cnt 为包计数器,data_out[7..0]为数据输出。

sy nc_out

pck_cnt[31..0]

data_out[7..0]

rs_encoder

clk

rst

clken

sy nc_in

v alid

data_in[7..0]

inst

图 5 RS 编码器

4 结论

本文设计了一种用于 DVB-C 系统的 RS 编码器,利用 MATLAB7.0 和 modelsim6.2b 对

其进行了大量的仿真和测试,并在 FPGA 中进行了验证,结果表明本文所设计的 RS 编码器

是完全可行的。

[参考文献] (References)

[1] GB 20600—2006,《数字电视有线广播传输系统帧结构、信道编码和调制》国家强制标准[S].2006.

[2] Shu Lin,Daniel J.Error Control Coding Fundamentals and Applications.Prentice.Hall,Inc.,1983,15-180.

[3] 梁炜新,王群生.基于 FPGA 的通用 RS 编解码器的 VHDL 设计方法[J]. 电视技术,2004,No. 3:16-20.

[4] 王新梅,肖国镇.纠错码-原理与方法[M]. 西安电子科技大学出版社,2001.

[5] 赵坚勇. 数字电视原理与接收[M]. 电子工业出版社,2006.

[6] 苏佳宁. 适用于数字多媒体广播系统的前向纠错码解码器原理与 VLSI 实现研究[D]. 同济大学硕士学位

论文,2007.

- 5 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc