简答题:

1. 进制转换(二-十,十-十六进制转换,注意带小数十进制数转二进制,BCD 码的转换)

答:BCD 码,又称 8421 码,四位;十制小数转换成二进制,乘 2 处理。

2. 单片机 C51 用 idata 及 xdata 定义变量的存放区域 及其汇编指令

答:

3. 位运算 (置位 清零 取反)

将 a.2 清零,其他位不变,语句(~0x04)&a

将 a.2 置位,其他位不变,语句 0x04|a___

将 a.2 取反,其他位不变,语句 (a&~4)^(~a)

4. 卡诺图化简法求出最简式。基本的卡诺图化简为最简与或式

答:存同去异,法则 A’B+AB=B(A’+A)=B

5. 看门电路写出函数式。

答:与门:Y=AB 或门:Y=A+B 与非门:Y=(AB)’ 或非门:Y=(A+B)’ 非门:Y=A’ 异或

门:Y=A’B+AB’ 同或门:Y=A’B’+AB

6. 亚稳态解释和解决办法

答:触发器无法在规定的时间内达到一个稳定的输出电平状态,解决的方法:用反应快的触

发器,降底时钟的频率,改善时钟质量,引入同步机制。

7. CPLD 和 FPGA 的主要区别。

答:

1.结构上的不同

2.集成度不同

CPLD:500---50000 门

FPGA:1K----10M 门

3.应用范围不同

1

�

CPLD 逻辑能力强而寄存器少(1K 左右),适用于控制密集型系统;

FPGA 逻辑能力较弱但寄存器多(100 多 K),适用于数据密集型系统.

4.使用的方法不同

CPLD 是 EEPROM,FPGA 是 SRAM 工艺.

8. 求运放电压增益

答:(虚短虚断,叠加定理)

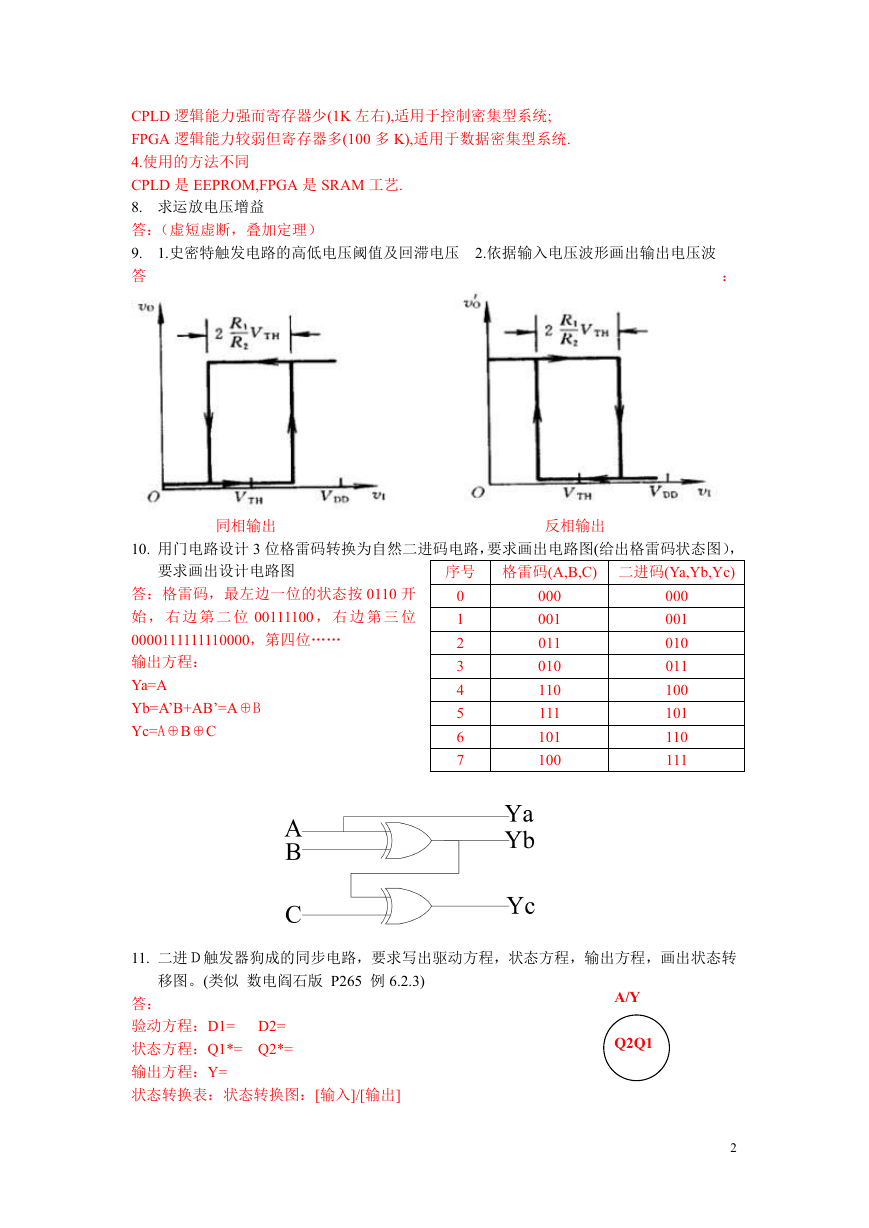

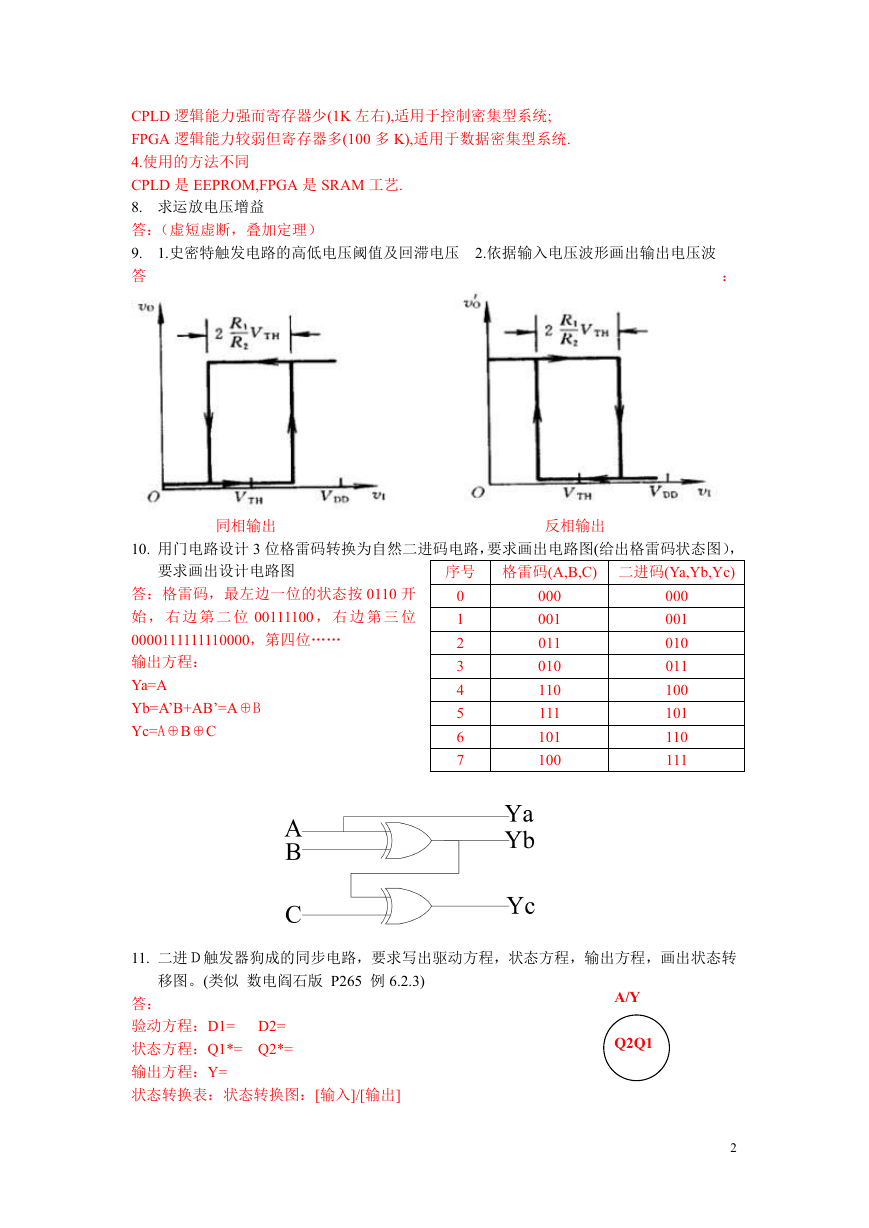

9. 1.史密特触发电路的高低电压阈值及回滞电压 2.依据输入电压波形画出输出电压波

答

:

同相输出

反相输出

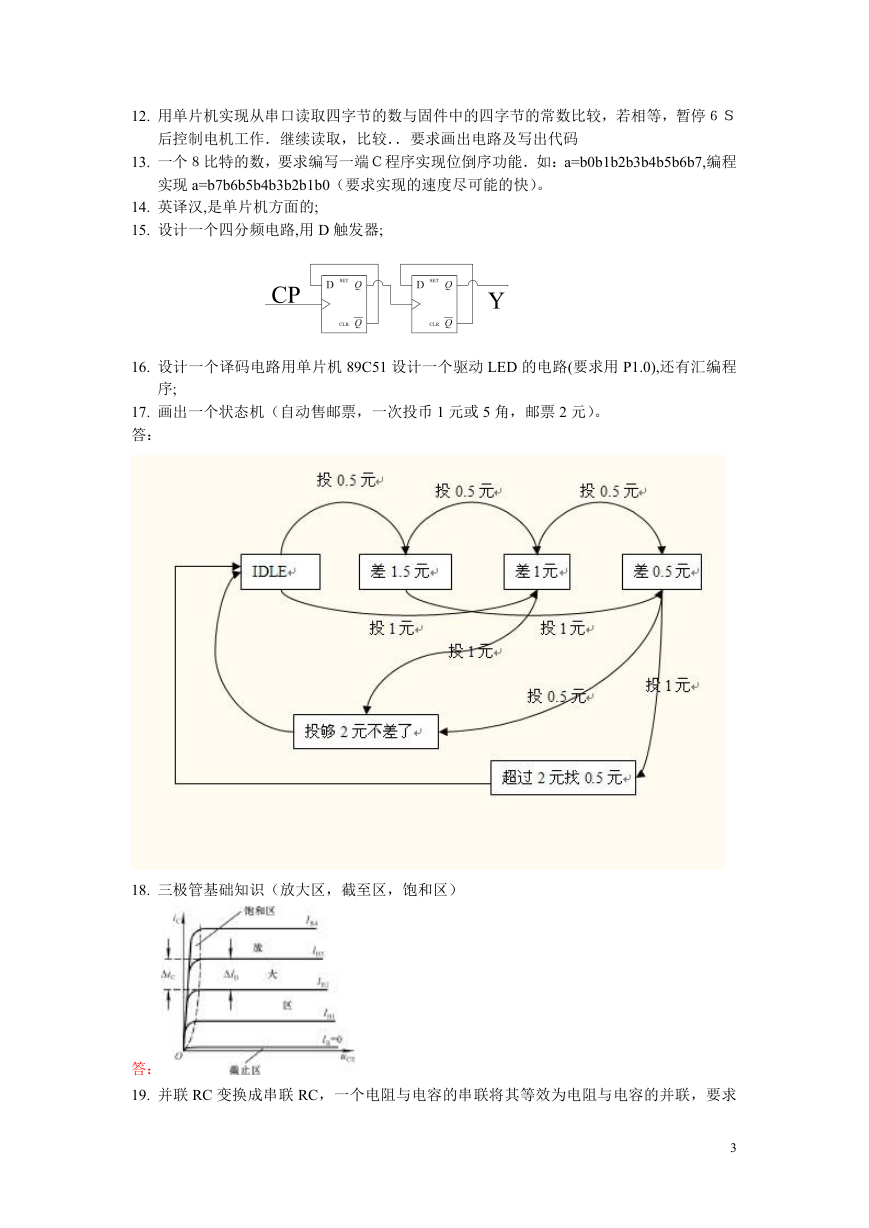

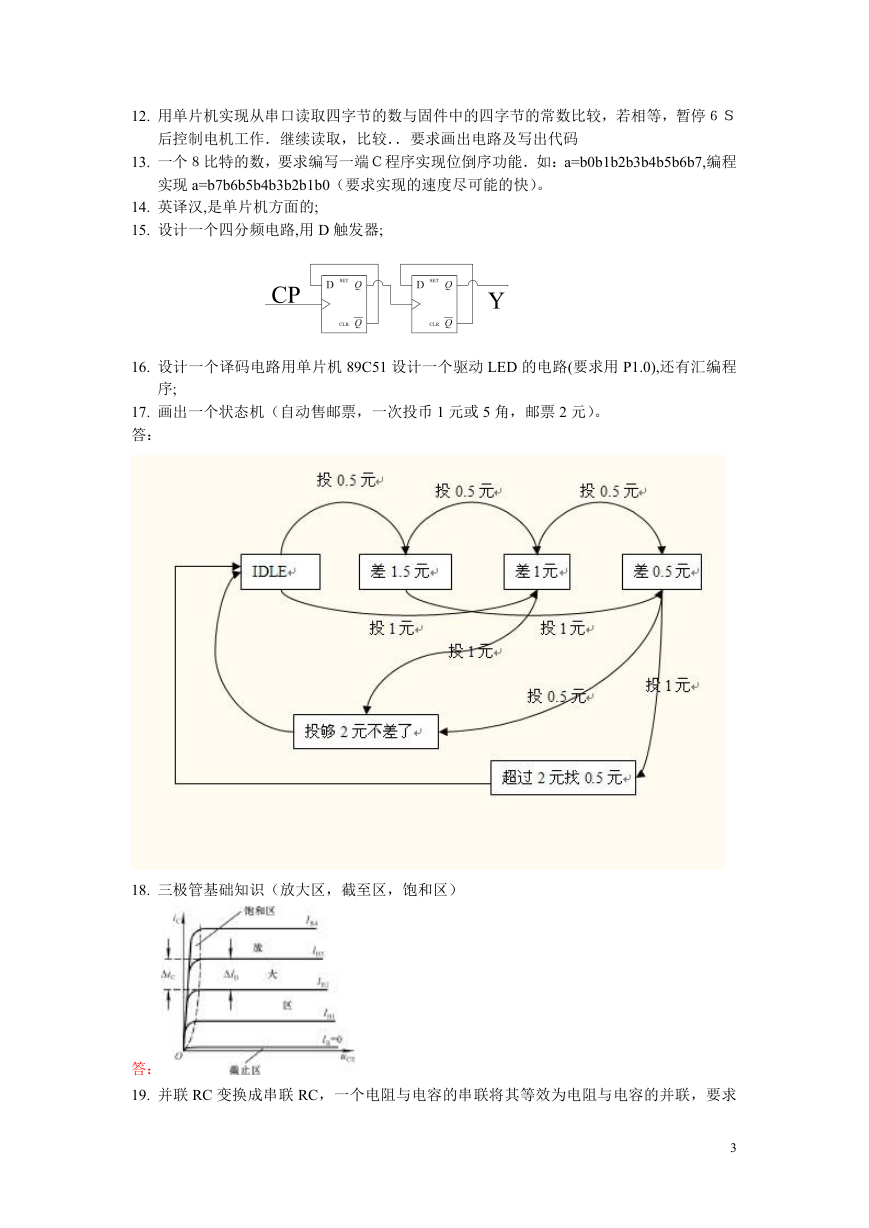

10. 用门电路设计 3 位格雷码转换为自然二进码电路,要求画出电路图(给出格雷码状态图),

序号 格雷码(A,B,C) 二进码(Ya,Yb,Yc)

要求画出设计电路图

答:格雷码,最左边一位的状态按 0110 开

始 , 右 边 第 二 位 00111100 , 右 边 第 三 位

0000111111110000,第四位……

输出方程:

Ya=A

Yb=A’B+AB’=A⊕B

Yc=A⊕B⊕C

0

1

2

3

4

5

6

7

000

001

011

010

110

111

101

100

000

001

010

011

100

101

110

111

11. 二进D触发器狗成的同步电路,要求写出驱动方程,状态方程,输出方程,画出状态转

移图。(类似 数电阎石版 P265 例 6.2.3)

答:

验动方程:D1=

D2=

状态方程:Q1*= Q2*=

输出方程:Y=

状态转换表:状态转换图:[输入]/[输出]

A/Y

Q2Q1

2

�

12. 用单片机实现从串口读取四字节的数与固件中的四字节的常数比较,若相等,暂停6S

后控制电机工作.继续读取,比较..要求画出电路及写出代码

13. 一个8比特的数,要求编写一端C程序实现位倒序功能.如:a=b0b1b2b3b4b5b6b7,编程

实现 a=b7b6b5b4b3b2b1b0(要求实现的速度尽可能的快)。

14. 英译汉,是单片机方面的;

15. 设计一个四分频电路,用 D 触发器;

16. 设计一个译码电路用单片机 89C51 设计一个驱动 LED 的电路(要求用 P1.0),还有汇编程

序;

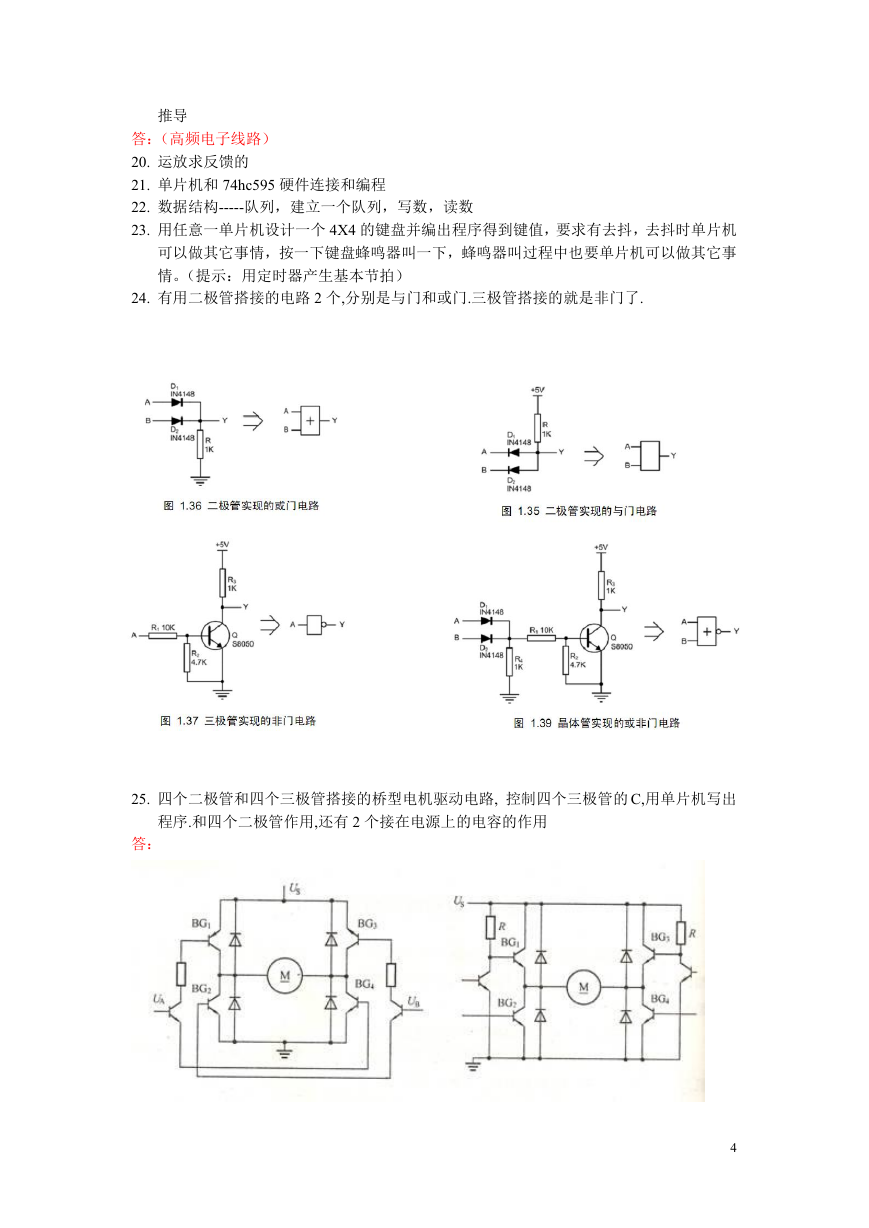

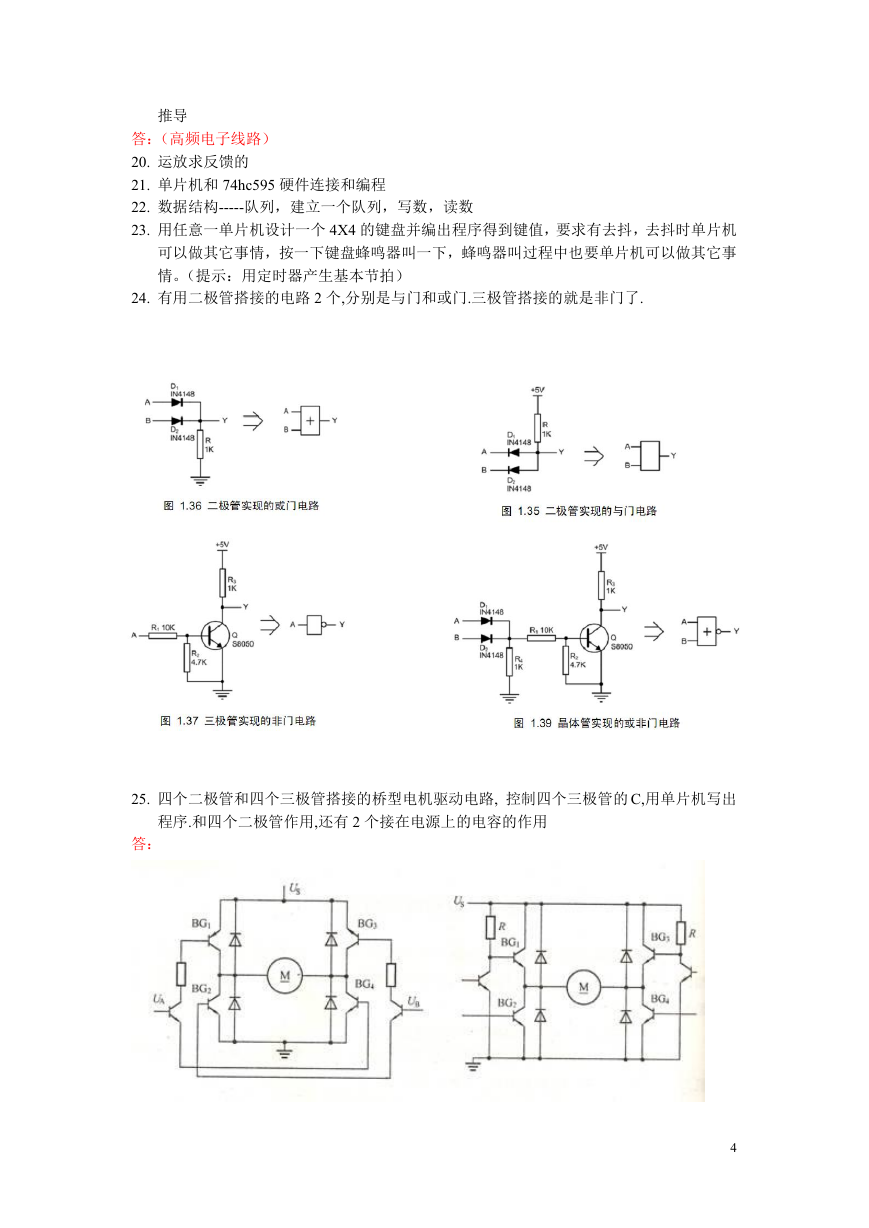

17. 画出一个状态机(自动售邮票,一次投币 1 元或 5 角,邮票 2 元)。

答:

18. 三极管基础知识(放大区,截至区,饱和区)

答:

19. 并联 RC 变换成串联 RC,一个电阻与电容的串联将其等效为电阻与电容的并联,要求

3

�

推导

答:(高频电子线路)

20. 运放求反馈的

21. 单片机和 74hc595 硬件连接和编程

22. 数据结构-----队列,建立一个队列,写数,读数

23. 用任意一单片机设计一个 4X4 的键盘并编出程序得到键值,要求有去抖,去抖时单片机

可以做其它事情,按一下键盘蜂鸣器叫一下,蜂鸣器叫过程中也要单片机可以做其它事

情。(提示:用定时器产生基本节拍)

24. 有用二极管搭接的电路 2 个,分别是与门和或门.三极管搭接的就是非门了.

25. 四个二极管和四个三极管搭接的桥型电机驱动电路, 控制四个三极管的 C,用单片机写出

程序.和四个二极管作用,还有 2 个接在电源上的电容的作用

答:

4

�

电容的作用:电源去耦电容,即降低电源对 GND 的交流阻抗。小容量的电容器是在高频情

况下降低阻抗作用,所以如果不配置在电路近邻,则电容器的引线增长,由于引线本身的阻

抗,电源的阻抗不能降低。

26. 一个数组,已排序.要求给出数组首位置,长度,要查找的数值.....

int find(char n,char *a,char len,char *nsr)

答:char find(char N,char *a,char len,char *snr)

// len<=127

{

char low,high,middle;

low = 0;

high = len - 1;

while(low <= high)

{

middle = (low + high) >> 1;

if(N == a[middle])

{

*snr = middle;

return 1;

}

else if(N > a[middle])

low = middle + 1;

else

high = middle - 1;

}

return 0;

}

27. 算法题:数据排序最优时间

28. 有关三极管饱和截止的,提出了输出电压与电流的要求,求两个电阻的取值

29. 用 555 定时器搭建的多谐振荡器,充放电时间由 555 中的三极管的截止与饱和来控制时

间不一样,第一问填很多空,5 分;第二问画参考电压,图像 3 分,第三问要求求充放

电时间了,也就是周期,三要素法记不住公式了,基本没戏了,12 分,这问做不上;

30. 用 51 单片机的 P0 口的三个端口来控制 74HC595(移位寄存器)来控制一个数码管从 0

显示到 9,要求肉眼能看清变化,数码管是共阴的

31. C 语言的数据结构题,FIFO

32. 给出一个数字逻辑电路,描述实现什么

功能,你是如何推测的。(是一个四输入

的优先编码器)

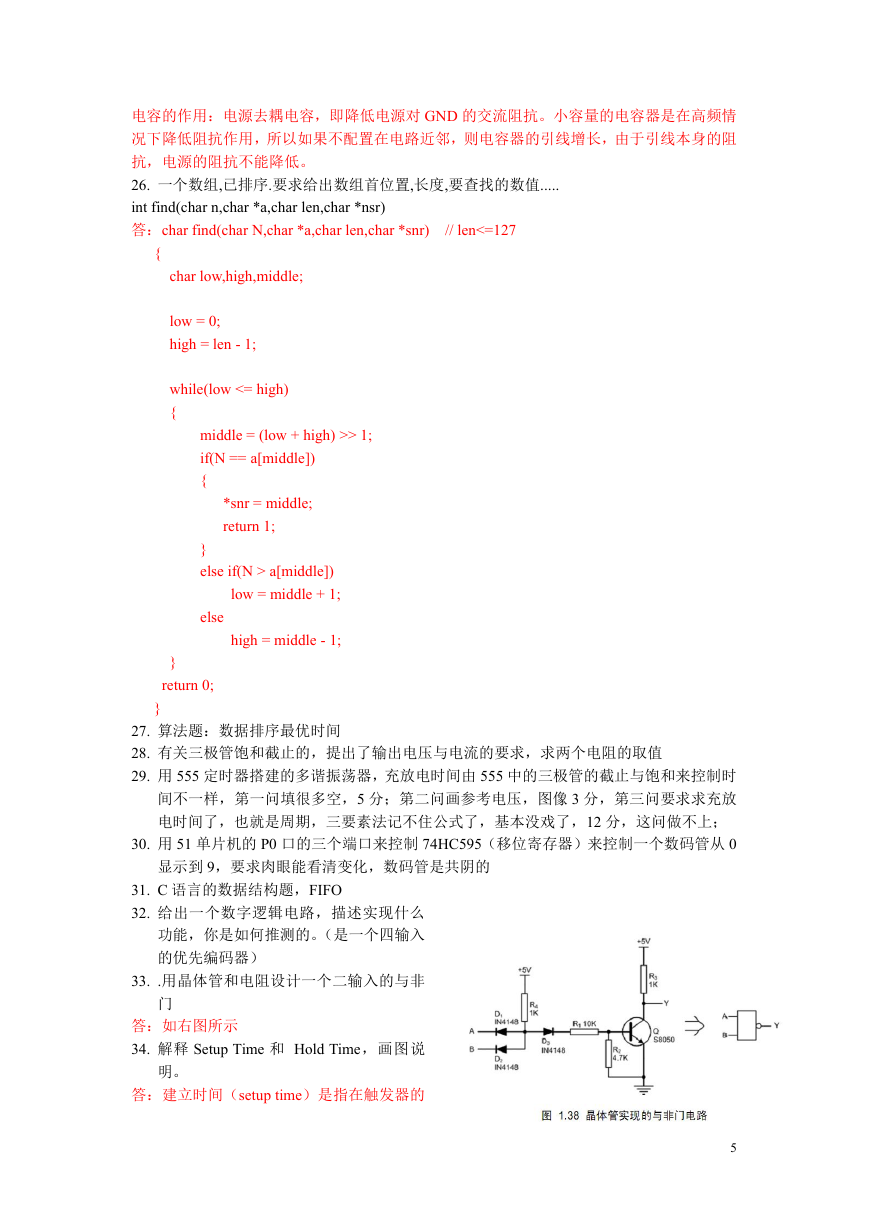

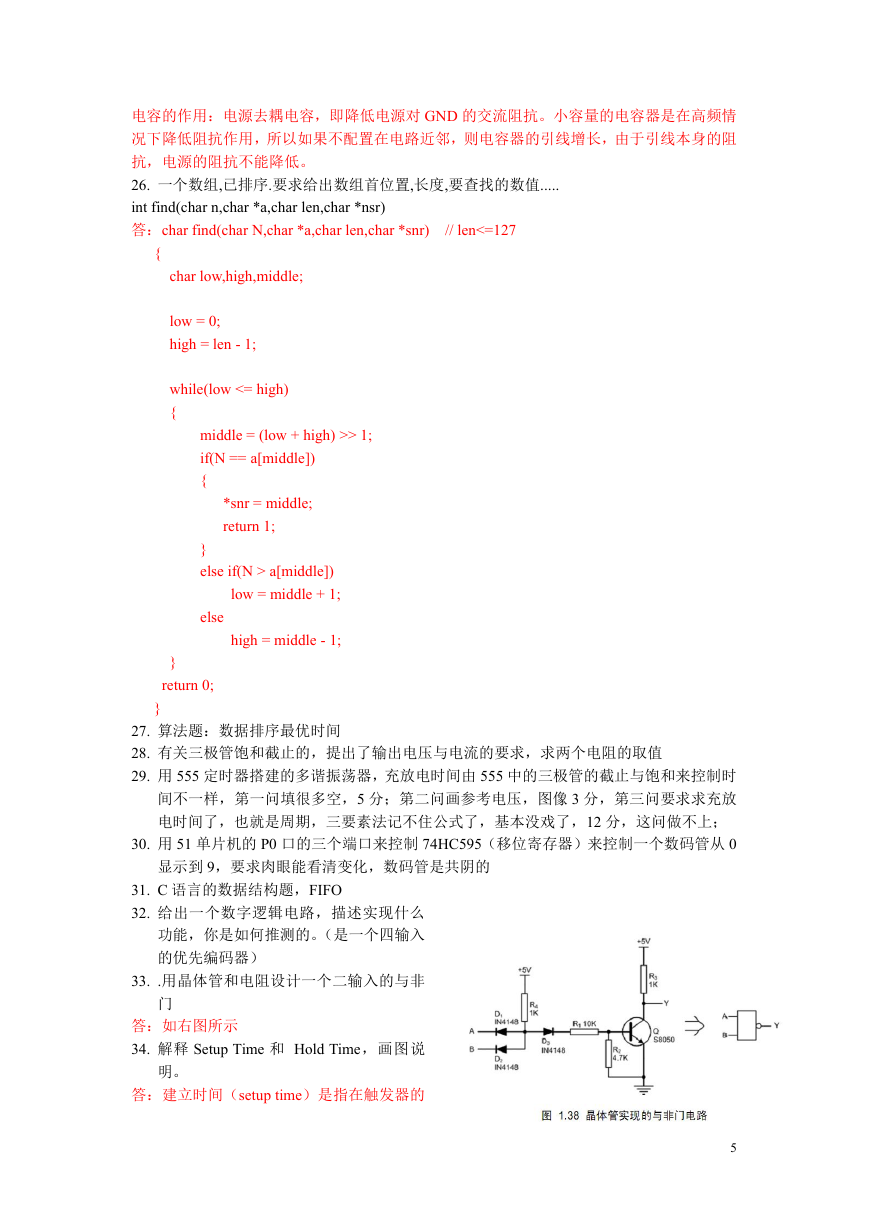

33. .用晶体管和电阻设计一个二输入的与非

门

答:如右图所示

34. 解释 Setup Time 和 Hold Time,画图说

明。

答:建立时间(setup time)是指在触发器的

5

�

时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时

钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,

数据稳定不变的时间, 如果保持时间不够,数据同样不能被打入触发器.数据稳定传输必须

满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

35. .亚稳态,有何解决办法。

答:即触发器无法在规定的时间内达到一个稳定的输出电平状态……;解决方法:用反应快

的触发器,降低时钟频率,改善时钟质量,引入同步机制等均可。

36. 关于 T 触发器的问题,还有几个与门和异或门,然后两个 T 触发器,让写状态方程,激

励方程,状态表,状态图,然后能实现什么功能

答:

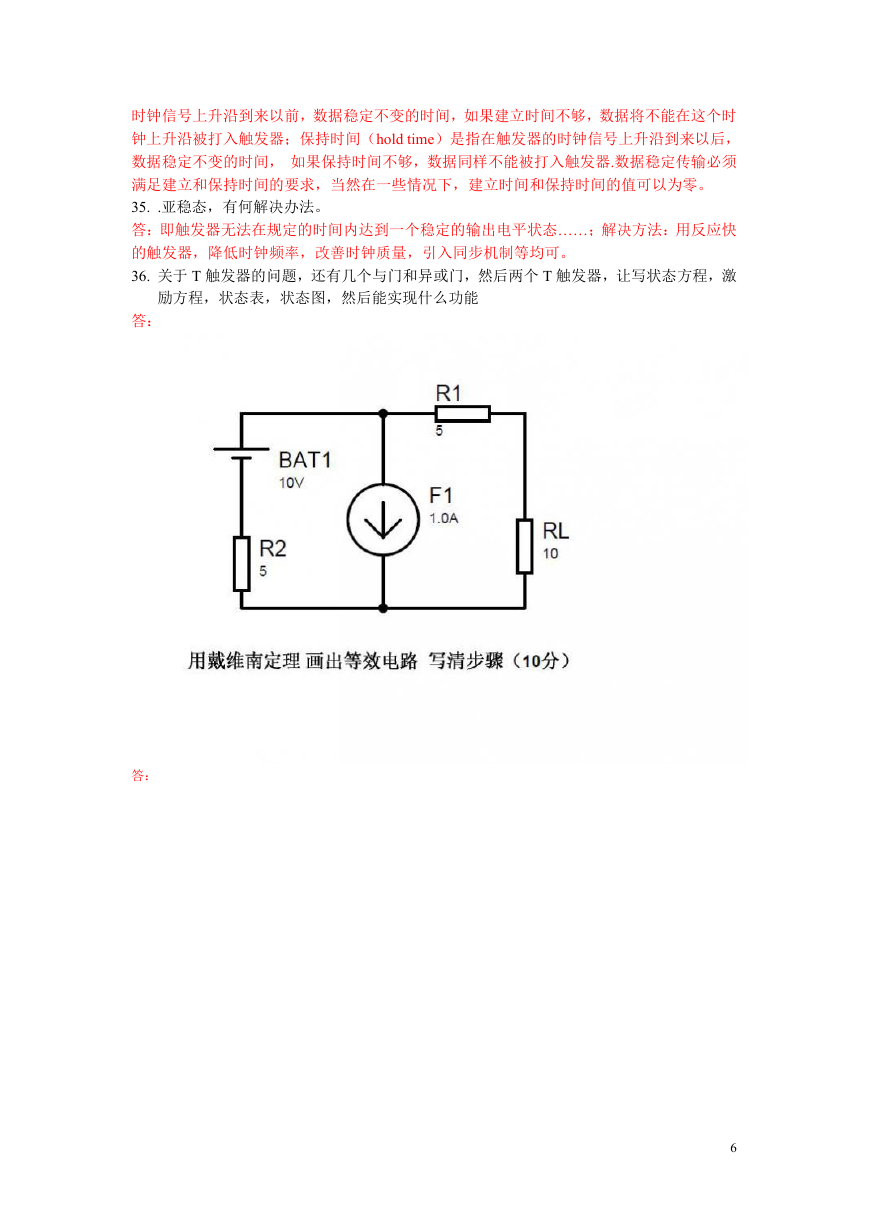

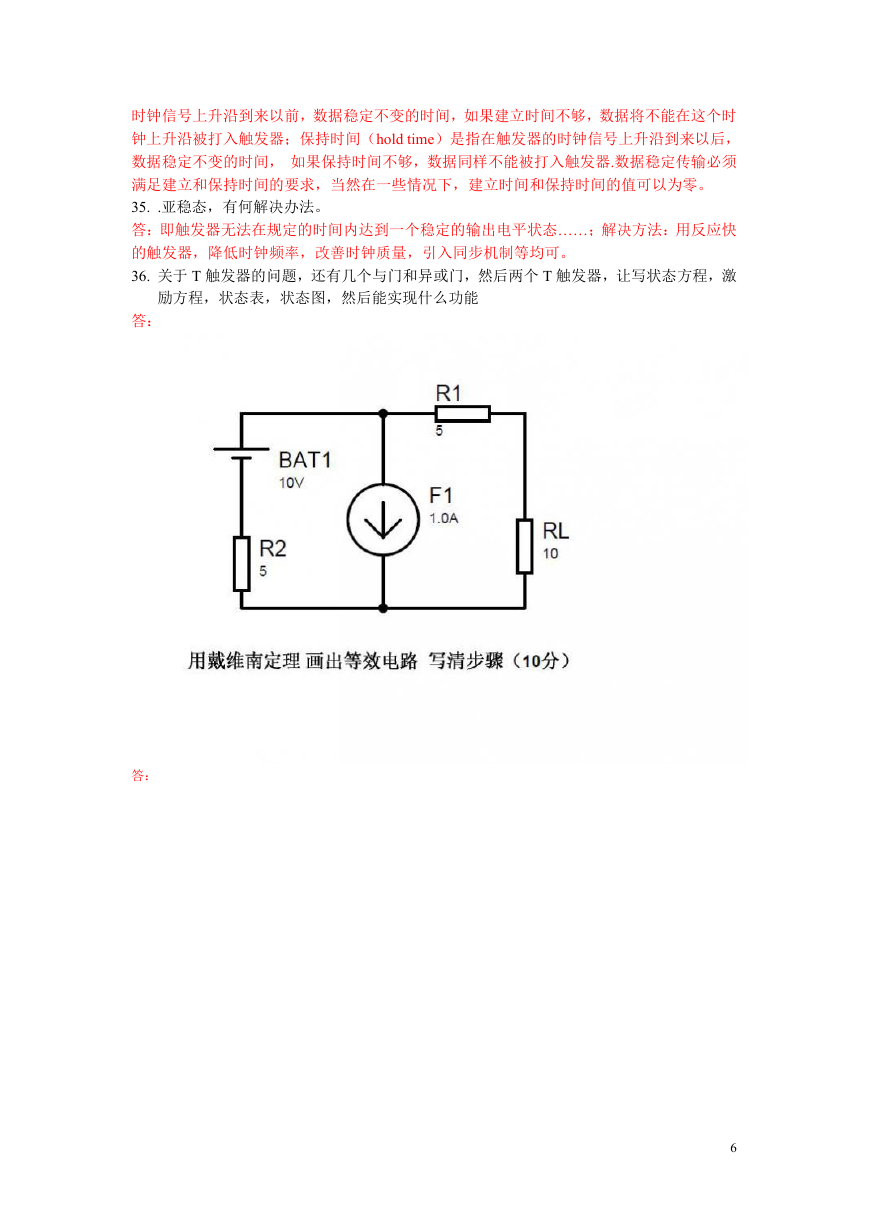

答:

6

�

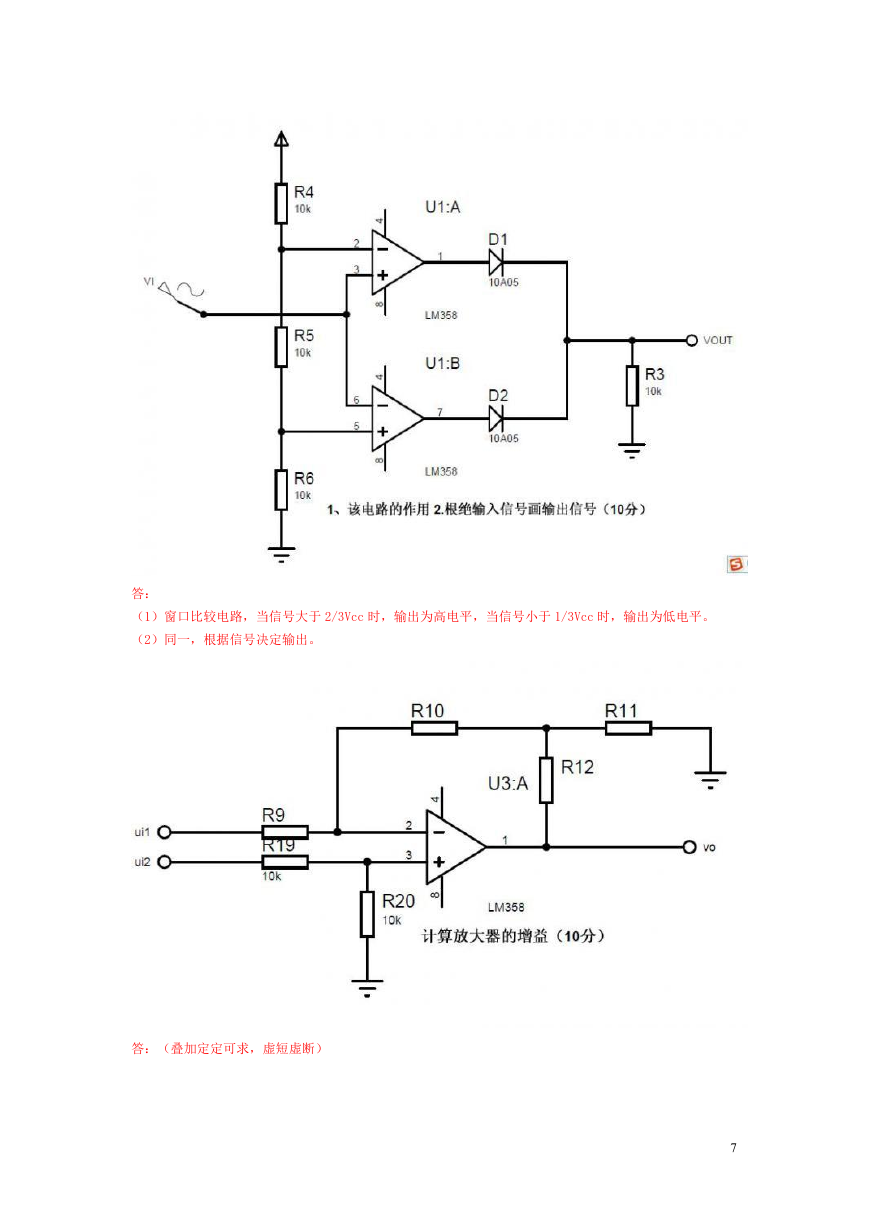

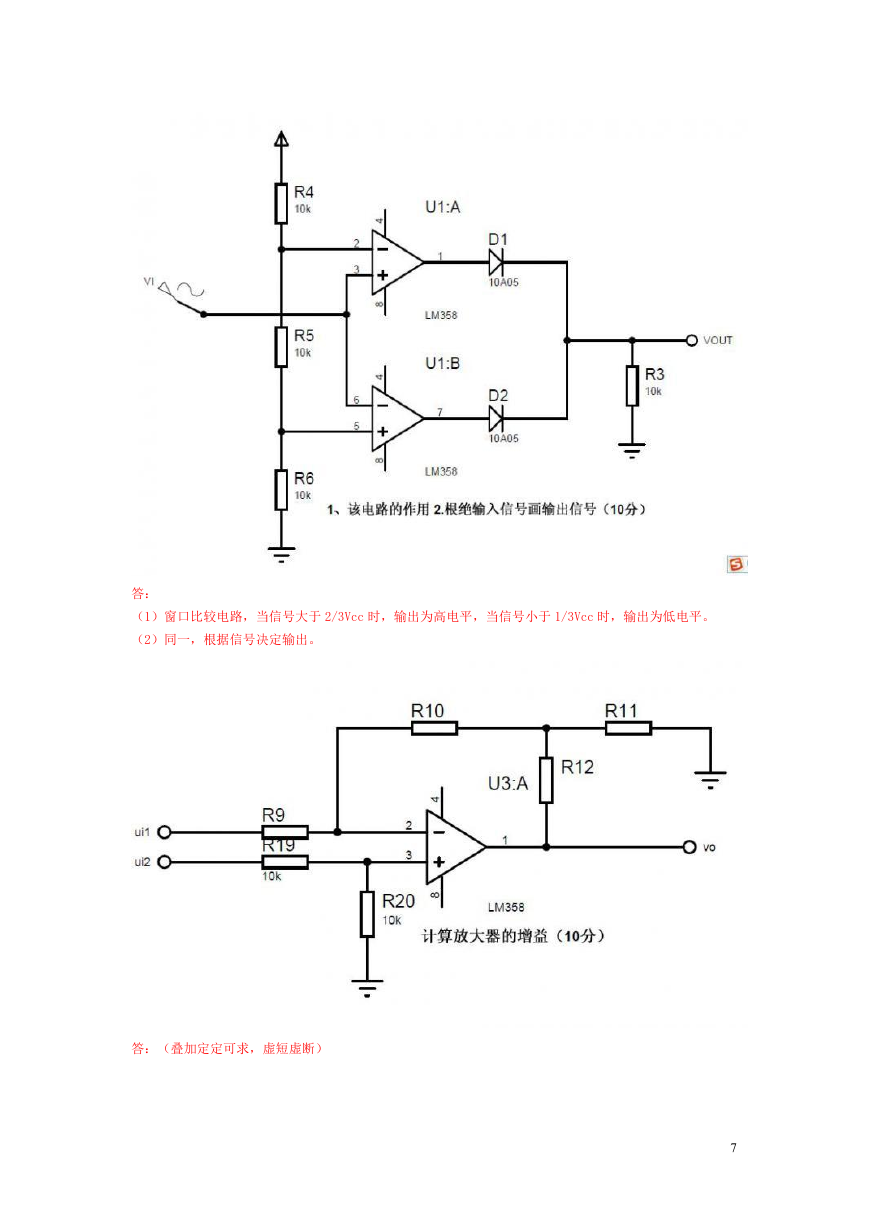

答:

(1)窗口比较电路,当信号大于 2/3Vcc 时,输出为高电平,当信号小于 1/3Vcc 时,输出为低电平。

(2)同一,根据信号决定输出。

答:(叠加定定可求,虚短虚断)

7

�

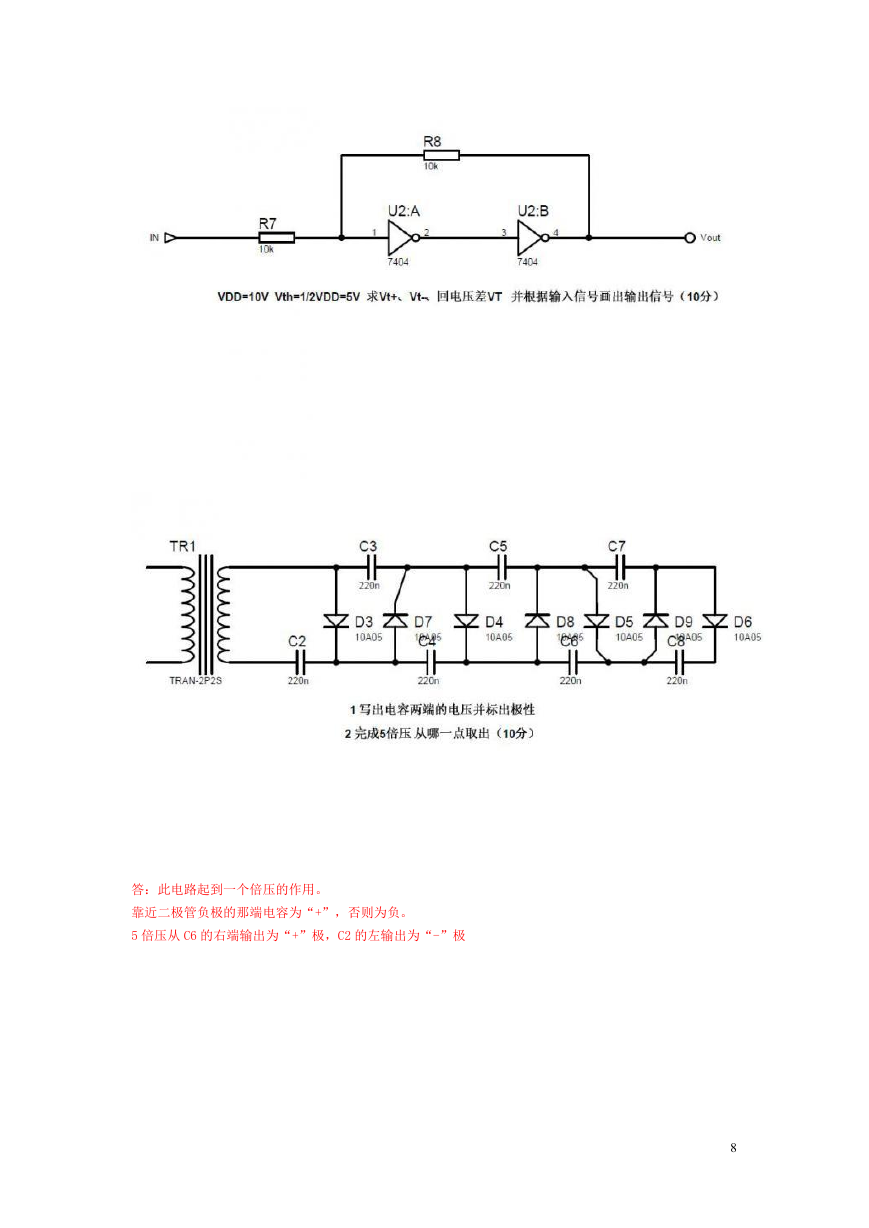

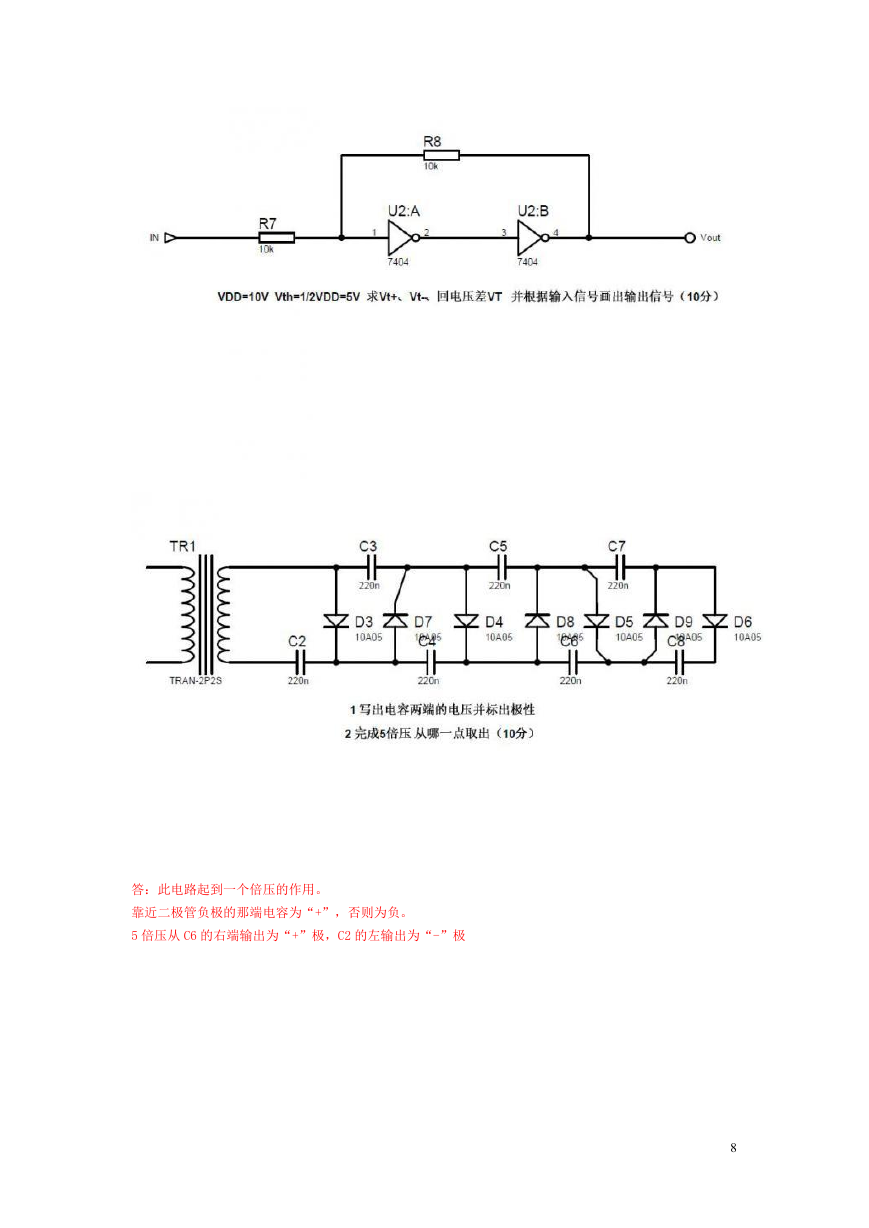

答:此电路起到一个倍压的作用。

靠近二极管负极的那端电容为“+”,否则为负。

5 倍压从 C6 的右端输出为“+”极,C2 的左输出为“-”极

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc