低功耗设计:https://www.cnblogs.com/IClearner/p/6912455.html

Tcl 和 DC 综合:https://www.cnblogs.com/IClearner/p/6660380.html

DC 教程:https://blog.csdn.net/steven_yan_2014/article/details/43445231

IC 设计中异步电路处理的若干问题:

https://blog.csdn.net/wordwarwordwar/article/details/79894843

FPGA 设计中时钟约束的重要性:

https://blog.csdn.net/u010203275/article/details/80569502

低功耗设计的几个思路:

https://blog.csdn.net/moon9999/article/details/77900306

verilog 二分频代码&verilog 三分频代码:

https://blog.csdn.net/hanghang121/article/details/20073985

建立时间和保持时间概念:

https://blog.csdn.net/wordwarwordwar/article/details/80160755

复位最佳方式:异步复位,同步释放:

https://blog.csdn.net/frank_wff/article/details/43226507

随笔分类 - 数字 IC(前端)/逻辑设计技巧:

https://www.cnblogs.com/IClearner/category/971863.html

IC 设计流程:https://blog.csdn.net/Burning_blade/article/details/81148352

计算机组成原理——总线的基本概念:

https://blog.csdn.net/dala_da/article/details/78650035

�

计算机体系结构期末复习题:

https://blog.csdn.net/igiphons/article/details/5650136

计算机体系结构:https://blog.csdn.net/he582754810/article/details/77862078

cordic 算法详解:https://blog.csdn.net/u010712012/article/details/77755567

ARM 获得 PC 指针为何 PC=PC+8:

https://blog.csdn.net/sddzycnqjn/article/details/7691534

MIPS 五级流水线:

https://blog.csdn.net/EckoTan/article/details/46533843?utm_source=blogxgw

z3

《大话处理器》连载——微架构(4) 史上最经典的 5 级流水线:

https://blog.csdn.net/muxiqingyang/article/details/6661417?utm_source=blog

xgwz0

Verilog 基础知识 7(FIFO 深度计算):

https://blog.csdn.net/times_poem/article/details/51917648

最常考的有:

1. 说到亚稳态,就不得不说 setup time 和 hold time。一定要掌握两种时

钟约束和分析时钟约束的方法。清楚四种路径(输入到输出,输入到寄

存器,寄存器到寄存器,寄存器到输出),并能找到关键路径。会计算

最高的工作频率。

�

2. sv 基础,包括@signal 触发和 wait(signal)的区别,事件触发,队列操

作,task 同步调度(fork ...join,fork ...join_any,fork ...join_none 的用法差

异)

3. 掌握一些常用的协议,如 I2C(能够根据提示用 verilog 实现),SRAM

协,AMBA(AHB),AXI

4. 在验证环境中,C 如何 access 和 dut 中寄存器,是如何联系的?Verilog

提供 VPI 接口,可以将 DUT 的层次结构开放给外部的 C/C++代码,而

systemverilog 提供了更好的接口:DPI.

5. 掌握一些常用的低功耗方法,如 clock gating(能画出电路结构图),了解

DVFS,多阈值电压技术,多电压技术

6. 组合逻辑输出需经过寄存器过滤毛刺,因此在三段式状态机的最后一段

通过时序逻辑来防止毛刺的出现

一、复位

1. 亚稳态:

时序不满足会导致亚稳态问题,比如建立时间、保持时间不满足会导致亚稳态的产

生,也就是触发器的输出处于不稳定的状态,亚稳态时间段内,数值可能为 0,可

能为 1,宗旨是不确定的。

亚稳态是可以传播的,例如本该是逻辑 0 的,却成了 1,之后亚稳态又传播下去,

导致逻辑错误,因此亚稳态时有害的。

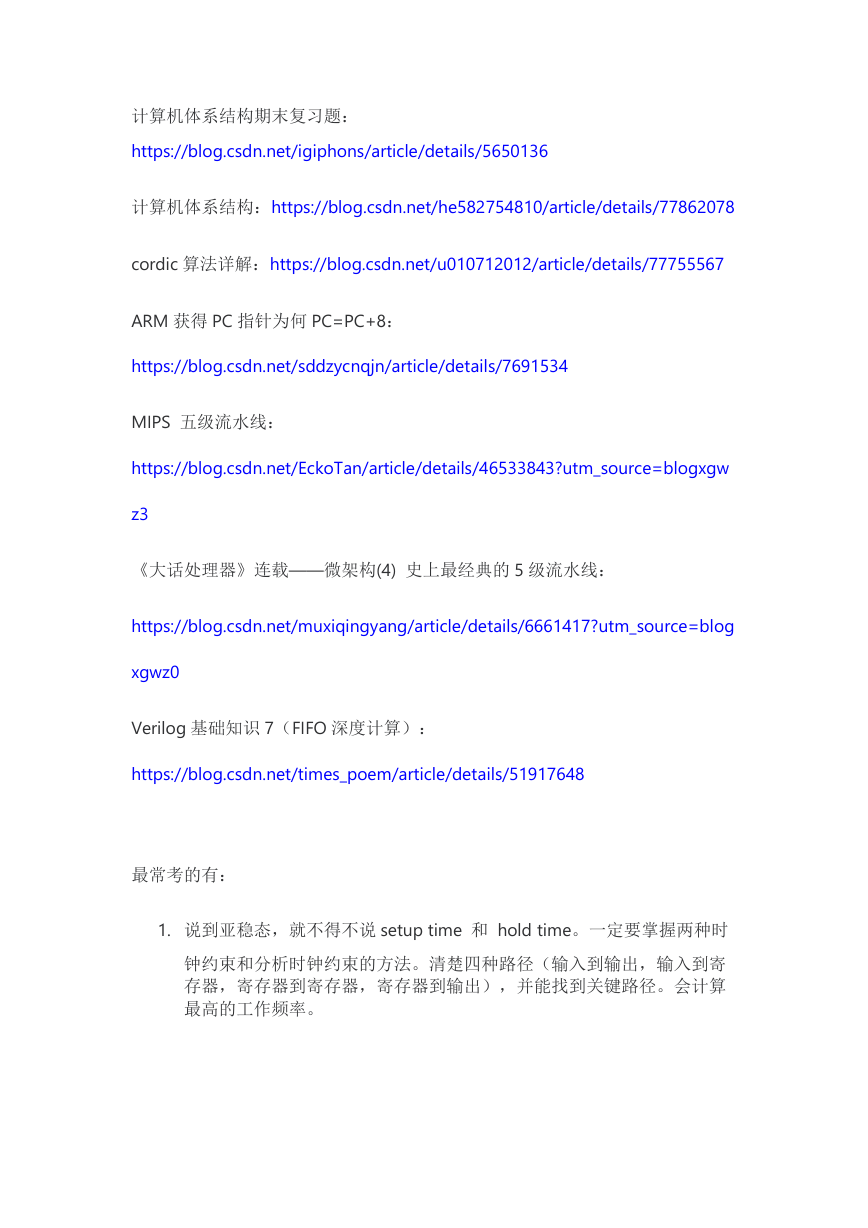

2. 恢复时间

异步复位存在恢复时间不满足而导致亚稳态问题。

复位恢复时间是指释放一个复位有效信号时,也即复位撤离,复位信号的有效状态

释放时刻和下一个时钟上升沿之间的时间。

�

异步复位的恢复时间要大于这一数值才能避免时序冲突。如果不满足恢复时间,则

会导致亚稳态的产生。

3. 异步复位

异步复位就是复位和时钟无关,电路只要检测到复位信号,就可以立即进入复位状

态,而不必考虑时钟问题。

异步复位的优点是复位信号识别方便,复位速度快,且 FPGA 以及 IC 内部的触发

器集成了异步复位端,所以比较节省资源,方便使用。

缺点就是容易受毛刺影响,异步复位必须满足恢复时间,否则会出现亚稳态。

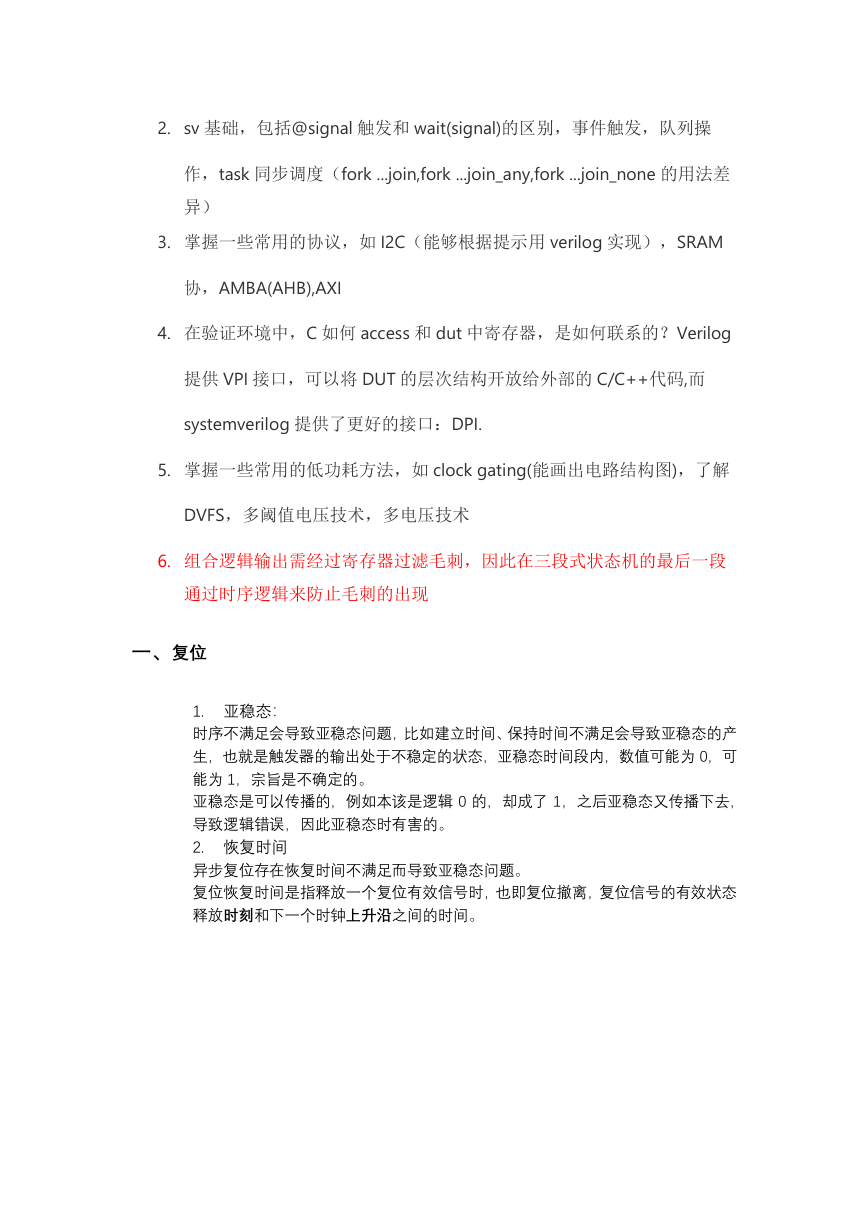

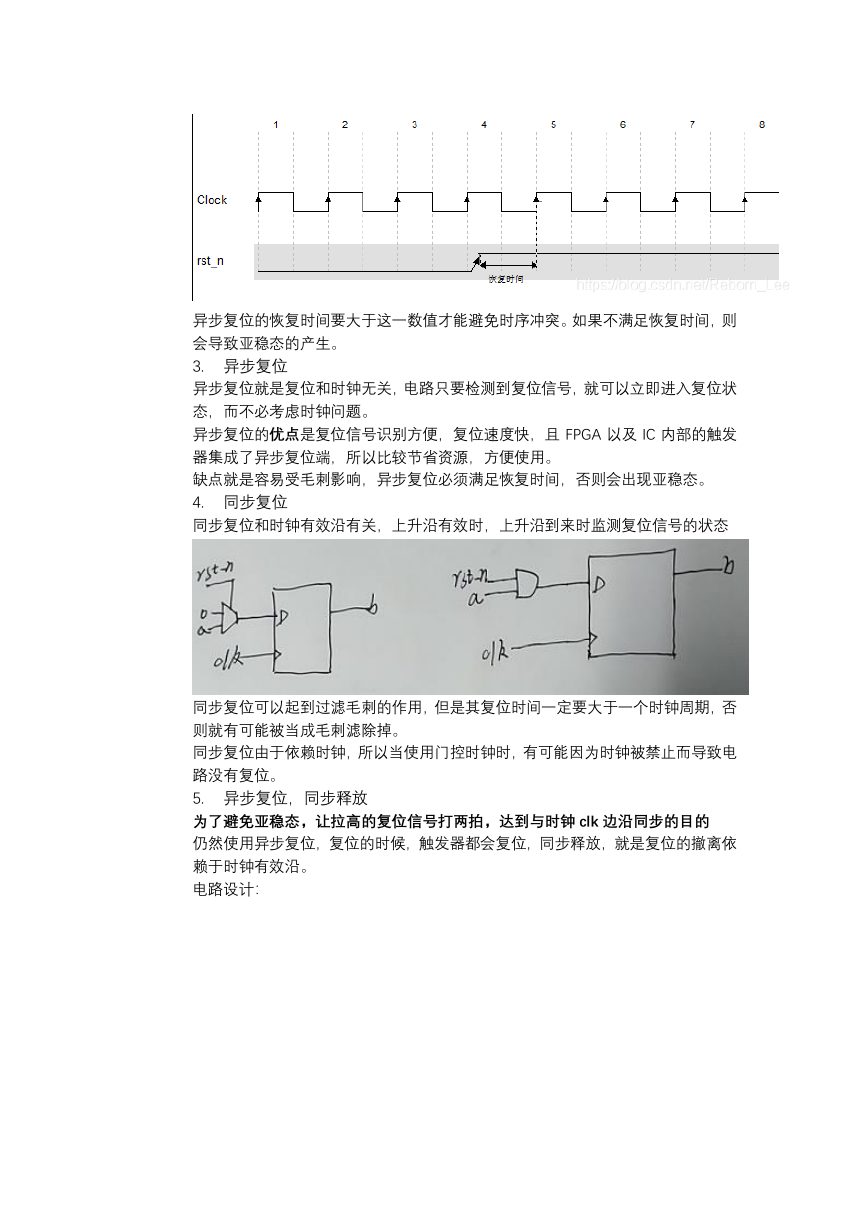

4. 同步复位

同步复位和时钟有效沿有关,上升沿有效时,上升沿到来时监测复位信号的状态

同步复位可以起到过滤毛刺的作用,但是其复位时间一定要大于一个时钟周期,否

则就有可能被当成毛刺滤除掉。

同步复位由于依赖时钟,所以当使用门控时钟时,有可能因为时钟被禁止而导致电

路没有复位。

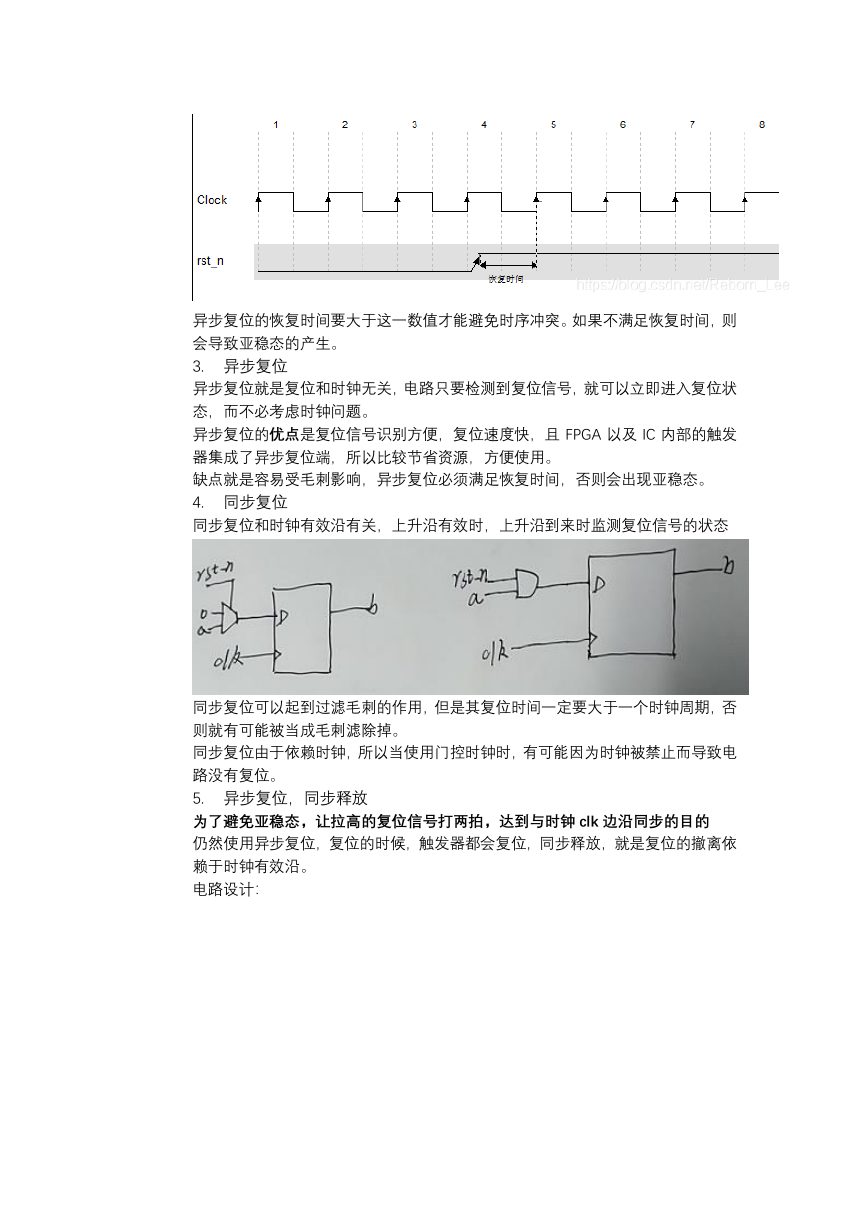

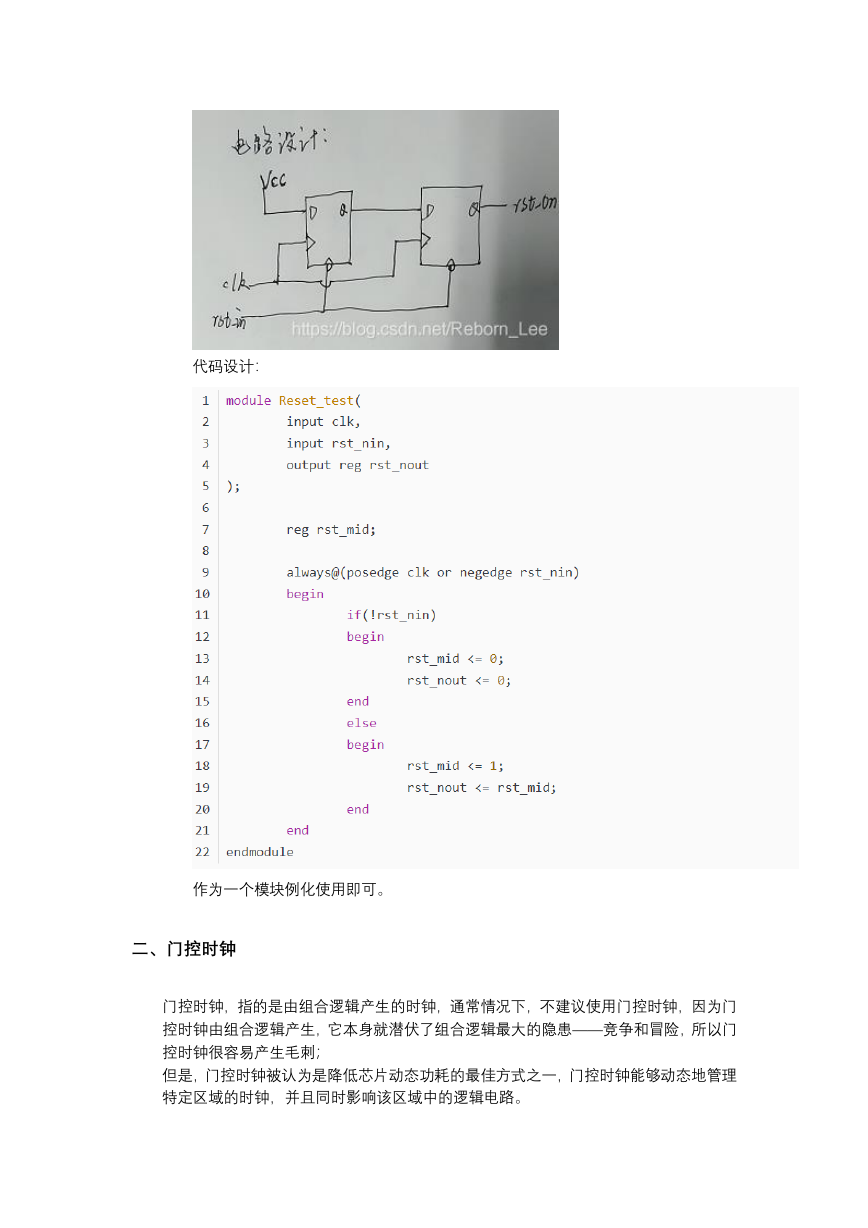

5. 异步复位,同步释放

为了避免亚稳态,让拉高的复位信号打两拍,达到与时钟 clk 边沿同步的目的

仍然使用异步复位,复位的时候,触发器都会复位,同步释放,就是复位的撤离依

赖于时钟有效沿。

电路设计:

�

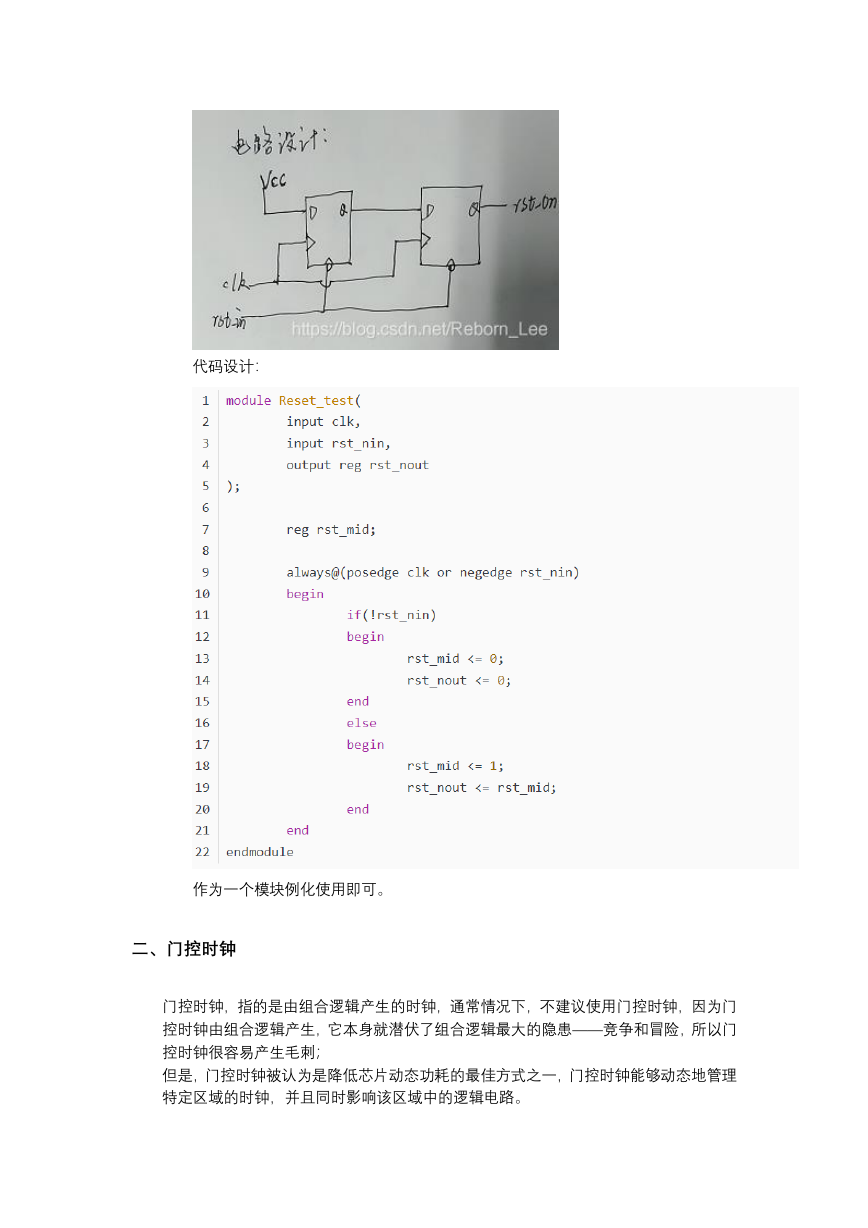

代码设计:

作为一个模块例化使用即可。

二、门控时钟

门控时钟,指的是由组合逻辑产生的时钟,通常情况下,不建议使用门控时钟,因为门

控时钟由组合逻辑产生,它本身就潜伏了组合逻辑最大的隐患——竞争和冒险,所以门

控时钟很容易产生毛刺;

但是,门控时钟被认为是降低芯片动态功耗的最佳方式之一,门控时钟能够动态地管理

特定区域的时钟,并且同时影响该区域中的逻辑电路。

�

6. 门控时钟低功耗原理

门控时钟也就是在使能信号有效的时候,把时钟打开,使能信号无效的时候,关闭

时钟,时钟关闭后,它所驱动的寄存器的输出就不会改变,因此就降低了动态功耗。

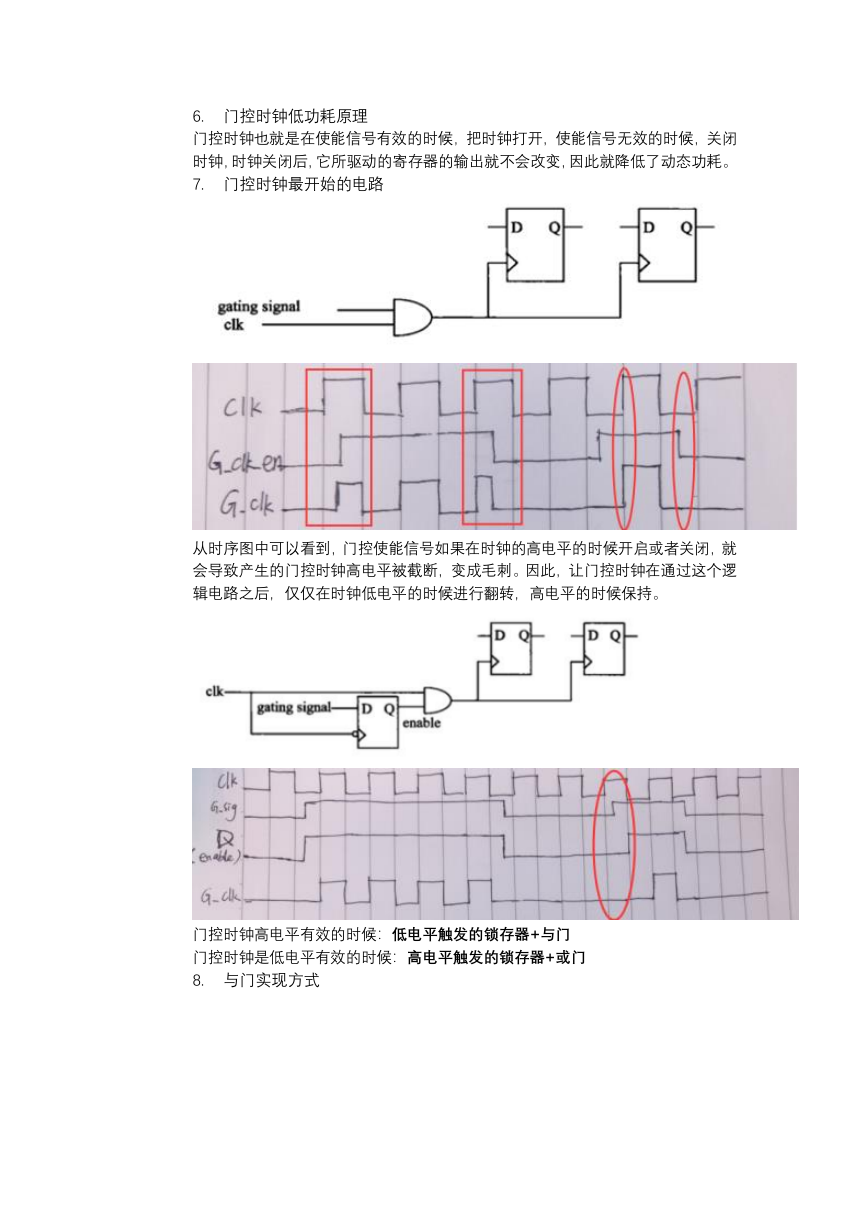

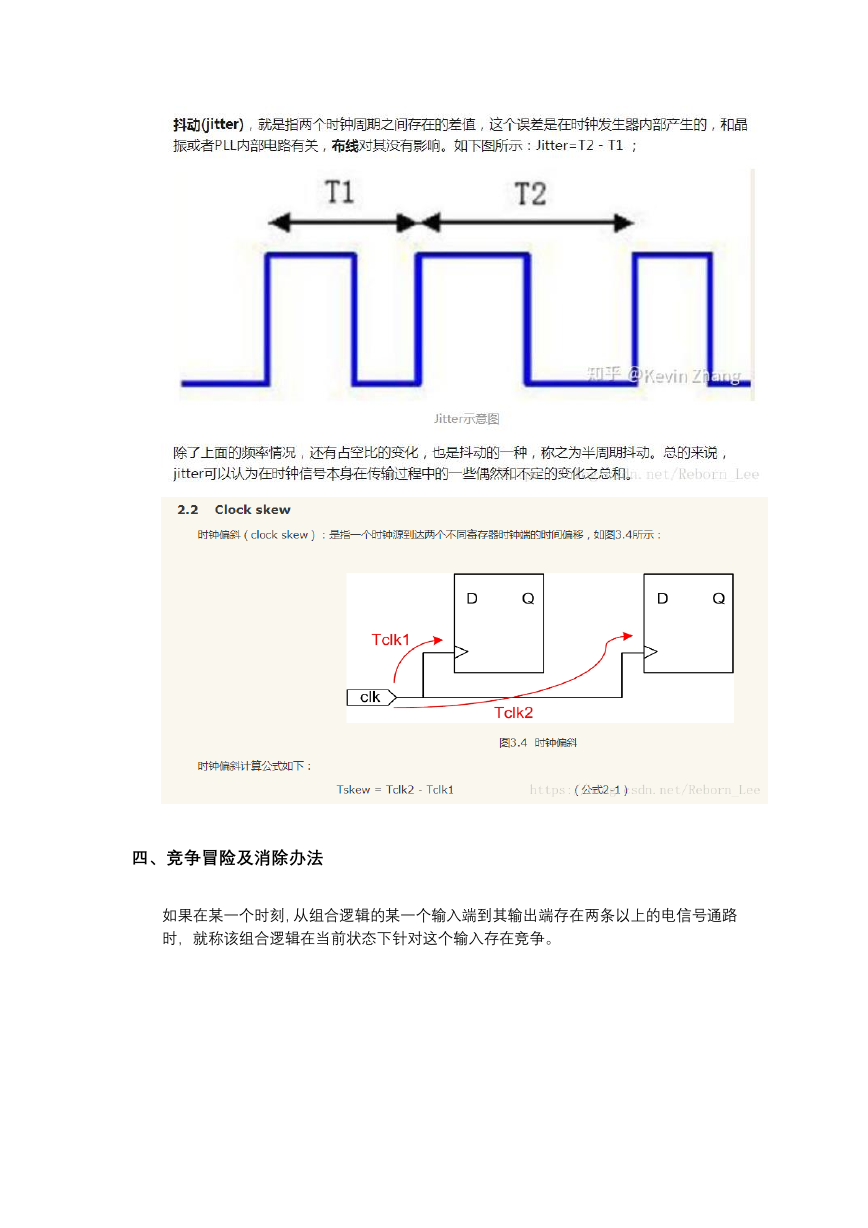

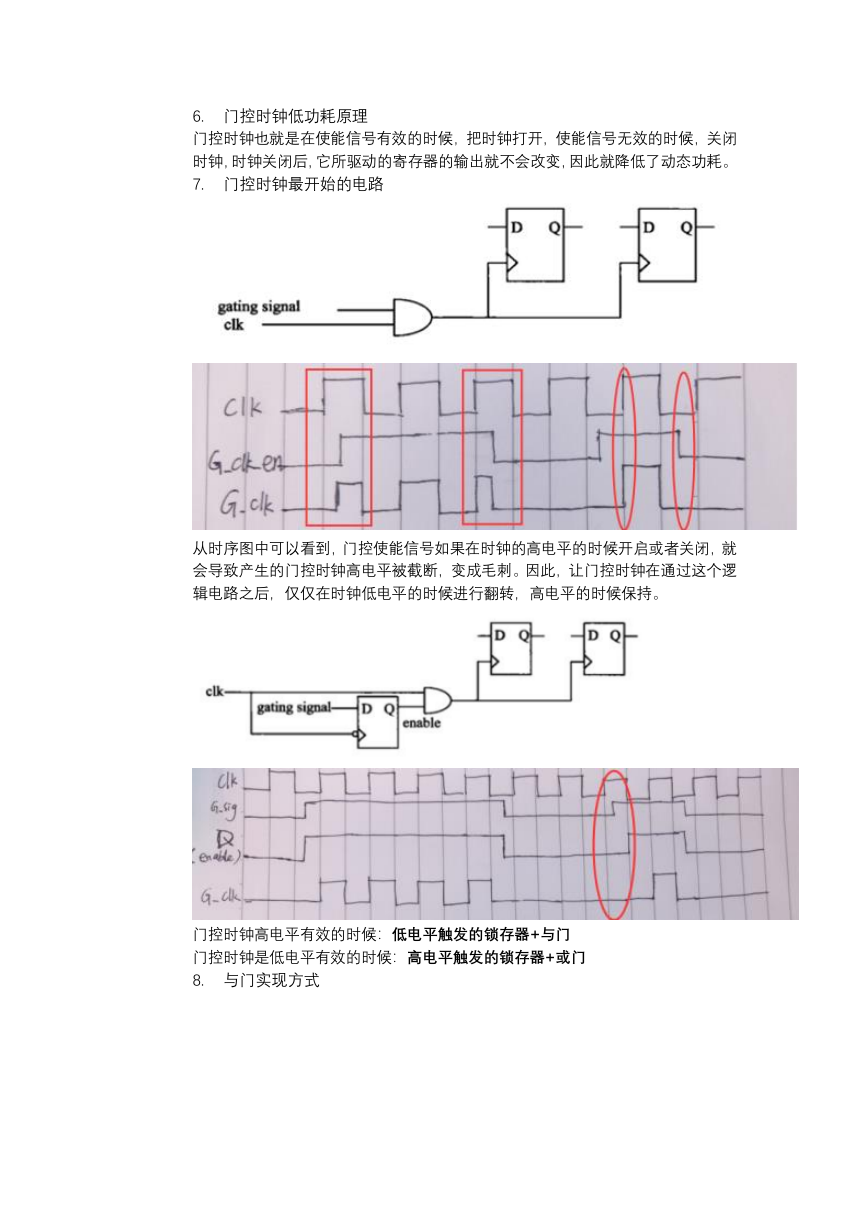

7. 门控时钟最开始的电路

从时序图中可以看到,门控使能信号如果在时钟的高电平的时候开启或者关闭,就

会导致产生的门控时钟高电平被截断,变成毛刺。因此,让门控时钟在通过这个逻

辑电路之后,仅仅在时钟低电平的时候进行翻转,高电平的时候保持。

门控时钟高电平有效的时候:低电平触发的锁存器+与门

门控时钟是低电平有效的时候:高电平触发的锁存器+或门

8. 与门实现方式

�

或门实现方式

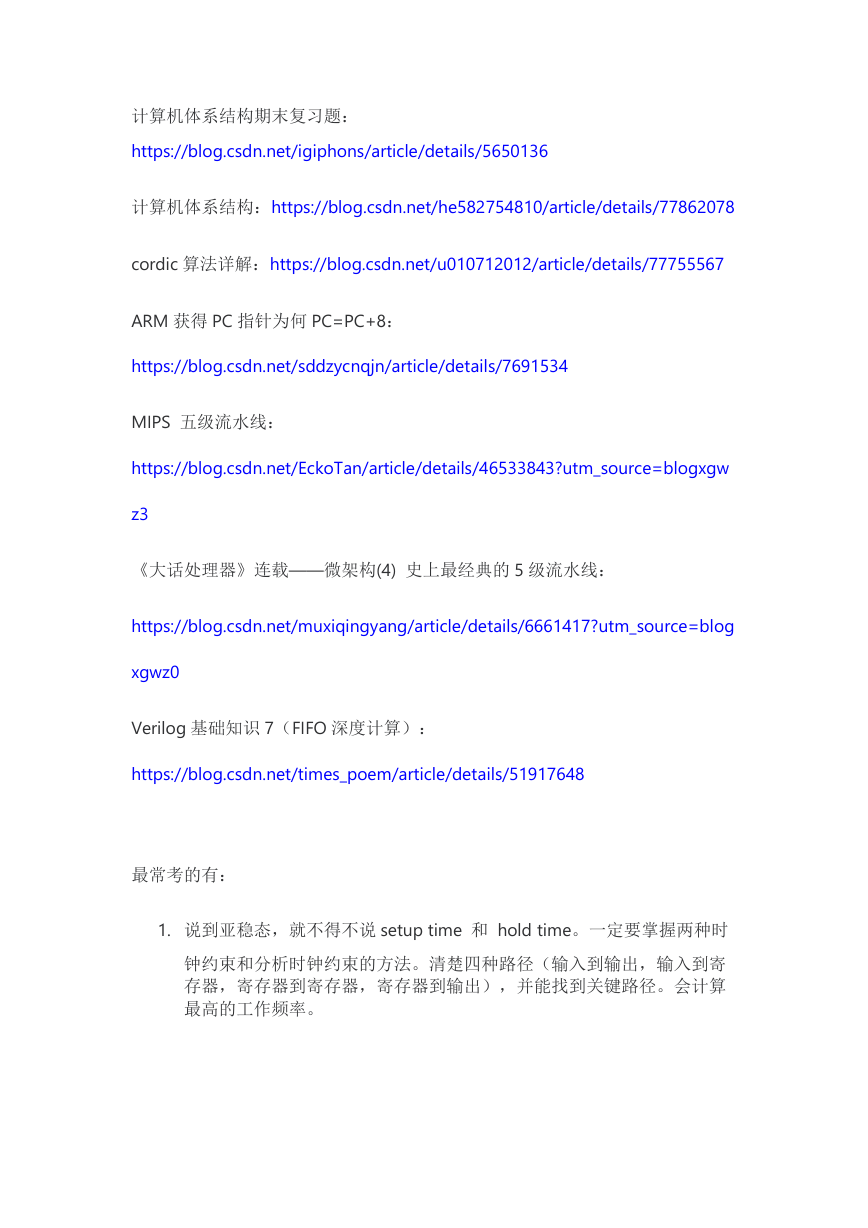

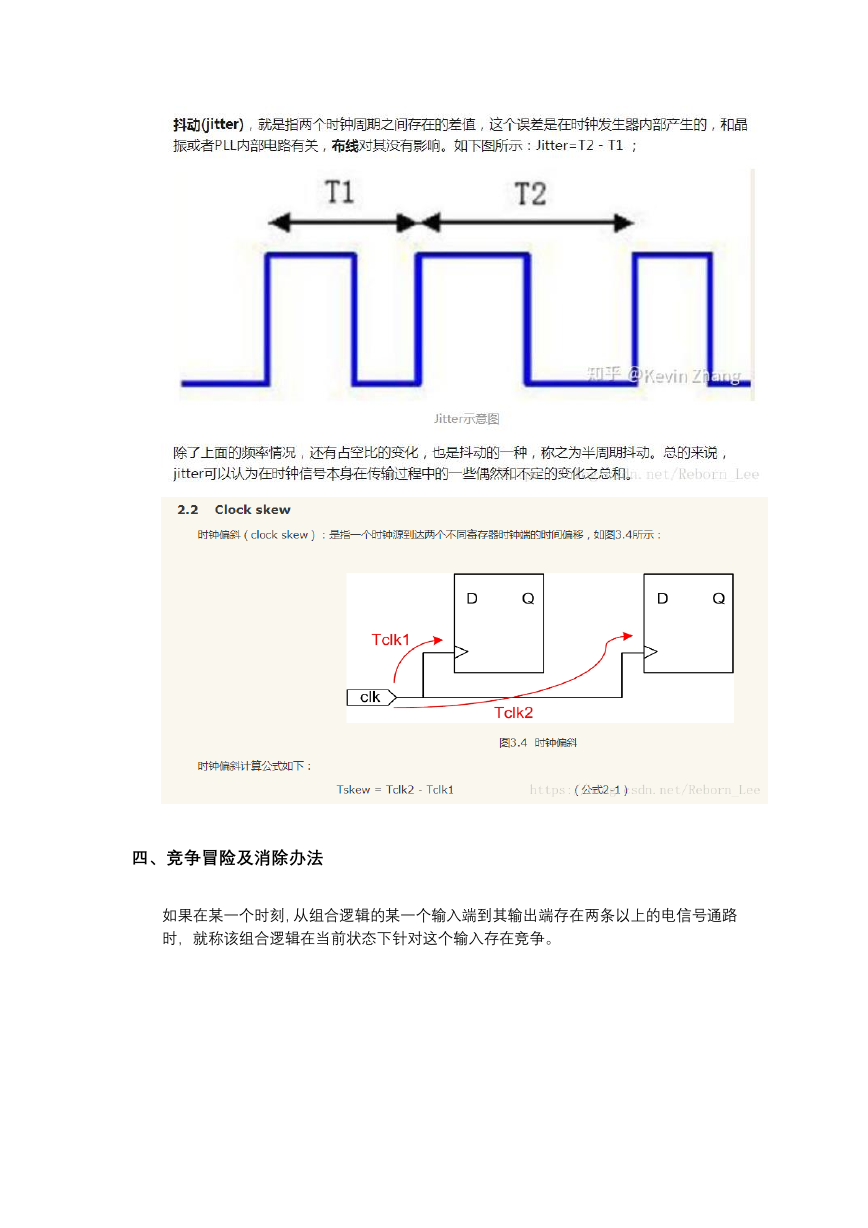

三、时钟抖动(Jitter)和时钟偏斜(Skew)

Skew 通常是时钟相位上的不确定,而 jitter 是时钟频率上的不确定。

由于市中院到达不同寄存器所经历的驱动和负载的不同,时钟边沿的位置有所差异,因

此就带来了 skew。

由于晶振本身稳定性,电源以及温度变化等造成时钟频率的变化,就是 jitter.

�

四、竞争冒险及消除办法

如果在某一个时刻,从组合逻辑的某一个输入端到其输出端存在两条以上的电信号通路

时,就称该组合逻辑在当前状态下针对这个输入存在竞争。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc