安徽农业科学,Journal of Anhui A西.Sci.2010,38(8):4355~4357

责任编辑常俊香责任校对卢瑶

循环冗余校验(CRC)编码器设计及FPGA实现

许正荣1,贾贤龙2,杨敦毅1

(1.安徽农业大学信息与计算机学院,安徽合肥,230036;2.合肥工业大学,安徽合肥,230009)

摘要介绍了循环冗余校验(CRC)编码器的设计及FPGA实现过程,采用原理图输入法对整个系统进行了编译和仿真,并在芯片

EPlK30TCl44.3中对该设计的核心部分进行了测试验证。结果表明,试验数据与理论分析结果完全相符。

关键词循环冗余校验(CRC);原理图输入;现场可编程门列阵(FPGA)

中图分类号11P302 文献标识码A

文章编号0517—661l(20LO)08—04355—03

Design and FPGA Implement of Cyclic Redllnd邺Check(CRC)Encoder

XU Zheng·rong et al(Colege of Information and Computer Engineering,Anhui Asrlcultural University,Hefei。Anhui 230036)

Abstract

11le process of design and FPGA implement of cychc redundancy check(CRC)encoder was introduced.偈e whole system was eonl.

piled and emulated with schematic diagram input method.and tlIe core part ofthe design was tested and verified in chip ofEPIl(=眦144—3.The

results showed that the tested data was completely conformed(with the theoretical analysis results.

Key words

Cyclic redundancy cheek(CRC);Schematic diagram input.;Fie王d programmable gate array(眦)

在数字农业中,计算机在数据通信中的应用越来越广

或运算一致,即以2为模的加法和减法是等价的。

泛。但由于农作物生长环境、数据传输距离等诸多因素的影

响.计算机与采集设备之间的通讯数据往往会发生元法预测

的错误。传输数据的检错方法一般包括奇偶码、汉明码和循

采用CRC校验时,发送方和接收方使用同一个生成多

项式g(x)(生成多项式是标准化的,可根据具体需要自行选

择),将最后的余数作为CRC校验码。其实现步骤如下:

环码,其中循环码的检错效果最好。而循环冗余校验(CRC:

(1)用Xn-k乘信息码m(茗);其中,n为发送码字长度,k

cyclic redundancy check)码(简称循环码或CRC码)的编码与

解码电路比较简单且容易实现,其在数据传输、通信系统的

设计、通信协议的分析及软件保护等方面常被用于实现差错

控制‘㈦3。

为信息码长度。

(2)用生成的多项式g(x)除xn-ltm(茗),得到商Q(茗),余

式r(x);

茗n-k,n(石)/g(省)=Q(x)+r(x)/g(x)。

作为正确性检验的方法,CRC以一个数据块为对象进行

(3)编出的码组为C(x)=n-km(石)+r(石)。

校验,可检验编码中多位出错的情况。CRC的计算实现方法

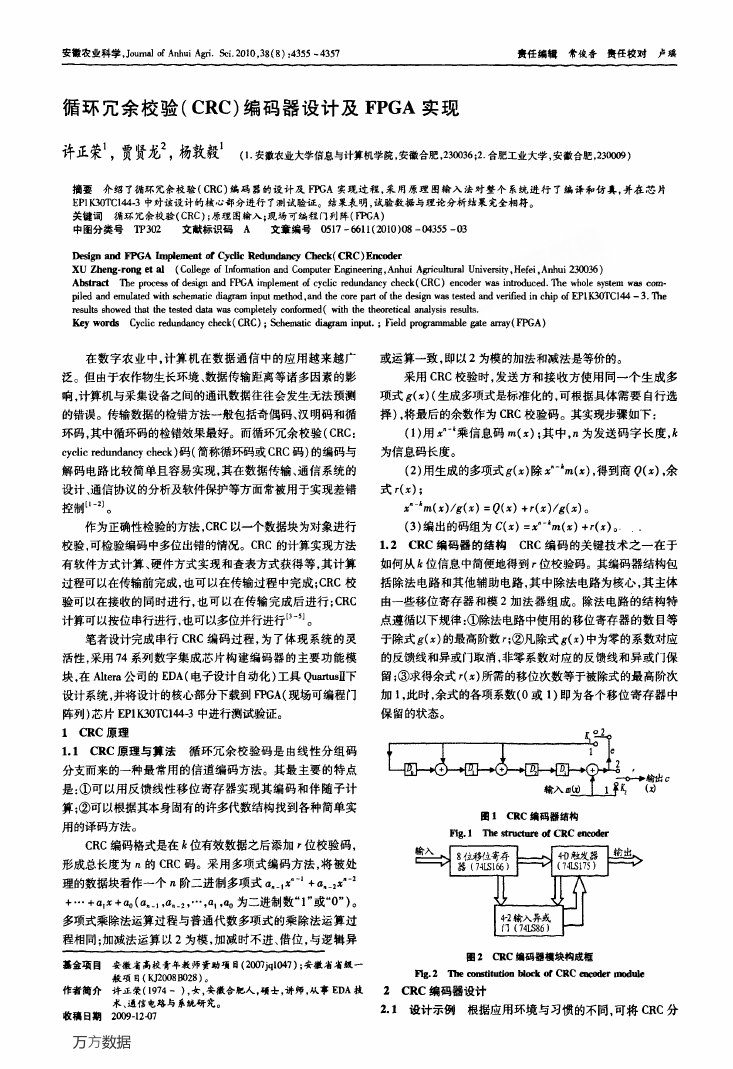

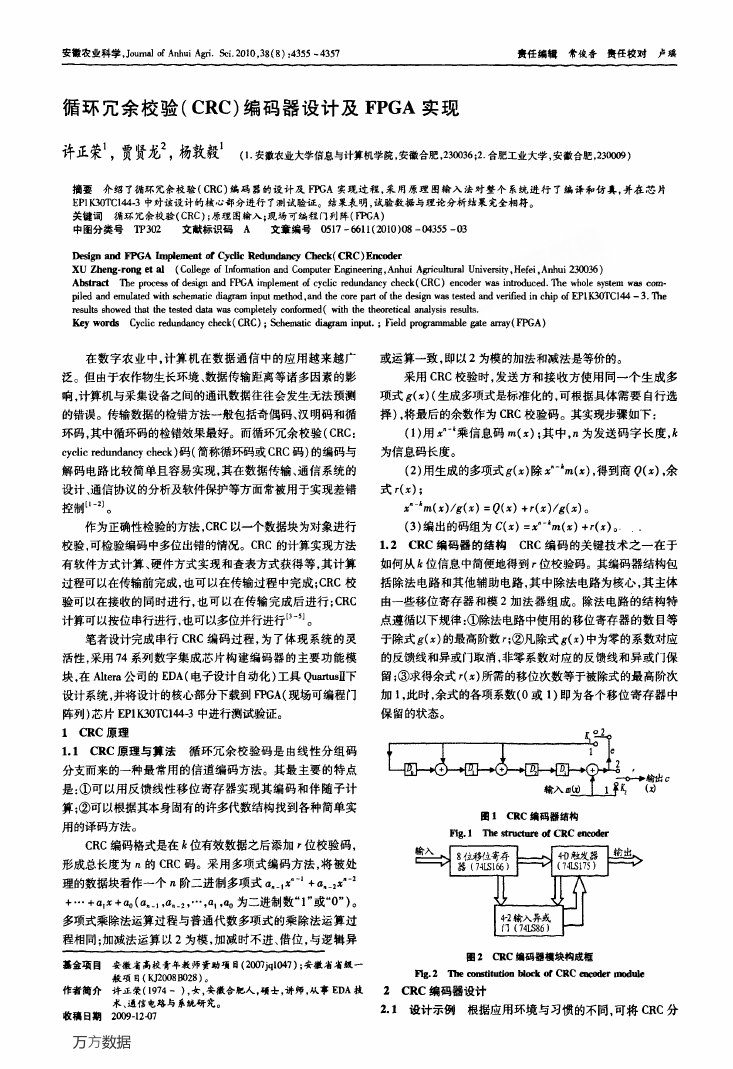

1.2 CRC编码器的结构 CRC编码的关键技术之一在于

有软件方式计算、硬件方式实现和查表方式获得等,其计算

如何从k位信息中简便地得到r位校验码。其编码器结构包

过程可以在传输前完成,也可以在传输过程中完成;CRC校

括除法电路和其他辅助电路,其中除法电路为核心,其主体

验可以在接收的同时进行,也可以在传输完成后进行;CRC

计算可以按位串行进行,也可以多位并行进行p。-。

由一些移位寄存器和模2加法器组成。除法电路的结构特

点遵循以下规律:①除法电路中使用的移位寄存器的数目等

笔者设计完成串行CRC编码过程,为了体现系统的灵

活性,采用74系列数字集成芯片构建编码器的主要功能模

于除式g(x)的最高阶数r;②凡除式g(x)中为零的系数对应

的反馈线和异或门取消,非零系数对应的反馈线和异或门保

块,在Ahera公司的EDA(电子设计自动化)工具QuartusH下

留;③求得余式r(x)所需的移位次数等于被除式的最高阶次

设计系统,并将设计的核心部分下载到FPGA(现场可编程门

阵列)芯片EPl K30TCl44-3中进行测试验证。

1 CRC原理

1.1

CRC原理与算法循环冗余校验码是由线性分组码

分支而来的一种最常用的信道编码方法。其最主要的特点

是:①可以用反馈线性移位寄存器实现其编码和伴随子计

算;②可以根据其本身固有的许多代数结构找到各种简单实

用的译码方法。

CRC编码格式是在J|}位有效数据之后添加r位校验码,

形成总长度为n的CRC码。采用多项式编码方法,将被处

加1,此时,余式的各项系数(0或1)即为各个移位寄存器中

保留的状态。

翰吐f

(对

圈1 CRC编码器结构

Fig.I

The structure of CRC ellcoder

理的数据块看作一个n阶二进制多项式an-I矿“+an_2毒”2

+…+at石+ao(a川,a。一2,…,nl,o,o为二进制数“1”或…0’)o

多项式乘除法运算过程与普通代数多项式的乘除法运算过

程相同;加减法运算以2为模,加减时不进、借位,与逻辑异

基金i;磊磊;i-;磊_;赢磊,;i省省舻

弛:m兰一篙嚣:删m躺$(KJ20088028

作者简介许正荣(1974一),女,安徽舍肥人,硕士,讲师,从事EDA技

T1‘‘ 11’‘口儿。’uuCluRuC00813028

g

… 、

一

,o—

2

CRC编码器设计

u u¨—^‘朋、一-‘、。‘‘_1’u‘1 1uuuul‘

甜盈口蜘术、通信电路与系统研究。

收稿日期

2.1设计示例根据应用环境与习惯的不同,可将CRC分200912-07

一

“”1…’1““4””。“1。“”1’…’1们

”

万方数据

�

4356

安徽农业科学

2010年

为以下几种标准:①CRC.12码;②CRC-16码;③CRC-CCrlT

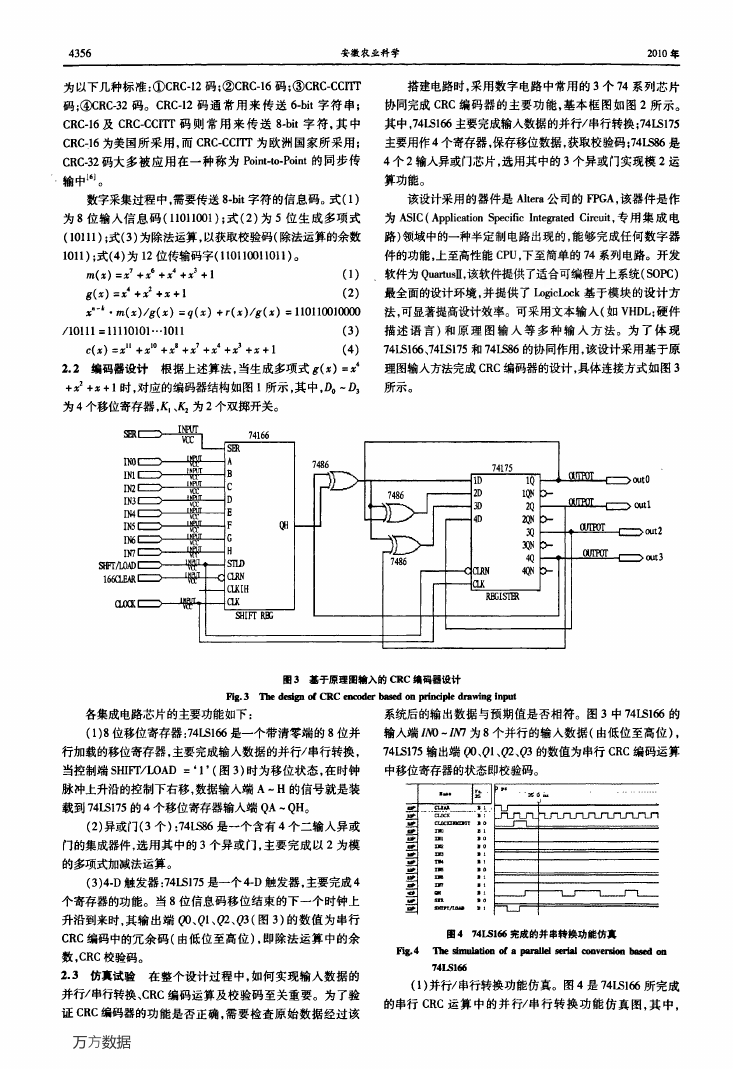

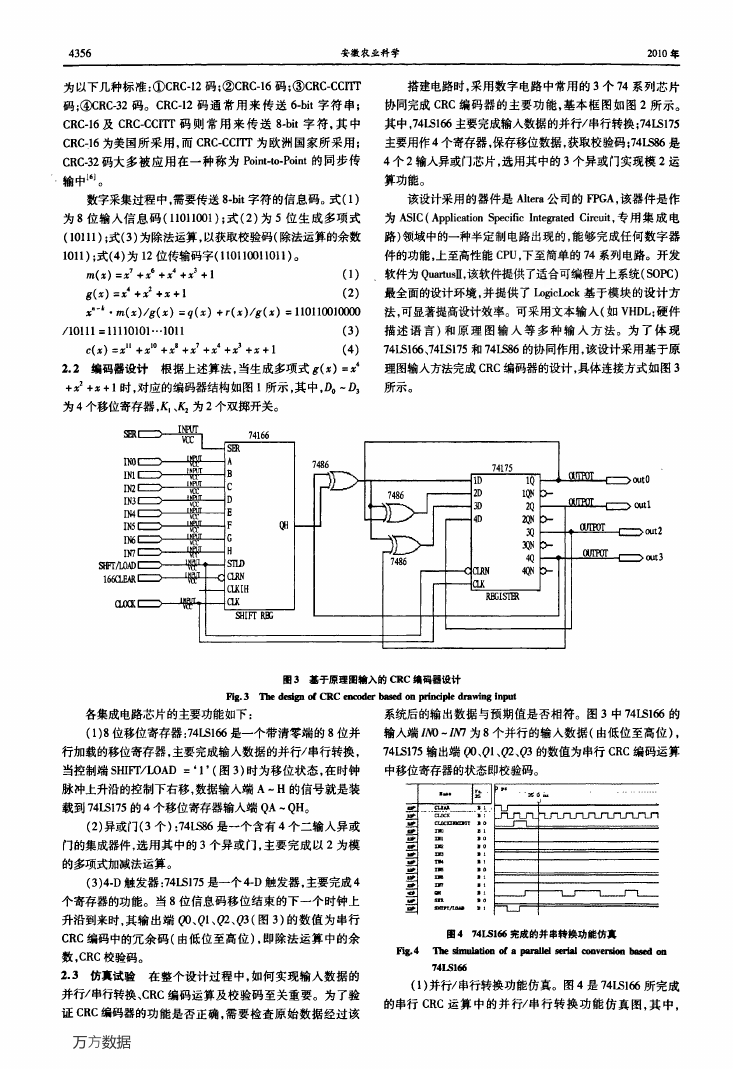

搭建电路时,采用数字电路中常用的3个74系列芯片

码;④cRc-32码。CRC.12码通常用来传送6-bit字符串;

CRC.16及CRC.CCIW码则常用来传送8.bit字符,其中

CRC.16为美国所采用,而CRC-CCITt为欧洲国家所采用;

协同完成CRC编码器的主要功能,基本框图如图2所示。

其中,74LSl66主要完成输入数据的并行/串行转换;74LSl75

主要用作4个寄存器,保存移位数据,获取校验码;74LS86是

CRC.32码大多被应用在一种称为Point—to·Point的同步传

4个2输入异或门芯片,选用其中的3个异或门实现模2运

输中归1。

算功能。

数字采集过程中,需要传送8-bit字符的信息码。式(1)

该设计采用的器件是Altera公司的FPGA,该器件是作

为8位输入信息码(11011001);式(2)为5位生成多项式

(10111);式(3)为除法运算,以获取校验码(除法运算的余数

为ASIC(Application Specific Integrated Circuit,专用集成电

路)领域中的一种半定制电路出现的,能够完成任何数字器

1011);式(4)为12位传输码字(110110011011)。

件的功能,上至高性能CPU,下至简单的74系列电路。开发

m(x)=茗7+省6+∥+菇3+l

g(x)=矿+菇。+菇+1

(1)

(2)

软件为QuartuslI,该软件提供了适合可编程片上系统(SOPC)

最全面的设计环境.并提供了Logicl_Dck基于模块的设计方

茹4’‘·re(x)/g(石)=q(x)+r(石)/g(髫)=110110010000

法,可显著提高设计效率。可采用文本输入(如VHDL:硬件

/10111=11110101…1011

c(菇)=并¨+茗10+X8+,+∥+菇3+耳+1

(3)

(4)

描述语言)和原理图输入等多种输入方法。为了体现

74LSl66、74LSl75和74LS86的协同作用,该设计采用基于原

2.2编码器设计根据上述算法,当生成多项式g(x)=矿

理图输入方法完成CRC编码器的设计,具体连接方式如图3

+舅2+茹+1时,对应的编码器结构如图l所示,其中,Do—D3

所示。

为4个移位寄存器,K、K为2个双掷开关。

骶硒

吼缸 肿眦眦肿鹏肺肺肿舳眦

图3基于原理图输入的CRC编码器设计

Fig.3 The design of CRC encoder based on principle drawing Input

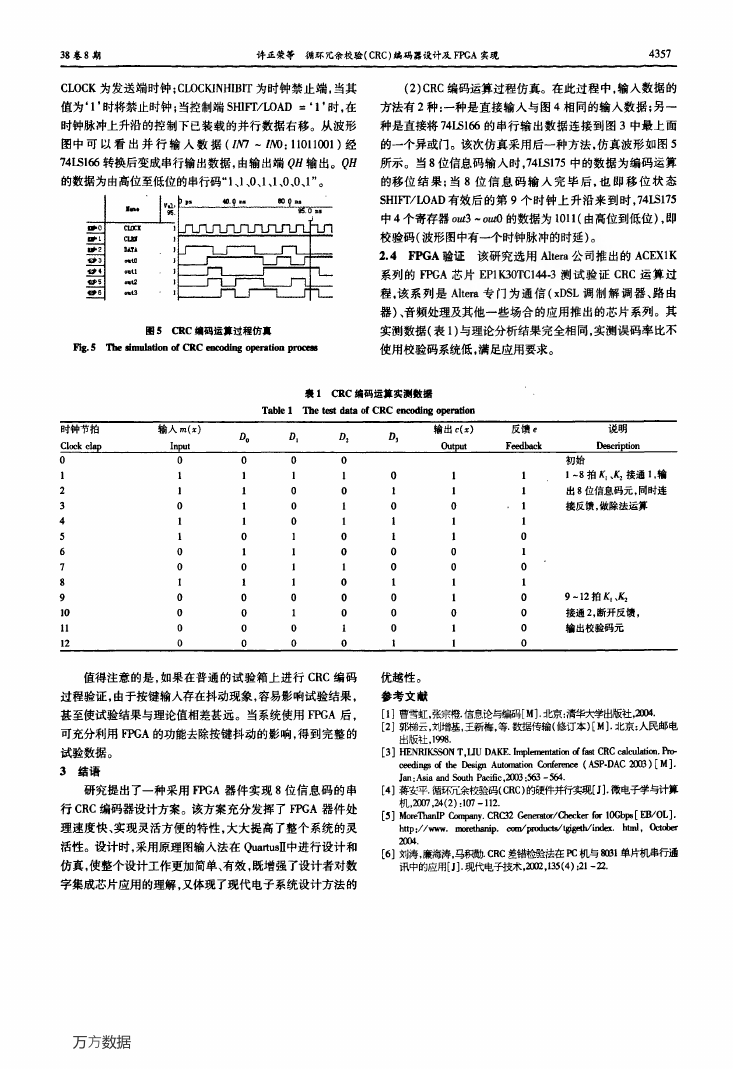

各集成电路芯片的主要功能如下:

(1)8位移位寄存器:74LSl66是一个带清零端的8位并

行加载的移位寄存器,主要完成输入数据的并行/串行转换,

系统后的输出数据与预期值是否相符。图3中74LSl66的

输入端/NO一胂为8个并行的输入数据(由低位至高位)。

74LSl75输出端Qo、口l、Q2、Q3的数值为串行CRC编码运算

当控制端SHIFT/LOAD=‘l’(图3)时为移位状态,在时钟

中移位寄存器的状态即校验码。

脉冲上升沿的控制下右移,数据输入端A—H的信号就是装

p,o

载到74L5175的4个移位寄存器输入端QA—QH。

(2)异或门(3个):74Ls86是一个含有4个二输入异或

门的集成器件,选用其中的3个异或门,主要完成以2为模

的多项式加减法运算。

(3)4.D触发器:74LSl75是一个4一D触发器。主要完成4

个寄存器的功能。当8位信息码移位结束的下一个时钟上

升沿到来时,其输出端Qo、Ql、Q2、Q3(图3)的数值为串行

CRC编码中的冗余码(由低位至高位),即除法运算中的余

数,CRC校验码。

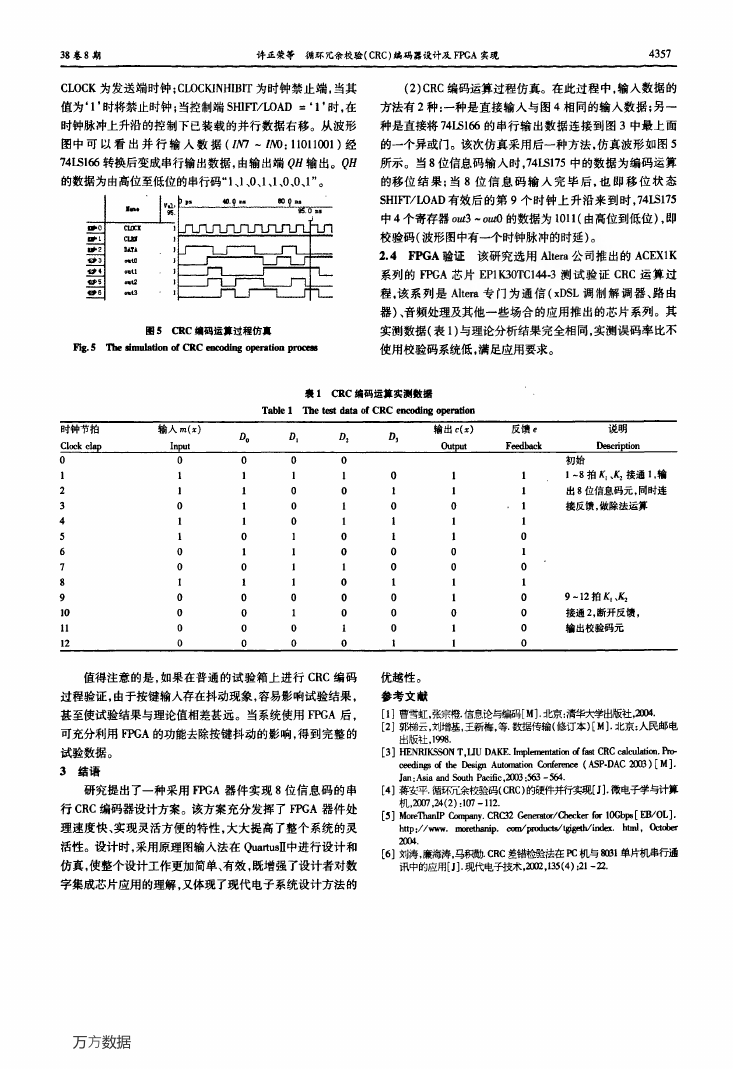

2.3仿真试验在整个设计过程中,如何实现输入数据的

并彳=秒串行转换、CRC编码运算及校验码至关重要。为了验

证CRC编码器的功能是否正确。需要检查原始数据经过该

万方数据

]J

n n n ]门广1几n几n n n n

广]

●●一 ——1广]广1

图4

74LSl66完成的并串转换功能仿真

晦4

The simulation 0f a Imrallel serial conversion based On

74LSl66

(1)并缈串行转换功能仿真。图4是74LSl66所完成

的串行CRC运算中的并行/串行转换功能仿真图,其中。

�

38卷8期

许正荣等循环冗余校验(CRC)编码器设计及F/V.A实现

4357

CLOCK为发送端时钟;CLOCKINHIBIT为时钟禁止端。当其

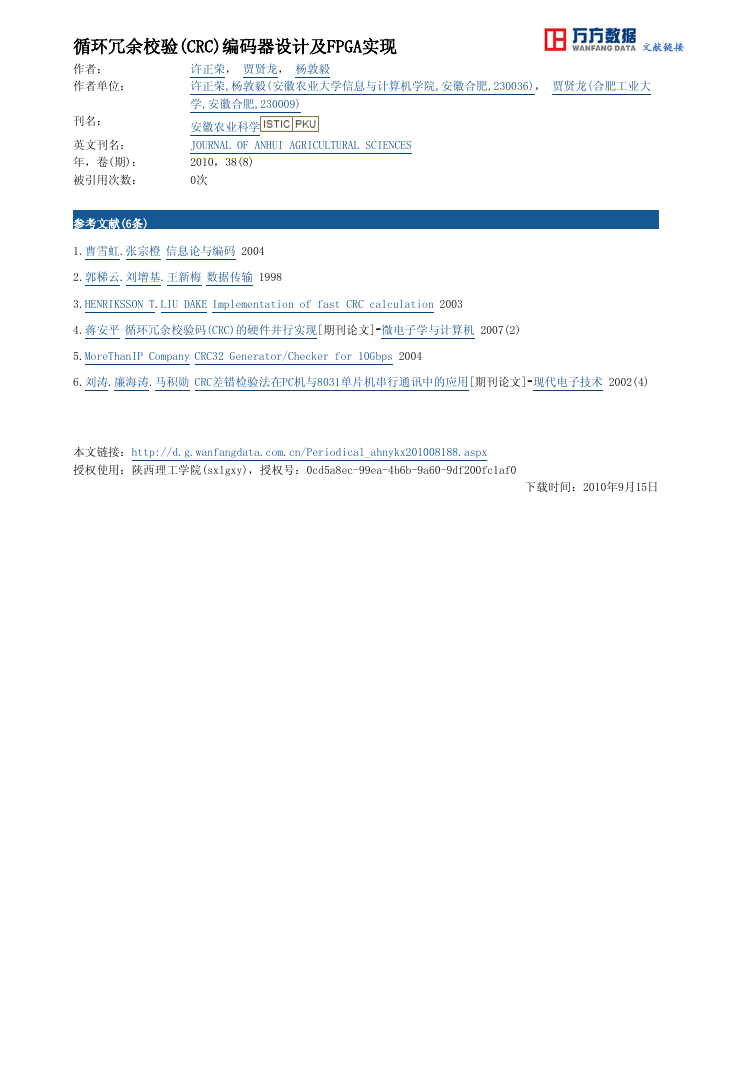

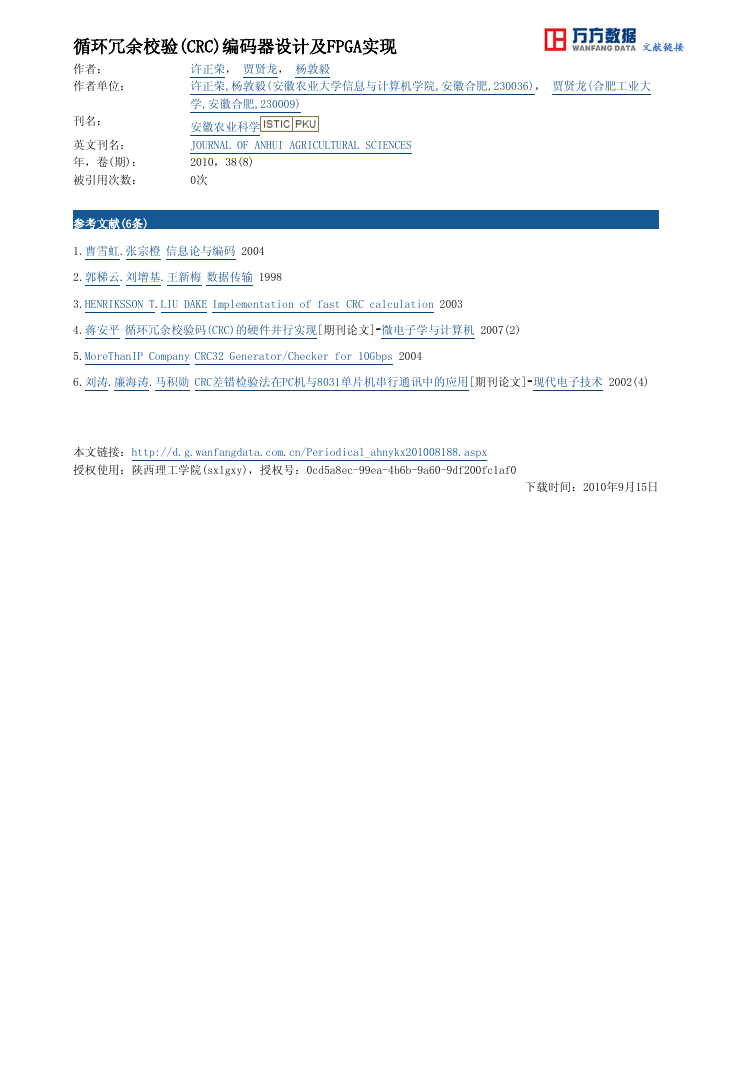

(2)CRC编码运算过程仿真。在此过程中,输入数据的

值为‘1’时将禁止时钟;当控制端SHIF'r/LOAD=‘1’时,在

方法有2种:一种是直接输入与图4相同的输入数据;另一

时钟脉冲上升沿的控制下已装载的并行数据右移。从波形

图中可以看出并行输入数据(肿一/NO:11011001)经

74LSl66转换后变成串行输出数据,由输出端QH输出。Q曰

种是直接将74LSl66的串行输出数据连接到图3中最上面

的一个异或门。该次仿真采用后一种方法,仿真波形如图5

所示。当8位信息码输入时,74LSl75中的数据为编码运算

的数据为由高位至低位的串行码“1、1、0,1、1、0.0、1”。

的移位结果;当8位信息码输入完毕后,也即移位状态

V.1,

镐

■-●

C眦

CU■

埘^

●■∞

坩U

州

●tt3

I’O

■一l

l●2

·‘多3

t,●

。t步5

·_’6

图5

CRC编码运算过程仿真

№.5 m simulation of CRC蛐eoaing operation process

SHIFT/LOAD有效后的第9个时钟上升沿来到时,74LSl75

中4个寄存器out3一out0的数据为101l(由高位到低位),即

校验码(波形图中有一个时钟脉冲的时延)。

2.4 FPGA验证该研究选用Altera公司推出的ACEXlK

系列的FPGA芯片EPlK30TCl44-3测试验证CRC运算过

程,该系列是Ahera专门为通信(xDSL调制解调器、路由

器)、音频处理及其他一些场合的应用推出的芯片系列。其

实测数据(表1)与理论分析结果完全相同,实测误码率比不

使用校验码系统低,满足应用要求。

时钟节拍

Clock clap

输入m(z)

Input

0

l

2

3

4

5

6

7

8

9

10

ll

0

1

1

O

l

1

0

0

l

0

0

0

襄1

CRC编码运算实测数据

Table 1 The test data of CRC encoding operation

Dl

92

D,

。

输出c(z)

Output

反馈e

Feedback

说明

D∞cri皿on

0

l

0

0

O

1

l

l

l

0

1

0

0

l

0

l

1

0

0

l

0

0

0

l

0

1

0

l

l

O

0

l

0

0

O

l

l

0

l

l

0

0

l

l

0

l

1

l

1

l

0

1

0

1

0

0

O

初始

l~8拍墨、岛接通1。输

出8位信息码元,同时连

接反馈,做除法运算

9一12拍K、K

接通2,断开反馈,

输出校验码元

Do

”

0

1

1

l

l

0

l

0

1

0

0

0

值得注意的是,如果在普通的试验箱上进行CRC编码

过程验证,由于按键输入存在抖动现象,容易影响试验结果,

甚至使试验结果与理论值相差甚远。当系统使用FPGA后,

可充分利用[]aGA的功能去除按键抖动的影响,得到完整的

试验数据。

3结语

优越性。

参考文献

[1]曹雪虹,张宗橙.信息论与编码[M].北京:清华大学出版社,2004.

[2]郭梯云,刘增基,王新梅,等.数据传输(修订本)[M].北京:人民邮电

出版社,1998.

[3]HENRIKSSON T。LIU DAKE.Implementation 0ffast CRC ealeuhtion.Pro-

ceedings of the Design Automation Confercn08(ASP-DAC 2003)[M]·

Jan:Asia and South Pacific。2003:563—564.

研究提出了一种采用FPGA器件实现8位信息码的串

[4]蒋安平.循环冗余校验码(cRc)的硬件并行实现【J].微电子学与计算

行CRC编码器设计方案。该方案充分发挥了FPGA器件处

理速度快、实现灵活方便的特性,大大提高了整个系统的灵

活性。设计时,采用原理图输入法在Quartusll中进行设计和

机,2007,24(2):107—112.

[5]MoreThanlP瞄砷any.CRC32 Generator/Checker for 10Gbps[EB/OL].

http://www.morethanip.佩n/p10dIlcts/tgigeth/ilId既.htral,October

2004.

[6]刘涛,廉海涛,马积勋.CRC差错检验法在Pc机与8031单片机串行通

仿真,使整个设计工作更加简单、有效,既增强了设计者对数

讯中的应用[J】.现代电子技术,2002,135(4):21—22.

字集成芯片应用的理解,又体现了现代电子系统设计方法的

万方数据

�

循环冗余校验(CRC)编码器设计及FPGA实现

作者:

许正荣, 贾贤龙, 杨敦毅

作者单位:

许正荣,杨敦毅(安徽农业大学信息与计算机学院,安徽合肥,230036), 贾贤龙(合肥工业大

刊名:

学,安徽合肥,230009)

安徽农业科学

英文刊名:

JOURNAL OF ANHUI AGRICULTURAL SCIENCES

年,卷(期):

2010,38(8)

0次

被引用次数:

参考文献(6条)

1.曹雪虹.张宗橙 信息论与编码 2004

2.郭梯云.刘增基.王新梅 数据传输 1998

3.HENRIKSSON T.LIU DAKE Implementation of fast CRC calculation 2003

4.蒋安平 循环冗余校验码(CRC)的硬件并行实现[期刊论文]-微电子学与计算机 2007(2)

5.MoreThanIP Company CRC32 Generator/Checker for 10Gbps 2004

6.刘涛.廉海涛.马积勋 CRC差错检验法在PC机与8031单片机串行通讯中的应用[期刊论文]-现代电子技术 2002(4)

本文链接:http://d.g.wanfangdata.com.cn/Periodical_ahnykx201008188.aspx

授权使用:陕西理工学院(sxlgxy),授权号:0cd5a8ec-99ea-4b6b-9a60-9df200fc1af0

下载时间:2010年9月15日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc