Microcomputer Applications Vol. 25, No.12, 2009 技术交流 微型电脑应用 2009 年第 25 卷第 12 期

文章编号:1007-757X(2009)12-0046-02

USB 协议的下的 PC 机与 FPGA 的数据通信

岳奎,刘少君,任参,黄道平

摘 要:该文通过设计 EZ_USB FX2 CY7C68013A 芯片与 FPGA 的接口电路,并基于 USB 协议来实现 PC 机与 FPGA 的数据

通信。详细介绍了固件程序的设计,Slave FIFO 模式特性,CY7C68013A 芯片的 Slave FIFO 接口模式与 FPGA 的电路设计

以及与 FPGA 接口的读写 VHDL 语言设计。

关键词:CY7C68013A;FPGA;固件;Slave FIFO;数据通信

中图分类号:TP335 文献标志码:A

0 引 言

当今越来越多的计算机外部设备追求高速度和高通用

性,为了满足用户的需求,USB 通用串行总线协议诞生了。

USB 是英文 Universal Serial Bus 的缩写,中文的含义是“通

用串行总线”。USB 是计算机与外部设备连接的一种新型

接口,具有连接方便,传输速率及可靠性高,能自动完成设

备的检测与设置以及无需单独供电等特点。因此 USB 技术

得到广泛的应用,越来越多的外部设备具有 USB 接口。

FPGA(现场可编程门阵列)是专用集成电路(ASIC)

中集成度最高的一种,用户可对 FPGA 内部的逻辑模块和

I/O 模块重新配置,以实现用户的逻辑,因而也被用于对 CPU

的模拟。用户对 FPGA 的编程数据放在 Flash 芯片中,通过

上电加载到 FPGA 中,对其进行初始化。也可在线对其编程,

实现系统在线重构,这一特性可以构建一个根据计算任务不

同而实时定制的 CPU,这是当今研究的热门领域。

本文利用 EZ_USB FX2 CY7C68013A 芯片与 Cyclone

公司的 EP1C6Q240C8 FPGA 设计电路来实现 PC 机与外部

设备 FPGA 的 USB 高速数据通信。

1.系统的整体设计

(SIE)、增强型 8051、8.5KB 的 RAM、4KB 的 FIFO 存储

器、I/O 口、数据总线、地址总线、I2C 控制器和通用可编

程接口(GPIF)。

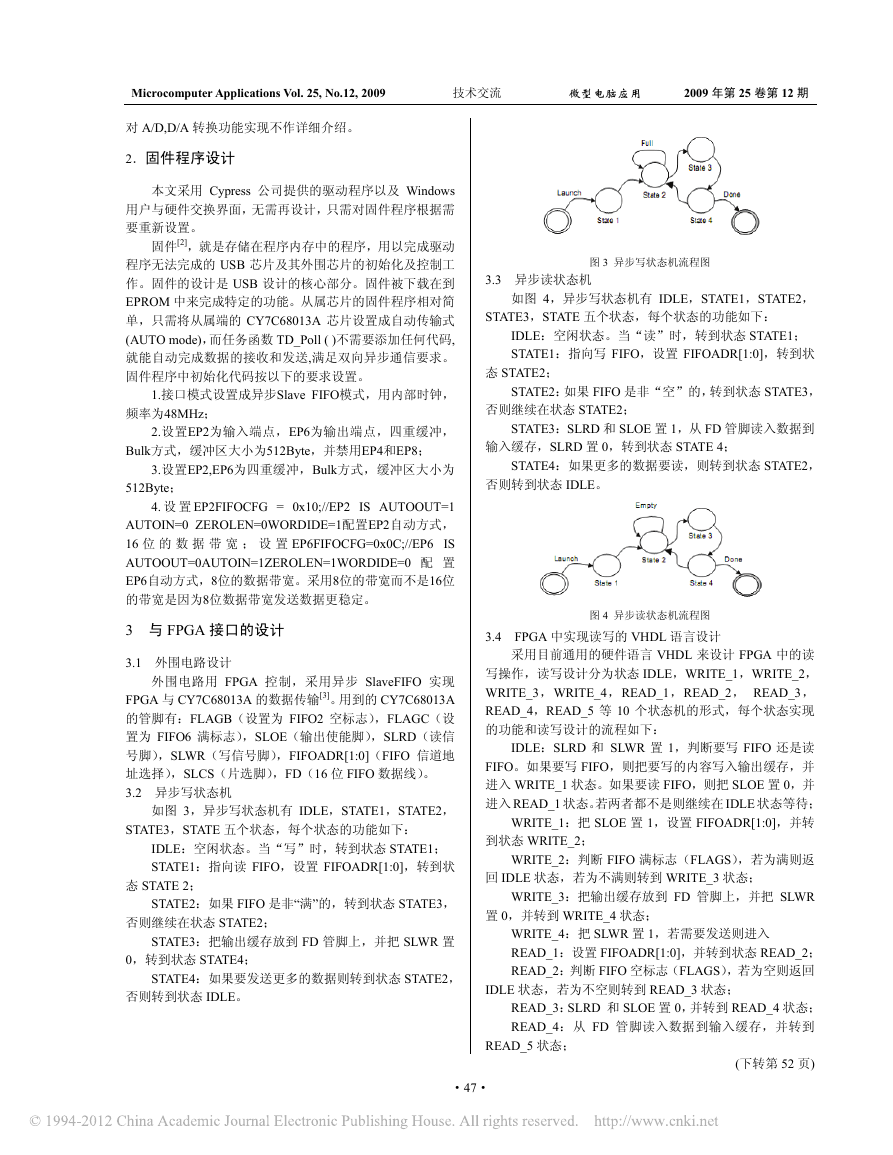

1.2 Slave FIFO 接口模式

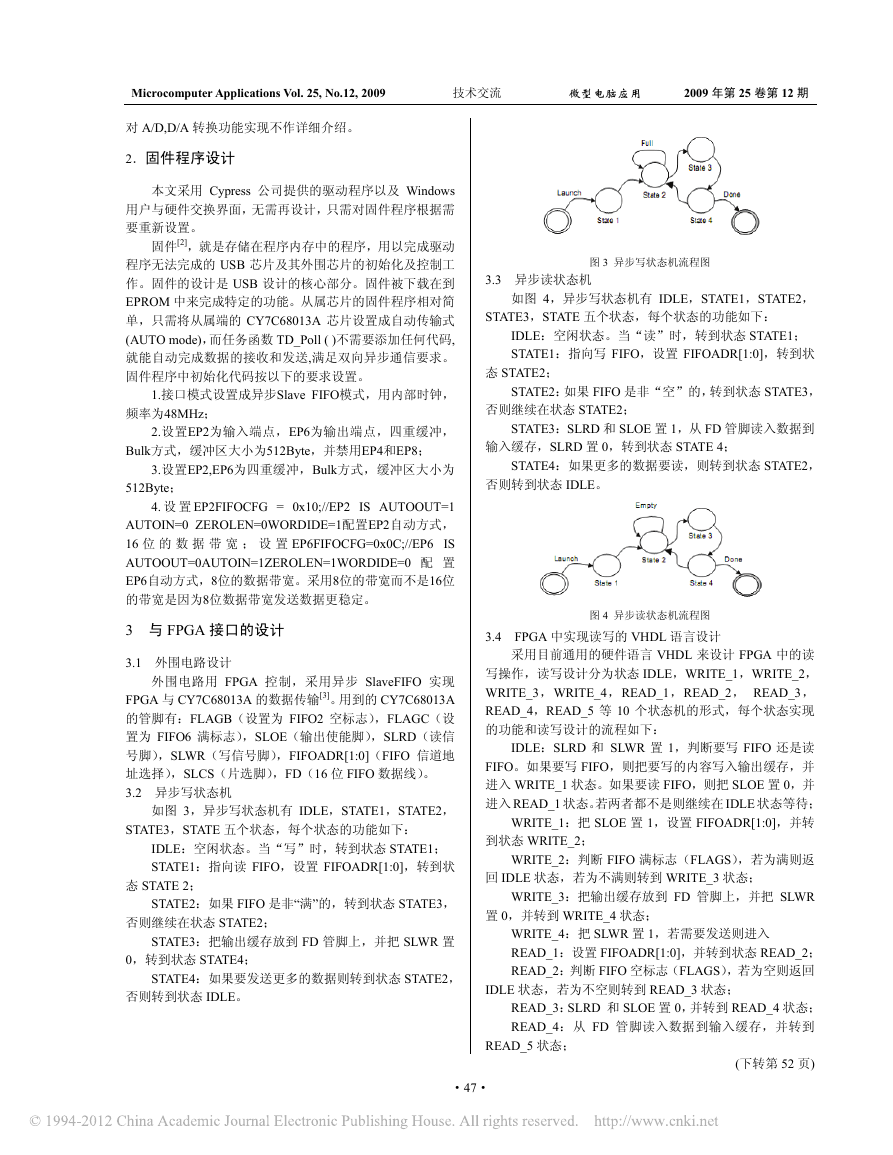

EZ_USB FX2 CY7C68013A 具有 Slave FIFO 接口和通

用可编程接口(GPIF)两种接口模式[1]。本文采用 Slave FIFO

接口模式,EZ_USB FX2 提供了一种独特的架构,使 USB

接口和外围电路直接共享 FIFO 存储器,如图 2 所示。这时,

增强型 8051 不参与数据传输,但可通过 FIFO 和 RAM 的方

式访问所传输的数据。对于从属模式 Slave FIFOs,外围电

路可像普通 FIFO 一样对 FX2 的端点 2、4、6、8 的数据缓

冲区进行读写。

USB 执行 OUT 传输,将 EPx 端点设成 512 字节四重

FIFO。在 USB 端和外部接口端都并不知道有四重 FIFO。

USB 端只要有一个 FIFO 为半满就可以继续发送数据。当被

操作的 FIFO 写“满”时,FX2 自动将其转换到外部接口端,

排队等待读取;并将 USB 接口队列中下一个为“空”的

FIFO 转移到 USB 接口上,供其继续写数据。外部接口端与

此类似,只要有个 FIFO 为“半满”,就可以继续读取数据。

当前操作的 FIFO 读“空”时,FX2 自动将其转换到 USB

接口端,排队等候写入;并将外部接口队列中下一个为

“满”的 FIFO 转移到外部接口上,供其继续读取数据。

图 2 EZ_USB FX2 数据传输示意图

1.3 FPGA 的选择

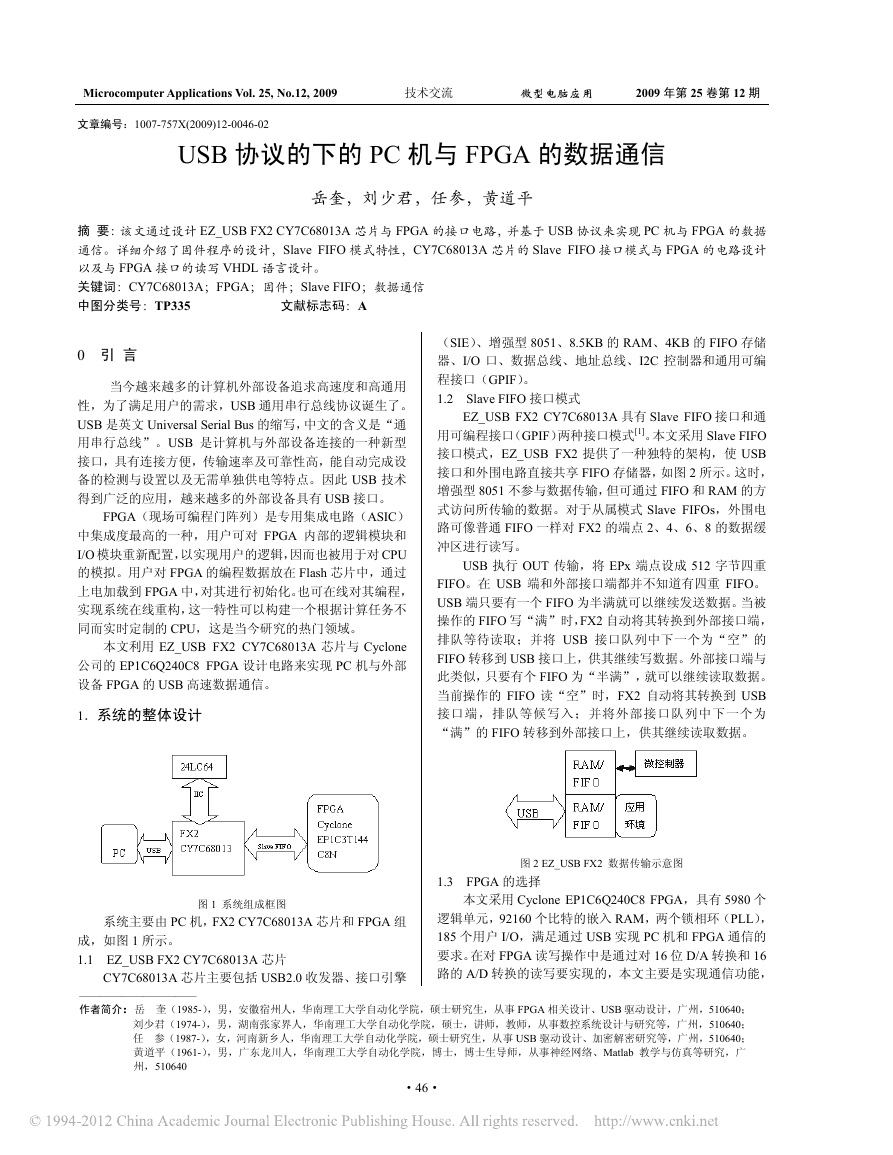

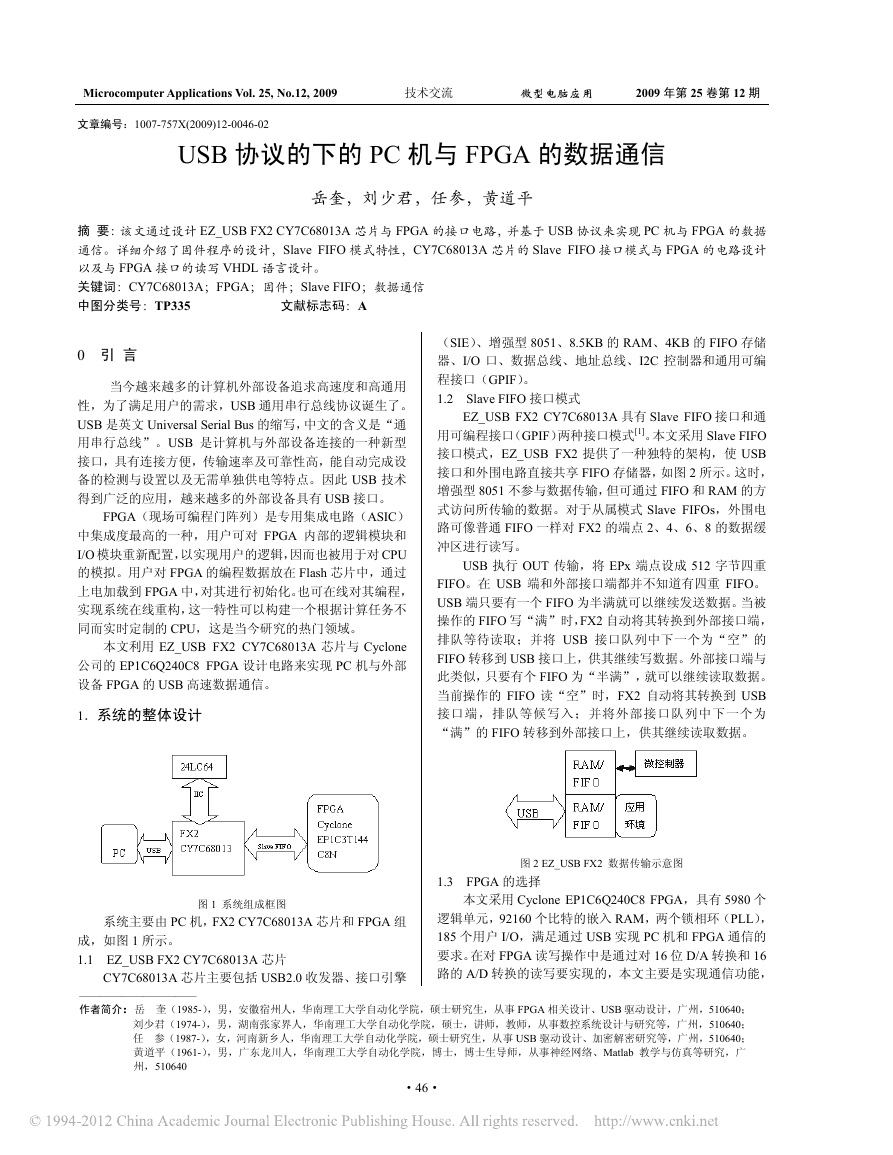

图 1 系统组成框图

系统主要由 PC 机,FX2 CY7C68013A 芯片和 FPGA 组

成,如图 1 所示。

1.1 EZ_USB FX2 CY7C68013A 芯片

CY7C68013A 芯片主要包括 USB2.0 收发器、接口引擎

本文采用 Cyclone EP1C6Q240C8 FPGA,具有 5980 个

逻辑单元,92160 个比特的嵌入 RAM,两个锁相环(PLL),

185 个用户 I/O,满足通过 USB 实现 PC 机和 FPGA 通信的

要求。在对 FPGA 读写操作中是通过对 16 位 D/A 转换和 16

路的 A/D 转换的读写要实现的,本文主要是实现通信功能,

———————————

作者简介:岳 奎(1985-),男,安徽宿州人,华南理工大学自动化学院,硕士研究生,从事 FPGA 相关设计、USB 驱动设计,广州,510640;

刘少君(1974-),男,湖南张家界人,华南理工大学自动化学院,硕士,讲师,教师,从事数控系统设计与研究等,广州,510640;

任 参(1987-),女,河南新乡人,华南理工大学自动化学院,硕士研究生,从事 USB 驱动设计、加密解密研究等,广州,510640;

黄道平(1961-),男,广东龙川人,华南理工大学自动化学院,博士,博士生导师,从事神经网络、Matlab 教学与仿真等研究,广

州,510640

·46·

�

Microcomputer Applications Vol. 25, No.12, 2009 技术交流 微型电脑应用 2009 年第 25 卷第 12 期

对 A/D,D/A 转换功能实现不作详细介绍。

2.固件程序设计

本文采用 Cypress 公司提供的驱动程序以及 Windows

用户与硬件交换界面,无需再设计,只需对固件程序根据需

要重新设置。

固件[2],就是存储在程序内存中的程序,用以完成驱动

程序无法完成的 USB 芯片及其外围芯片的初始化及控制工

作。固件的设计是 USB 设计的核心部分。固件被下载在到

EPROM 中来完成特定的功能。从属芯片的固件程序相对简

单,只需将从属端的 CY7C68013A 芯片设置成自动传输式

(AUTO mode),而任务函数 TD_Poll ( )不需要添加任何代码,

就能自动完成数据的接收和发送,满足双向异步通信要求。

固件程序中初始化代码按以下的要求设置。

1.接口模式设置成异步Slave FIFO模式,用内部时钟,

频率为48MHz;

2.设置EP2为输入端点,EP6为输出端点,四重缓冲,

Bulk方式,缓冲区大小为512Byte,并禁用EP4和EP8;

3.设置EP2,EP6为四重缓冲,Bulk方式,缓冲区大小为

512Byte;

4. 设 置 EP2FIFOCFG = 0x10;//EP2 IS AUTOOUT=1

AUTOIN=0 ZEROLEN=0WORDIDE=1配置EP2自动方式,

16 位 的 数 据 带 宽 ; 设 置 EP6FIFOCFG=0x0C;//EP6 IS

AUTOOUT=0AUTOIN=1ZEROLEN=1WORDIDE=0 配 置

EP6自动方式,8位的数据带宽。采用8位的带宽而不是16位

的带宽是因为8位数据带宽发送数据更稳定。

3 与 FPGA 接口的设计

3.1 外围电路设计

外围电路用 FPGA 控制,采用异步 SlaveFIFO 实现

FPGA 与 CY7C68013A 的数据传输[3]。用到的 CY7C68013A

的管脚有:FLAGB(设置为 FIFO2 空标志),FLAGC(设

置为 FIFO6 满标志),SLOE(输出使能脚),SLRD(读信

号脚),SLWR(写信号脚),FIFOADR[1:0](FIFO 信道地

址选择),SLCS(片选脚),FD(16 位 FIFO 数据线)。

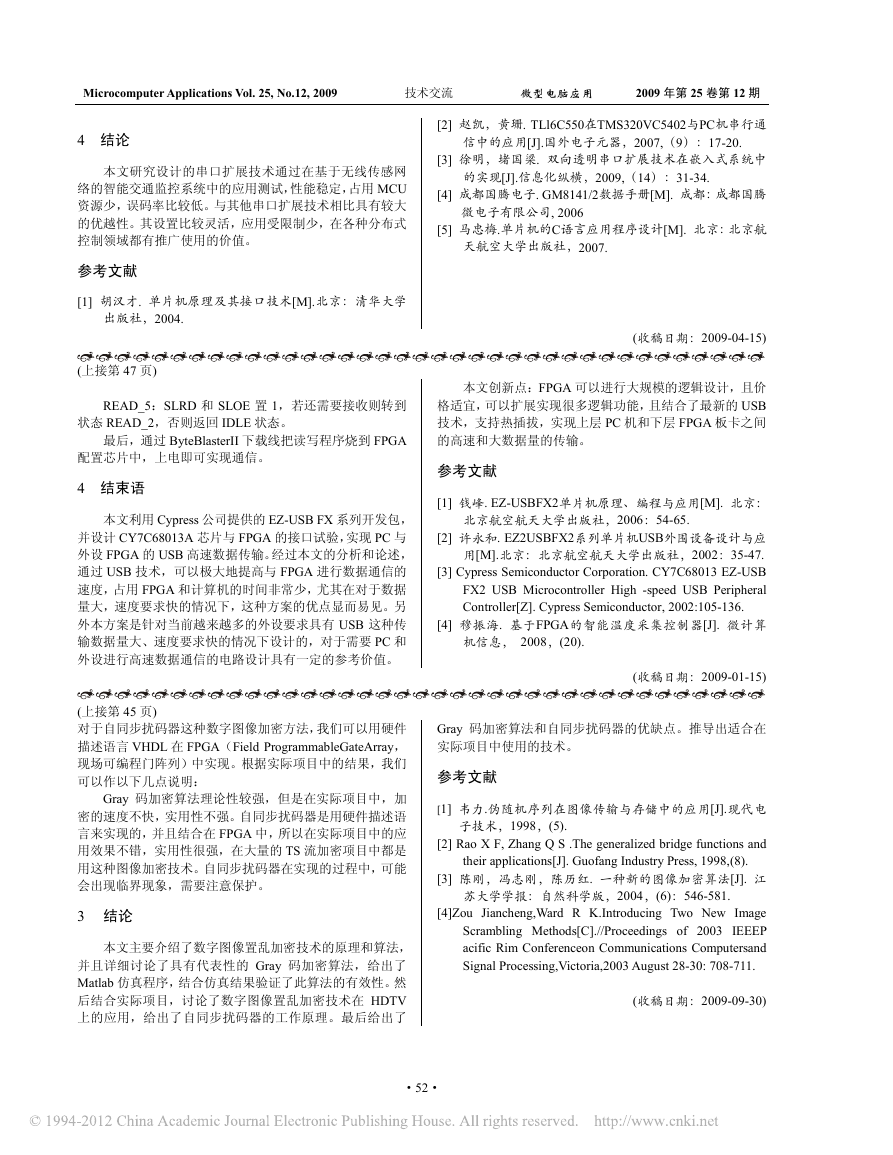

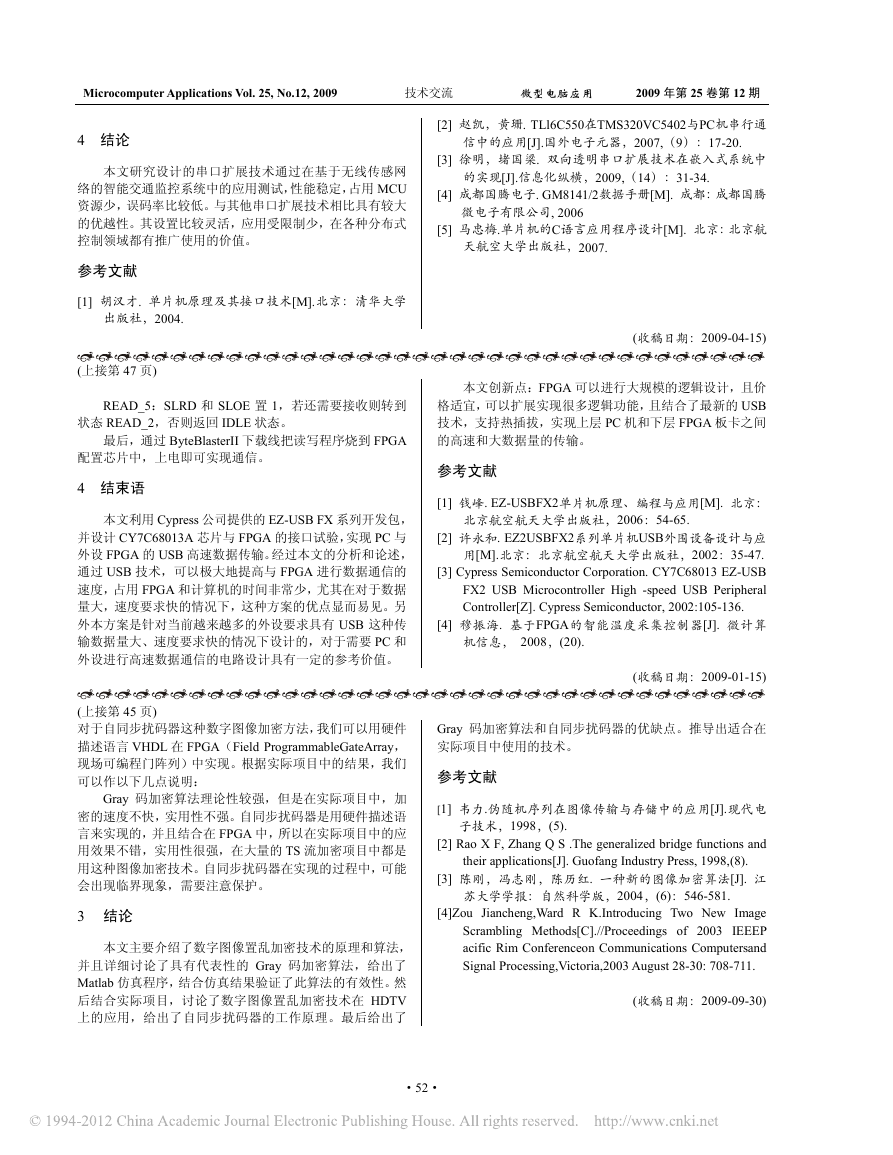

3.2 异步写状态机

如图 3,异步写状态机有 IDLE,STATE1,STATE2,

STATE3,STATE 五个状态,每个状态的功能如下:

IDLE:空闲状态。当“写”时,转到状态 STATE1;

STATE1:指向读 FIFO,设置 FIFOADR[1:0],转到状

态 STATE 2;

STATE2:如果 FIFO 是非“满”的,转到状态 STATE3,

否则继续在状态 STATE2;

STATE3:把输出缓存放到 FD 管脚上,并把 SLWR 置

0,转到状态 STATE4;

STATE4:如果要发送更多的数据则转到状态 STATE2,

否则转到状态 IDLE。

图 3 异步写状态机流程图

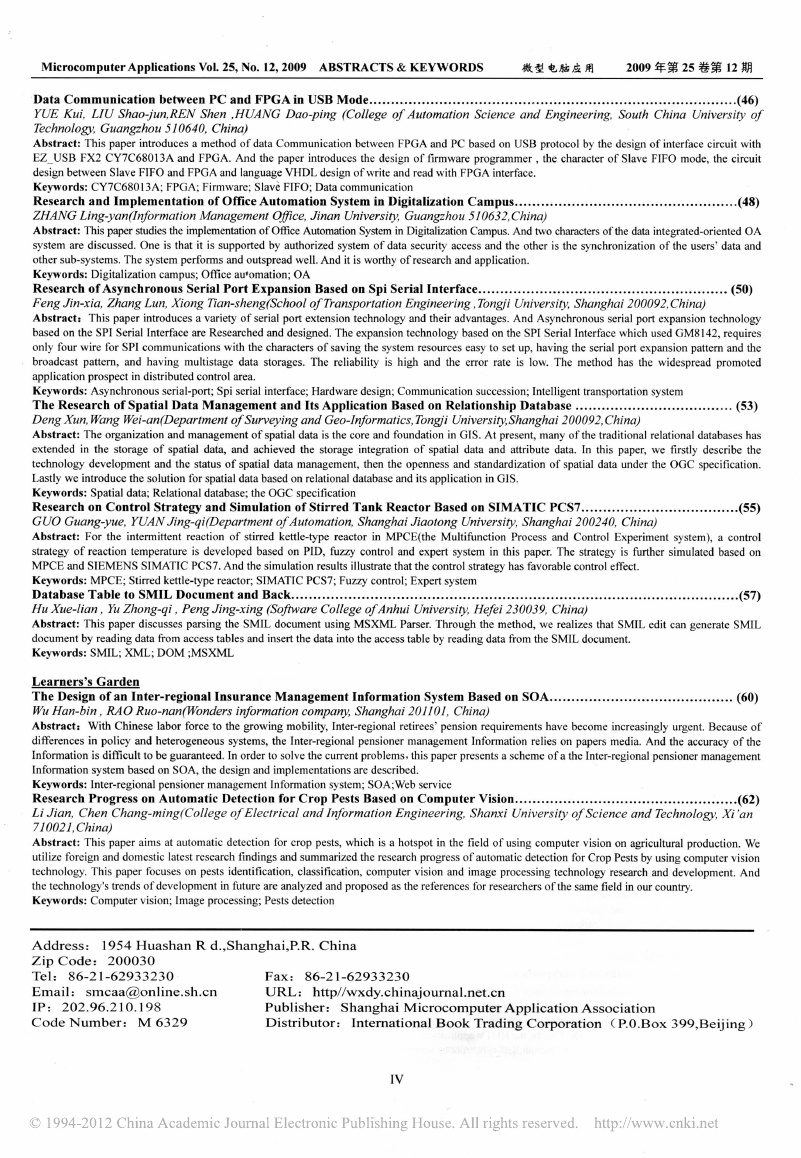

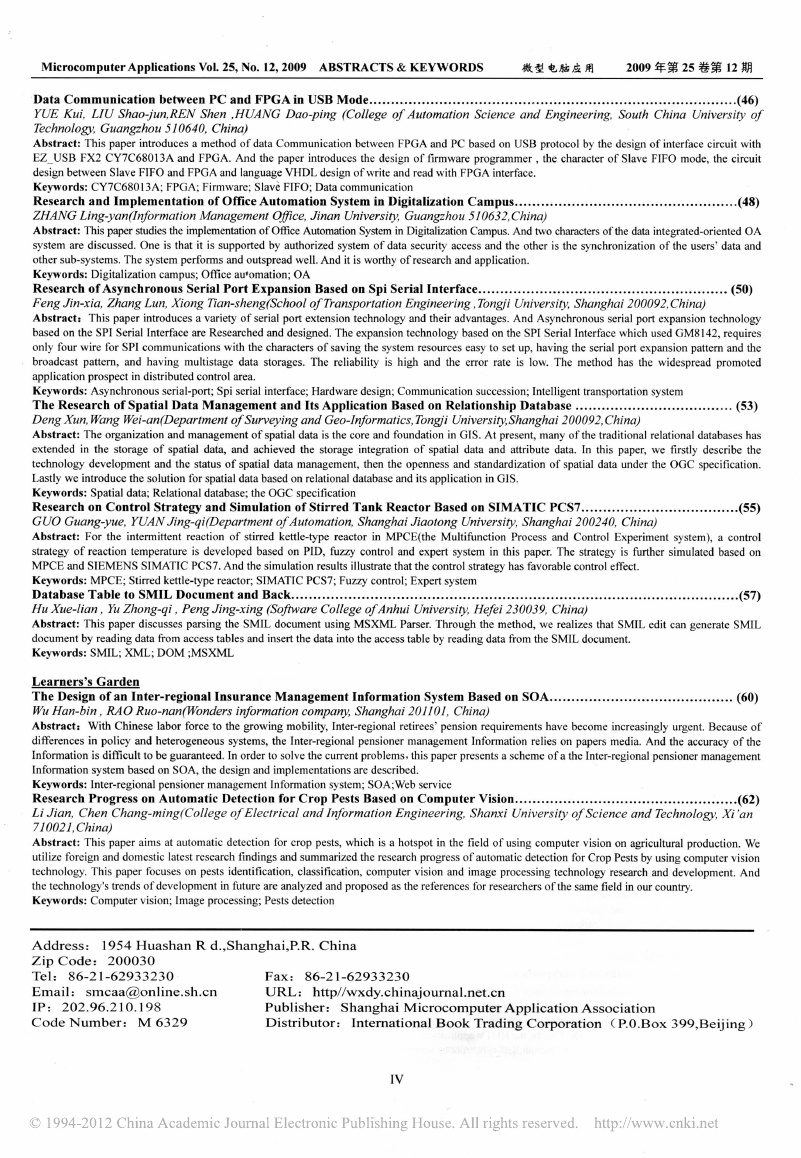

3.3 异步读状态机

如图 4,异步写状态机有 IDLE,STATE1,STATE2,

STATE3,STATE 五个状态,每个状态的功能如下:

IDLE:空闲状态。当“读”时,转到状态 STATE1;

STATE1:指向写 FIFO,设置 FIFOADR[1:0],转到状

态 STATE2;

STATE2:如果 FIFO 是非“空”的,转到状态 STATE3,

否则继续在状态 STATE2;

STATE3:SLRD 和 SLOE 置 1,从 FD 管脚读入数据到

输入缓存,SLRD 置 0,转到状态 STATE 4;

STATE4:如果更多的数据要读,则转到状态 STATE2,

否则转到状态 IDLE。

图 4 异步读状态机流程图

3.4 FPGA 中实现读写的 VHDL 语言设计

采用目前通用的硬件语言 VHDL 来设计 FPGA 中的读

写操作,读写设计分为状态 IDLE,WRITE_1,WRITE_2,

WRITE_3,WRITE_4,READ_1,READ_2, READ_3,

READ_4,READ_5 等 10 个状态机的形式,每个状态实现

的功能和读写设计的流程如下:

IDLE:SLRD 和 SLWR 置 1,判断要写 FIFO 还是读

FIFO。如果要写 FIFO,则把要写的内容写入输出缓存,并

进入 WRITE_1 状态。如果要读 FIFO,则把 SLOE 置 0,并

进入 READ_1 状态。若两者都不是则继续在 IDLE 状态等待;

WRITE_1:把 SLOE 置 1,设置 FIFOADR[1:0],并转

到状态 WRITE_2;

WRITE_2:判断 FIFO 满标志(FLAGS),若为满则返

回 IDLE 状态,若为不满则转到 WRITE_3 状态;

WRITE_3:把输出缓存放到 FD 管脚上,并把 SLWR

置 0,并转到 WRITE_4 状态;

WRITE_4:把 SLWR 置 1,若需要发送则进入

READ_1:设置 FIFOADR[1:0],并转到状态 READ_2;

READ_2:判断 FIFO 空标志(FLAGS),若为空则返回

IDLE 状态,若为不空则转到 READ_3 状态;

READ_3:SLRD 和 SLOE 置 0,并转到 READ_4 状态;

READ_4:从 FD 管脚读入数据到输入缓存,并转到

READ_5 状态;

(下转第 52 页)

·47·

�

Microcomputer Applications Vol. 25, No.12, 2009 技术交流 微型电脑应用 2009 年第 25 卷第 12 期

4 结论

本文研究设计的串口扩展技术通过在基于无线传感网

络的智能交通监控系统中的应用测试,性能稳定,占用 MCU

资源少,误码率比较低。与其他串口扩展技术相比具有较大

的优越性。其设置比较灵活,应用受限制少,在各种分布式

控制领域都有推广使用的价值。

参考文献

[1] 胡汉才. 单片机原理及其接口技术[M].北京:清华大学

出版社,2004.

[2] 赵凯,黄珊. TLl6C550在TMS320VC5402与PC机串行通

信中的应用[J].国外电子元器,2007,(9):17-20.

[3] 徐明,堵国梁. 双向透明串口扩展技术在嵌入式系统中

的实现[J].信息化纵横,2009,(14):31-34.

[4] 成都国腾电子. GM8141/2数据手册[M]. 成都:成都国腾

微电子有限公司, 2006

[5] 马忠梅.单片机的C语言应用程序设计[M]. 北京:北京航

天航空大学出版社,2007.

(上接第 47 页)

READ_5:SLRD 和 SLOE 置 1,若还需要接收则转到

状态 READ_2,否则返回 IDLE 状态。

最后,通过 ByteBlasterII 下载线把读写程序烧到 FPGA

本文创新点:FPGA 可以进行大规模的逻辑设计,且价

格适宜,可以扩展实现很多逻辑功能,且结合了最新的 USB

技术,支持热插拔,实现上层 PC 机和下层 FPGA 板卡之间

的高速和大数据量的传输。

(收稿日期:2009-04-15)

配置芯片中,上电即可实现通信。

4 结束语

本文利用 Cypress 公司提供的 EZ-USB FX 系列开发包,

并设计 CY7C68013A 芯片与 FPGA 的接口试验,实现 PC 与

外设 FPGA 的 USB 高速数据传输。经过本文的分析和论述,

通过 USB 技术,可以极大地提高与 FPGA 进行数据通信的

速度,占用 FPGA 和计算机的时间非常少,尤其在对于数据

量大,速度要求快的情况下,这种方案的优点显而易见。另

外本方案是针对当前越来越多的外设要求具有 USB 这种传

输数据量大、速度要求快的情况下设计的,对于需要 PC 和

外设进行高速数据通信的电路设计具有一定的参考价值。

(上接第 45 页)

对于自同步扰码器这种数字图像加密方法,我们可以用硬件

描述语言 VHDL 在 FPGA(Field ProgrammableGateArray,

现场可编程门阵列)中实现。根据实际项目中的结果,我们

可以作以下几点说明:

Gray 码加密算法理论性较强,但是在实际项目中,加

密的速度不快,实用性不强。自同步扰码器是用硬件描述语

言来实现的,并且结合在 FPGA 中,所以在实际项目中的应

用效果不错,实用性很强,在大量的 TS 流加密项目中都是

用这种图像加密技术。自同步扰码器在实现的过程中,可能

会出现临界现象,需要注意保护。

3 结论

本文主要介绍了数字图像置乱加密技术的原理和算法,

并且详细讨论了具有代表性的 Gray 码加密算法,给出了

Matlab 仿真程序,结合仿真结果验证了此算法的有效性。然

后结合实际项目,讨论了数字图像置乱加密技术在 HDTV

上的应用,给出了自同步扰码器的工作原理。最后给出了

参考文献

[1] 钱峰. EZ-USBFX2单片机原理、编程与应用[M]. 北京:

北京航空航天大学出版社,2006:54-65.

[2] 许永和. EZ2USBFX2系列单片机USB外围设备设计与应

用[M].北京:北京航空航天大学出版社,2002:35-47.

[3] Cypress Semiconductor Corporation. CY7C68013 EZ-USB

FX2 USB Microcontroller High -speed USB Peripheral

Controller[Z]. Cypress Semiconductor, 2002:105-136.

[4] 穆振海. 基于FPGA的智能温度采集控制器[J]. 微计算

机信息, 2008,(20).

(收稿日期:2009-01-15)

Gray 码加密算法和自同步扰码器的优缺点。推导出适合在

实际项目中使用的技术。

参考文献

[1] 韦力.伪随机序列在图像传输与存储中的应用[J].现代电

子技术,1998,(5).

[2] Rao X F, Zhang Q S .The generalized bridge functions and

their applications[J]. Guofang Industry Press, 1998,(8).

[3] 陈刚,冯志刚,陈历红. 一种新的图像加密算法[J]. 江

苏大学学报:自然科学版,2004,(6):546-581.

[4]Zou Jiancheng,Ward R K.Introducing Two New Image

Scrambling Methods[C].//Proceedings of 2003 IEEEP

acific Rim Conferenceon Communications Computersand

Signal Processing,Victoria,2003 August 28-30: 708-711.

(收稿日期:2009-09-30)

·52·

�

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc