延安大学计算机学院实验报告专用纸

学号

1110218014074

姓名

王楠

班级 计科 18 课程名称

计算机组成原理

实验项目名称

超前进位加法器设计实验

任课教师

指导教师

实验组别 第

组

同组者

教师评语及成绩:

实验成绩:

教师签字:

(请按照实验报告的有关要求书写,一般必须包括:1、实验目的;2、实验内容;3、实验步骤与方法;4、

实验数据与程序清单;5、出现的问题及解决方法;6、实验结果、结果分析与体会等内容。)

【1】实验目的

(1)掌握超前进位加法器的原理及其设计方法。

(2)熟悉 CPLD 应用设计及 EDA 软件的使用。

【2】实验环境

PC 机-一台, TD-CMA 实验系统一套

【3】实验步骤

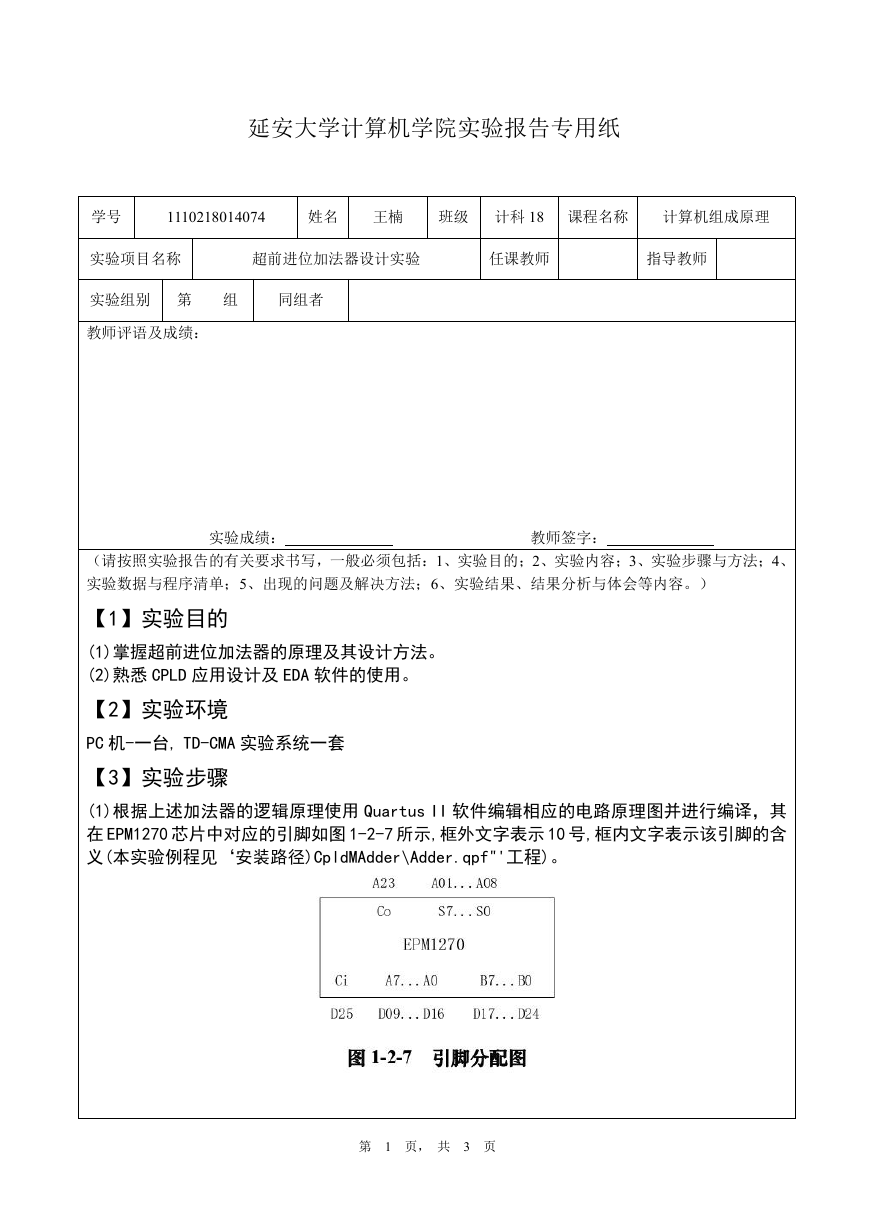

(1)根据上述加法器的逻辑原理使用 Quartus II 软件编辑相应的电路原理图并进行编译,其

在 EPM1270 芯片中对应的引脚如图 1-2-7 所示,框外文字表示 10 号,框内文字表示该引脚的含

义(本实验例程见‘安装路径)CpldMAdder\Adder.qpf"'工程)。

第 1 页, 共 3 页

�

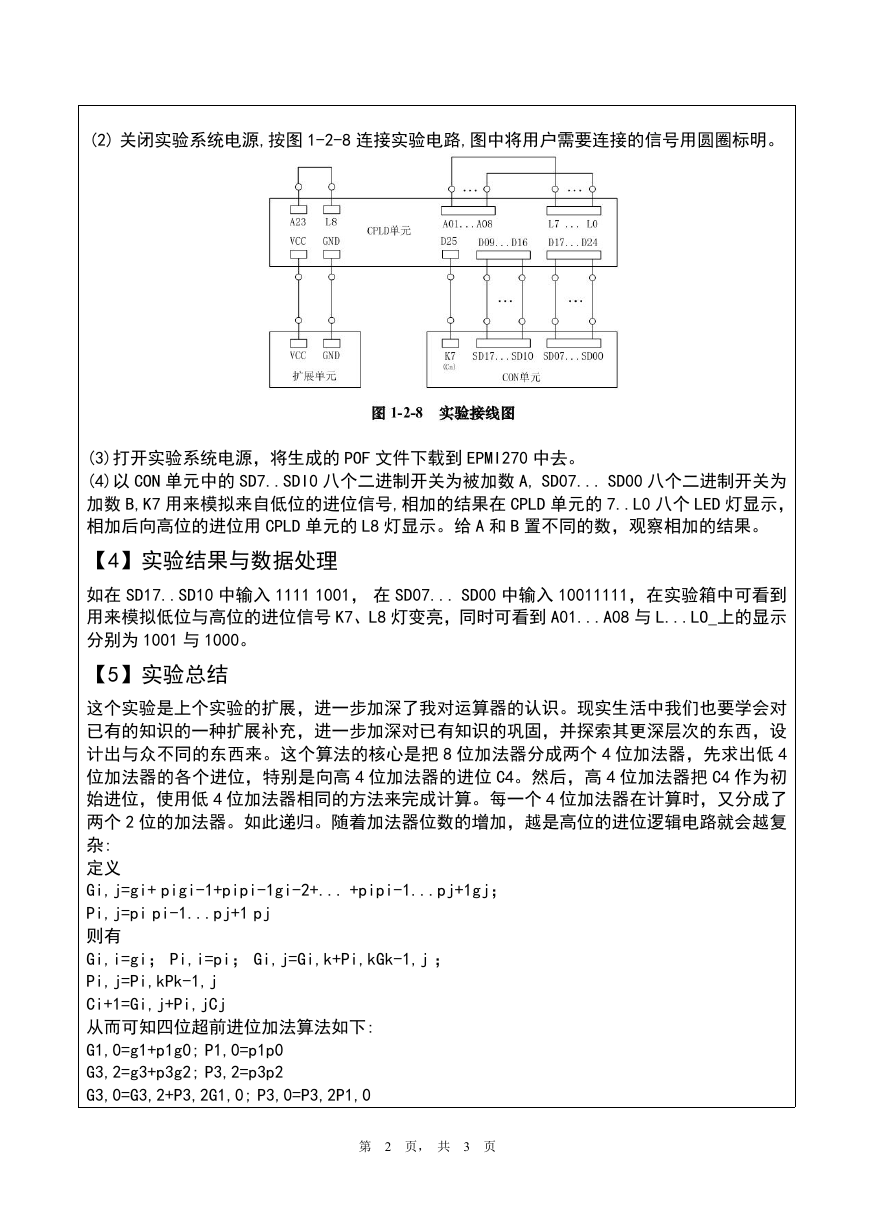

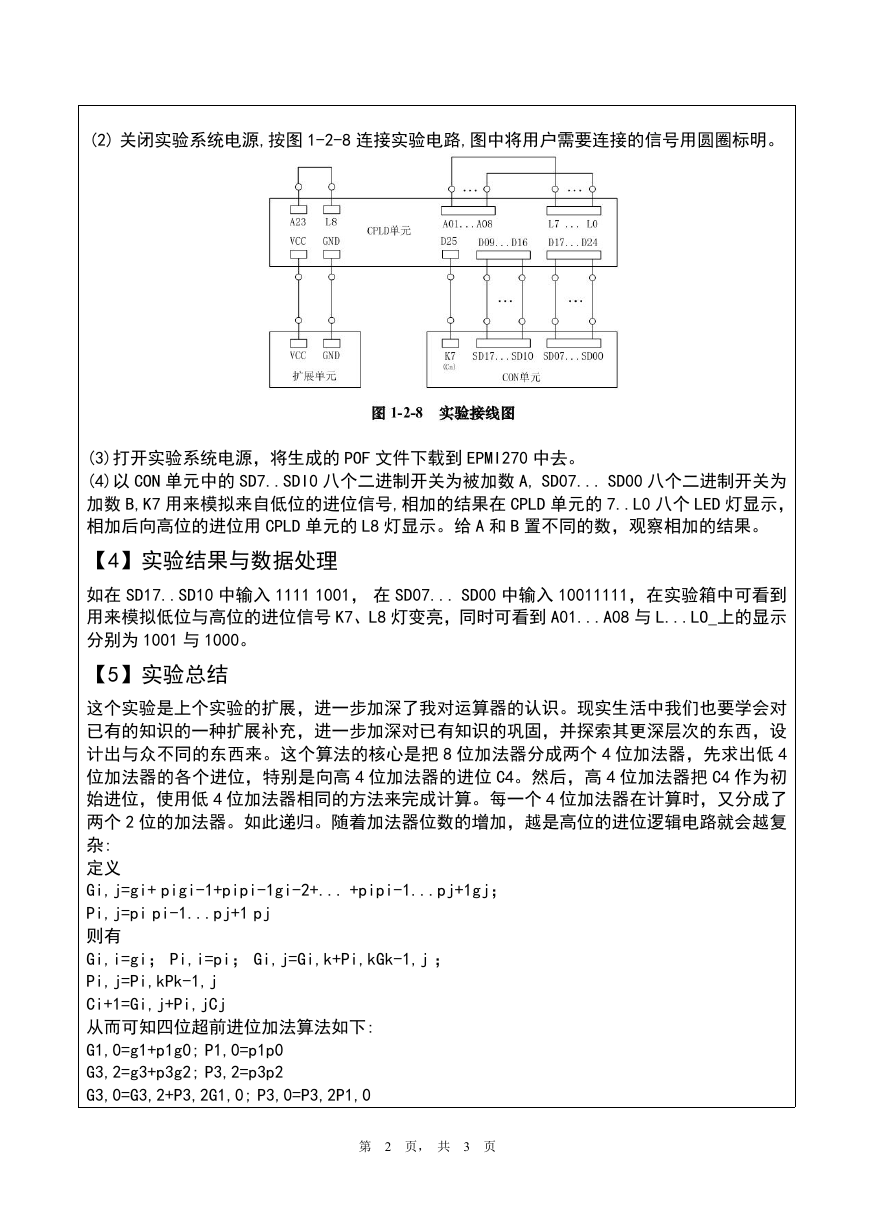

(2) 关闭实验系统电源,按图 1-2-8 连接实验电路,图中将用户需要连接的信号用圆圈标明。

(3)打开实验系统电源,将生成的 POF 文件下载到 EPMI270 中去。

(4)以 CON 单元中的 SD7..SDI0 八个二进制开关为被加数 A, SD07... SD00 八个二进制开关为

加数 B,K7 用来模拟来自低位的进位信号,相加的结果在 CPLD 单元的 7..L0 八个 LED 灯显示,

相加后向高位的进位用 CPLD 单元的 L8 灯显示。给 A 和 B 置不同的数,观察相加的结果。

【4】实验结果与数据处理

如在 SD17..SD10 中输入 1111 1001, 在 SD07... SD00 中输入 10011111,在实验箱中可看到

用来模拟低位与高位的进位信号 K7、L8 灯变亮,同时可看到 A01...A08 与 L...LO_上的显示

分别为 1001 与 1000。

【5】实验总结

这个实验是上个实验的扩展,进一步加深了我对运算器的认识。现实生活中我们也要学会对

已有的知识的一种扩展补充,进一步加深对已有知识的巩固,并探索其更深层次的东西,设

计出与众不同的东西来。这个算法的核心是把 8 位加法器分成两个 4 位加法器,先求出低 4

位加法器的各个进位,特别是向高 4 位加法器的进位 C4。然后,高 4 位加法器把 C4 作为初

始进位,使用低 4 位加法器相同的方法来完成计算。每一个 4 位加法器在计算时,又分成了

两个 2 位的加法器。如此递归。随着加法器位数的增加,越是高位的进位逻辑电路就会越复

杂:

定义

Gi,j=gi+ pigi-1+pipi-1gi-2+... +pipi-1...pj+1gj;

Pi,j=pi pi-1...pj+1 pj

则有

Gi,i=gi; Pi,i=pi; Gi,j=Gi,k+Pi,kGk-1,j ;

Pi,j=Pi,kPk-1,j

Ci+1=Gi,j+Pi,jCj

从而可知四位超前进位加法算法如下:

G1,0=g1+p1g0; P1,0=p1p0

G3,2=g3+p3g2; P3,2=p3p2

G3,0=G3,2+P3,2G1,0; P3,0=P3,2P1,0

第 2 页, 共 3 页

�

C4=G3,0+P3,0C0

八位超前进位加法算法如下:

G1,0=g1+p1g0; P1,0=p1p0

G3,2=g3+p3g2; P3,2=p3p2

G3,0=G3,2+P3,2G1,0; P3,0=P3,2P1,0

G5,4=g5+p5g4; P5,4=p5p4

G7,6=g7+p7g6; P7,6=p7p6 ;

G7,4=G7,6+P7,6G5,4; P7,4=P7,6P5,4

G7,0=G7,4+P7,4G3,0; P7,0=Р7,4P3,0

C8=G7,0+P7,0C0

第 3 页, 共 3 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc