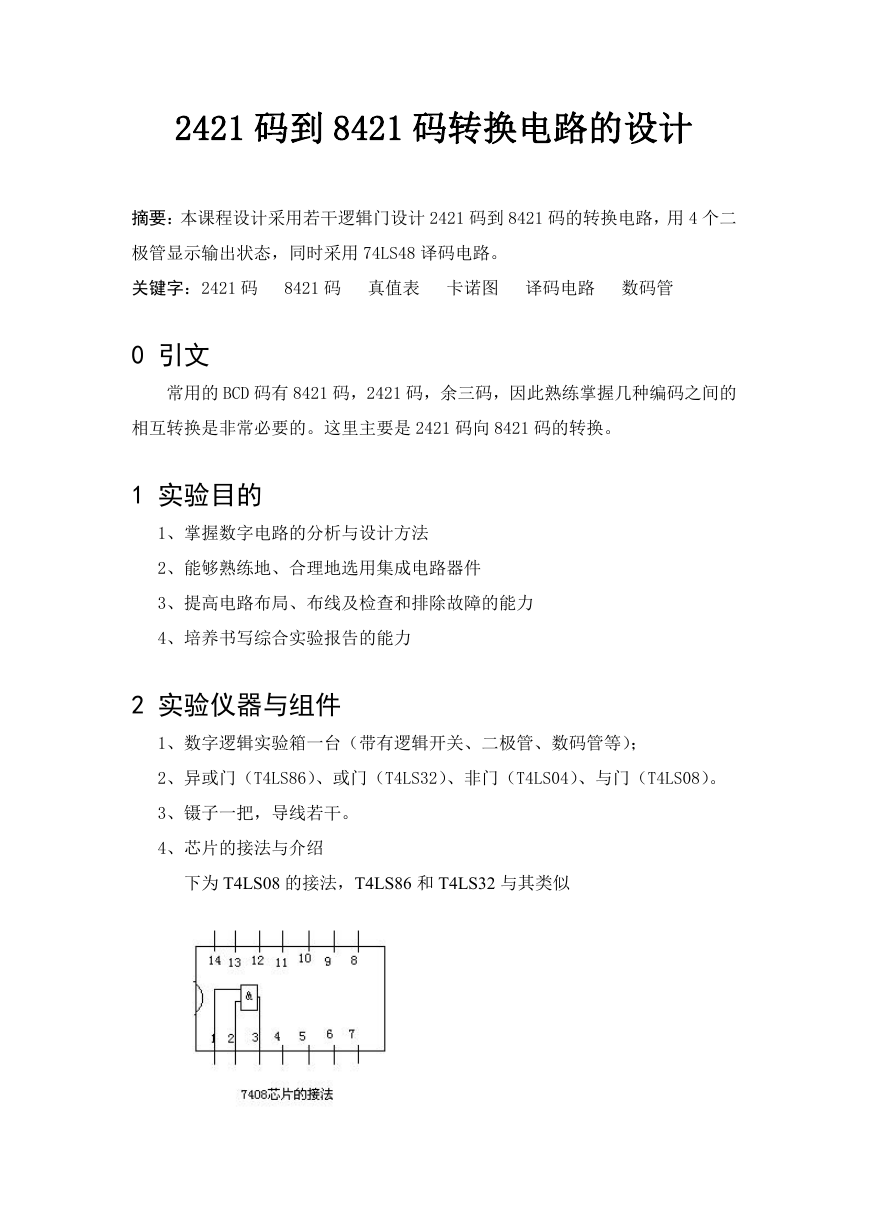

2421 码到 8421 码转换电路的设计

摘要:本课程设计采用若干逻辑门设计 2421 码到 8421 码的转换电路,用 4 个二

极管显示输出状态,同时采用 74LS48 译码电路。

关键字:2421 码 8421 码 真值表 卡诺图 译码电路 数码管

0 引文

常用的 BCD 码有 8421 码,2421 码,余三码,因此熟练掌握几种编码之间的

相互转换是非常必要的。这里主要是 2421 码向 8421 码的转换。

1 实验目的

1、掌握数字电路的分析与设计方法

2、能够熟练地、合理地选用集成电路器件

3、提高电路布局、布线及检查和排除故障的能力

4、培养书写综合实验报告的能力

2 实验仪器与组件

1、数字逻辑实验箱一台(带有逻辑开关、二极管、数码管等);

2、异或门(T4LS86)、或门(T4LS32)、非门(T4LS04)、与门(T4LS08)。

3、镊子一把,导线若干。

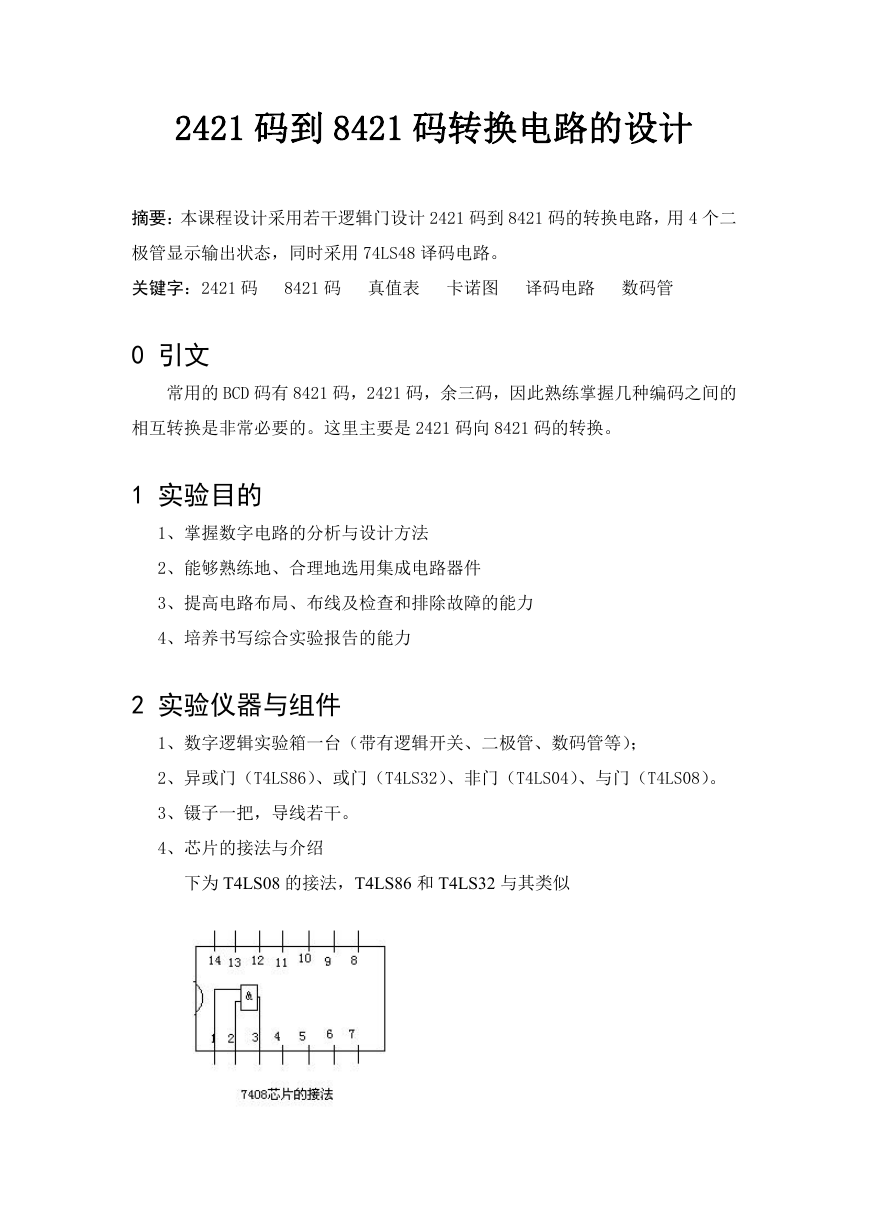

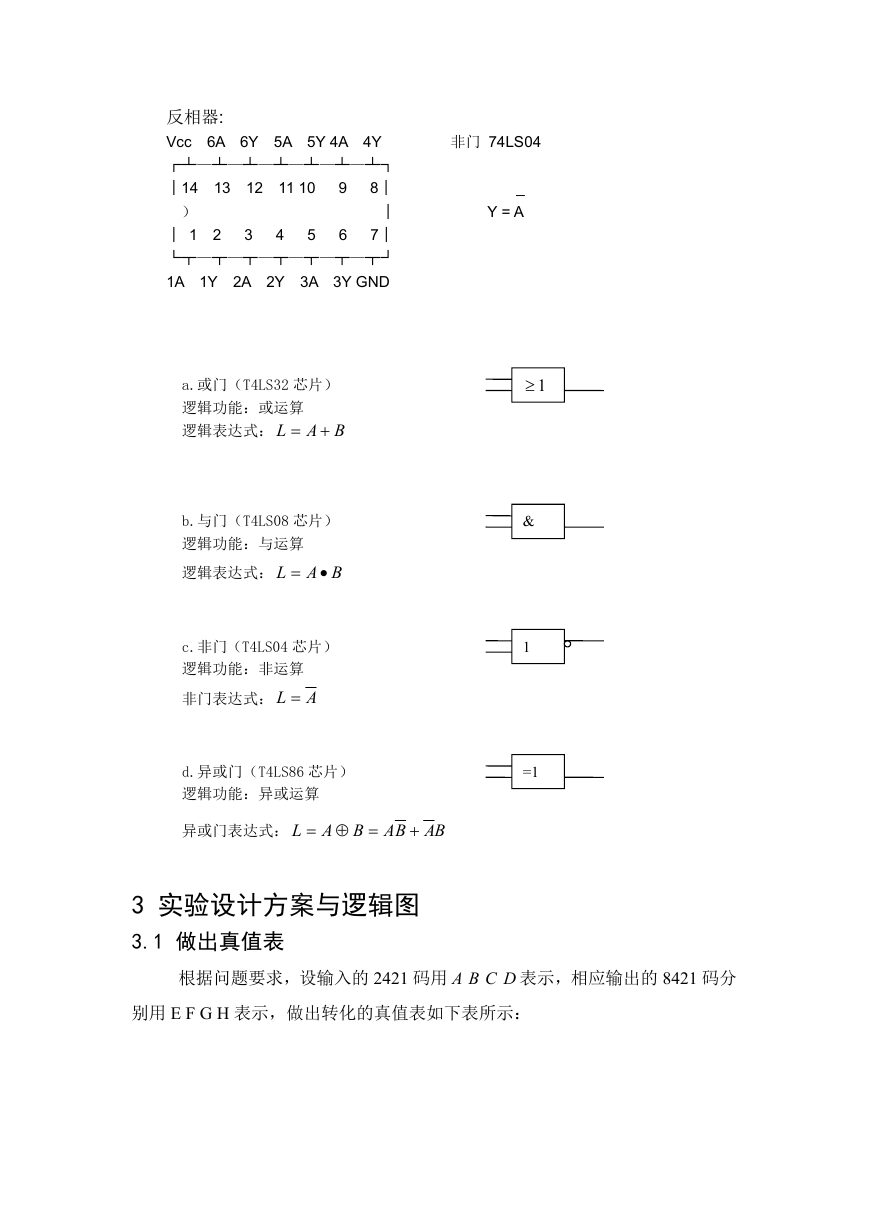

4、芯片的接法与介绍

下为 T4LS08 的接法,T4LS86 和 T4LS32 与其类似

�

反相器:

Vcc 6A 6Y 5A 5Y 4A 4Y

┌┴—┴—┴—┴—┴—┴—┴┐

│14 13 12 11 10

8│

│

│ 1 2

7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND

)

3

9

6

4

5

a.或门(T4LS32 芯片)

逻辑功能:或运算

逻辑表达式:

BAL

b.与门(T4LS08 芯片)

逻辑功能:与运算

逻辑表达式:

BAL

c.非门(T4LS04 芯片)

逻辑功能:非运算

非门表达式:

AL

d.异或门(T4LS86 芯片)

逻辑功能:异或运算

异或门表达式:

BABABAL

非门 74LS04

_

Y = A

1

&

1

=1

3 实验设计方案与逻辑图

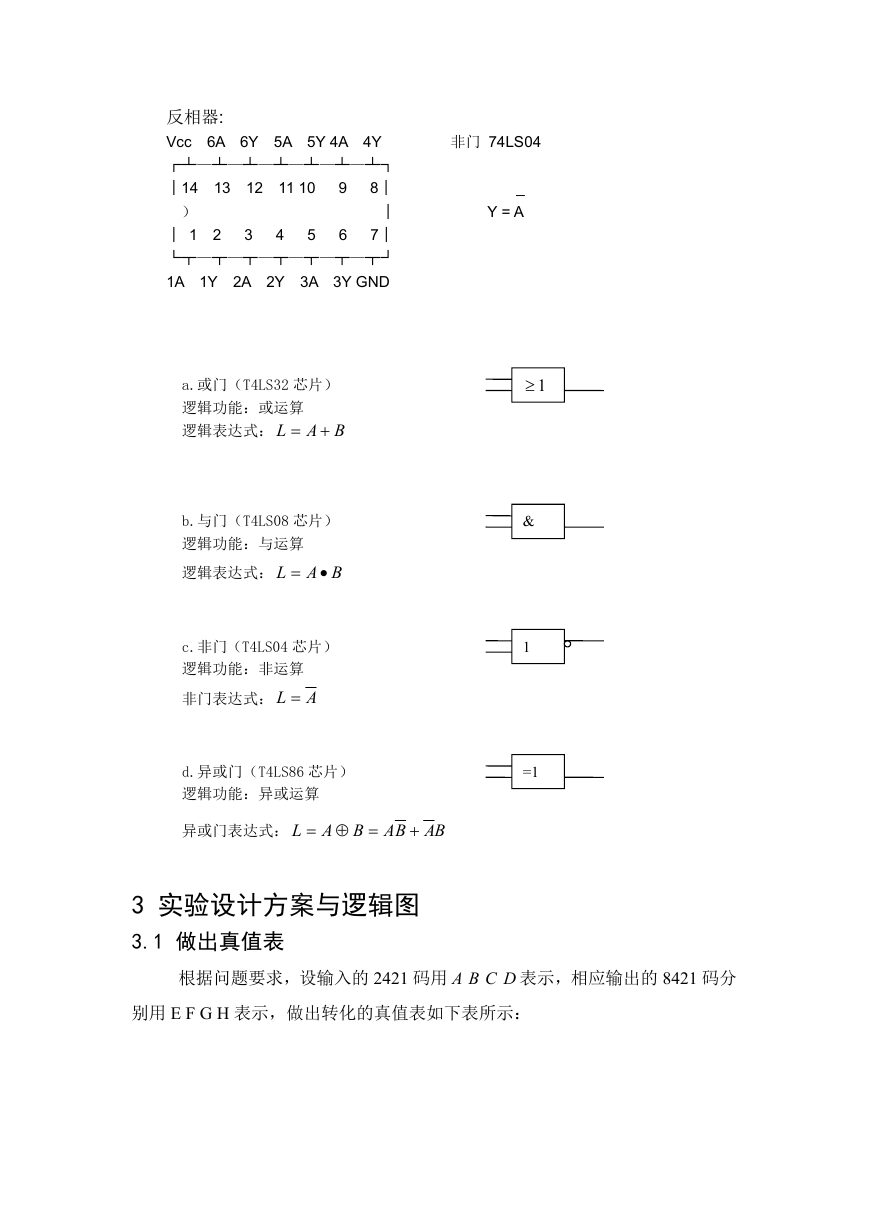

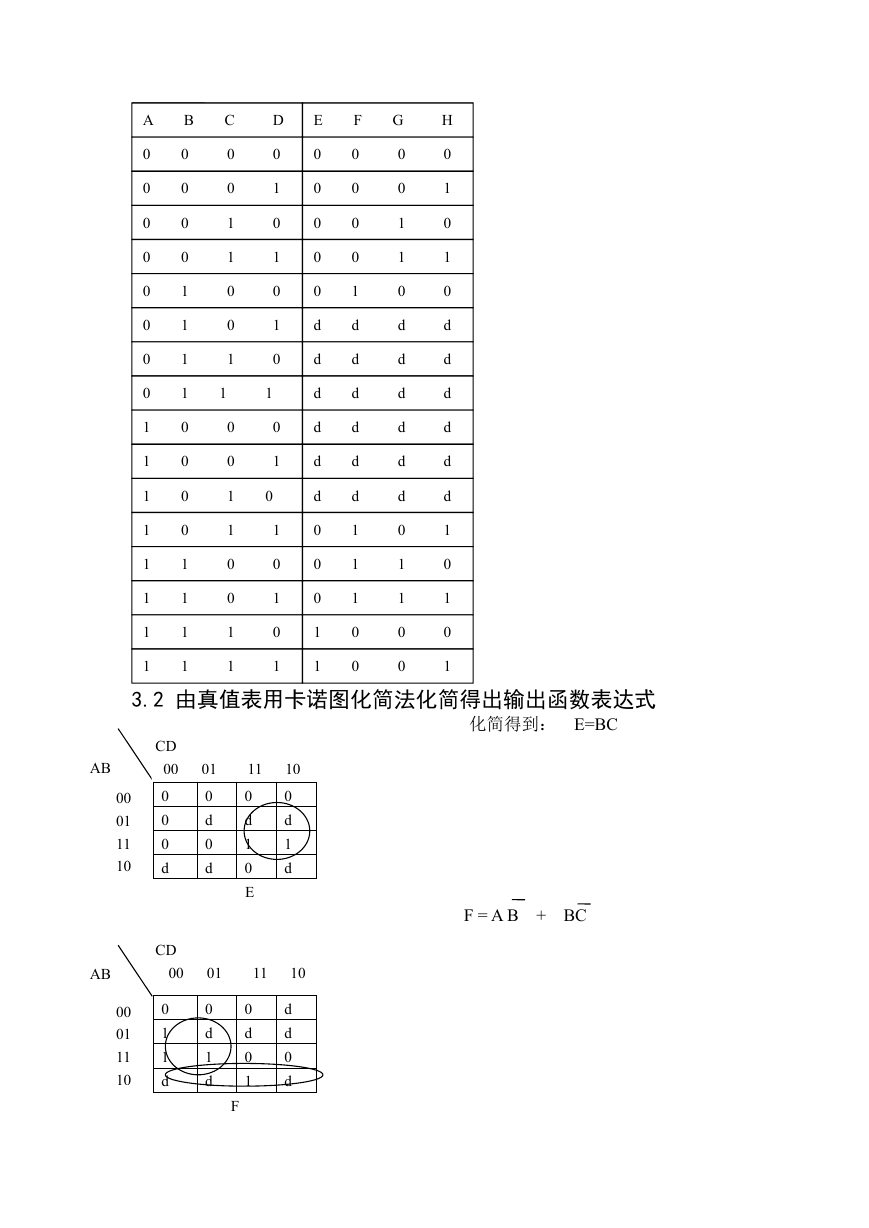

3.1 做出真值表

根据问题要求,设输入的 2421 码用 A B C D 表示,相应输出的 8421 码分

别用 E F G H 表示,做出转化的真值表如下表所示:

�

A

B

C

D

E

F

G

H

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

d

d

d

d

d

d

0

0

0

1

1

0

0

0

0

1

d

d

d

d

d

d

1

1

1

0

0

0

0

1

1

0

d

d

d

d

d

d

0

1

1

0

0

0

1

0

1

0

d

d

d

d

d

d

1

0

1

0

1

3.2 由真值表用卡诺图化简法化简得出输出函数表达式

化简得到: E=BC

F = A B + BC

AB

AB

00

01

11

10

00

01

11

10

CD

00

0

0

0

d

CD

00

0

1

1

d

01

0

d

0

d

10

0

d

1

d

11

0

d

1

0

E

01

11

10

0

d

1

d

0

d

0

1

F

d

d

0

d

�

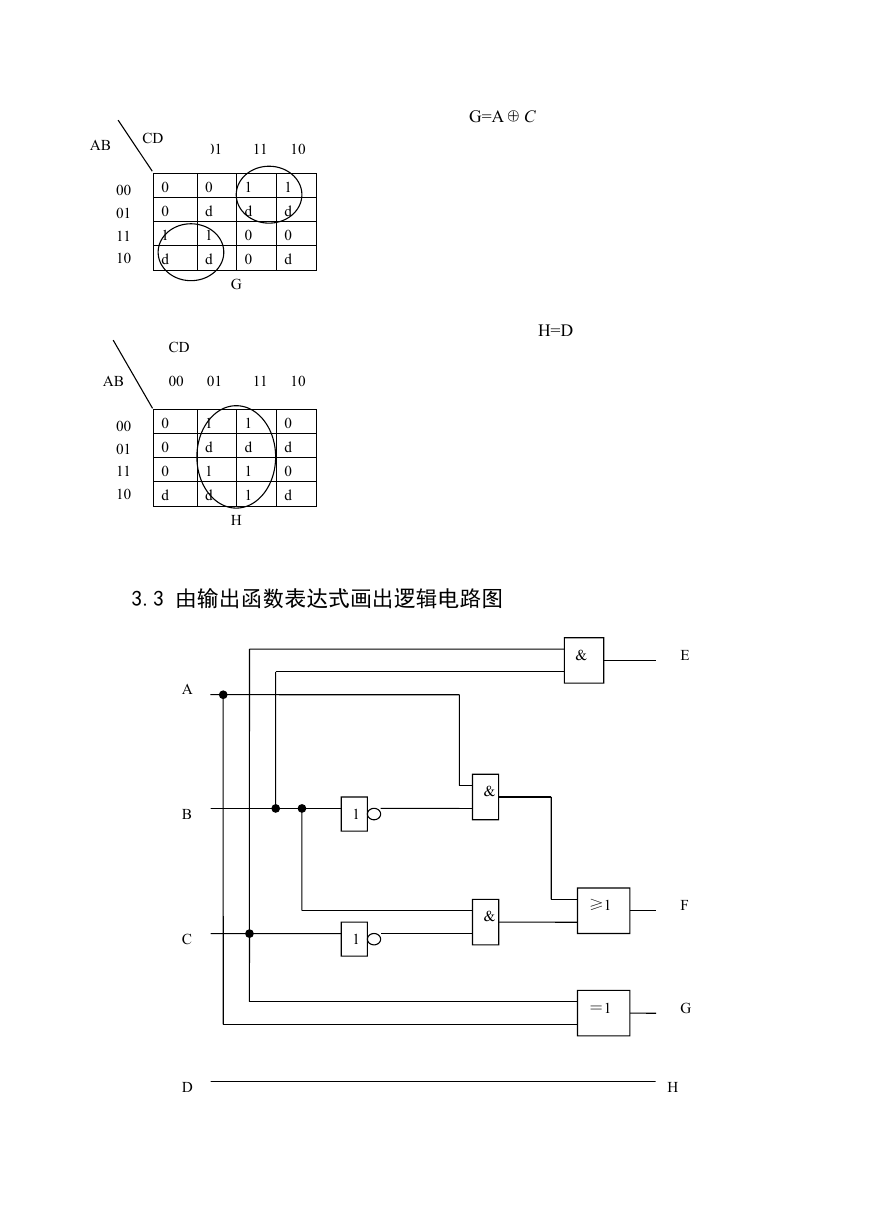

G=A⊕C

H=D

AB

CD

00

01

11

10

00

01

11

10

0

0

1

d

0

d

1

d

1

d

0

0

G

1

d

0

d

CD

00

0

0

0

d

AB

00

01

11

10

01

11

10

1

d

1

d

1

d

1

1

H

0

d

0

d

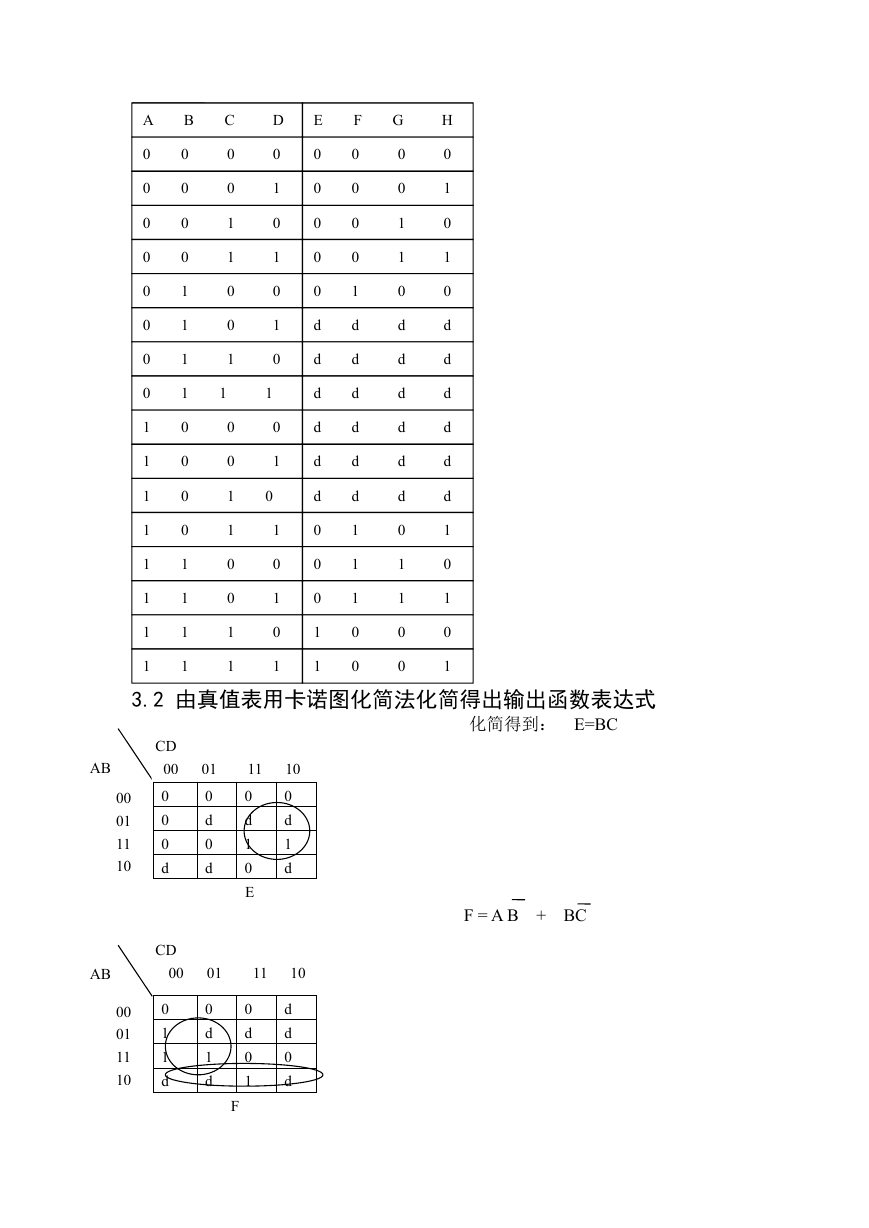

3.3 由输出函数表达式画出逻辑电路图

A

B

C

D

&

&

1

1

&

E

≥1

=1

F

G

H

�

3.4 测试结果

将 EFGH 分别接到四个二极管,可以看见显示结果正确,与真值表对应。将

其直接连到数码管,并将数码管的 seg 接地,如 ABCD 分别置 1111,则数码管显

示 9,对应于 2421 码的数字均显示正确。

4

2

A

0

0

0

0

0

1

1

1

1

1

2

C

0

0

1

1

0

B

0

0

0

0

1

0101~1010

0

1

1

1

1

1

0

0

1

1

1

D

0

1

0

1

0

1

0

1

0

1

8421 码

F

G

0

0

0

0

0

1

1

0

0

1

d

d

0

1

1

1

1

1

0

0

1

0

E

0

0

0

0

0

d

0

1

0

1

1

二极管状态

H Q1 Q2 Q3 Q4

0 灭 灭 灭 灭

1 灭 灭 灭 亮

0 灭 灭 亮 灭

1 灭 灭 亮 亮

0 灭 亮 灭 灭

d

1 灭 亮 灭 亮

0 亮 亮 亮 灭

1 灭 亮 亮 亮

0 亮 灭 灭 灭

1 亮 亮 灭 亮

任意状态

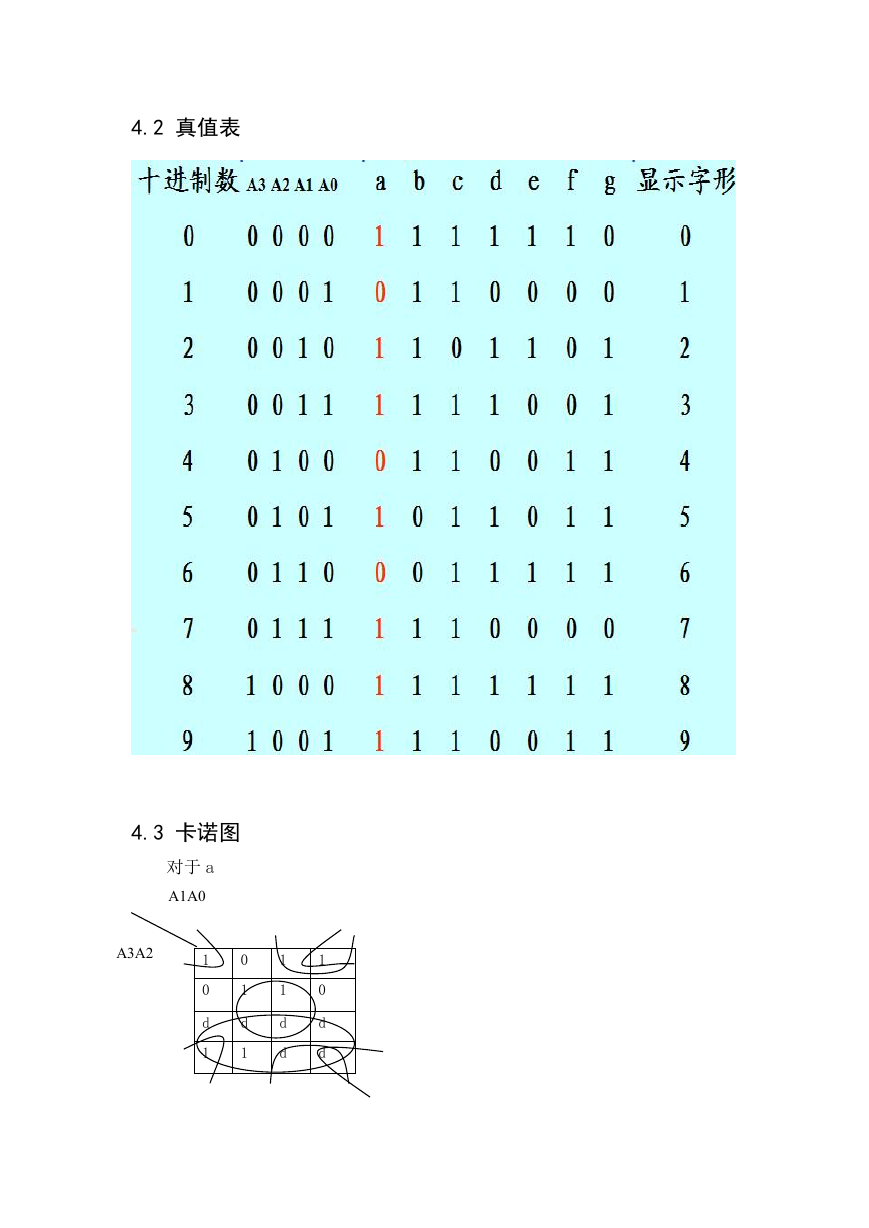

4 设计译码器:

4.1 原理

七段显示译码器 7448 的输出为高电平有效,即输出为 1 时,对应字段点亮;

输出为 0 时对应字段熄灭。输入 A3,A2,A1 和 A0 接受 4 位二进制码,输出 a,b,

c,d,e,f 和 g 分别驱动七段显示器的 a,b,c,d,e,f 和 g 字段。

A3

A2

A1

A0

译

码

器

Y

Y

a

Y

Y

Y

Y

Y

a

f

g

de

b

c

�

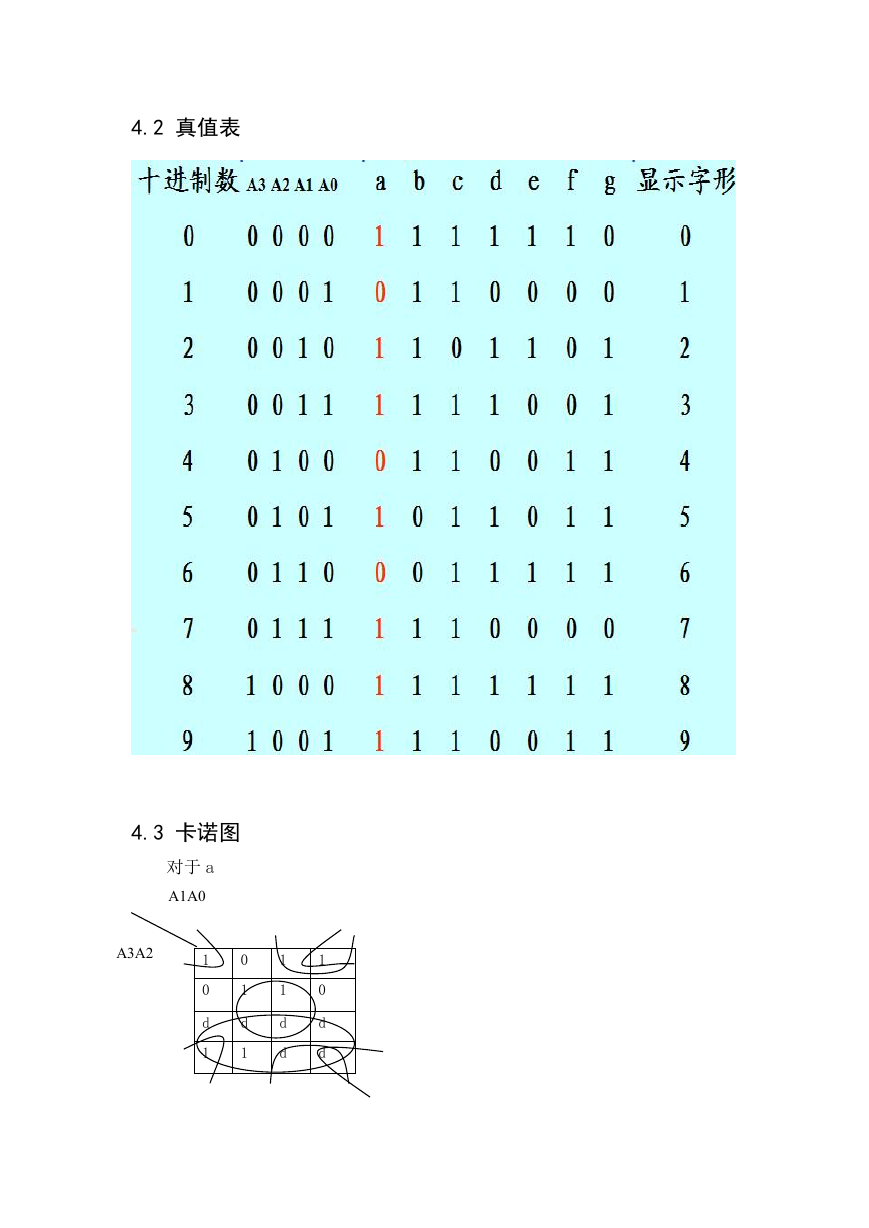

4.2 真值表

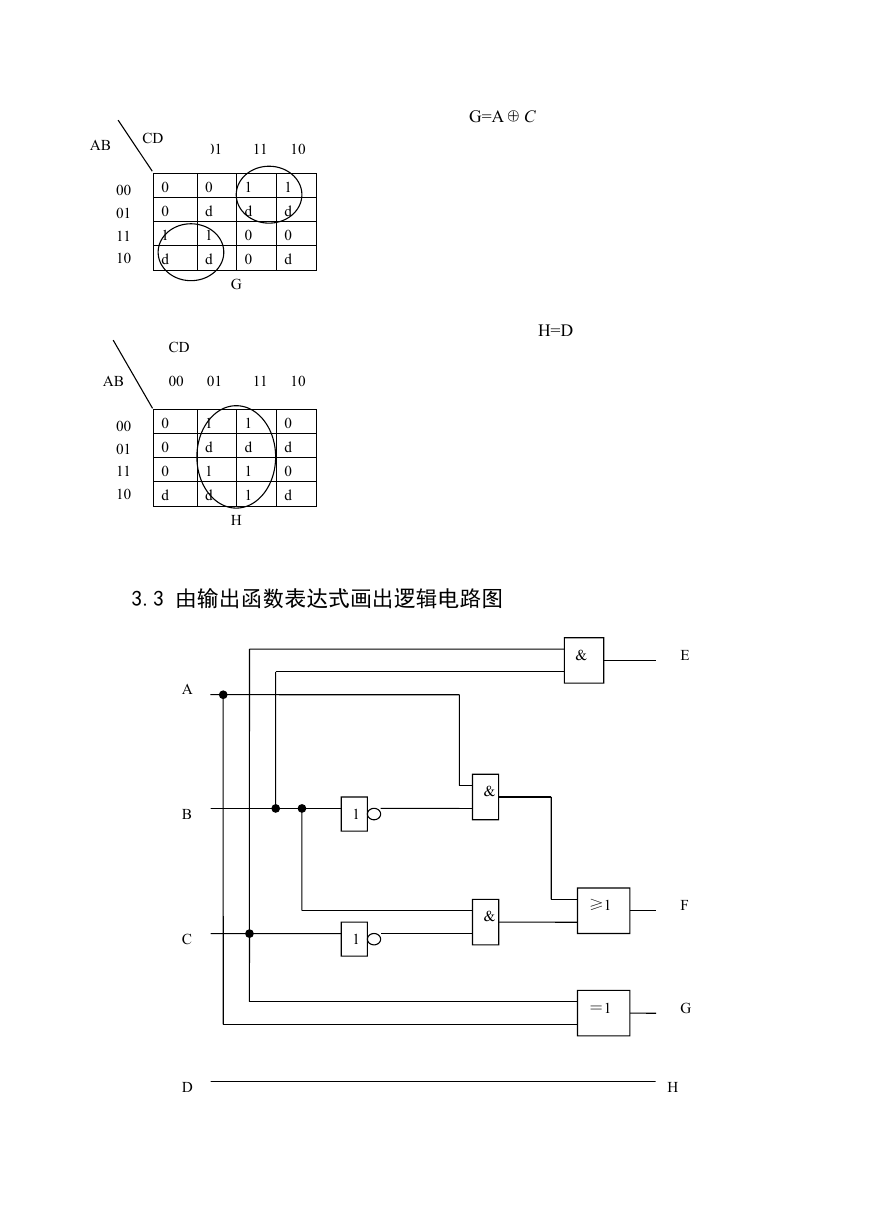

4.3 卡诺图

对于 a

A1A0

A3A2

1

0

d

1

0

1

d

1

1

1

d

d

1

0

d

d

�

a = A3 + A2 A0 + A2 A1 + A2 A0

同理可得:

b = A1 A0 + A1 A0 + A2

c = A2 A1 A0

d = A2 A0 + A2 A1 A0 + A1 A0 + A2 A1

e = A2 A0 + A1 A0

f = A1 A0

+A2 A0 + A2 A1 + A3

g = A3 A2 A1 + A2 A1 A0

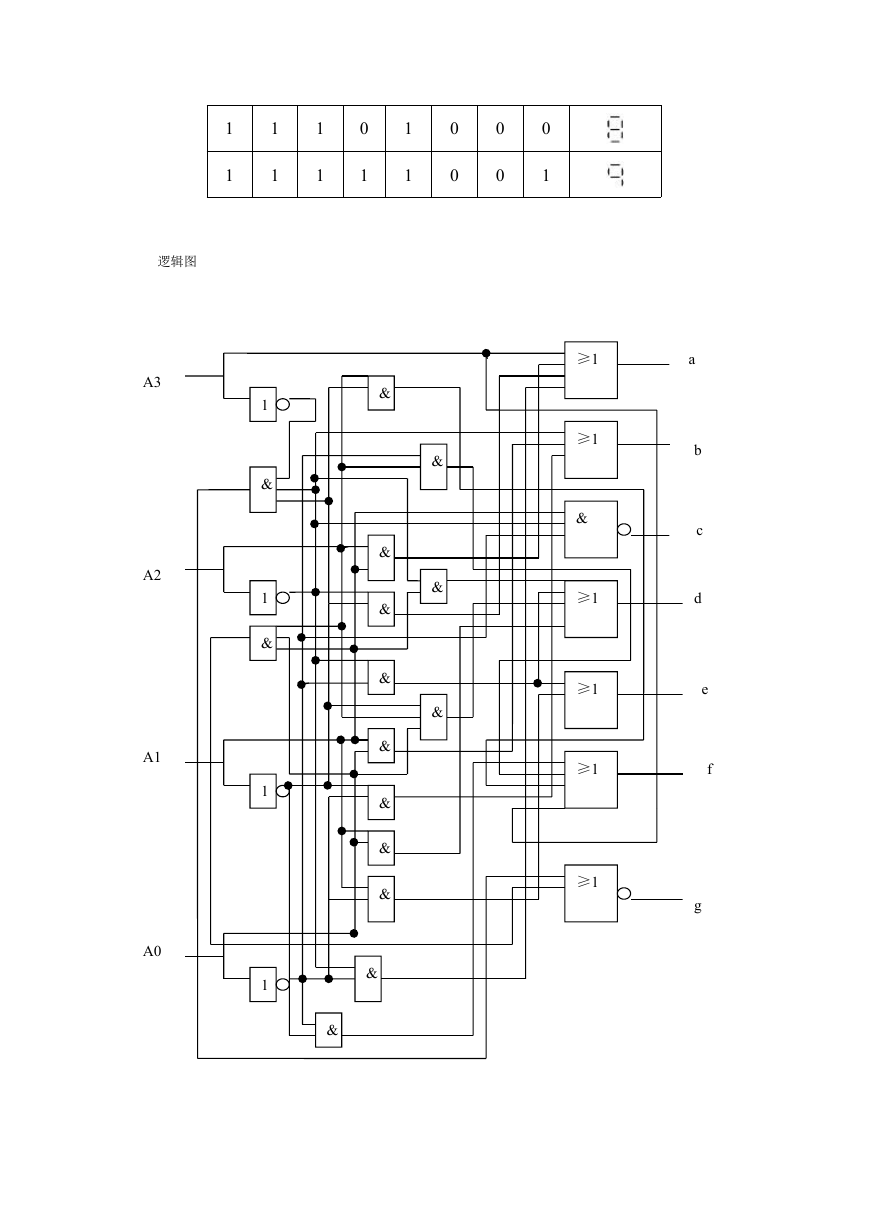

4.4 逻辑图

见下页

4.5 测试结果

将上一步输出的 E F G H 接到 A3 A2 A1 A0,并将 a,b,c,d,e,f,g 接到相应

的位置,若将 E F G H 设置为 1111,则数码管显示 ,对于其它 2421 码的值,

其相应的显示结果也正确。所以译码器连接正确。

G

0

A

0

B

0

F

0

C

0

D

0

E

0

0

0

0

0

1

1

1

0

0

0

1

0

1

1

0

0101~1010

0

1

1

1

0

0

1

0

1

0

1

0

1

0

0

0

0

d

0

0

0

0

0

0

1

d

1

1

1

0

1

1

0

d

0

1

1

H

0

1

0

1

0

d 任意状态

1

0

1

�

1

1

1

1

1

1

0

1

1

1

0

0

0

0

0

1

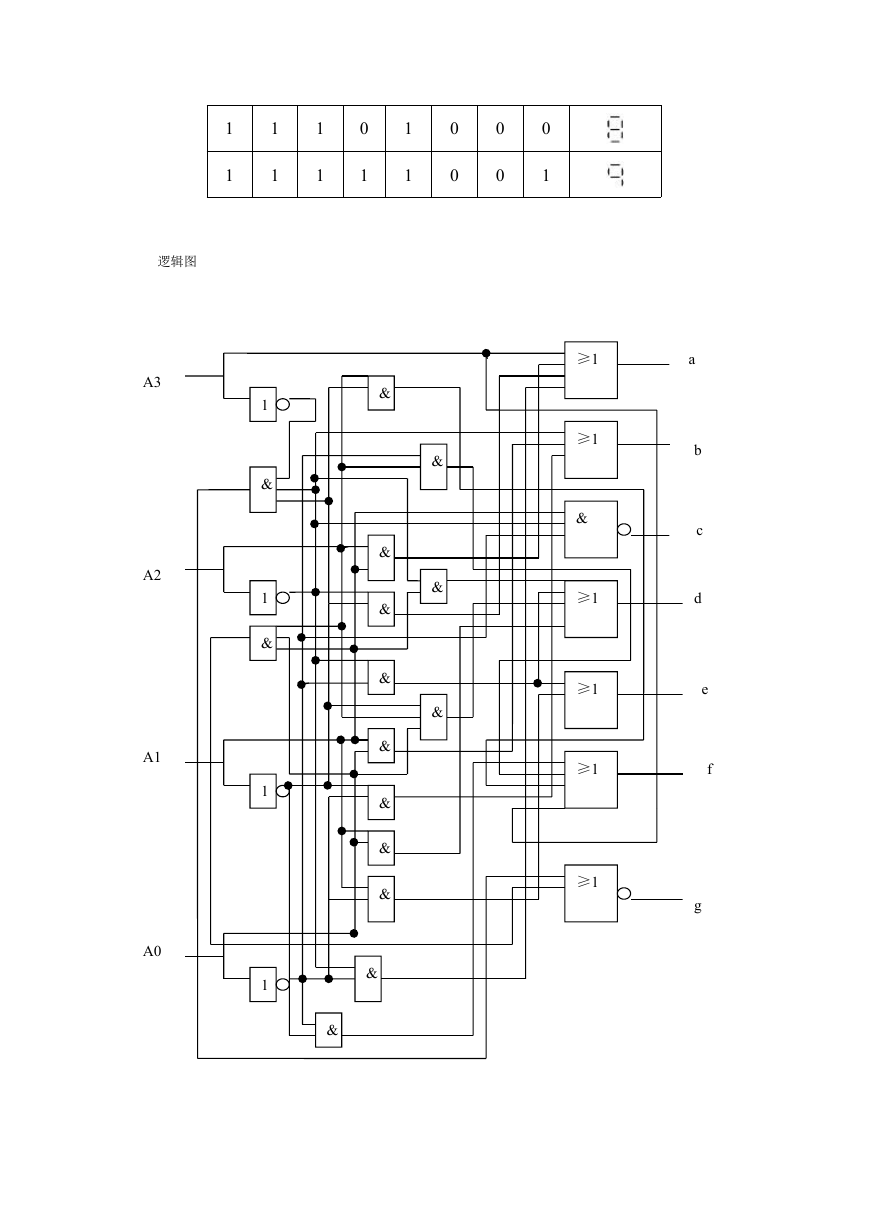

逻辑图

A3

A2

A1

A0

1

&

1

&

1

1

&

&

&

&

&

&

&

&

&

&

&

&

&

≥1

≥1

&

≥1

≥1

≥1

≥1

a

b

c

d

e

f

g

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc