第 44 卷

2011 年

第 3 期

3 月

M ICROM OTORS

Vol. 44. No. 3

Mar. 2011

基于 FPGA 的一种新型数字鉴频鉴相器的设计

李海滨1,2 ,房建成1,2 ,魏 彤1,2

( 1. 北京航空航天大学 仪器科学与光电工程学院,北京 100191;

2. 新型惯性仪表与导航系统技术国防重点学科实验室,北京 100191)

摘 要: 对于电机的锁相控制,需要对相差进行 PI 性质的环路滤波,但现有的锁相环中鉴频鉴相器输出为相差脉冲

而非数字量,难以直接进行 PI 特性的环路滤波。该文提出了一种基于 FPGA 的新型数字鉴频鉴相器,通过对晶振时

钟的非整数分频获取准确的参考时钟,基于触发器计数机制实现了 PFD 相差脉冲的数字量化,且可以输出频差数字

量。利用 VHDL 硬件描述语言进行设计,在 ModelSim 软件中进行仿真,并在 EPF10K40 型 FPGA 芯片中进行综合实

现,仿真和实验结果验证了该方法的正确性和有效性,为电机锁相控制中环路滤波参数的调整及控制算法的改进提

供了便利条件。

关键词: 高速电机锁相控制; PI 环路滤波; 数字鉴频鉴相器; FPGA; VHDL

中图分类号: TM301. 2; TM355

文献标志码: A

文章编号: 1001-6848( 2011) 03-0084-05

A Digital PFD Design for Phase - locked Loop Control Based on FPGA

LI Haibin1,2 ,FANG Jiancheng1,2 ,WEI Tong1,2

( 1. School of Instrumentation Science & Opto-electronics Engineering,Beijing University of Aeronautics and

Astronautics,Beijing 100191,China; 2. Key Laboratory of Fundamental Science for National Defense of

Novel Inertial Instrument and Navigation System Technology,Beijing 100191,China)

Abstract: A PI loop filter is needed for PLL control of motor,but the normal PFD has an output of phase er-

ror pulse instead of numeric digitals in phase-locked loop,which makes it hard to design a PI loop filter u-

sing pulse output. This paper proposed a novel digital phase-frequency detector based on FPGA. Numeric

output of phase and frequency error was realized based on flip-flop counter mechanism and a precise refer-

ence clock was achieved with method of a non-integer division of crystal clock. VHDL hardware description

language was used to design the modules,and ModelSim was introduced to implement logic and sequential

simulation. An experiment was carried on in Altera EPF10K40 chip. Both the simulation and experimental

results verify the correctness and validity of the method,which greatly enhance the convenience of adjust-

ment of parameters and improvement of control algorithms.

Key words: PLL control of high-speed motor; PI loop filter; digital phase-frequency detector; FPGA; VHDL

0 引 言

度决定。为了达到高的速率稳定度( 优于 0. 02% ) ,

电 机 的 稳 速 控 制 采 用 全 数 字 锁 相 环 进 行 电 机 锁 相

锁相环是频率和相位的同步控制系统,实现输

控制。

入参考信号和反馈信号的频率相等,相位差恒定。

全数字锁相环路( ADPLL) ,以及最近出现的纯

利用锁相环技术可实现数字信号的同步,将这个思

想引入电机的速度控制系统中,则能够实现稳态精

度很高的转速控制[1]。

磁悬浮控制力矩陀螺系统由高速转子系统、磁

轴承系统和框架系统组成。高速转子系统采用永磁

直流无刷电机驱动,其中输出力矩的精度主要由高

软件锁相环( SPLL) 。全数字锁相环( ADPLL) 与传统

的模拟锁相环和模数混合锁相环相比,不含外部分

立元件,因此关键参数不会因为元件的离散而改变,

具有精度高且不受温漂和器件老化影响的优点[2]。

由于纯软件锁相环( SPLL) 的计算量大,要求计算周

期短,而电机控制算法本身也由一定的计算量,因

速无刷直流电机的速率精度和框架转动的角速率精

此 SPLL 不适合用于电机的控制。采用单片 FPGA 实

收稿日期: 2010-06-01

作者简介: 李海滨( 1987) ,硕士研究生,研究领域为无刷直流电机及其控制技术,数字逻辑系统设计。

E-mail:

lihaibin24385@ yahoo.com.cn

�

3 期

李海滨等: 基于 FPGA 的一种新型数字鉴频鉴相器的设计

F( s) = Kp +

K1

s

·58·

( 2)

现 ADPLL 具有集成度高,且易于编程修改等优点。

在电机的锁相控制中,由于 VCO ( 由电机及霍

尔传感器构成) 是一个二阶系统,因此环路滤波器的

特性一般是比例加积分的控制结构[3],而一般通用

的鉴频鉴相器的输出都是相差脉冲的形式,无法直

当鉴频鉴相器为数字量输出时,环路滤波器的

设计变得简单,如果环路滤波器的输出记为 ,输入

记为 ε[k],在采样周期为 T 的前提下对环路滤波器

接将相差量以数字量的形式表示出来。因而很难直

离散化,得到

接进行 PI 特性的数字环路滤波器的设计,且不便于

u[k]= u[k - 1]+ Kpε[k]+ ( K1 T - Kp) ε[k - 1]

环路滤波控制算法的修改和分析。

( 3)

文献[4 - 5]介绍了全数字锁相环的一些基本概

其中,环路滤波器的输入 ε[k]就是新型数字鉴

念,原理和设计方法以及相关的应用。文献[6 - 7]

频鉴相器的线性相差数字量输出。因此,数字量输

基于全数字锁相环对直流电机进行锁相控制进行了

相关的实验研究,使用伯德图对 PI,PID 特性的环

出的鉴频鉴相器有利于后续数字环路滤波器的设计

以及 Kp,Ki 参数的调整和环路滤波算法的改进。

路滤波器进行了设计分析。文献[8]使用单片 FPGA

芯片搭建了直流电机的全数字锁相环控制系统并进

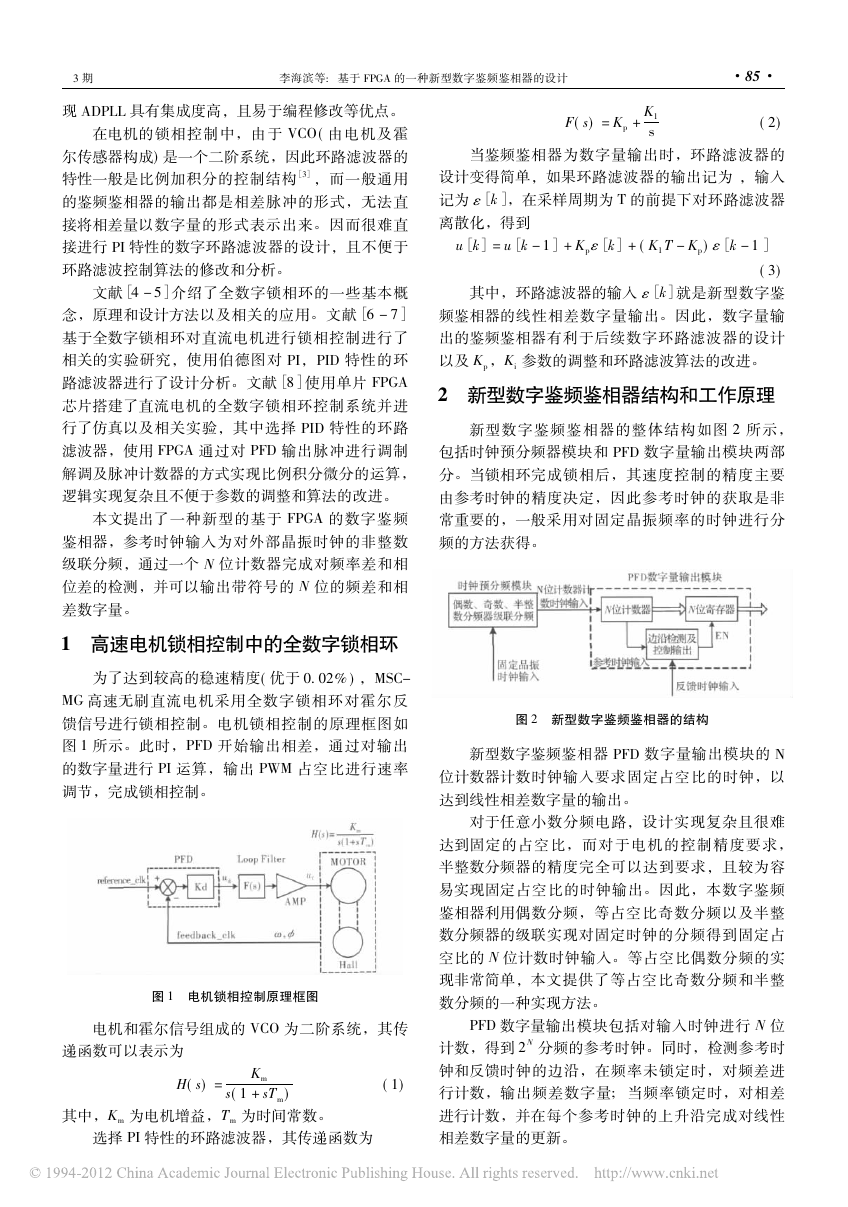

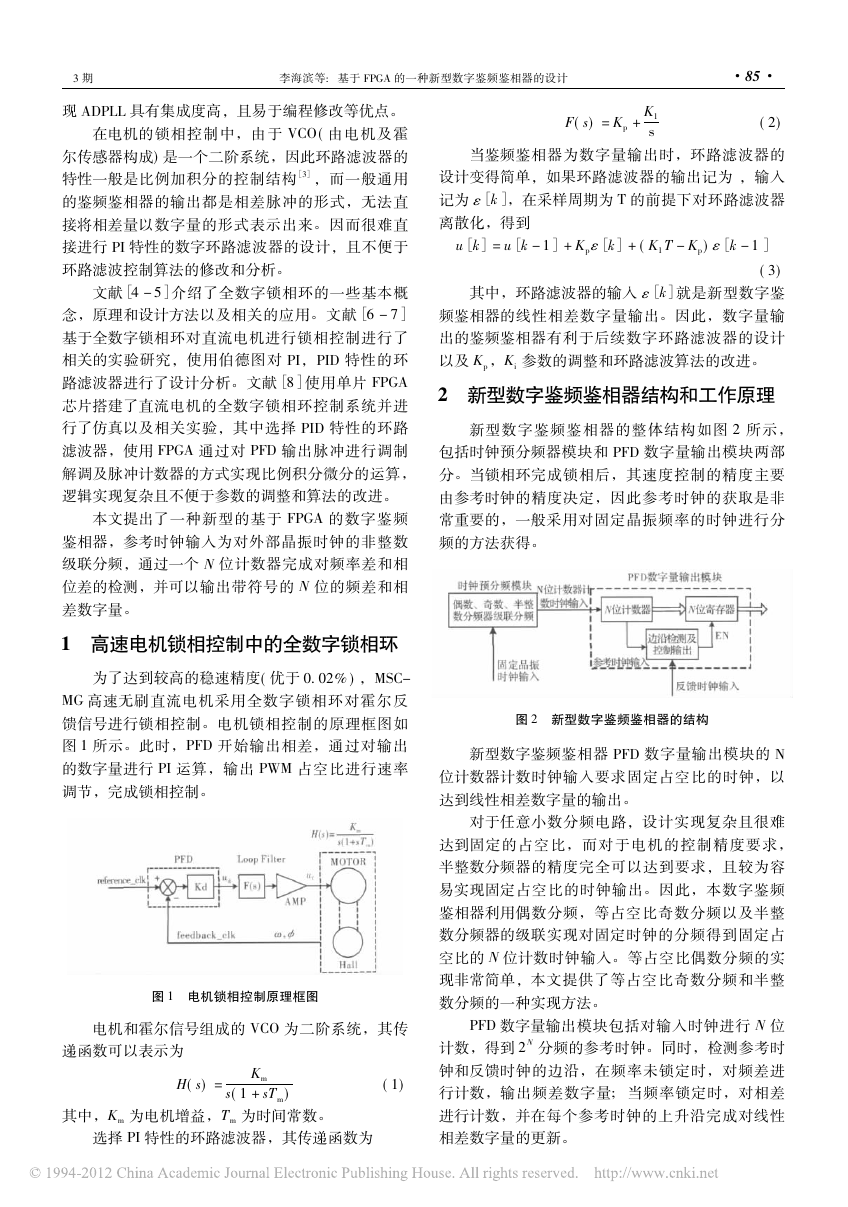

2 新型数字鉴频鉴相器结构和工作原理

行了仿真以及相关实验,其中选择 PID 特性的环路

新型数字鉴频鉴相器的整体结构如图 2 所示,

滤波器,使用 FPGA 通过对 PFD 输出脉冲进行调制

包括时钟预分频器模块和 PFD 数字量输出模块两部

解调及脉冲计数器的方式实现比例积分微分的运算,

分。当锁相环完成锁相后,其速度控制的精度主要

逻辑实现复杂且不便于参数的调整和算法的改进。

由参考时钟的精度决定,因此参考时钟的获取是非

本文提出了一种新型的基于 FPGA 的数字鉴频

常重要的,一般采用对固定晶振频率的时钟进行分

鉴相器,参考时钟输入为对外部晶振时钟的非整数

频的方法获得。

级联分频,通过一个 N 位计数器完成对频率差和相

位差的检测,并可以输出带符号的 N 位的频差和相

差数字量。

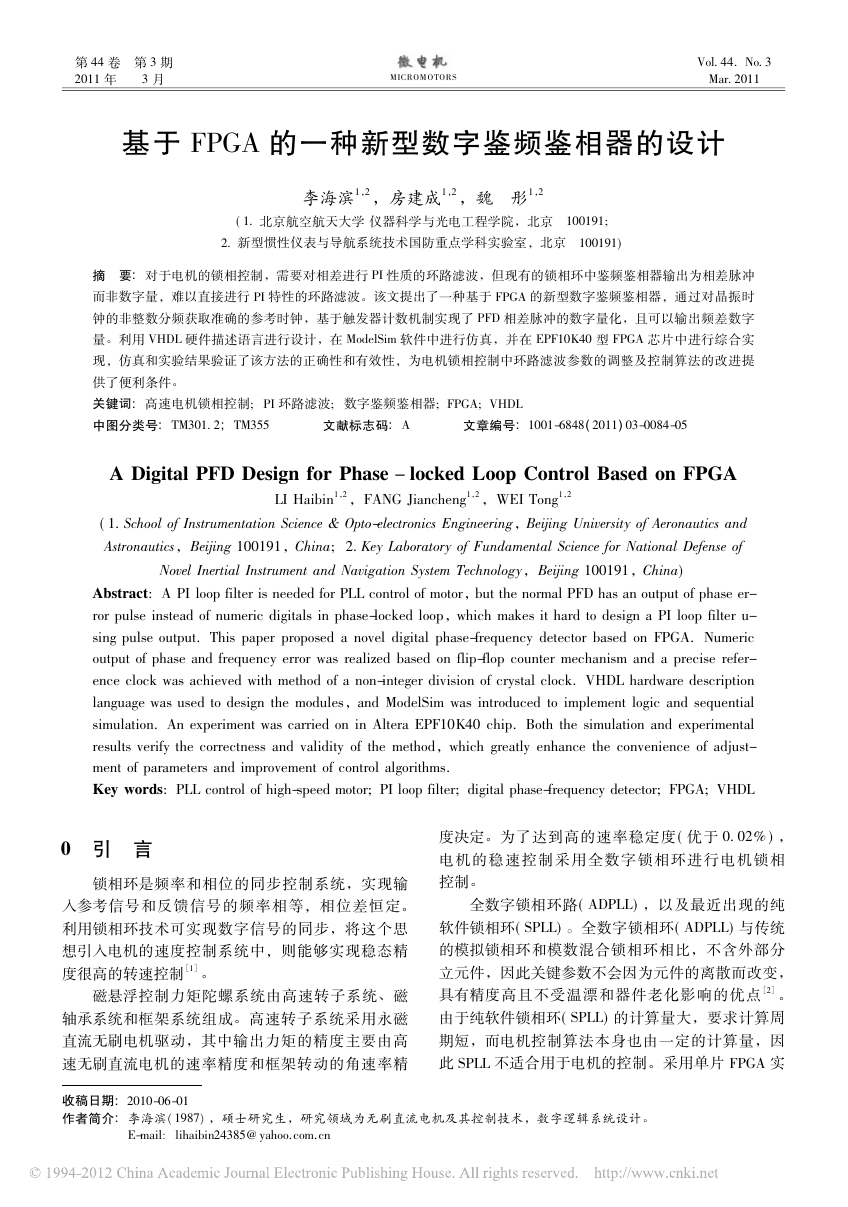

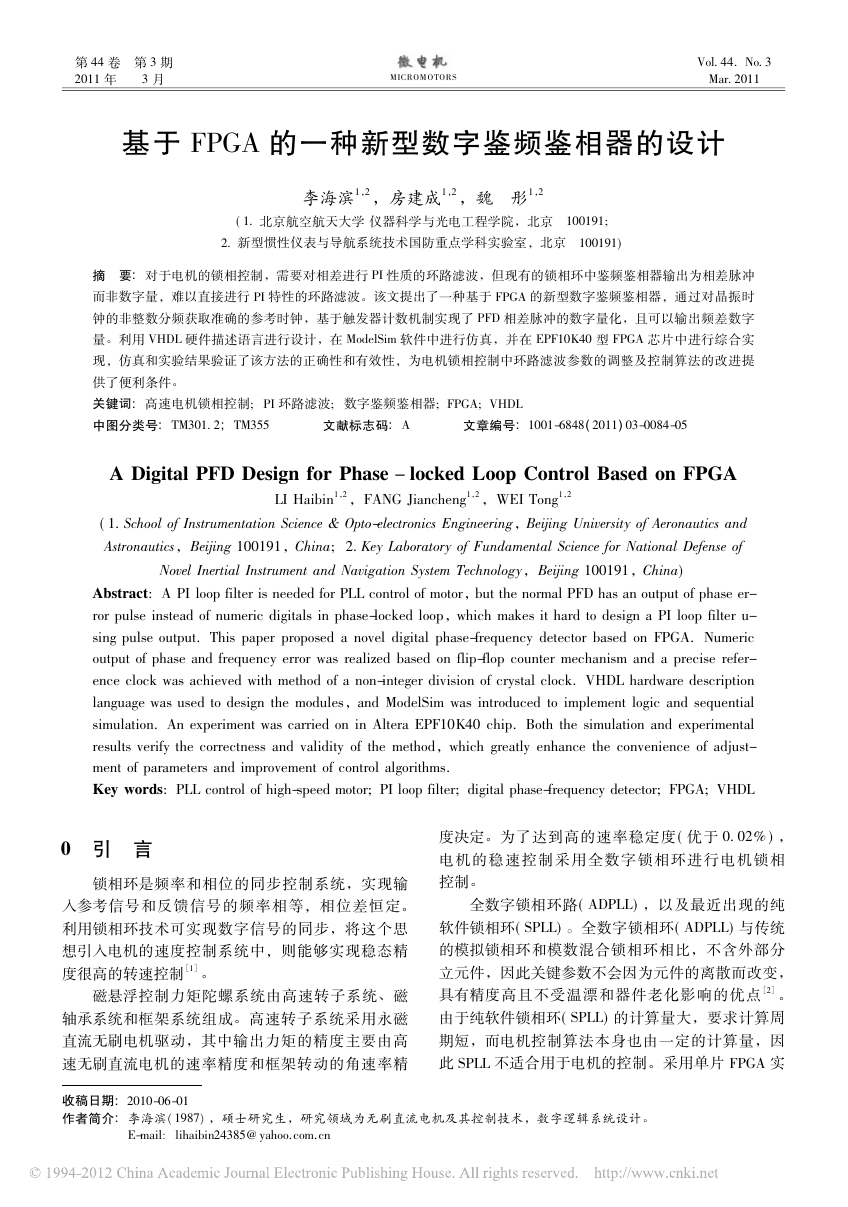

1 高速电机锁相控制中的全数字锁相环

为了达到较高的稳速精度( 优于 0. 02% ) ,MSC-

MG 高速无刷直流电机采用全数字锁相环对霍尔反

馈信号进行锁相控制。电机锁相控制的原理框图如

图 1 所示。此时,PFD 开始输出相差,通过对输出

的数字量进行 PI 运算,输出 PWM 占空比进行速率

调节,完成锁相控制。

图 2 新型数字鉴频鉴相器的结构

新型数字鉴频鉴相器 PFD 数字量输出模块的 N

位计数器计数时钟输入要求固定占空比的时钟,以

达到线性相差数字量的输出。

对于任意小数分频电路,设计实现复杂且很难

达到固定的占空比,而对于电机的控制精度要求,

半整数分频器的精度完全可以达到要求,且较为容

易实现固定占空比的时钟输出。因此,本数字鉴频

鉴相器利用偶数分频,等占空比奇数分频以及半整

数分频器的级联实现对固定时钟的分频得到固定占

空比的 N 位计数时钟输入。等占空比偶数分频的实

现非常简单,本文提供了等占空比奇数分频和半整

图 1 电机锁相控制原理框图

数分频的一种实现方法。

电机和霍尔信号组成的 VCO 为二阶系统,其传

递函数可以表示为

H( s) =

Km

s( 1 + sTm)

( 1)

其中,Km 为电机增益,Tm 为时间常数。

选择 PI 特性的环路滤波器,其传递函数为

PFD 数字量输出模块包括对输入时钟进行 N 位

计数,得到 2 N 分频的参考时钟。同时,检测参考时

钟和反馈时钟的边沿,在频率未锁定时,对频差进

行计数,输出频差数字量; 当频率锁定时,对相差

进行计数,并在每个参考时钟的上升沿完成对线性

相差数字量的更新。

�

·68·

44 卷

通过调整 N 值的大小,可以调节数字量输出的

馈信号滞后于参考信号,低 7 位的数值表明了滞后

分辨率,以达到更好的控制效果。

量的大小。当反馈信号的上升沿出现在参考信号的

2. 1 时钟预分频器模块原理

在 MSCMG 高速无刷直流电机控制系统中,当

额定转速 30000 r / min 时,霍尔反馈时钟为 500 Hz,

采用 8 位计数器以获得 8 位数字量输出,系统晶振

为 40 MHz 时钟。

为了得到 500 Hz 的参考时钟,需要对 40 MHz

的晶振时钟进行两次分频操作。

要实现占空比为 50% 的 M = 2N + 1 奇数分频电

路,本文采用计数器和 1 个或门来实现。利用输入时

钟的上升沿计数,设计一个模 M 的计数器,下降沿时

判断计数器的值并产生占空比为 1: 2N 的 M 分频器

C1; 上升沿时判断计数器的值并产生占空比为 N: N

+ 1 的 M 分频器 C0。两个分频器的输出端 C0 和 C1

相或既可实现等占空比的 M 分频器。当取 M = 125,

N = 62 的时候,就得到了等占空比的 125 分频电路。

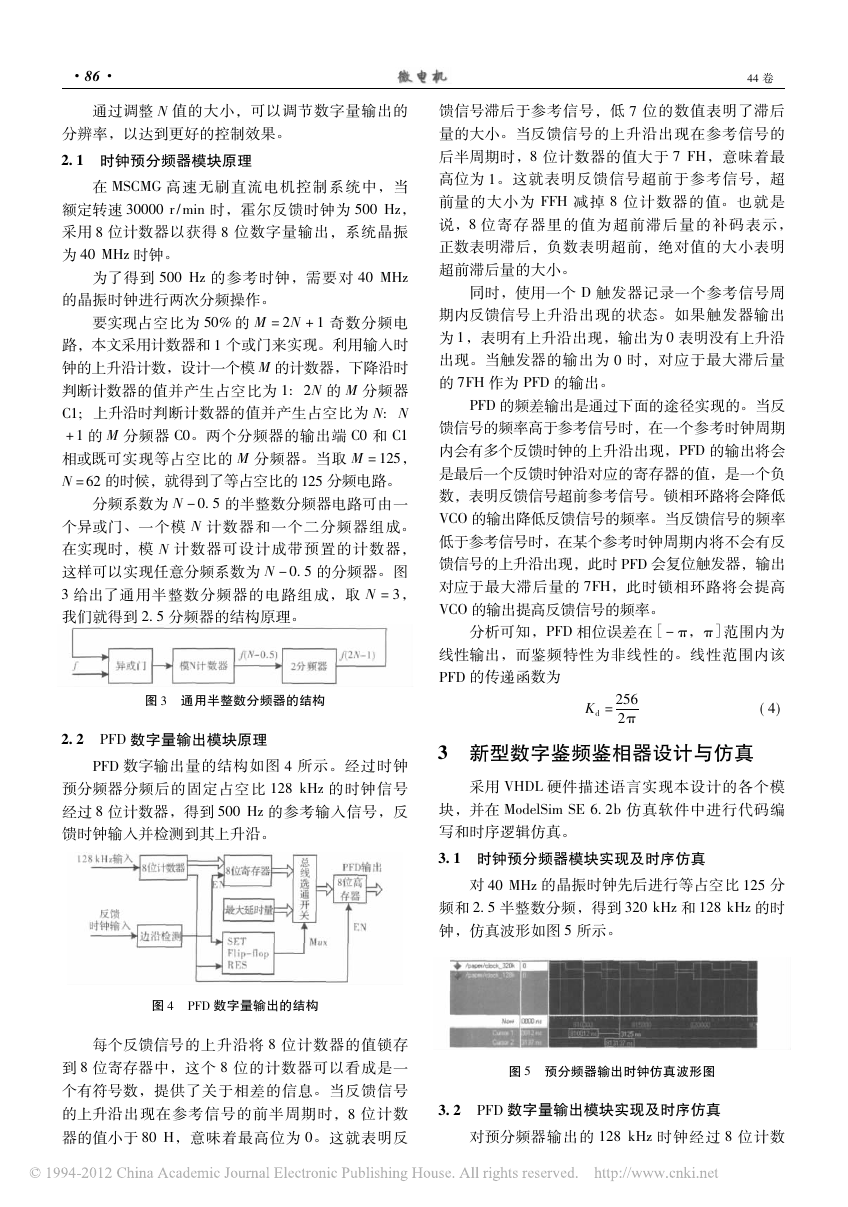

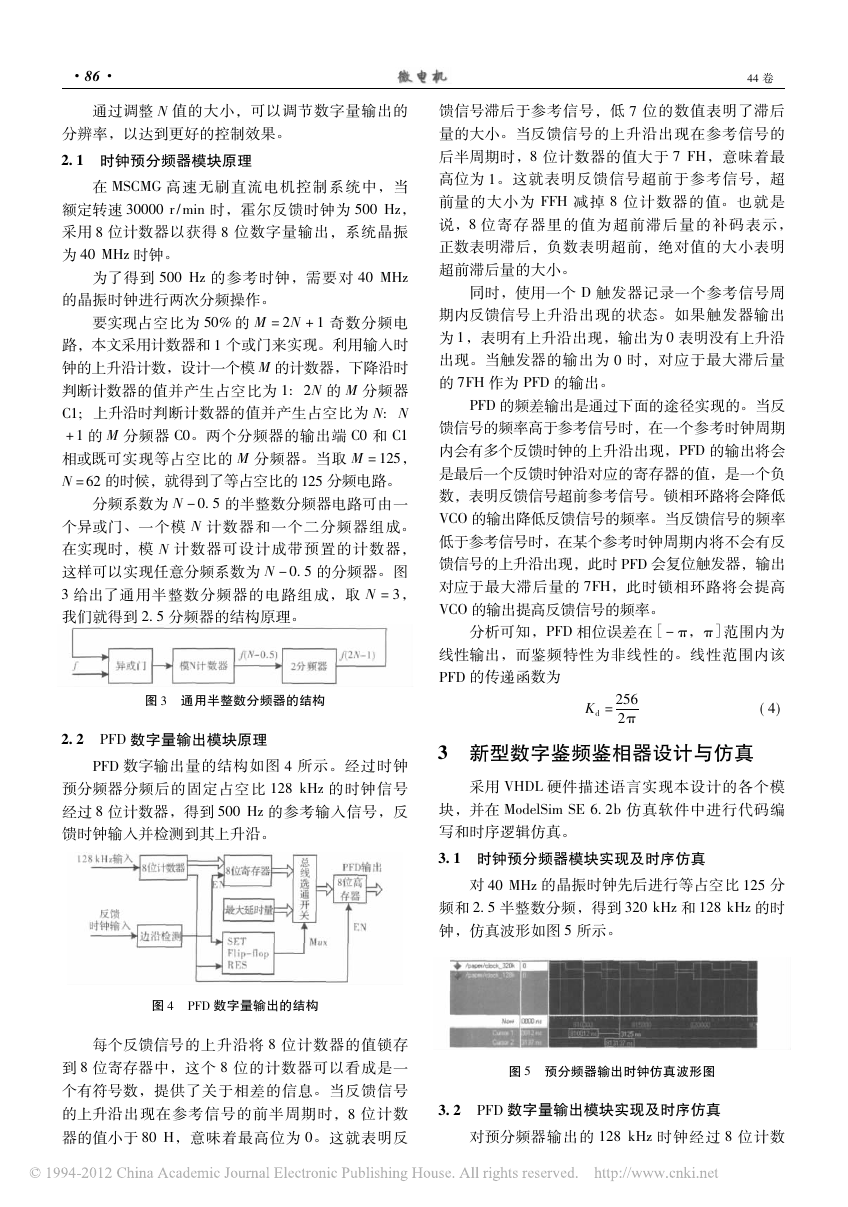

分频系数为 N - 0. 5 的半整数分频器电路可由一

个异或门、一个模 N 计数器和一个二分频器组成。

在实现时,模 N 计数器可设计成带预置的计数器,

这样可以实现任意分频系数为 N - 0. 5 的分频器。图

3 给出了通用半整数分频器的电路组成,取 N = 3,

我们就得到 2. 5 分频器的结构原理。

图 3 通用半整数分频器的结构

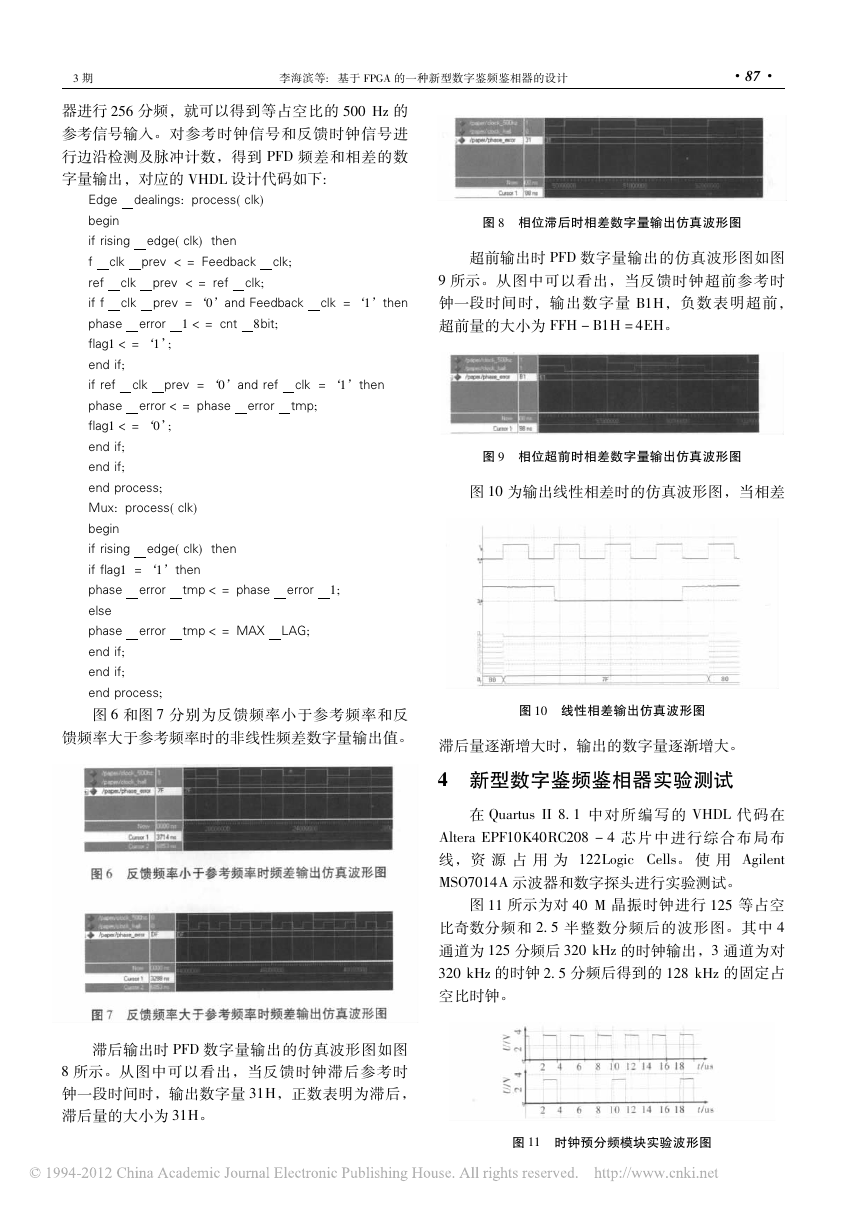

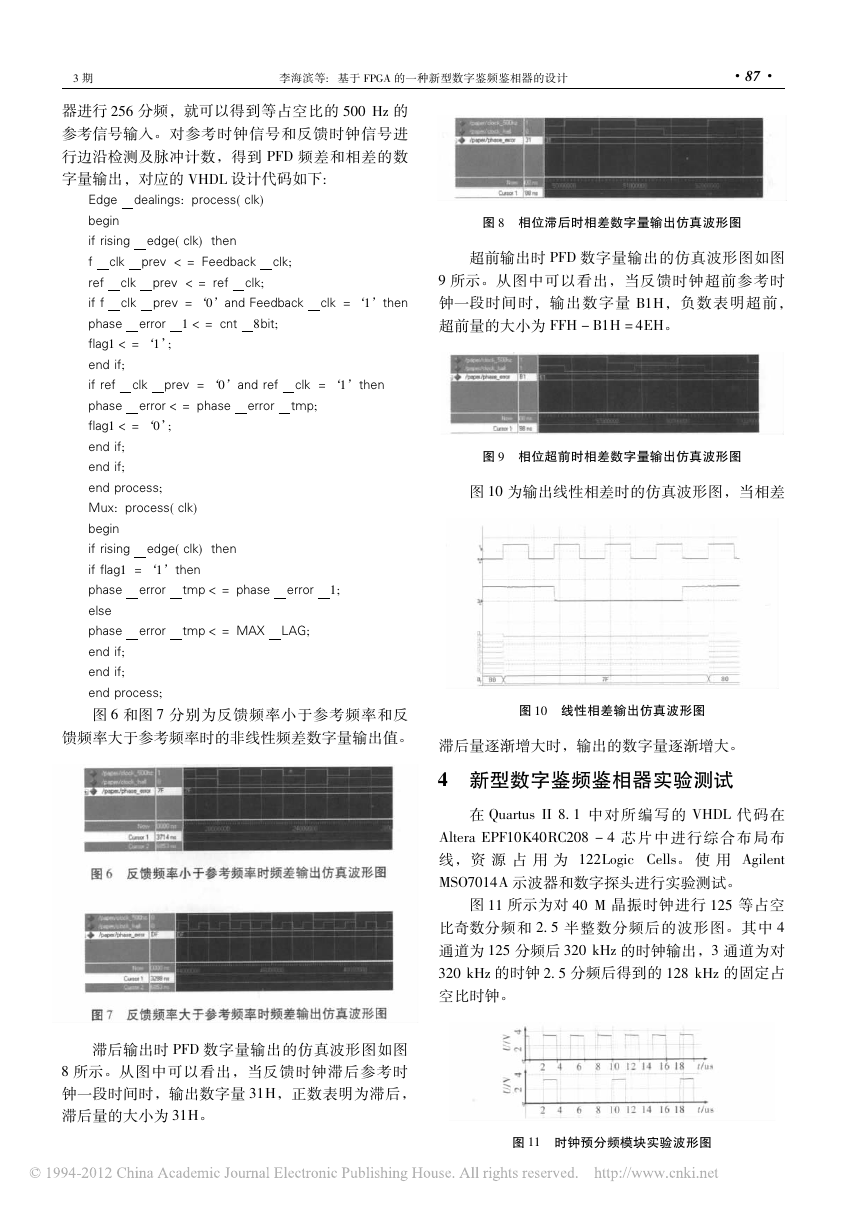

2. 2 PFD 数字量输出模块原理

PFD 数字输出量的结构如图 4 所示。经过时钟

后半周期时,8 位计数器的值大于 7 FH,意味着最

高位为 1。这就表明反馈信号超前于参考信号,超

前量的大小为 FFH 减掉 8 位计数器的 值。也 就 是

说,8 位寄 存 器 里 的 值 为 超 前 滞 后 量 的 补 码 表 示,

正数表明滞后,负数表明超前,绝对值的大小表明

超前滞后量的大小。

同时,使用一个 D 触发器记录一个参考信号周

期内反馈信号上升沿出现的状态。如果触发器输出

为 1,表明有上升沿出现,输出为 0 表明没有上升沿

出现。当触发器的输出为 0 时,对应于最大滞后量

的 7FH 作为 PFD 的输出。

PFD 的频差输出是通过下面的途径实现的。当反

馈信号的频率高于参考信号时,在一个参考时钟周期

内会有多个反馈时钟的上升沿出现,PFD 的输出将会

是最后一个反馈时钟沿对应的寄存器的值,是一个负

数,表明反馈信号超前参考信号。锁相环路将会降低

VCO 的输出降低反馈信号的频率。当反馈信号的频率

低于参考信号时,在某个参考时钟周期内将不会有反

馈信号的上升沿出现,此时 PFD 会复位触发器,输出

对应于最大滞后量的 7FH,此时锁相环路将会提高

VCO 的输出提高反馈信号的频率。

分析可知,PFD 相位误差在[- π,π]范围内为

线性输出,而鉴频特性为非线性的。线性范围内该

PFD 的传递函数为

Kd =

256

2π

( 4)

3 新型数字鉴频鉴相器设计与仿真

预分频器分频后的固定占空比 128 kHz 的时钟信号

采用 VHDL 硬件描述语言实现本设计的各个模

经过 8 位计数器,得到 500 Hz 的参考输入信号,反

块,并在 ModelSim SE 6. 2b 仿真软件中进行代码编

馈时钟输入并检测到其上升沿。

写和时序逻辑仿真。

3. 1 时钟预分频器模块实现及时序仿真

对 40 MHz 的晶振时钟先后进行等占空比 125 分

频和 2. 5 半整数分频,得到 320 kHz 和 128 kHz 的时

钟,仿真波形如图 5 所示。

图 4 PFD 数字量输出的结构

每个反馈信号的上升沿将 8 位计数器的值锁存

到 8 位寄存器中,这个 8 位的计数器可以看成是一

个有符号数,提供了关于相差的信息。当反馈信号

的上升沿出现在参考信号的前半周期时,8 位计数

图 5 预分频器输出时钟仿真波形图

3. 2 PFD 数字量输出模块实现及时序仿真

器的值小于 80 H,意味着最高位为 0。这就表明反

对预分频器输出的 128 kHz 时钟经过 8 位计数

�

3 期

李海滨等: 基于 FPGA 的一种新型数字鉴频鉴相器的设计

·78·

器进行 256 分频,就可以得到等占空比的 500 Hz 的

参考信号输入。对参考时钟信号和反馈时钟信号进

行边沿检测及脉冲计数,得到 PFD 频差和相差的数

字量输出,对应的 VHDL 设计代码如下:

Edge

dealings: process( clk)

begin

if rising

edge( clk)

then

f

clk

prev < = Feedback

clk;

ref

if f

clk

clk

prev < = ref

clk;

图 8 相位滞后时相差数字量输出仿真波形图

超前输出时 PFD 数字量输出的仿真波形图如图

9 所示。从图中可以看出,当反馈时钟超前参考时

prev = ‘0’and Feedback

clk = ‘1’then

钟一段时间时,输出数字量 B1H,负数表明超前,

phase

error

1 < = cnt

8bit;

超前量的大小为 FFH - B1H = 4EH。

flag1 < = ‘1’;

end if;

if ref

clk

prev = ‘0’and ref

clk = ‘1’then

phase

error < = phase

error

tmp;

flag1 < = ‘0’;

end if;

end if;

end process;

Mux: process( clk)

begin

if rising

edge( clk)

then

if flag1 = ‘1’then

phase

error

tmp < = phase

error

1;

else

phase

error

tmp < = MAX

LAG;

end if;

end if;

end process;

图 6 和图 7 分别为反馈频率小于参考频率和反

馈频率大于参考频率时的非线性频差数字量输出值。

图 9 相位超前时相差数字量输出仿真波形图

图 10 为输出线性相差时的仿真波形图,当相差

图 10 线性相差输出仿真波形图

滞后量逐渐增大时,输出的数字量逐渐增大。

4 新型数字鉴频鉴相器实验测试

在 Quartus II 8. 1 中 对 所 编 写 的 VHDL 代 码 在

Altera EPF10K40RC208 - 4 芯 片 中 进 行 综 合 布 局 布

线, 资 源 占 用 为 122Logic Cells。 使 用 Agilent

MSO7014A 示波器和数字探头进行实验测试。

图 11 所示为对 40 M 晶振时钟进行 125 等占空

比奇数分频和 2. 5 半整数分频后的波形图。其中 4

通道为 125 分频后 320 kHz 的时钟输出,3 通道为对

320 kHz 的时钟 2. 5 分频后得到的 128 kHz 的固定占

空比时钟。

滞后输出时 PFD 数字量输出的仿真波形图如图

8 所示。从图中可以看出,当反馈时钟滞后参考时

钟一段时间时,输出数字量 31H,正数表明为滞后,

滞后量的大小为 31H。

图 11 时钟预分频模块实验波形图

�

·88·

44 卷

图 12 表示了当反馈时钟小于参考时钟时,输出

频差数字量的波形图,输出的数字量 7FH 对应于相

差最大滞后量,此时锁相环路将会提高 VCO 的输出

增大反馈信号的频率。图 13 表示了反馈时钟频率大

于参考时钟时时,输出频差数字量的波形图,输出

的数字量 E0H 是负数,此时锁相环路将会降低 VCO

的输出减小反馈信号的频率。由图 13 和图 14 可知,

频差输出量为非线性的。

从图 14 中可以看出,当反馈时钟超前参考时钟

一段时间时,8 位数据总线输出数字量 D8H,负数

表明超前,超前量的大小为 FFH - D8H = 27H。

从图 15 中可以看出,当反馈时钟滞后参考时钟

一段时间时,8 位数据总线输出数字量 39H,整数表

明滞后,滞后量的大小为 39H。

图 16 通过给定不断线性增大的相差滞后,可以

输出线性增大的正的数字量输出,表明了线性相差

图 16 反馈时钟相位滞后参考时钟时的线性相差输出

5 结 论

本文针对电机锁相控制环路滤波器的特点,提

出了一种基于 FPGA 的新型数字鉴频鉴相方法,并

设计实现了 40 M 晶振时钟输入下,输出 8 位带符号

相差和频差数字量的数字鉴频鉴相器。本鉴频鉴相

器包含了对晶振时钟的一次半整数分频操作和一次

等占空比奇数分频操作,以获得准确的计数脉冲和

参考时钟,并通过触发器计数机制输出线性相差和

非线性频差的数字量,极大地方便了环路滤波参数

的调整及控制算法的改进。利用 VHDL 硬件描述语

言进行 设 计,在 ModelSim 软 件 中 进 行 仿 真,并 在

EPF10K40 型 FPGA 中进行综合实现,仿真和实验结

果验证了该方法的正确性和有效性,为电机锁相控

制中环路滤波参数的调整及控制算法的改进提供了

便利条件,可以用于 MSCMG 高速无刷直流电机进

行锁相控制。

参考文献

[1] 薛峰,吴捷. 锁相技术在电机调速系统中的应用概述[J]. 微电

机,1999,32( 3) : 26 - 29.

[2] Roland E. Best. 锁相环设计、仿真与应用[M]. 5 版. 李永明,

译. 北京: 清华大学出版社,2007.

输出 的 正 确 性。 其 中[- π,0]对 应 的 数 字 量 为

[3] Floyd M. Gardner. 锁相环技术[M]. 3 版. 姚剑清,译. 北京:

[7FH,0],[0,π]对应的数字量为[FFH,80H]。

人民邮电出版社,2007.

[4] Y. R. Shayan,T. Le - Ngoc. All Digital Phase - locked Loop:

Concepts,Design and Applications[J].

IEE Proceedings,1989,

136( 1) .

[5] Guan - Chyun Hsieh,James C. Hung. Phase - locked Loop Tech-

niques - A Survey[J]. IEEE Transactions on Industrial Electronics,

1996,43( 6) .

[6] H. Machida,F. Kobayashi. PLL / PID Motor Control System by U-

sing Time - domain Operation of PWM Signal[C]. Kagawa Univer-

sity: SICE Annual Conference 2007,2007.

[7] E. S. N. Prasad,G. K. Dubey,S. S. Prabhu. High - perform-

ance DC Motor Drive with Phase - locked Loop Regulation[J].

IEEE Trans. and. Appl. ,1985,IA - 21( 1) : 192 - 201.

[8] H. Machida F. Kobayashi. An Implementation of the One - chip

PLL / PWM Motor Control System[J]. Trans. IEEJ - C,2002,122

- C( 12) : 2144 - 2148.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc