基于单片机的简易逻辑分析仪

目 录

第 1 节 引 言……………………………………………………………………………3

1.1 系统概述………………………………………………………………………3

1.1.1 系统的特点………………………………………………………………4

1.1.2 系统的功能………………………………………………………………4

第 2 节 系统主要硬件电路设计…………………………………………………………5

2.1 系统结构框图…………………………………………………………………5

2.2 主体控制模块…………………………………………………………………5

2.3 系统硬件的主体实现…………………………………………………………7

2.3.1 数字信号发生器模块的电路设计与实现……………………………7

2.3.2 主控系统模块的电路设计与实现……………………………………8

2.3.3 LED 显示模块的电路设计与实现……………………………………10

2.3.4 硬件的抗干扰措施…………………………………………………12

第 3 节 系统软件设计…………………………………………………………………13

3.1 系统软件流程…………………………………………………………………13

3.2 中断服务子程序………………………………………………………………15

3.3 AT24C04 程序设计……………………………………………………………15

第 4 节 结束语…………………………………………………………………………19

参 考 文 献 … … … … … … … … … … … … … … … … … … … … … … … … … … … …20

1

�

基于单片机的简易逻辑分析仪

第1节 引 言

信息时代是数字化的时代,数字技术的高速发展,出现了以高性能计算机为核心

的数字通信、数字测量的数字系统。在研究这些数字系统产品的应用性能的同时也必

须研究在设计、生产和维修他们的过程中,如何验证数字电路设计的合理性、如何协

调硬件及其驱动应用软件的工作、如何测量其技术指标以及如何评价其性能。逻辑分

析仪的出现,为解决这些问题提供了可能。

随着数字系统复杂程序的增加,尤其是微处理器的高速发展,用示波器测试己显

得有些无能为力。1973 年在美国应运而生的逻辑分析仪(Logic Analyzer),能满足

数字域测试的各种要求。它属于总线分析仪一类的数据域测试仪器*主要用于查找总

线(或多线)相关故障.同时对于数据有很强的选择能力和跟踪能力,因此,逻辑分析

汉在数字系统的测试中获得了广泛的应用。

逻辑分析仪(Logic Analyzer)是以逻辑信号为分析对象的测量仪器。是一种数

据域仪器,其作用相当于时域测量中的示波器。正如在模拟电路错误分析中需要示波

器一样,在数字电路故障分析中也需要一种仪器,它适应了数字化技术的要求,是数

字、逻辑电路、仪器、设备的设计、分析及故障诊断工作中不可按少的工具。在测试

数字电路、研制和维修电子计算机、微处理器以及各种集成化数字仪表和装置中具有

广泛的用途;还是数字系统设计、侦错、软件开发和仿真的必备仪器;作为硬件设计

中必不可少的检测工具,还可将其引入实验教学中,建立直观感性的印象,提升学生

的硬件设计能力,可以全面提高教学质量; 随着科技的发展,LA 在多通道、大存储

量、高采样速率、多触发功能方面得到更快的发展,在航天、军事、通信等数字系统

领域得到越来越广泛的应用。

我们从上面可以看出逻辑分析仪在各个领域的广泛应用。那么我们在学习、应

用的同时设计并制作一个简易的逻辑分析仪就显的意义重大了,这样这个过程既可以

让我们更加深入理解其原理,又可以提高动手设计并制作整个系统电路的能力,还可

以将其作为简易仪器应用于以后的实验中。

1.1 系统概述

因在本节中,我们将对简易逻辑分析仪的应用进行分析。给出它的特点,能实现

的功能以及系统的简单操作

1.1.1 系统的特点

逻辑分析仪也称逻辑示波器,它是用来分析数字系统逻辑关系的一种仪器。逻辑

2

�

分析仪的主要作用有二个:一是用于观察的形式显示出数字系统的运行情况,相当于

扩展了人们的视野,起一个逻辑显示器的作用;二是对系统运行进行分析和故障诊断。

一般的逻辑分析仪是由数据获取和数据显示两大部分组成的。前者捕获并存储

所要观察分析的数据,后者用多种形式显示这些数据。在这里,关键是触发.它的作

用是在被分析的数据流中按索特定的数据字。一旦发现这个数据字,便产生触发信号

去控制和存储有效数据。因此,它决定了观察的数据窗口在数据流中的位置。

本设计具有以下特点:

1、具有足够多的输入通道,一般的示波器只有 2 路通道,本设计了 8 路输入通道。

2、多种触发方式:设置了单字触发和三级触发两种触发模式

3、具有记忆能力:采用 EEPROM 实现数据的掉电存储

本设计的主要特色:

★ 数字信号发生器使用 AT89C2051 单片机来控制,达到了高精度的信号输出。

★ 数字信号的逻辑状态显示也用 AT89C2051 单片机辅助主 CPU 系统实现。

★ 使用 D/A 电阻网络,结合单片机对信号幅度进行灵活地控制。

★ 采用发光二极管来指示电路测试点,一目了然,便于调试。

★ 在系统的软硬件设计中均加入了运行良好的抗干扰措施。

★ 强大的软件设计功能,大大简化了硬件电路。

1.1.2 系统的功能

逻辑分析仪的逻辑分析仪(简称 LA)是新型的数据域分析仪器,它有许多

独特的功能。把这些功能分成取数、触发、存储、显示等几个方面,

本系统实现的功能是:

(1)能产生 8 路可预置的循环移位逻辑信号序列,输出信号为 TTL 电平,序列时钟

频率为 100Hz,并能够重复输出。

(2)单次触发采集存储显示,单次触发方式是指在满足触发条件后,能对被测信号

进行一次采集、存储。之后输出通过 DAC 转化为模拟电压后输出,在示波器上显示

出 8 路信号,并能显示触发位置。

(3)任意两通道三级触发存储显示,由键盘输入 8 路中任意 2 通道的通道号及 3 级

触发字,当指定通道的触发字连续依次满足时,能对被测信号进行一次采集,存储,

送 DAC 后输出显示。同时在屏幕上标记出 3 级触发字的位置。

(4)显示触发字的位置,可以在模拟示波器显示屏上对触发字进行标记。

(5)显示可以移动的光标,可以通过键盘的加、减控制光标在水平方向的坐标。

(6)翻页显示,可以用键盘控制翻页显示,每隔 32bit 为一页的内容,扩展了存储深

度。

第2节 系统主要硬件电路设计

3

�

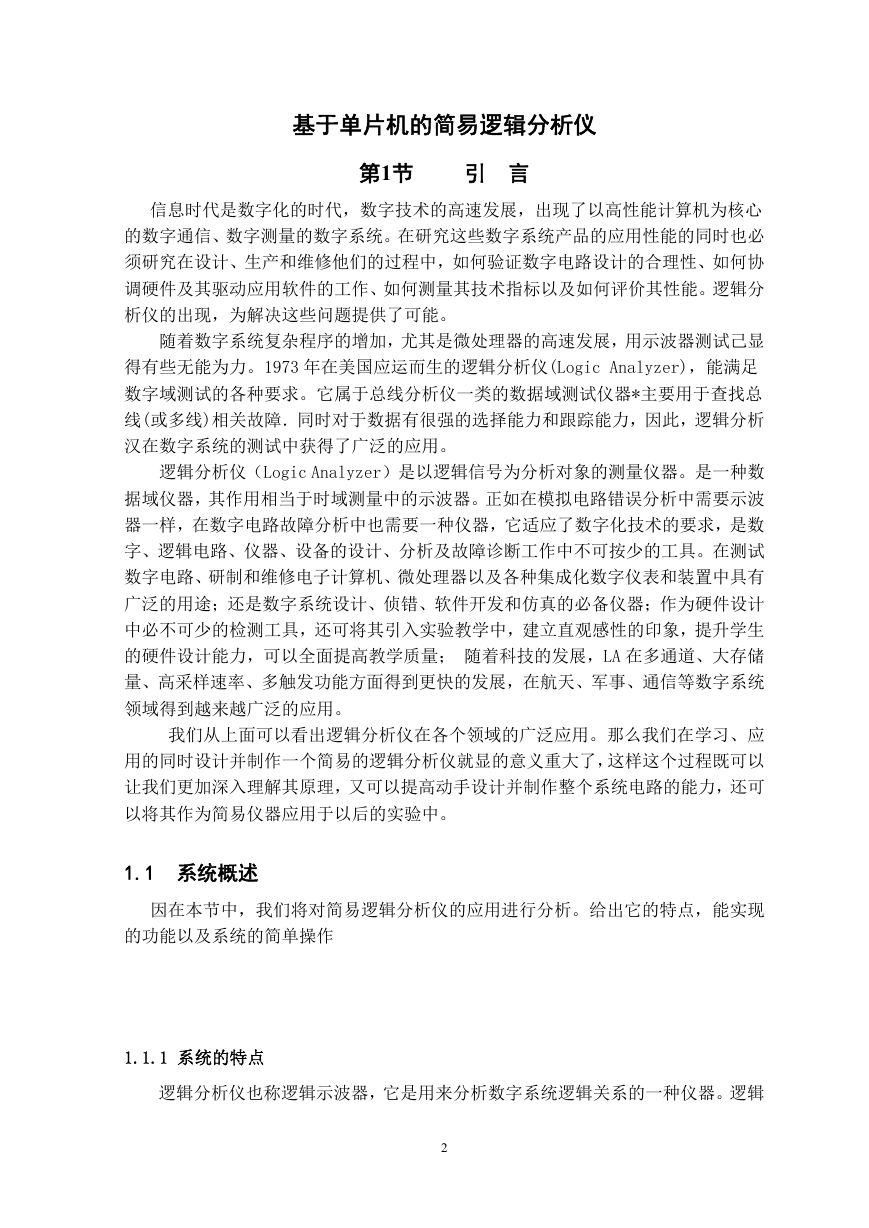

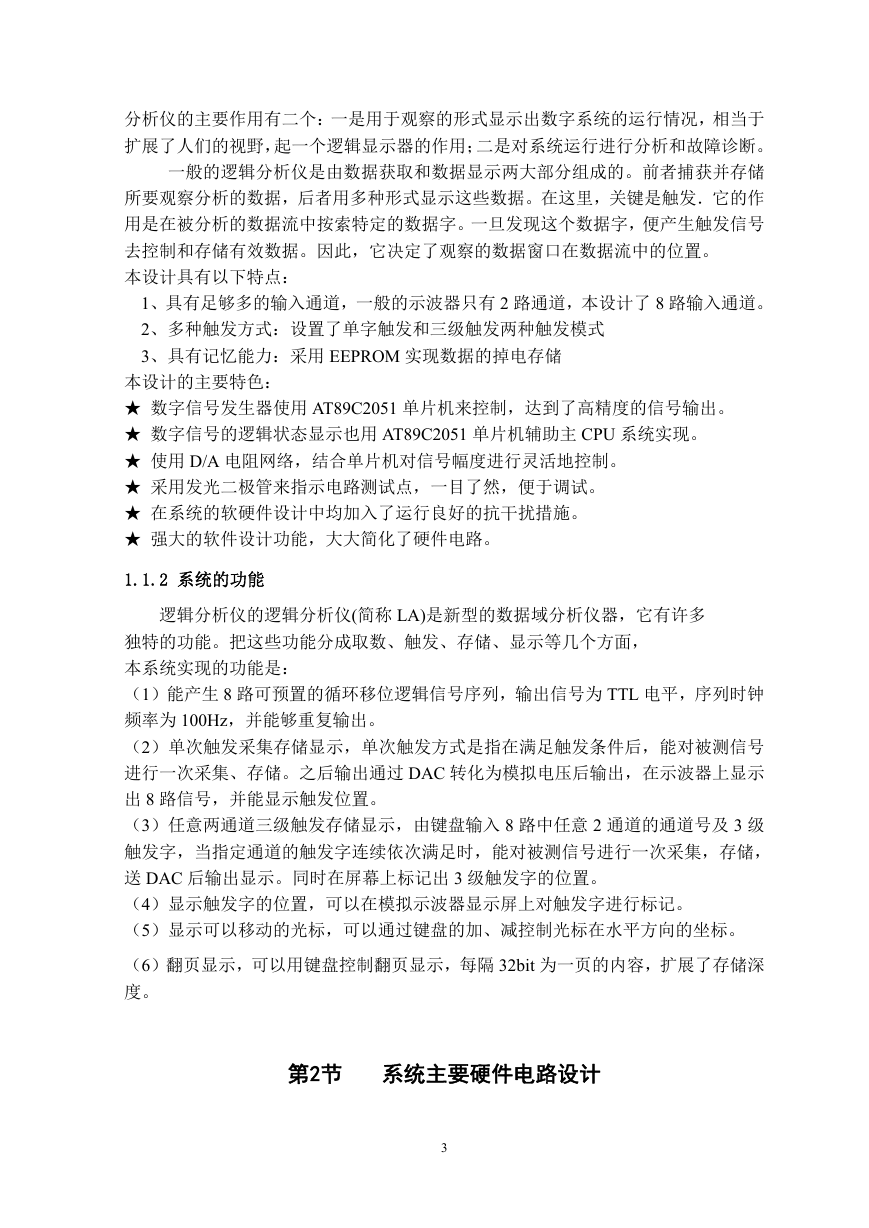

2.1 系统结构框图

图 2-1 系统结构框图

本系统采用单片机和可编程器件作为数据处理及控制核心,整个系统由一个信号

发生器和一个简易逻辑分析仪构成。将设计任务分解为数字信号发生、信号采集存储、

信号融合处理、显示、掉电保护等功能模块。图 1 即为该系统的总体框图。考虑到硬

件电路的紧凑性,故将上述模块合理分配连接成以下三个模块:数字信号发生器、最

小系统主控器、键盘/显示。由于数字信号发生器是用于测试的需要而设计的一个模

块,那么下面对各模块的设计进行逐一论证比较。

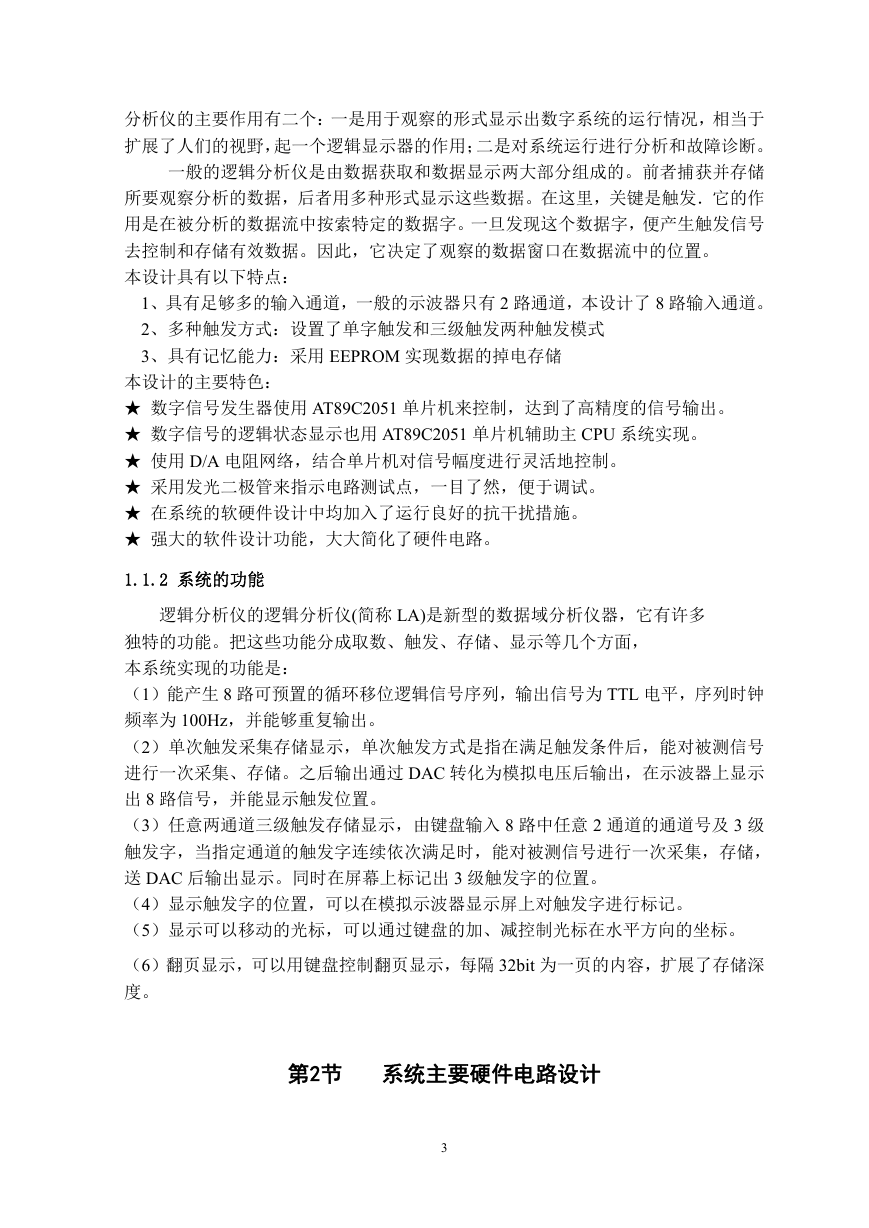

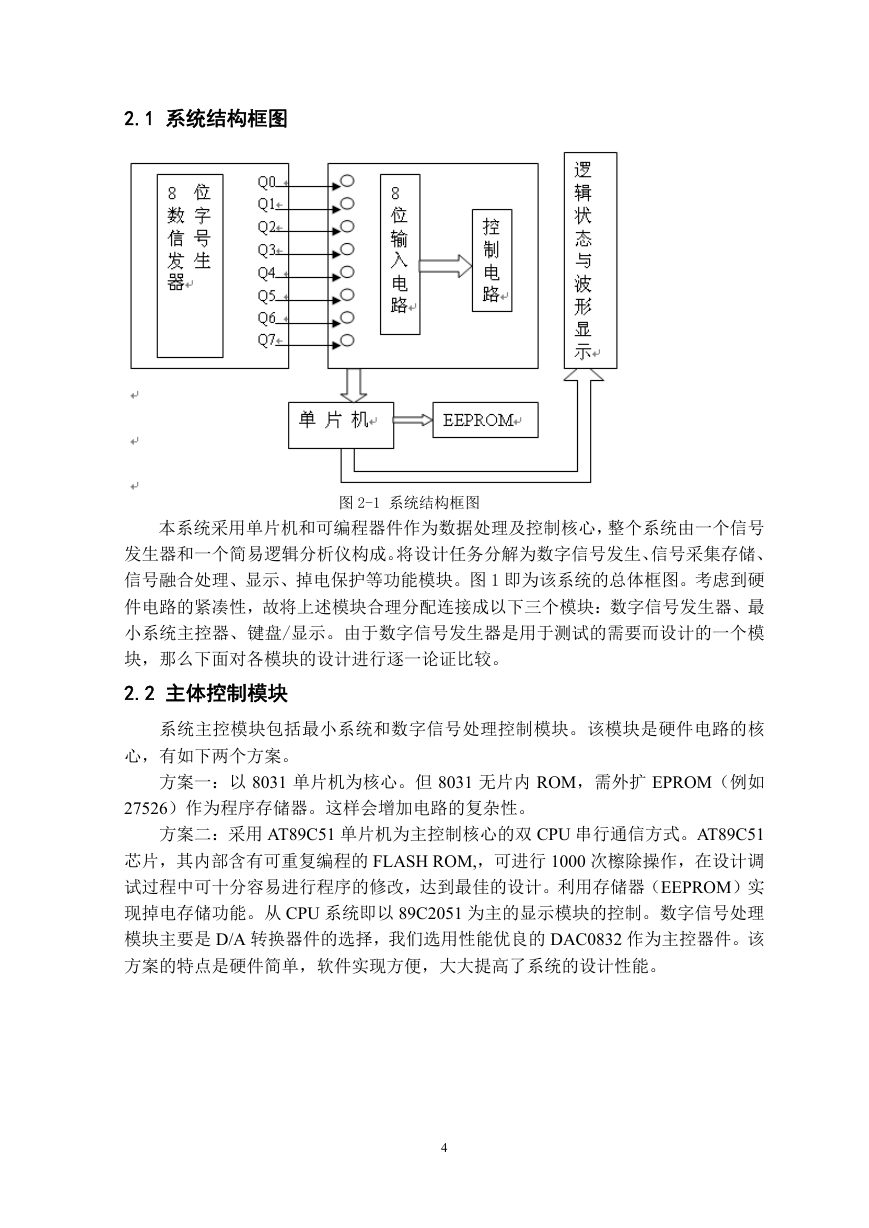

2.2 主体控制模块

系统主控模块包括最小系统和数字信号处理控制模块。该模块是硬件电路的核

心,有如下两个方案。

方案一:以 8031 单片机为核心。但 8031 无片内 ROM,需外扩 EPROM(例如

27526)作为程序存储器。这样会增加电路的复杂性。

方案二:采用 AT89C51 单片机为主控制核心的双 CPU 串行通信方式。AT89C51

芯片,其内部含有可重复编程的 FLASH ROM,,可进行 1000 次檫除操作,在设计调

试过程中可十分容易进行程序的修改,达到最佳的设计。利用存储器(EEPROM)实

现掉电存储功能。从 CPU 系统即以 89C2051 为主的显示模块的控制。数字信号处理

模块主要是 D/A 转换器件的选择,我们选用性能优良的 DAC0832 作为主控器件。该

方案的特点是硬件简单,软件实现方便,大大提高了系统的设计性能。

4

�

门限电压:

要实现门限电压 0.25-4V 之间 16 级可调这一问题上有两种方案。

方案一、电阻分压,利用电阻网络把电压分级作为触发门参考电压,用模拟开关

4067 在把每个通道的信号和这个参考电压用电压比较器来比较,判断输入信号高低,

输入单片机处理。

方案二、用 D/A 电阻网络进行电压等级的划分作为参考电压,在用比较器来比

较高低。与方案一比具有精确可调的优点。

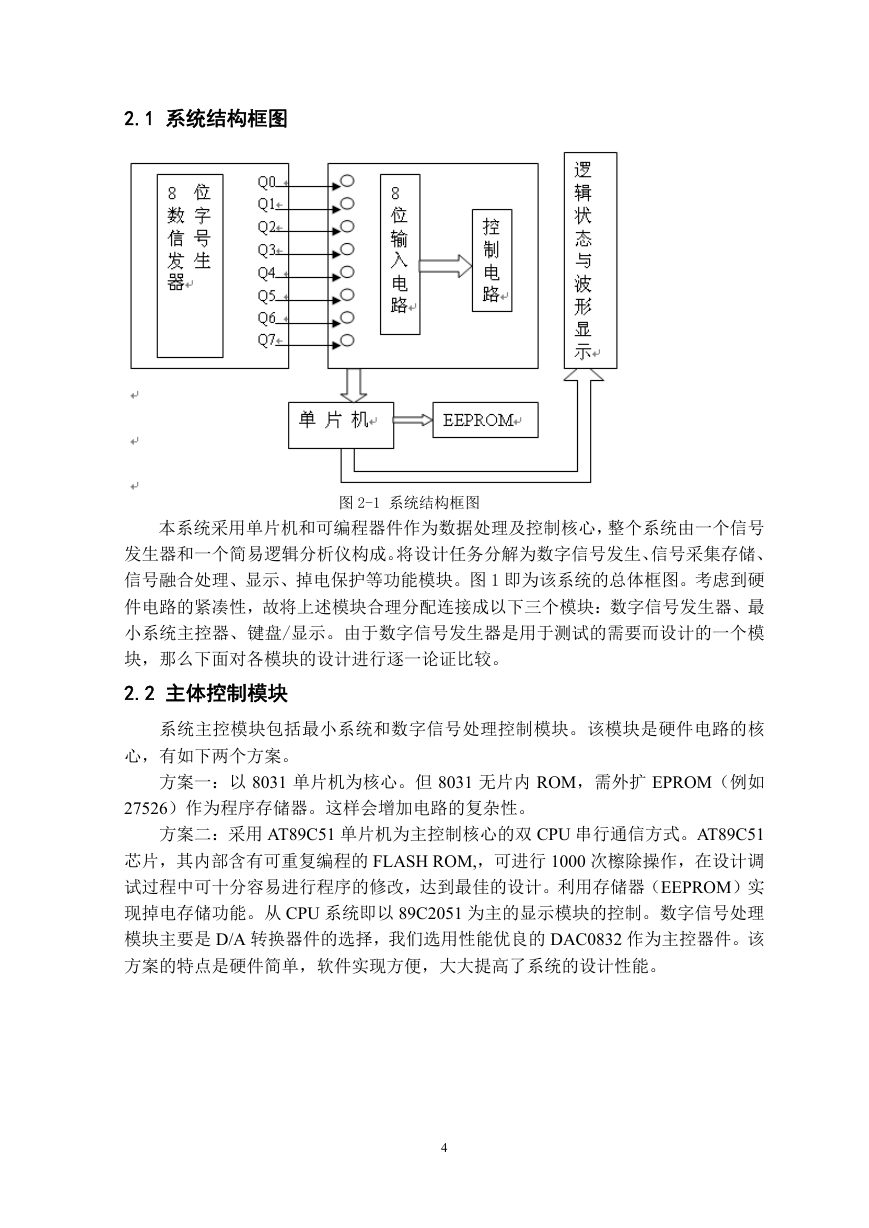

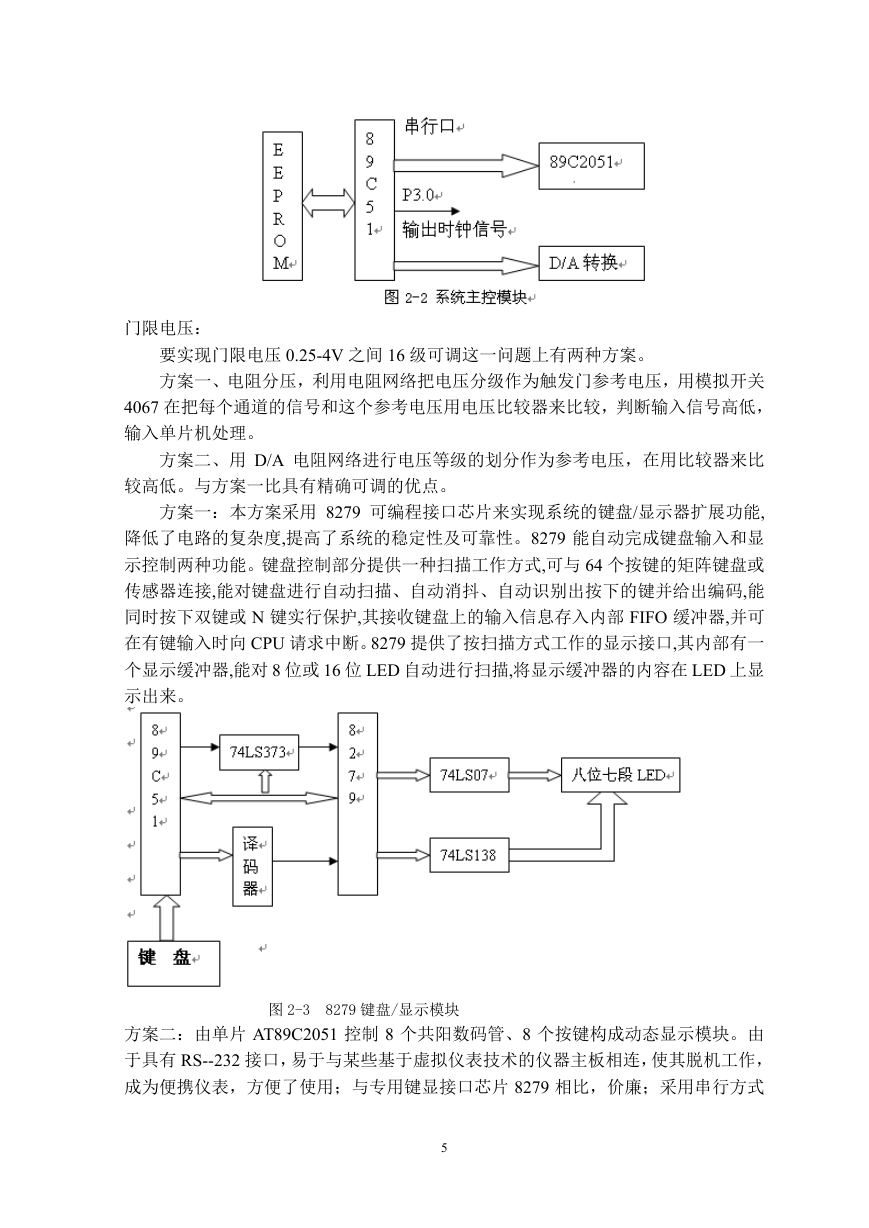

方案一:本方案采用 8279 可编程接口芯片来实现系统的键盘/显示器扩展功能,

降低了电路的复杂度,提高了系统的稳定性及可靠性。8279 能自动完成键盘输入和显

示控制两种功能。键盘控制部分提供一种扫描工作方式,可与 64 个按键的矩阵键盘或

传感器连接,能对键盘进行自动扫描、自动消抖、自动识别出按下的键并给出编码,能

同时按下双键或 N 键实行保护,其接收键盘上的输入信息存入内部 FIFO 缓冲器,并可

在有键输入时向 CPU 请求中断。8279 提供了按扫描方式工作的显示接口,其内部有一

个显示缓冲器,能对 8 位或 16 位 LED 自动进行扫描,将显示缓冲器的内容在 LED 上显

示出来。

图 2-3 8279 键盘/显示模块

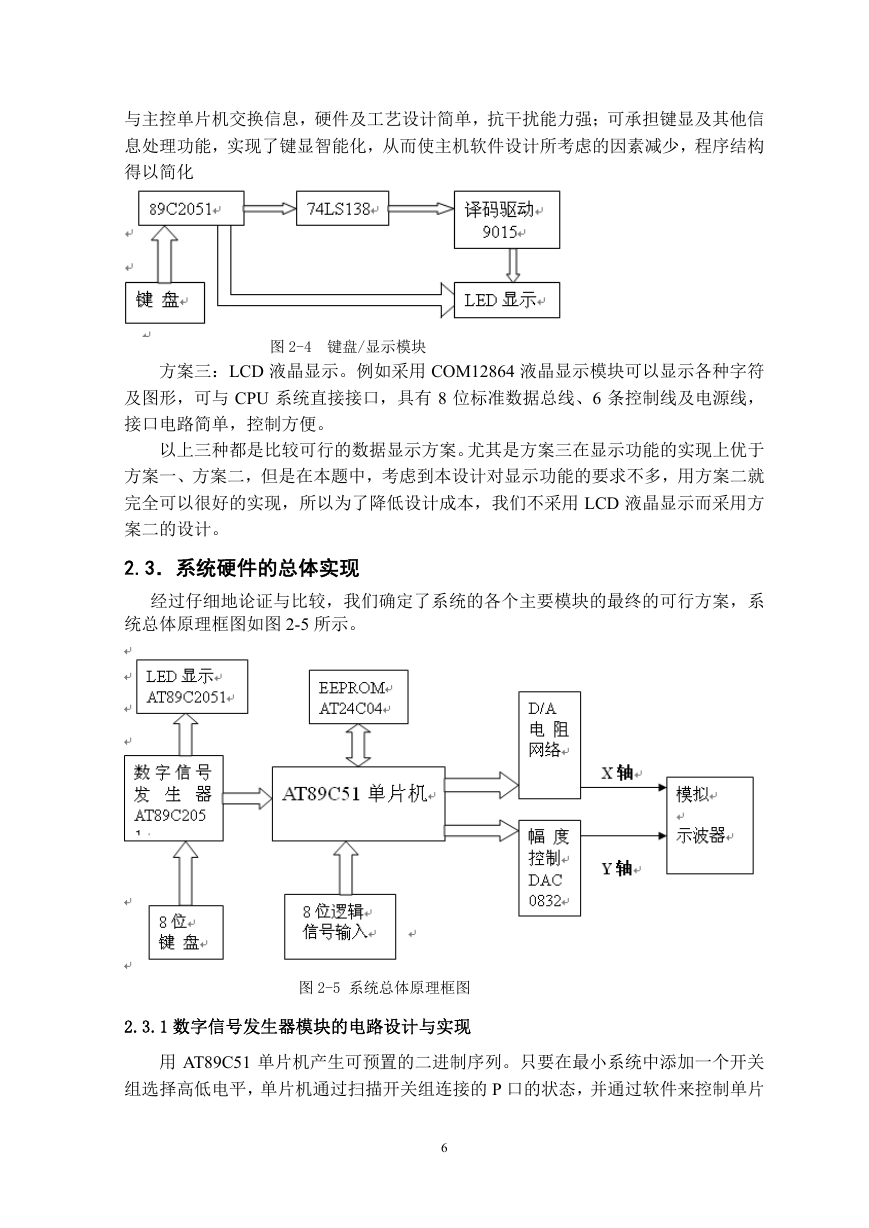

方案二:由单片 AT89C2051 控制 8 个共阳数码管、8 个按键构成动态显示模块。由

于具有 RS--232 接口,易于与某些基于虚拟仪表技术的仪器主板相连,使其脱机工作,

成为便携仪表,方便了使用;与专用键显接口芯片 8279 相比,价廉;采用串行方式

5

�

与主控单片机交换信息,硬件及工艺设计简单,抗干扰能力强;可承担键显及其他信

息处理功能,实现了键显智能化,从而使主机软件设计所考虑的因素减少,程序结构

得以简化

图 2-4 键盘/显示模块

方案三:LCD 液晶显示。例如采用 COM12864 液晶显示模块可以显示各种字符

及图形,可与 CPU 系统直接接口,具有 8 位标准数据总线、6 条控制线及电源线,

接口电路简单,控制方便。

以上三种都是比较可行的数据显示方案。尤其是方案三在显示功能的实现上优于

方案一、方案二,但是在本题中,考虑到本设计对显示功能的要求不多,用方案二就

完全可以很好的实现,所以为了降低设计成本,我们不采用 LCD 液晶显示而采用方

案二的设计。

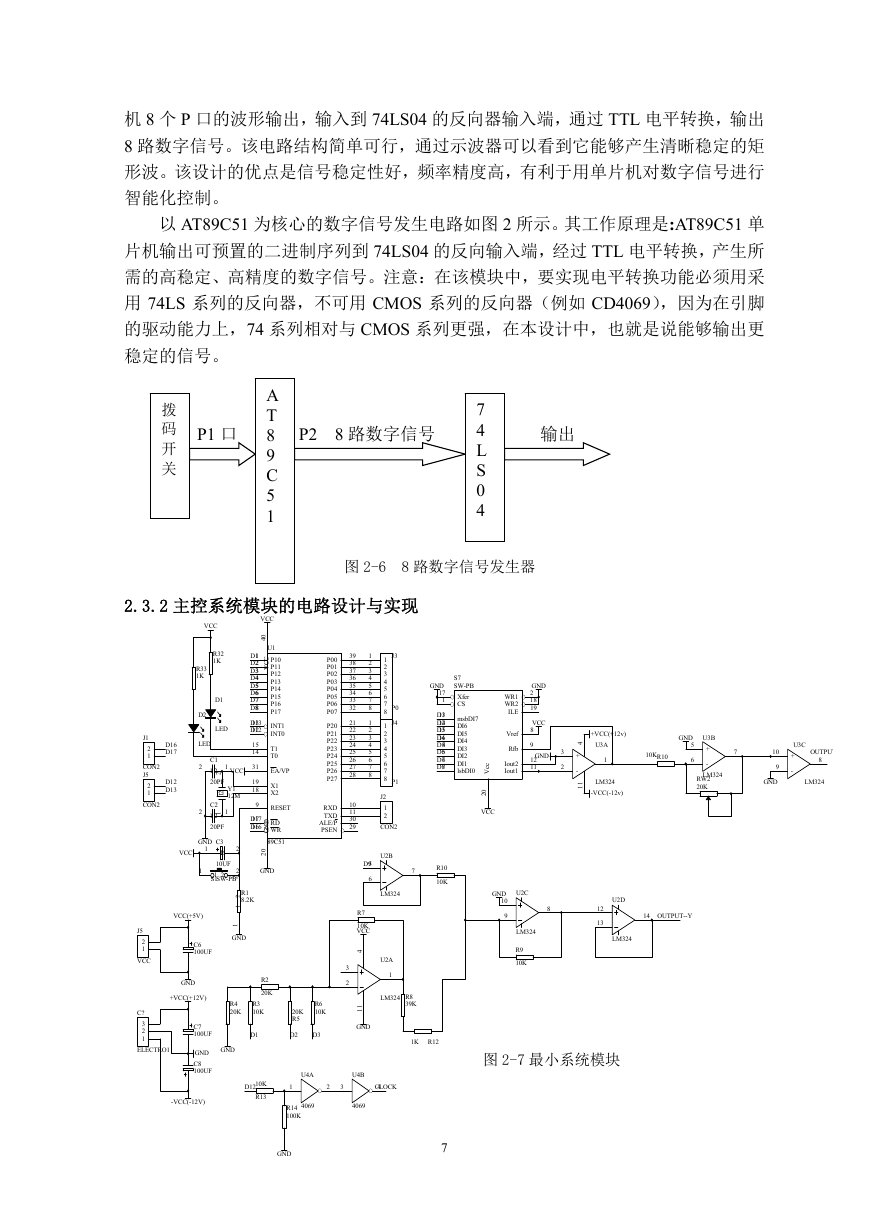

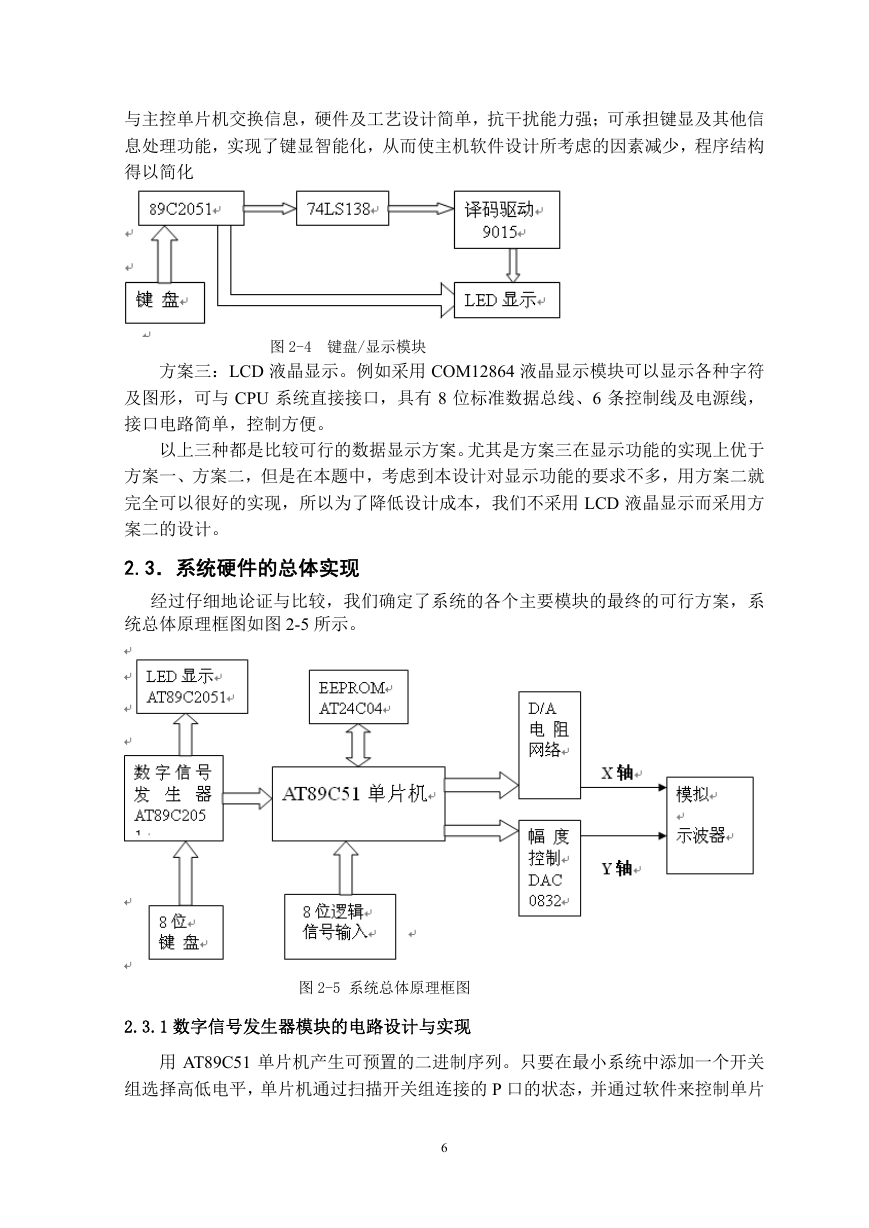

2.3.系统硬件的总体实现

经过仔细地论证与比较,我们确定了系统的各个主要模块的最终的可行方案,系

统总体原理框图如图 2-5 所示。

图 2-5 系统总体原理框图

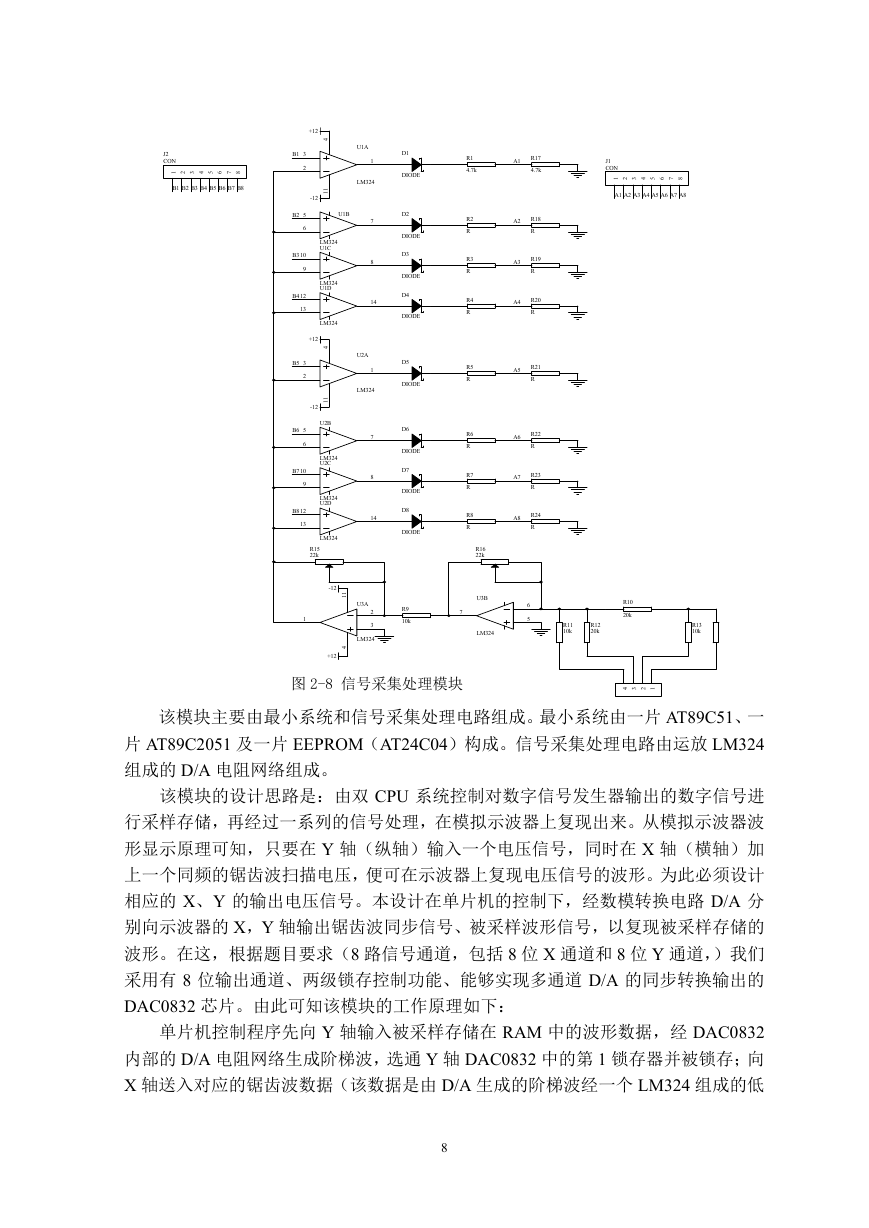

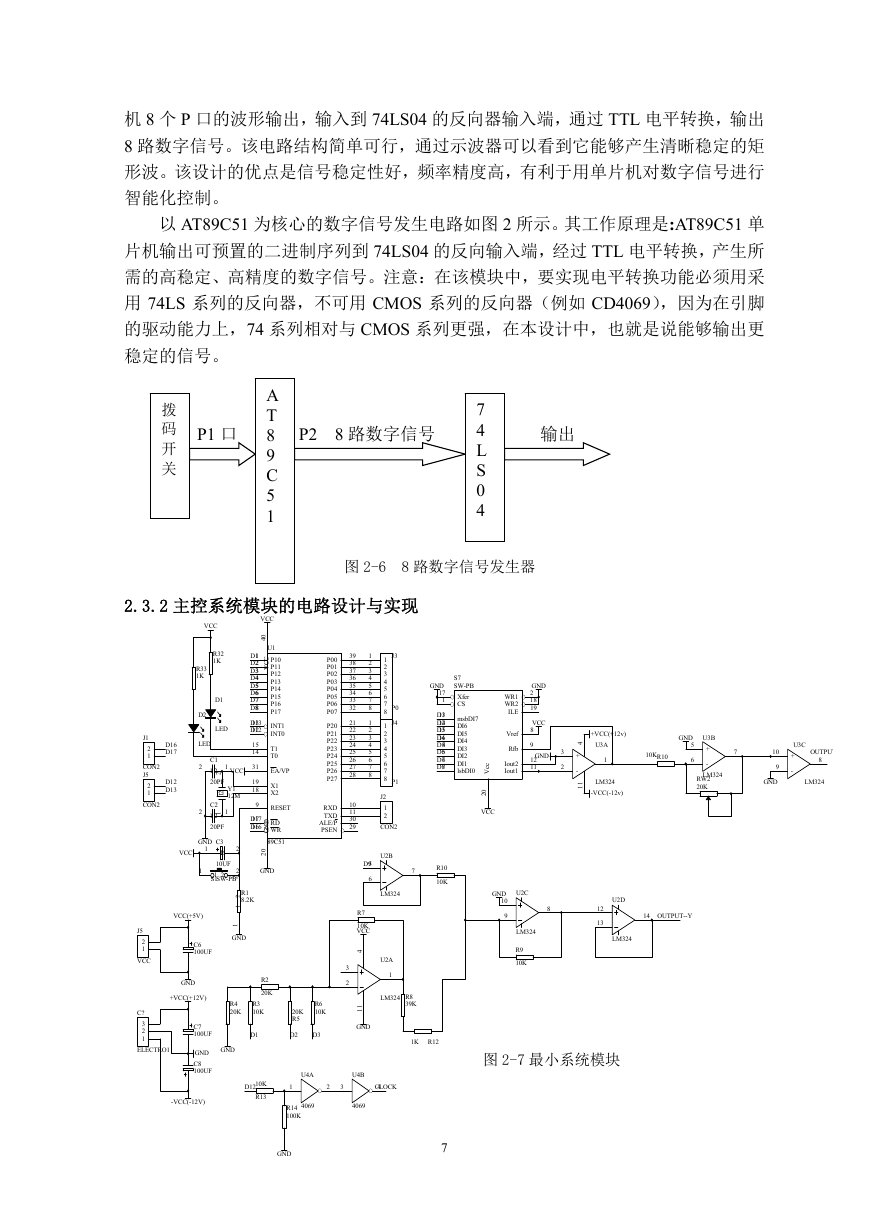

2.3.1 数字信号发生器模块的电路设计与实现

用 AT89C51 单片机产生可预置的二进制序列。只要在最小系统中添加一个开关

组选择高低电平,单片机通过扫描开关组连接的 P 口的状态,并通过软件来控制单片

6

�

机 8 个 P 口的波形输出,输入到 74LS04 的反向器输入端,通过 TTL 电平转换,输出

8 路数字信号。该电路结构简单可行,通过示波器可以看到它能够产生清晰稳定的矩

形波。该设计的优点是信号稳定性好,频率精度高,有利于用单片机对数字信号进行

智能化控制。

以 AT89C51 为核心的数字信号发生电路如图 2 所示。其工作原理是:AT89C51 单

片机输出可预置的二进制序列到 74LS04 的反向输入端,经过 TTL 电平转换,产生所

需的高稳定、高精度的数字信号。注意:在该模块中,要实现电平转换功能必须用采

用 74LS 系列的反向器,不可用 CMOS 系列的反向器(例如 CD4069),因为在引脚

的驱动能力上,74 系列相对与 CMOS 系列更强,在本设计中,也就是说能够输出更

稳定的信号。

拨

P1 口 P2 8 路数字信号 输出

码

开

关

7

4

L

S

0

4

A

T

8

9

C

5

1

图 2-6 8 路数字信号发生器

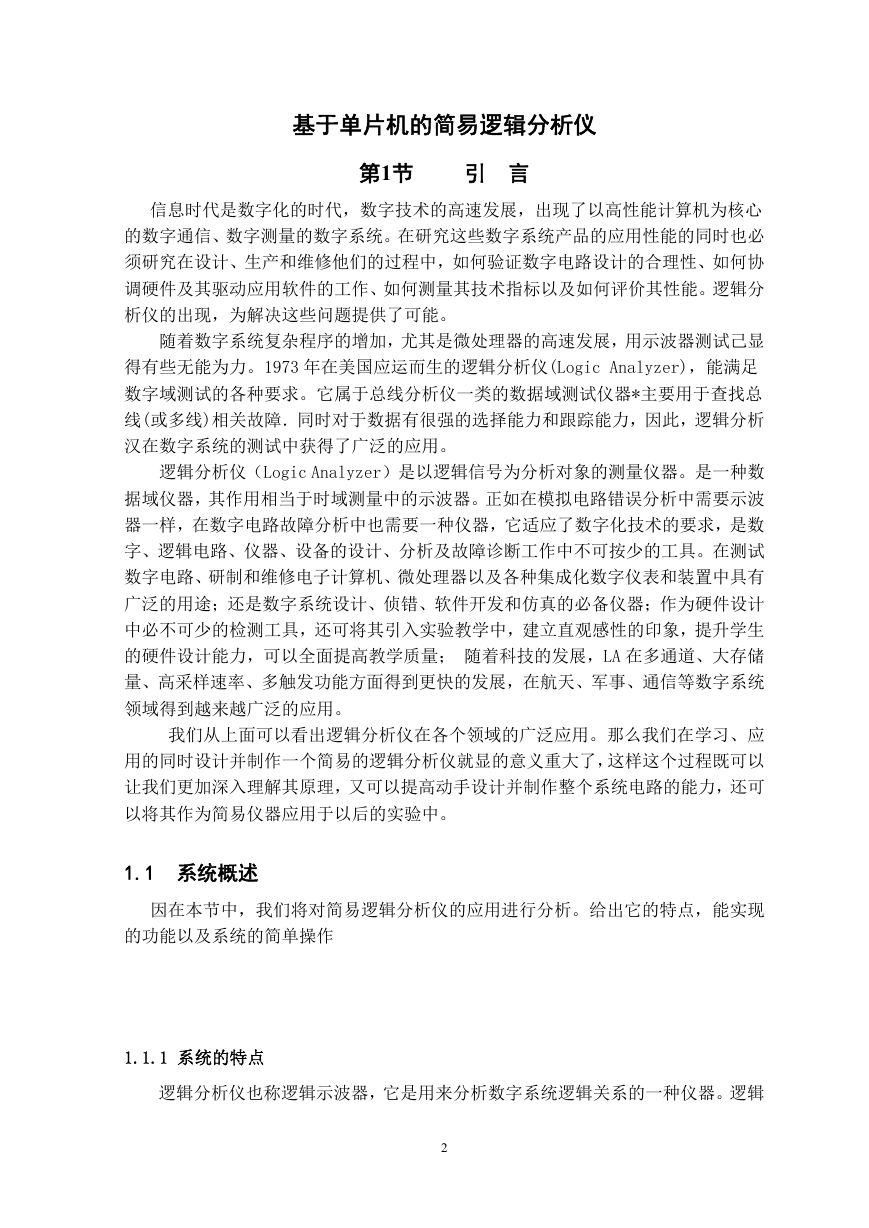

2.3.2 主控系统模块的电路设计与实现

GND

R2

+VCC(+12V)

LM324

20K

R8

39K

R4

20K

R3

10K

R6

10K

20K

R5

C?

3

2

1

C7

100UF

图 2-7 最小系统模块

ELECTRO1

GND

GND

R12

1K

D1

D2

D3

GND

C8

100UF

-VCC(-12V)

10K

D12

R13

U4A

U4B

1

2

3

4

CLOCK

4069

R14

100K

4069

GND

7

VCC

R32

1K

R33

1K

D1

LED

D2

LED

2

2

1

VCC

Y1

12M

1

C1

1

2

20PF

2

2

1

1

C2

1

2

20PF

GND

1

1

2

C3

1

2

10UF

2

1

S1SW-PB

2

2

J1

2

1

CON2

J5

2

1

CON2

D16

D17

D12

D13

VCC

VCC

0

4

C

C

V

U1

P10

P11

P12

P13

P14

P15

P16

P17

D1

1

2

D2

D3

3

D4

4

D5

5

D6

6

D7

7

D8

8

D13

13

D12

12

15

14

31

19

18

9

INT1

INT0

T1

T0

EA/VP

X1

X2

RESET

D17

17

D16

16

D

N

G

RD

WR

89C51

0

2

GND

2

R1

8.2K

1

1

GND

VCC(+5V)

C6

100UF

J5

2

1

VCC

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

J3

P0

J4

P1

J2

1

2

CON2

U2B

LM324

U2A

1

GND

2

18

19

VCC

8

9

GND

12

11

WR1

WR2

ILE

Vref

Rfb

Iout2

Iout1

GND

17

1

S7

SW-PB

Xfer

CS

D1

13

D2

14

D3

15

D4

16

D5

4

5

D6

6

D7

7

D8

msbDI7

DI6

DI5

DI4

DI3

DI2

DI1

lsbDI0

c

c

V

0

2

VCC

7

R10

10K

3

2

+VCC(+12v)

4 U3A

+

1

-

1

1

LM324

-VCC(-12v)

10K

R10

7

GND

5

6

U3B

+

-

LM324

RW2

20K

10

9

U3C

+

-

OUTPUT

8

GND

LM324

U2C

GND

10

9

8

LM324

R9

10K

U2D

12

13

LM324

14

OUTPUT--Y

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

P00

P01

P02

P03

P04

P05

P06

P07

P20

P21

P22

P23

P24

P25

P26

P27

RXD

TXD

ALE/P

PSEN

39

38

37

36

35

34

33

32

21

22

23

24

25

26

27

28

10

11

30

29

D9

5

6

R7

10K

VCC

4

3

2

1

1

�

J2

CON

1 2 3 4 5 6 7 8

B1 B2 B3 B4 B5 B6 B7 B8

B1

B2

3

2

5

6

B3

10

9

B4

12

13

B5

B6

3

2

5

6

B7

10

9

B8

12

13

1

U1A

1

LM324

7

8

14

U2A

1

LM324

7

8

14

+12

4

1

1

-12

U1B

LM324

U1C

LM324

U1D

LM324

+12

4

1

1

-12

U2B

LM324

U2C

LM324

U2D

LM324

R15

22k

-12

1

1

4

+12

U3A

2

3

LM324

D1

DIODE

D2

DIODE

D3

DIODE

D4

DIODE

D5

DIODE

D6

DIODE

D7

DIODE

D8

DIODE

R9

10k

R1

4.7k

A1

R17

4.7k

J1

CON

1 2 3 4 5 6 7 8

A1 A2 A3 A4 A5 A6 A7 A8

R2

R

R3

R

R4

R

R5

R

R6

R

R7

R

R8

R

R16

22k

U3B

7

LM324

A2

A3

A4

R18

R

R19

R

R20

R

A5

R21

R

A6

A7

A8

R22

R

R23

R

R24

R

6

5

R10

20k

R11

10k

R12

20k

R13

10k

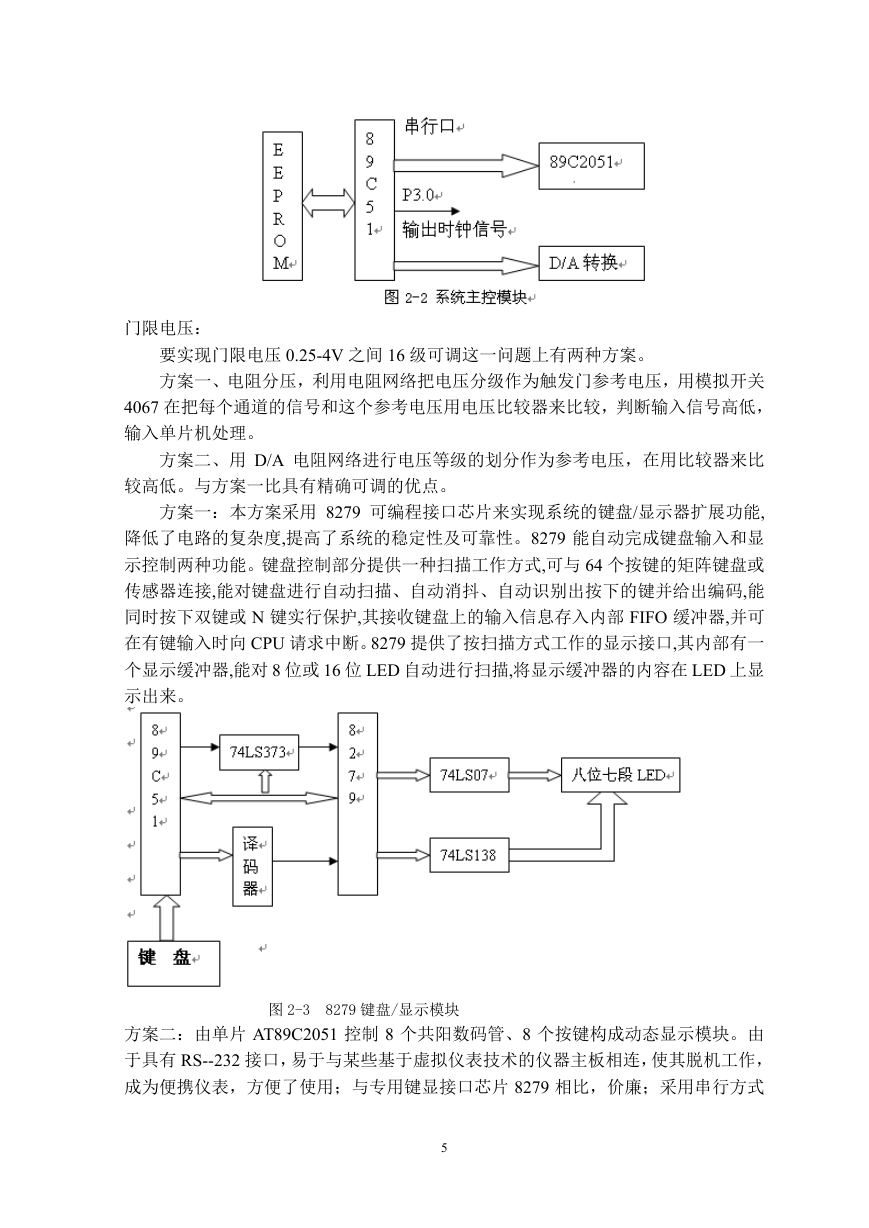

图 2-8 信号采集处理模块

1234

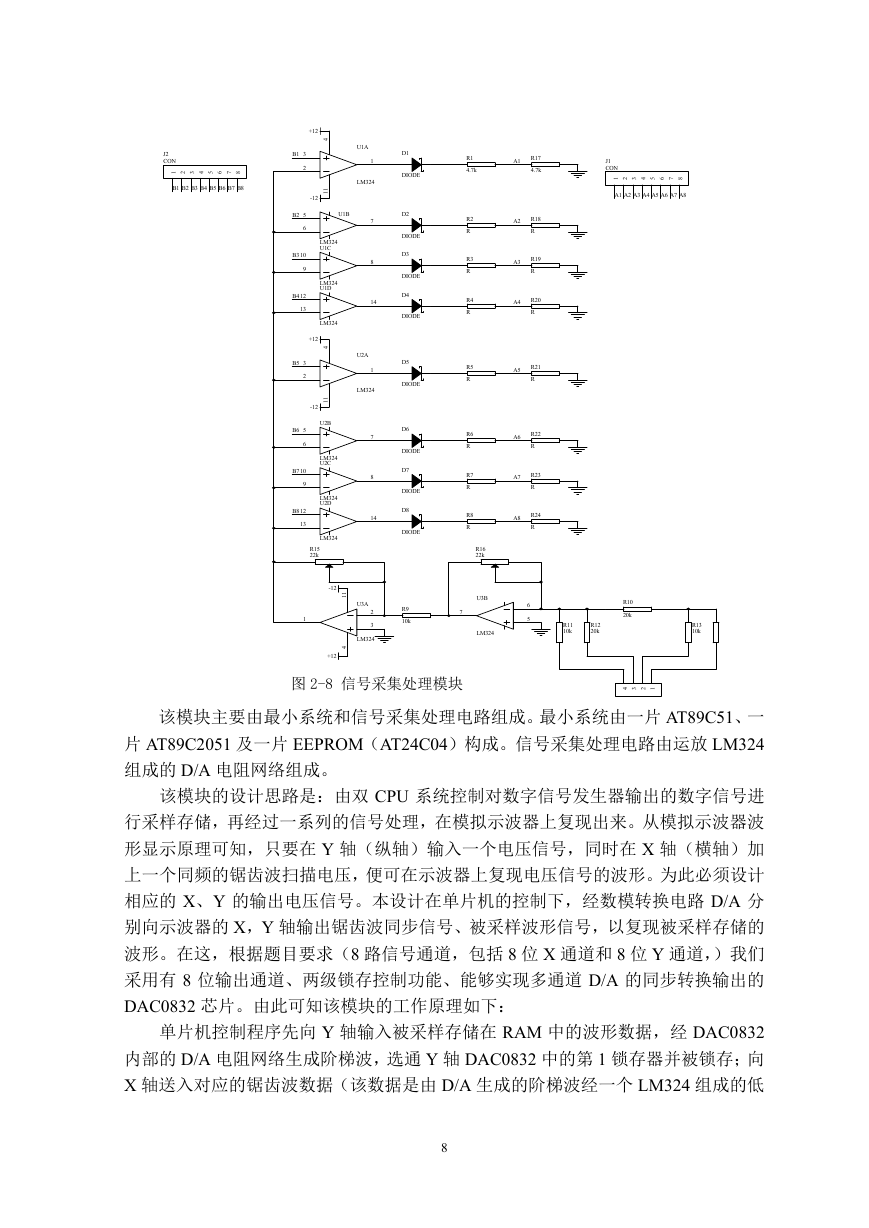

该模块主要由最小系统和信号采集处理电路组成。最小系统由一片 AT89C51、一

片 AT89C2051 及一片 EEPROM(AT24C04)构成。信号采集处理电路由运放 LM324

组成的 D/A 电阻网络组成。

该模块的设计思路是:由双 CPU 系统控制对数字信号发生器输出的数字信号进

行采样存储,再经过一系列的信号处理,在模拟示波器上复现出来。从模拟示波器波

形显示原理可知,只要在 Y 轴(纵轴)输入一个电压信号,同时在 X 轴(横轴)加

上一个同频的锯齿波扫描电压,便可在示波器上复现电压信号的波形。为此必须设计

相应的 X、Y 的输出电压信号。本设计在单片机的控制下,经数模转换电路 D/A 分

别向示波器的 X,Y 轴输出锯齿波同步信号、被采样波形信号,以复现被采样存储的

波形。在这,根据题目要求(8 路信号通道,包括 8 位 X 通道和 8 位 Y 通道,)我们

采用有 8 位输出通道、两级锁存控制功能、能够实现多通道 D/A 的同步转换输出的

DAC0832 芯片。由此可知该模块的工作原理如下:

单片机控制程序先向 Y 轴输入被采样存储在 RAM 中的波形数据,经 DAC0832

内部的 D/A 电阻网络生成阶梯波,选通 Y 轴 DAC0832 中的第 1 锁存器并被锁存;向

X 轴送入对应的锯齿波数据(该数据是由 D/A 生成的阶梯波经一个 LM324 组成的低

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc