课程设计任务书

课 程 名 称

微机原理及应用

院 部 名 称

机电工程学院

业 电气工程及其自动化

吴映阳

李国利

专

班

级

指 导 教 师

金陵科技学院教务处制

�

摘 要

学了微型计算机原理与应用课程之后,为了巩固和检测所学知识,我选择基于

8088CPU 的模拟计算器设计。要完成设计首先需要构建简单的微型计算机应用系统,其

次是确定组成各部件的芯片,然后画原理图并且用仿真软件仿真。仿真正确后再连接

硬件电路,电路连接完成后进行调试。设计过程中我们用到了 8088CPU、可编程计时器

8253、可编程并行输入/输出芯片 8255A、74LS138、2*8 矩阵式键盘、六位七段 LED 数

码管。原理图设计完成之后用 PROTUES 仿真软件对原理图进行了仿真得到了预期的结

果。我们的模拟计算器能实现 5 位十进制数以内的及减法运算和 2 位十进制数以内的

乘除法运算。

关键词:模拟计算器,8088CPU,PROTUES,8255A

2

�

目 录

一、 概述 ……………………………………………………………………………4

二、 硬件电路 ………………………………………………………………………4

2.1、CPU 控制模块…………………………………………………………………4

2.2、键盘输入模块…………………………………………………………………6

2.3、可编程并行通信接口芯片 8255A ……………………………………………7

2.4、可编程计数器/定时器……………………………………………………8

2.5、总原理图……………………………………………………………………9

三、软件设计框图 ……………………………………………………………………10

四、源程序 ……………………………………………………………………………11

五、调试过程 …………………………………………………………………………26

六、课程设计体会 ……………………………………………………………………26

七、参考文献 …………………………………………………………………………27

3

�

模拟计算器设计

一、 概述

设计思路:首先利用程序不断扫描键盘是不是有输入,如果没有就一直扫描,

如果有就停止扫描,完成输入,利用汇编的程序核对输入键的数值,通过调用子程

序实现 5 位十进制数以内的及减法运算和 2 位十进制数以内的乘除法运算。运算完

成后将运算的结果储存并显示到 LED 显示器上。

二、 硬件电路设计

硬件电路 键盘输入及 LED 数码管通过 8255A 接口与系统总线连接,键盘的 16 个

按键组成 8*2 矩阵,其中 8 根矩阵线作为 8255A 的输出线与 PB7~PB0 连接,2 根

矩阵线作为 8255A 的输入线与 PC7、PC6 连接。键盘采用逐次扫描原理,16 个按键

中 0~9 座位数字健,+、-、*、/、=作为加、减、乘、除和等号功能键,C 为清零

键。

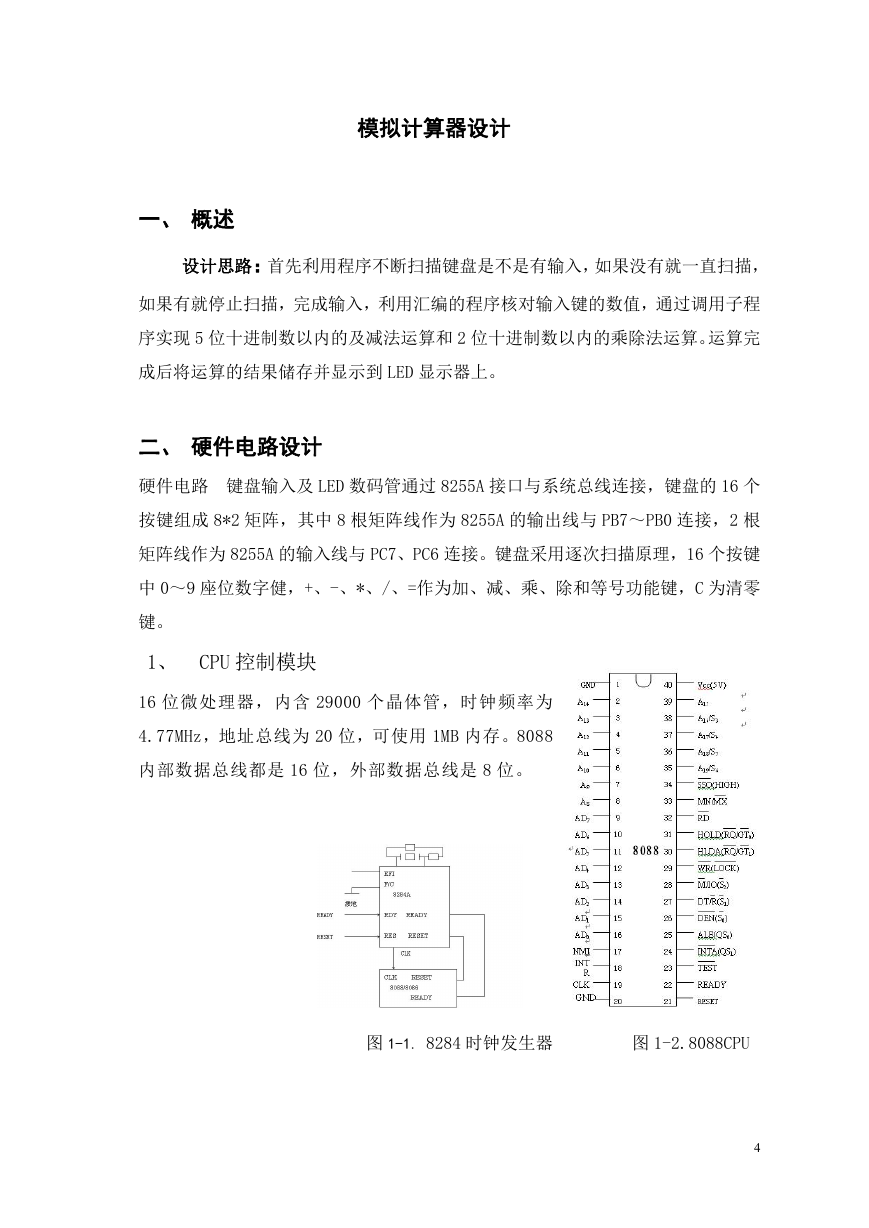

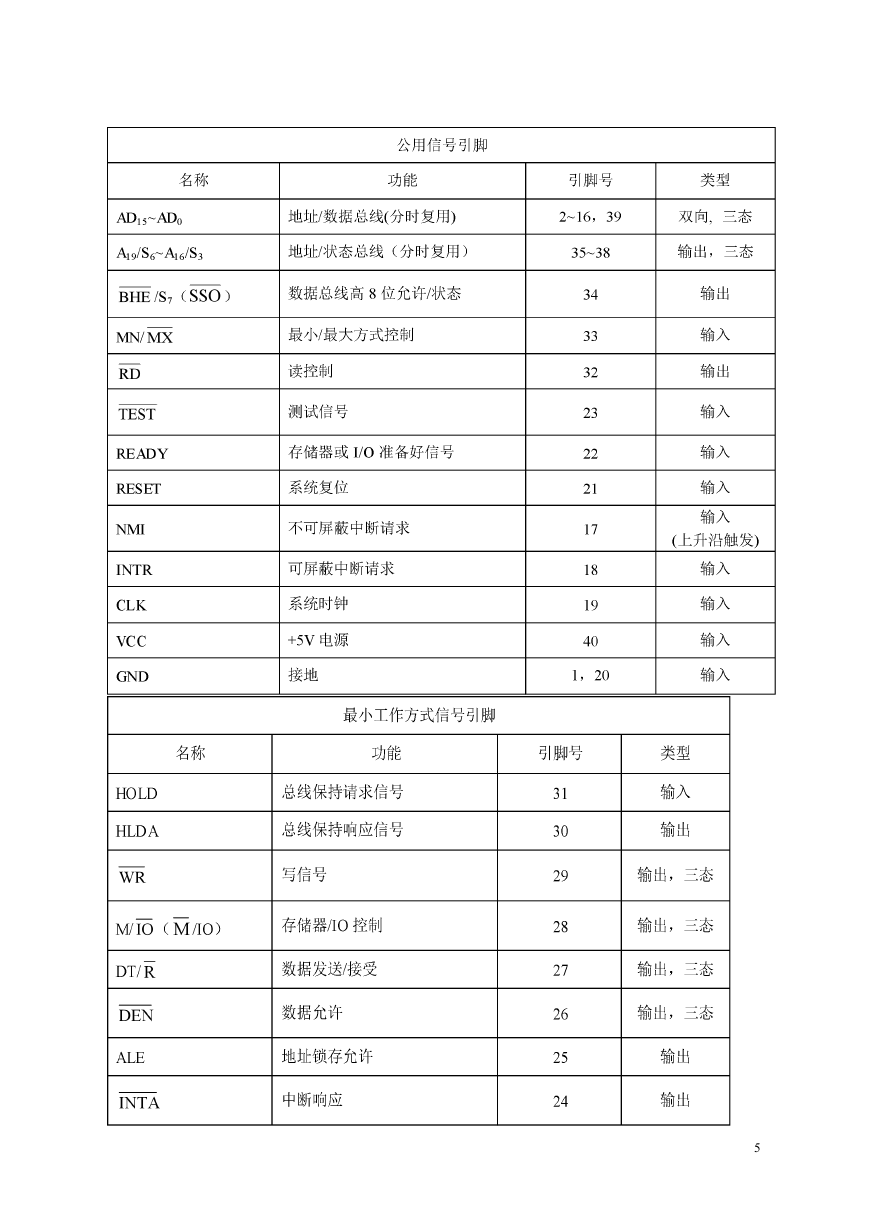

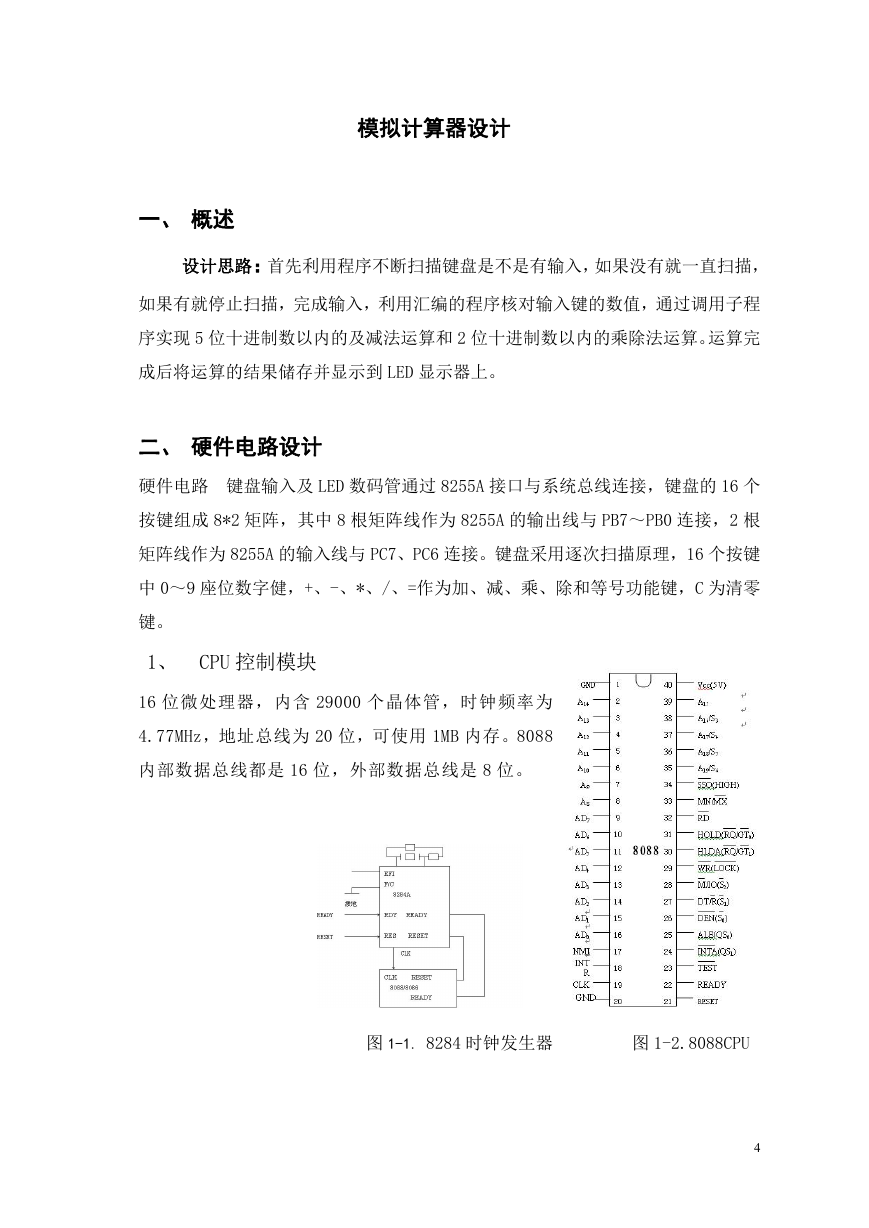

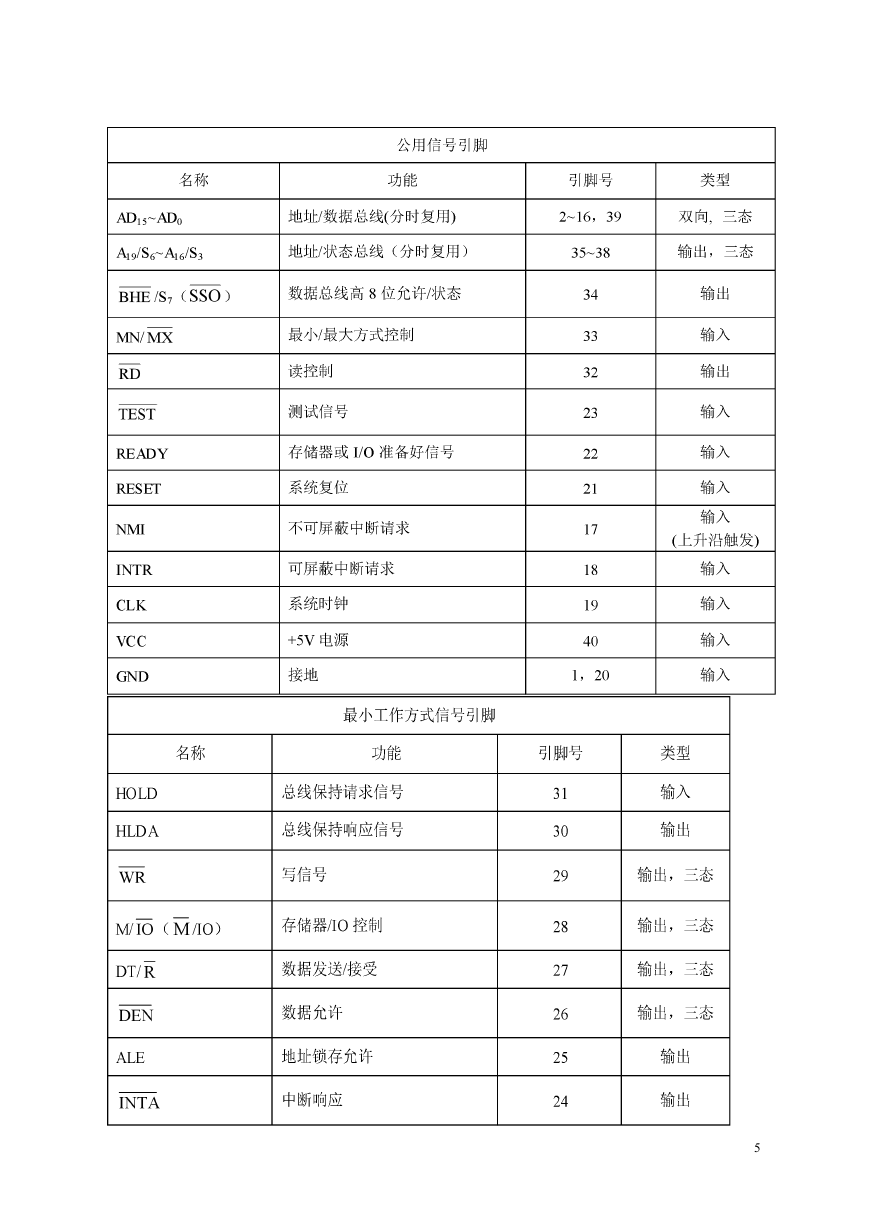

1、 CPU 控制模块

16 位微处理器,内含 29000 个晶体管,时钟频率为

4.77MHz,地址总线为 20 位,可使用 1MB 内存。8088

内部数据总线都是 16 位,外部数据总线是 8 位。

图 1-1. 8284 时钟发生器

图 1-2.8088CPU

4

�

5

�

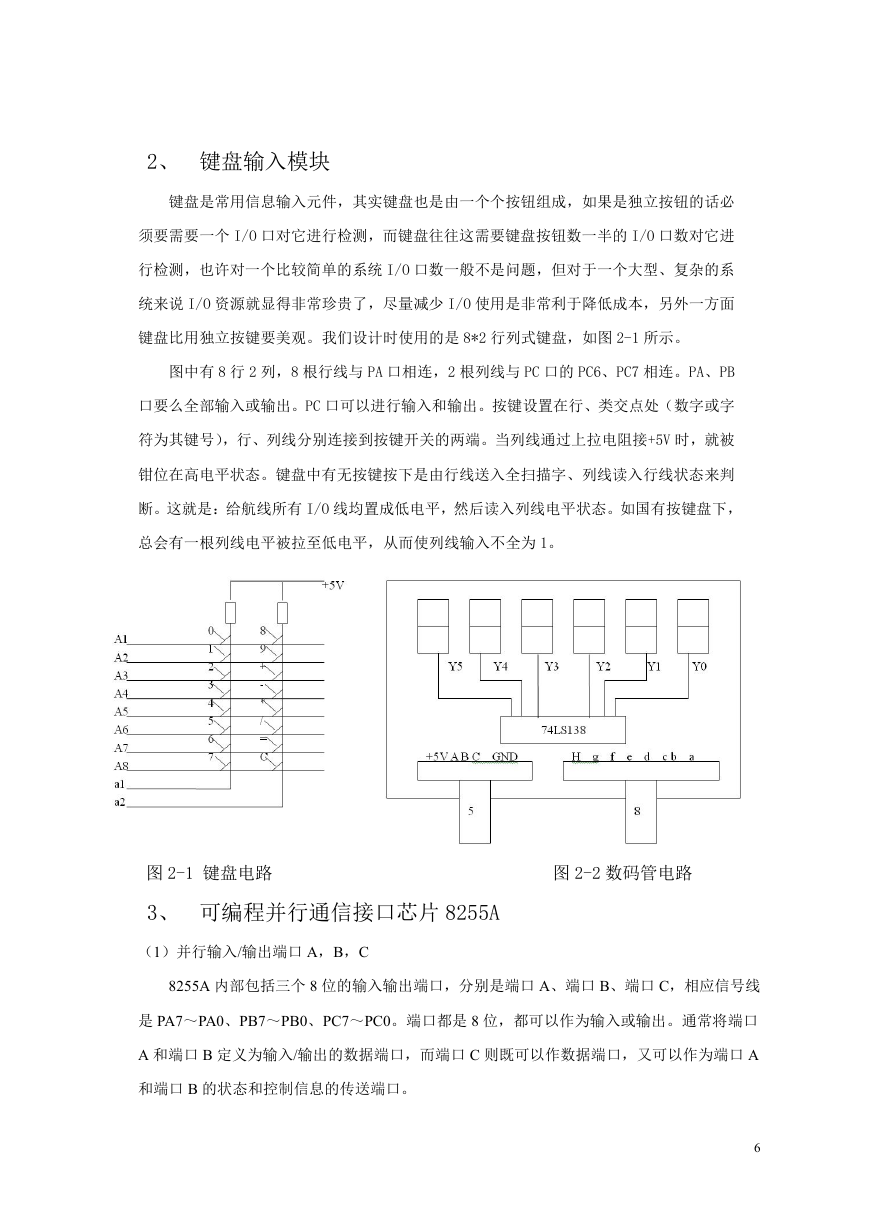

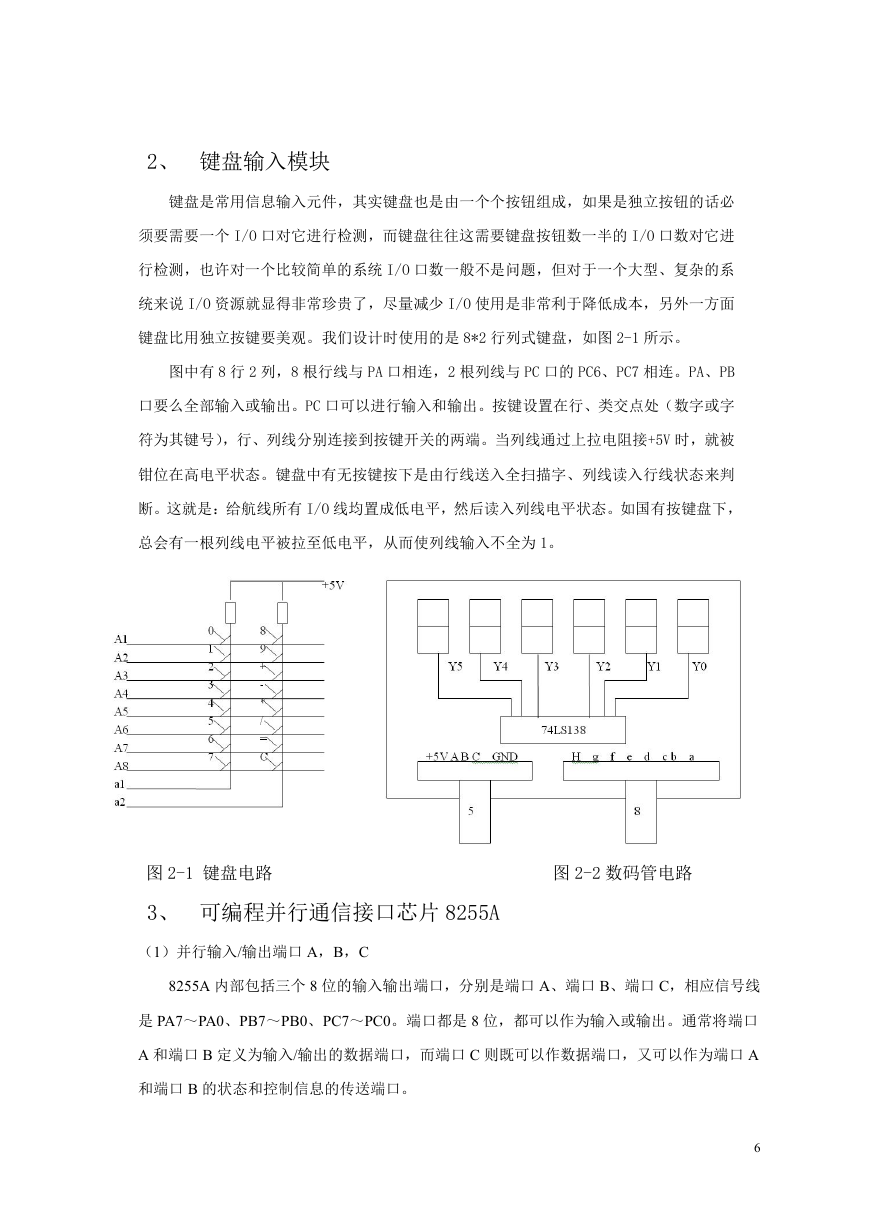

2、 键盘输入模块

键盘是常用信息输入元件,其实键盘也是由一个个按钮组成,如果是独立按钮的话必

须要需要一个 I/O 口对它进行检测,而键盘往往这需要键盘按钮数一半的 I/O 口数对它进

行检测,也许对一个比较简单的系统 I/O 口数一般不是问题,但对于一个大型、复杂的系

统来说 I/O 资源就显得非常珍贵了,尽量减少 I/O 使用是非常利于降低成本,另外一方面

键盘比用独立按键要美观。我们设计时使用的是 8*2 行列式键盘,如图 2-1 所示。

图中有 8 行 2 列,8 根行线与 PA 口相连,2 根列线与 PC 口的 PC6、PC7 相连。PA、PB

口要么全部输入或输出。PC 口可以进行输入和输出。按键设置在行、类交点处(数字或字

符为其键号),行、列线分别连接到按键开关的两端。当列线通过上拉电阻接+5V 时,就被

钳位在高电平状态。键盘中有无按键按下是由行线送入全扫描字、列线读入行线状态来判

断。这就是:给航线所有 I/O 线均置成低电平,然后读入列线电平状态。如国有按键盘下,

总会有一根列线电平被拉至低电平,从而使列线输入不全为 1。

图 2-1 键盘电路

图 2-2 数码管电路

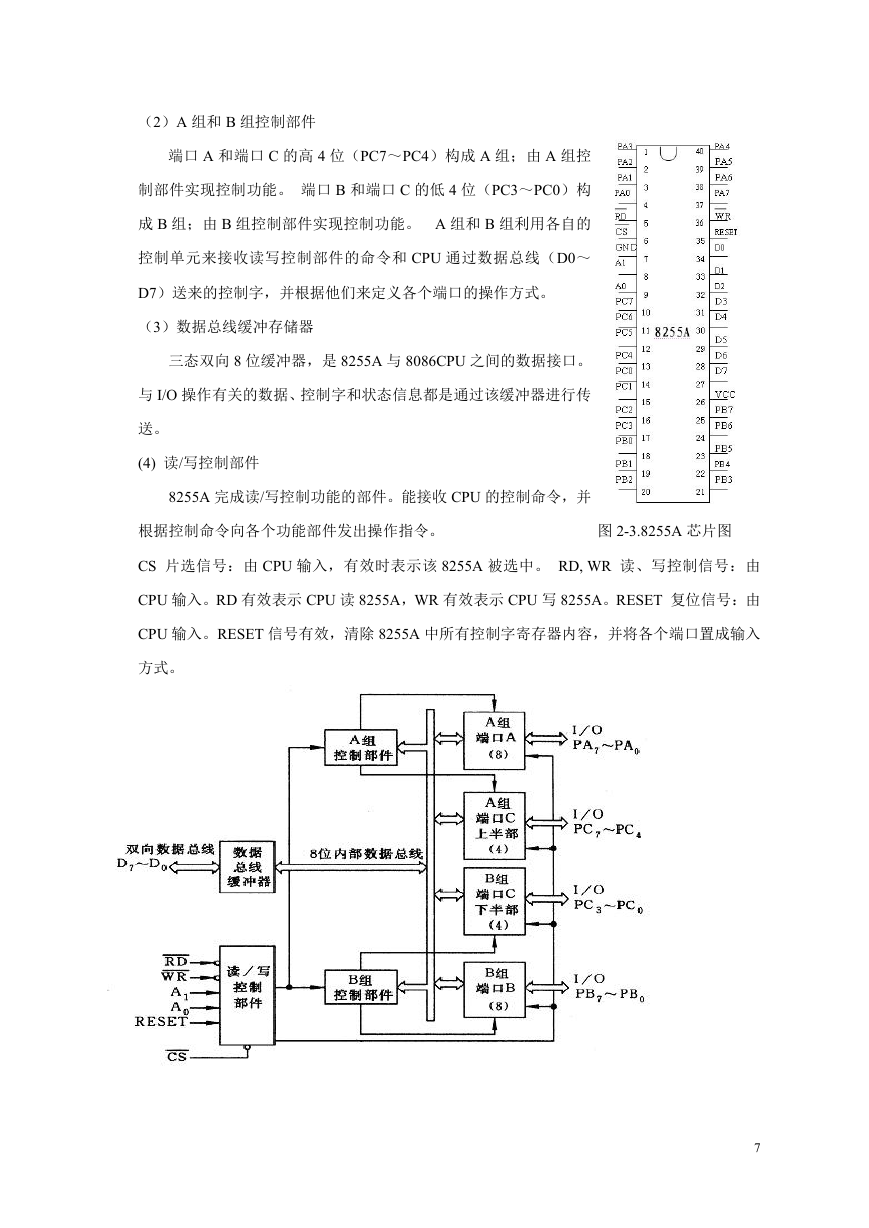

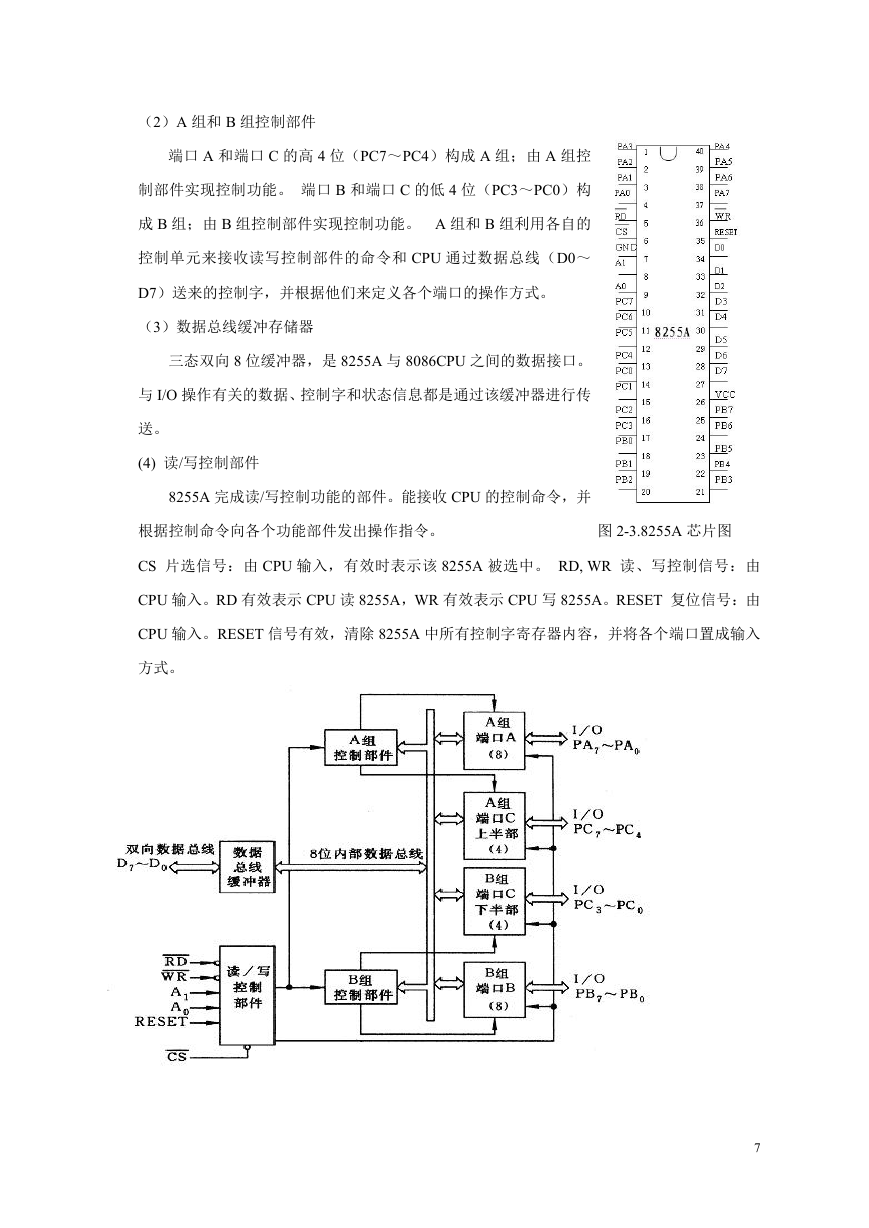

3、 可编程并行通信接口芯片 8255A

(1)并行输入/输出端口 A,B,C

8255A 内部包括三个 8 位的输入输出端口,分别是端口 A、端口 B、端口 C,相应信号线

是 PA7~PA0、PB7~PB0、PC7~PC0。端口都是 8 位,都可以作为输入或输出。通常将端口

A 和端口 B 定义为输入/输出的数据端口,而端口 C 则既可以作数据端口,又可以作为端口 A

和端口 B 的状态和控制信息的传送端口。

6

�

(2)A 组和 B 组控制部件

端口 A 和端口 C 的高 4 位(PC7~PC4)构成 A 组;由 A 组控

制部件实现控制功能。 端口 B 和端口 C 的低 4 位(PC3~PC0)构

成 B 组;由 B 组控制部件实现控制功能。 A 组和 B 组利用各自的

控制单元来接收读写控制部件的命令和 CPU 通过数据总线(D0~

D7)送来的控制字,并根据他们来定义各个端口的操作方式。

(3)数据总线缓冲存储器

三态双向 8 位缓冲器,是 8255A 与 8086CPU 之间的数据接口。

与 I/O 操作有关的数据、控制字和状态信息都是通过该缓冲器进行传

送。

(4) 读/写控制部件

8255A 完成读/写控制功能的部件。能接收 CPU 的控制命令,并

根据控制命令向各个功能部件发出操作指令。

图 2-3.8255A 芯片图

CS 片选信号:由 CPU 输入,有效时表示该 8255A 被选中。 RD, WR 读、写控制信号:由

CPU 输入。RD 有效表示 CPU 读 8255A,WR 有效表示 CPU 写 8255A。RESET 复位信号:由

CPU 输入。RESET 信号有效,清除 8255A 中所有控制字寄存器内容,并将各个端口置成输入

方式。

7

�

图 2-4 .8255A 内部结构

定义工作方式控制字:

工作方式 0:8255A 中各端口的基本输入/输出方式。

方式控制

图 2-5 .8255A 工 作

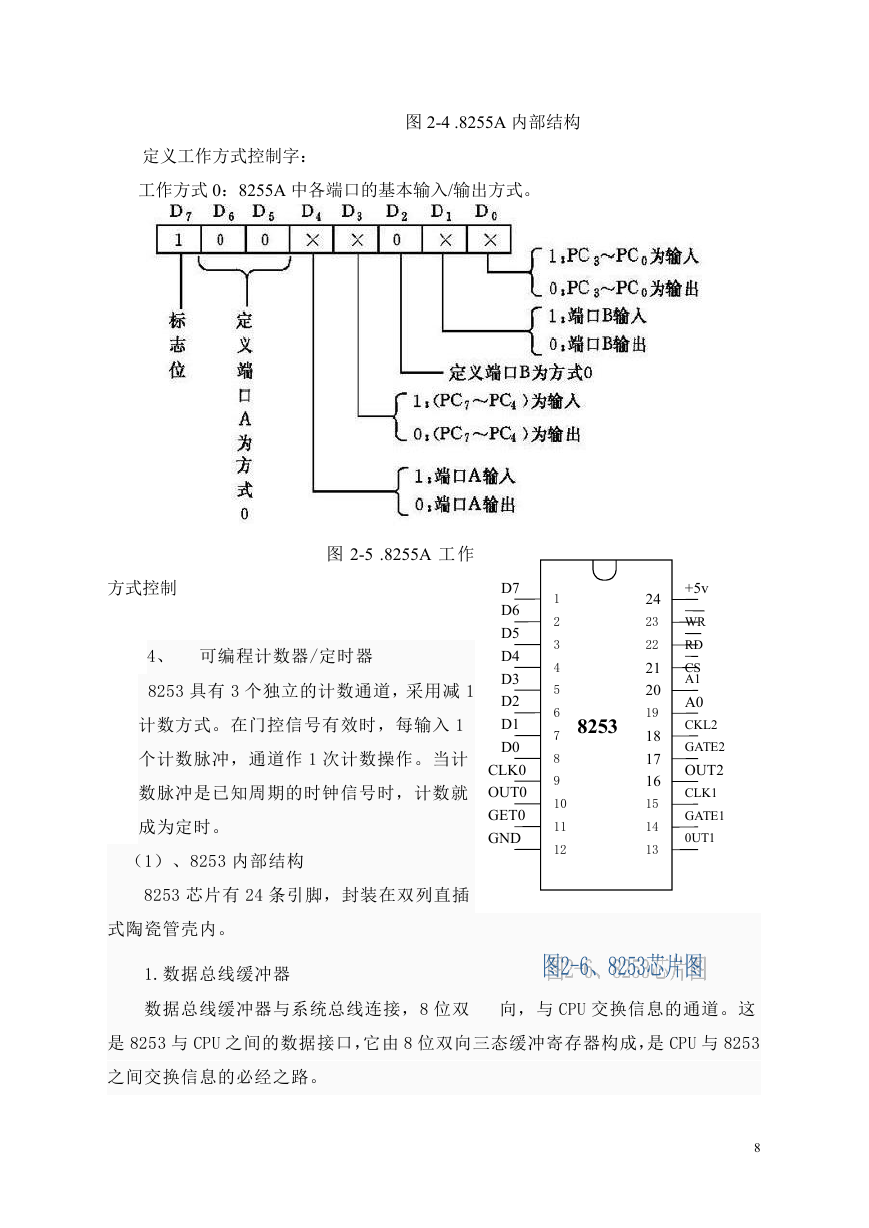

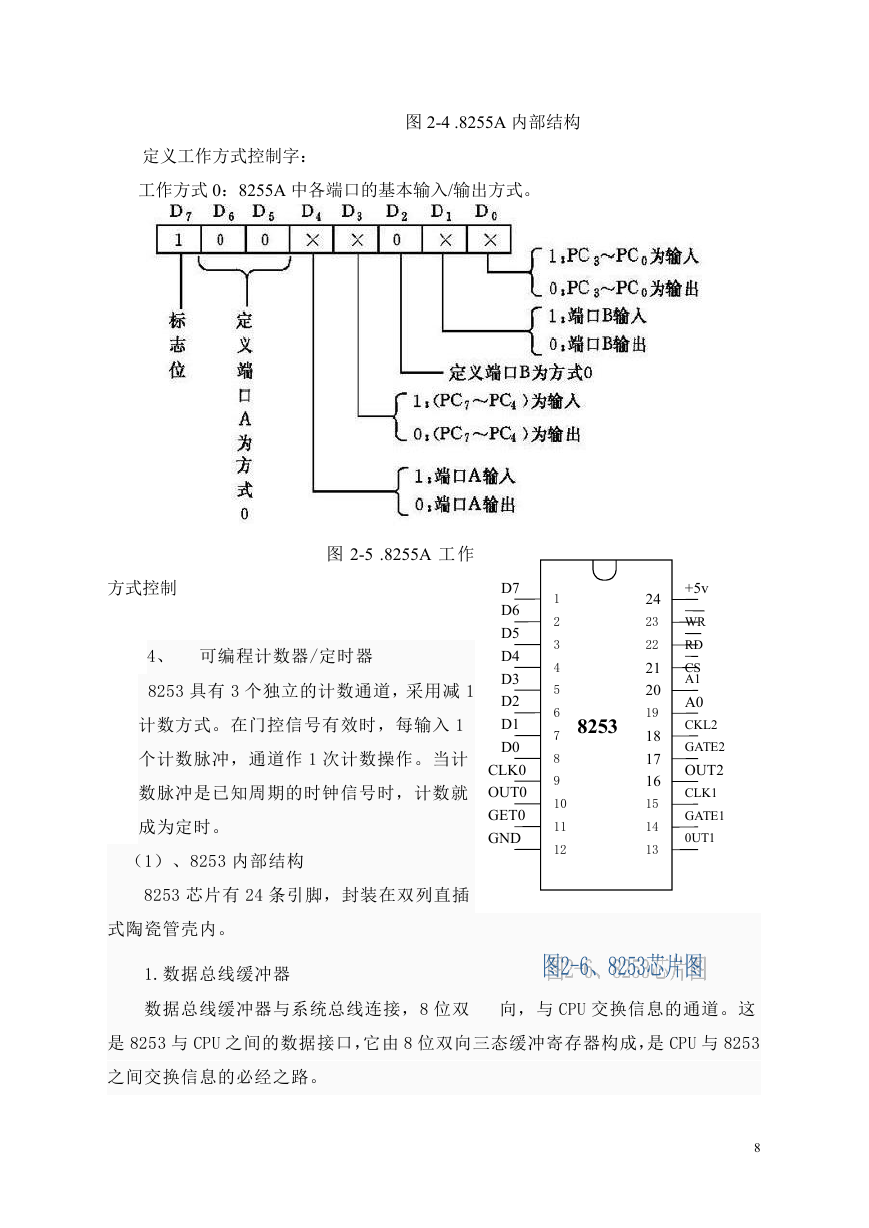

4、 可编程计数器/定时器

8253 具有 3 个独立的计数通道,采用减 1

计数方式。在门控信号有效时,每输入 1

个计数脉冲,通道作 1 次计数操作。当计

数脉冲是已知周期的时钟信号时,计数就

成为定时。

(1)、8253 内部结构

8253 芯片有 24 条引脚,封装在双列直插

式陶瓷管壳内。

1.数据总线缓冲器

D7

D6

D5

D4

D3

D2

D1

D0

CLK0

OUT0

GET0

GND

1

2

3

4

5

6

7

8

9

10

11

12

8253

+5v

WR

RD

CS

A1

A0

CKL2

GATE2

OUT2

CLK1

GATE1

0UT1

24

23

22

21

20

19

18

17

16

15

14

13

数据总线缓冲器与系统总线连接,8 位双 向,与 CPU 交换信息的通道。这

是 8253 与 CPU 之间的数据接口,它由 8 位双向三态缓冲寄存器构成,是 CPU 与 8253

之间交换信息的必经之路。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc