Altera 与 Xilinx FPGA 同在一个 JTAG 链中的配置方法

因为Altera与Xilinx两家FPGA绝大部分FPGA都符合JTAG标准,所以可以在同一个

JTAG链中进行配置。(这里需确认具体的器件型号序列支持JTAG标准)这里仅仅说

明在QuartusII中对Altera的FPGA进行配置步骤。(本地下载与远程下载两种方式)配

置Xilinx的FPGA必须在JTAG Programmer环境下进行。

1. 本地下载方式介绍及步骤

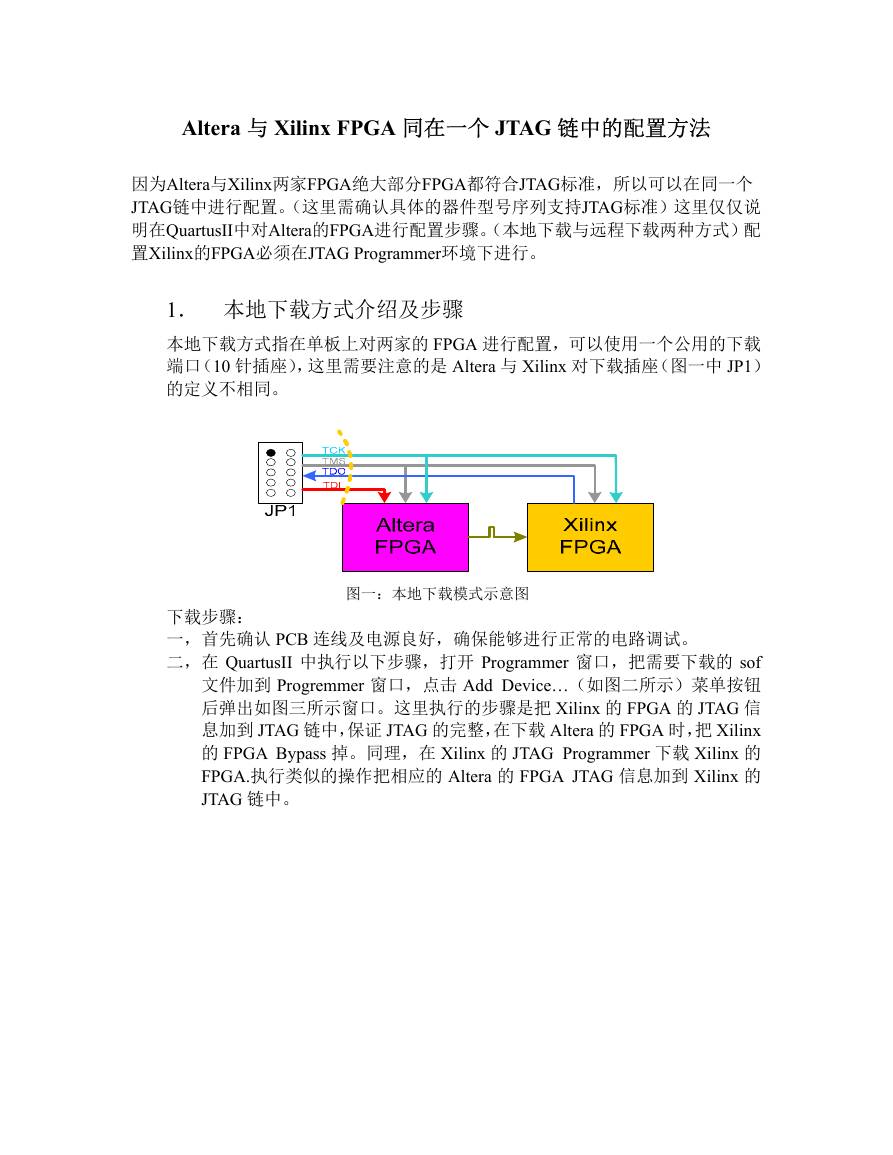

本地下载方式指在单板上对两家的 FPGA 进行配置,可以使用一个公用的下载

端口(10 针插座),这里需要注意的是 Altera 与 Xilinx 对下载插座(图一中 JP1)

的定义不相同。

图一:本地下载模式示意图

下载步骤:

一,首先确认 PCB 连线及电源良好,确保能够进行正常的电路调试。

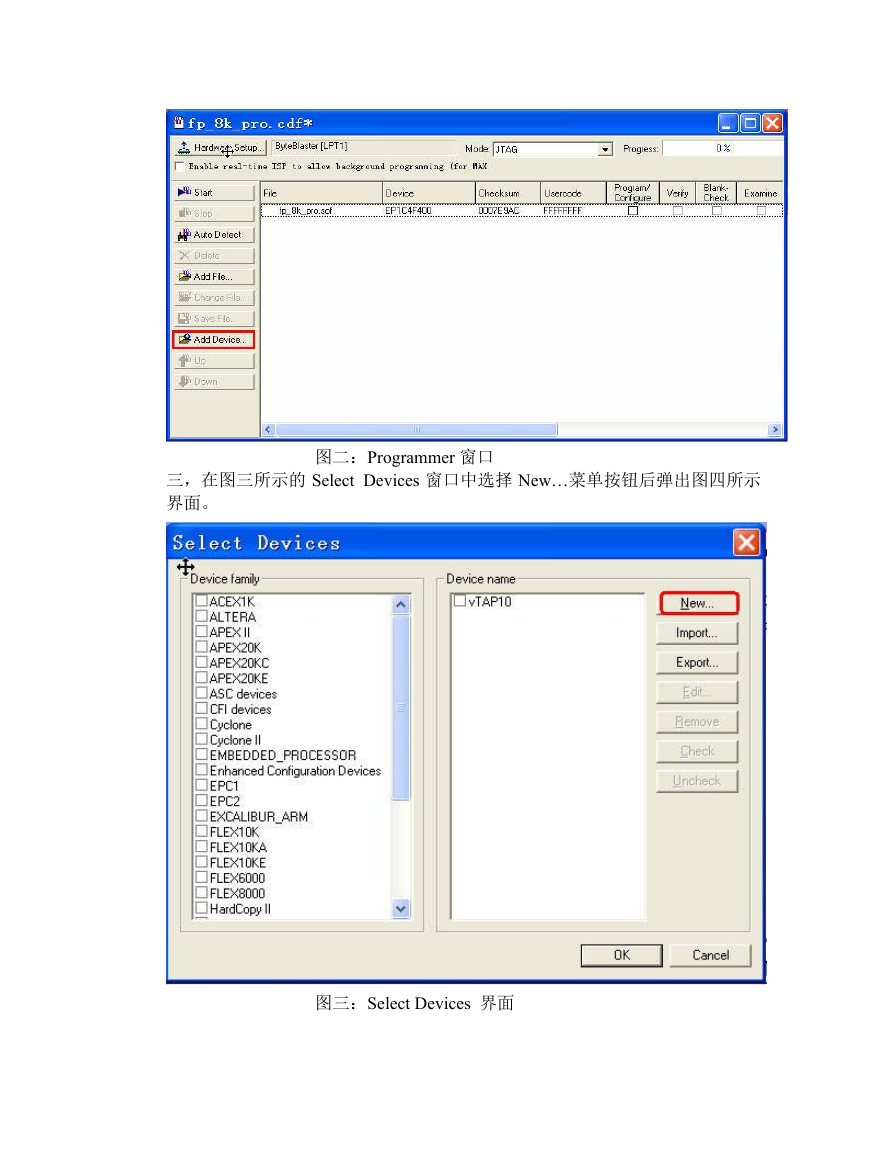

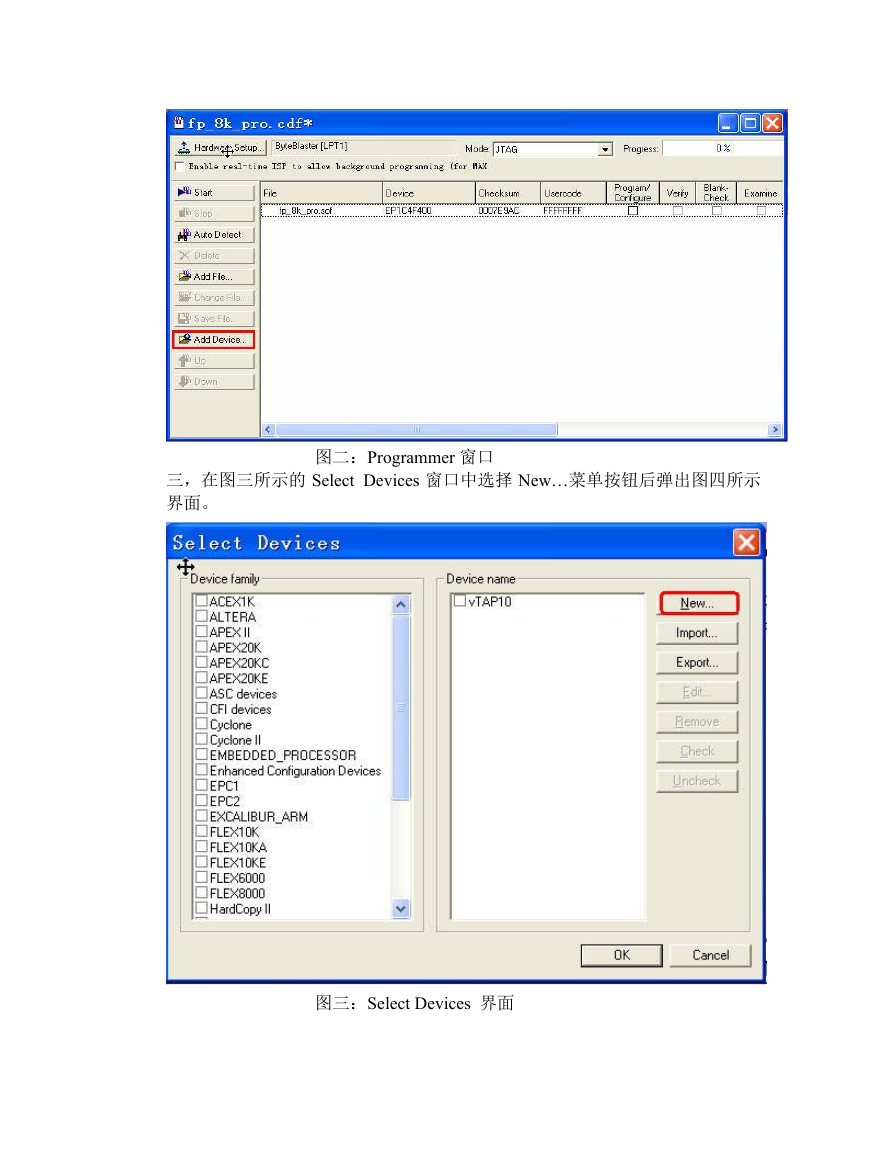

二,在 QuartusII 中执行以下步骤,打开 Programmer 窗口,把需要下载的 sof

文件加到 Progremmer 窗口,点击 Add Device…(如图二所示)菜单按钮

后弹出如图三所示窗口。这里执行的步骤是把 Xilinx 的 FPGA 的 JTAG 信

息加到 JTAG 链中,保证 JTAG 的完整,在下载 Altera 的 FPGA 时,把 Xilinx

的 FPGA Bypass 掉。同理,在 Xilinx 的 JTAG Programmer 下载 Xilinx 的

FPGA.执行类似的操作把相应的 Altera 的 FPGA JTAG 信息加到 Xilinx 的

JTAG 链中。

�

图二:Programmer 窗口

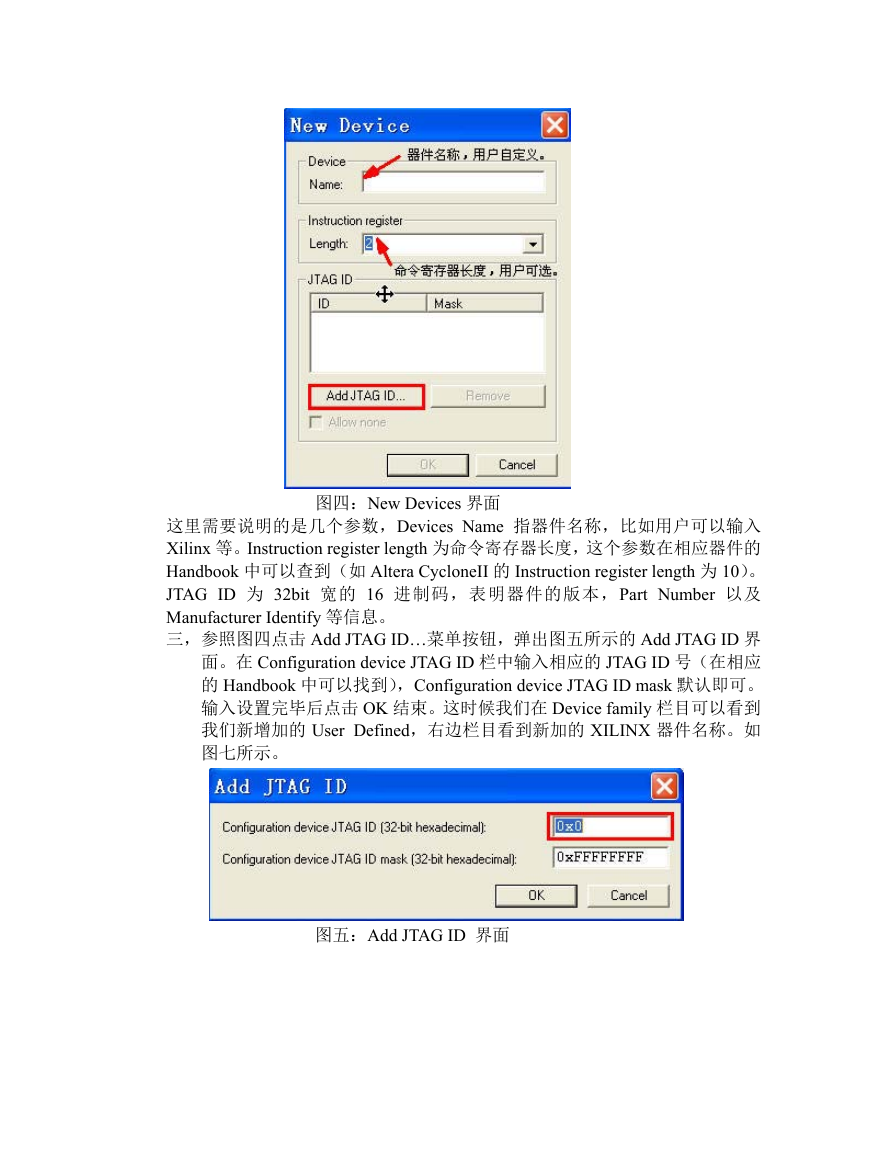

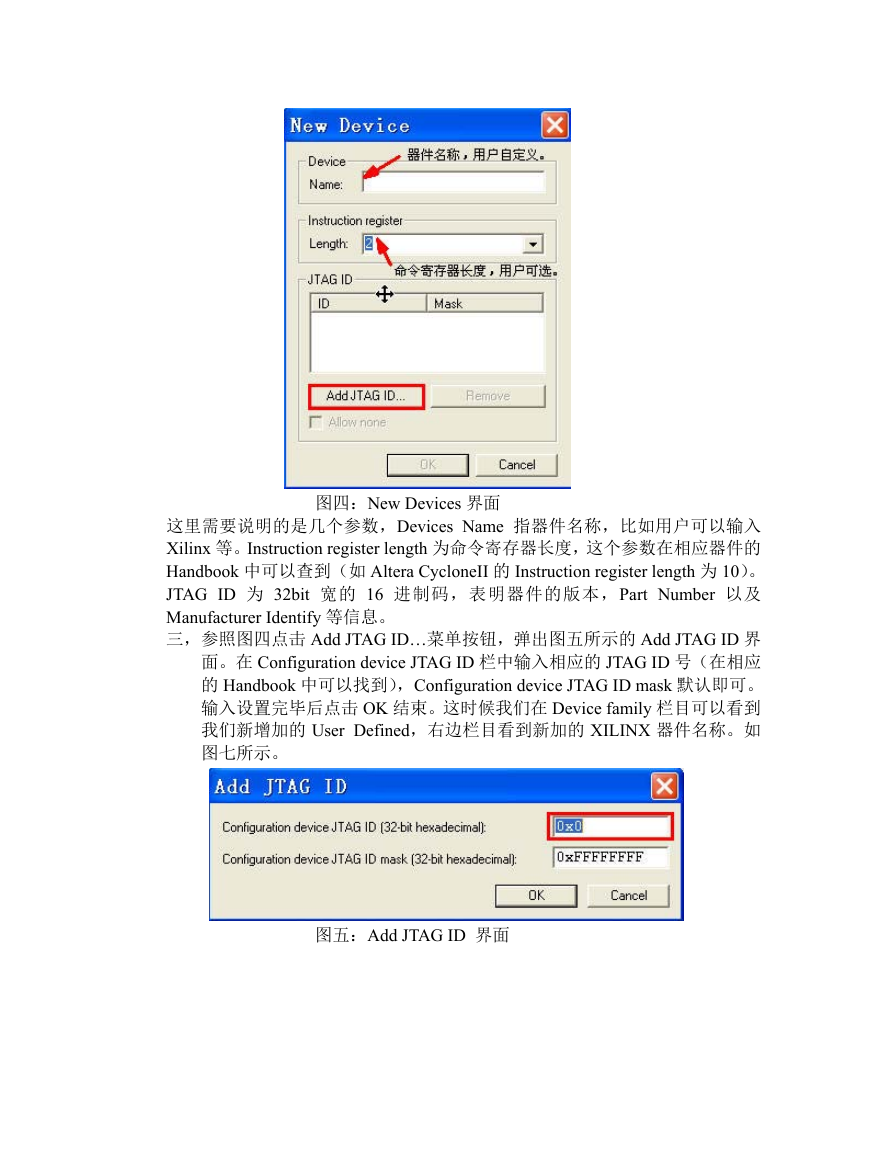

三,在图三所示的 Select Devices 窗口中选择 New…菜单按钮后弹出图四所示

界面。

图三:Select Devices 界面

�

图四:New Devices 界面

这里需要说明的是几个参数,Devices Name 指器件名称,比如用户可以输入

Xilinx 等。Instruction register length 为命令寄存器长度,这个参数在相应器件的

Handbook 中可以查到(如 Altera CycloneII 的 Instruction register length 为 10)。

JTAG ID 为 32bit 宽的 16 进制码,表明器件的版本,Part Number 以及

Manufacturer Identify 等信息。

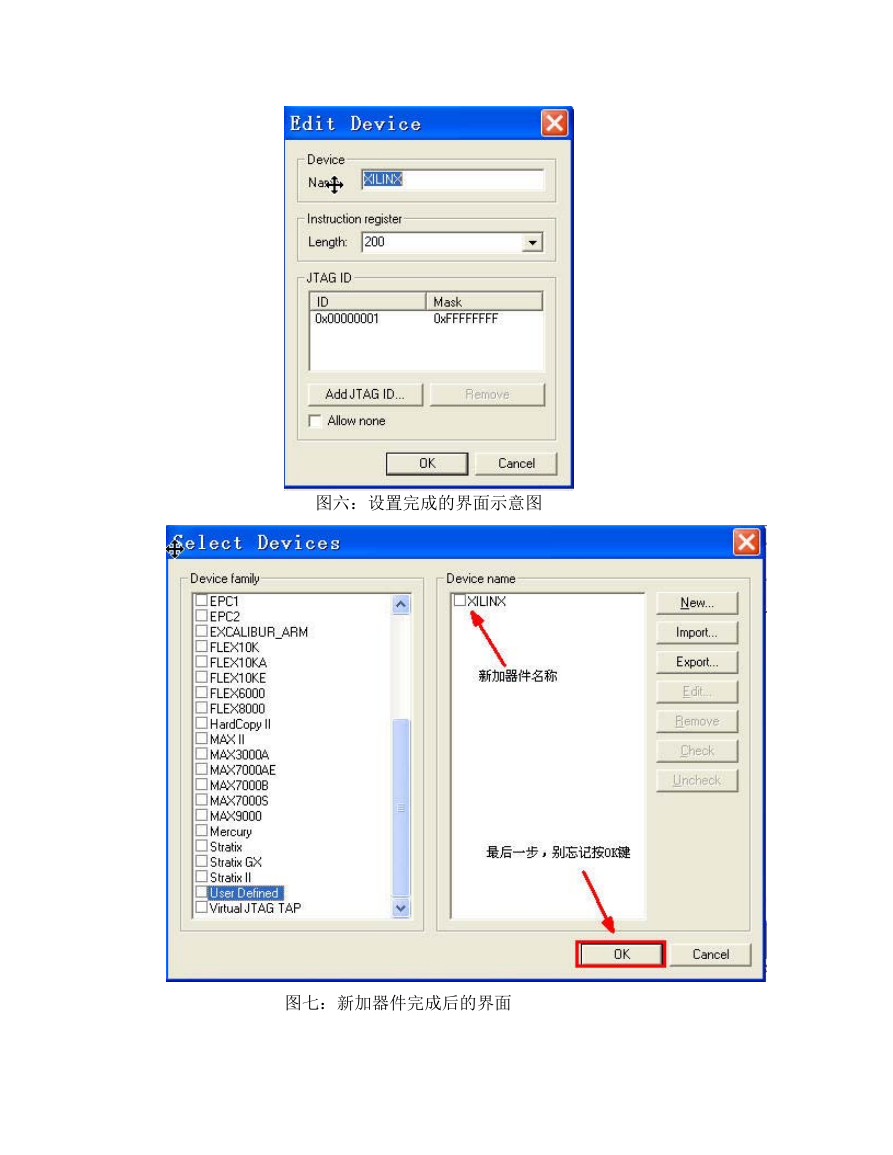

三,参照图四点击 Add JTAG ID…菜单按钮,弹出图五所示的 Add JTAG ID 界

面。在 Configuration device JTAG ID 栏中输入相应的 JTAG ID 号(在相应

的 Handbook 中可以找到),Configuration device JTAG ID mask 默认即可。

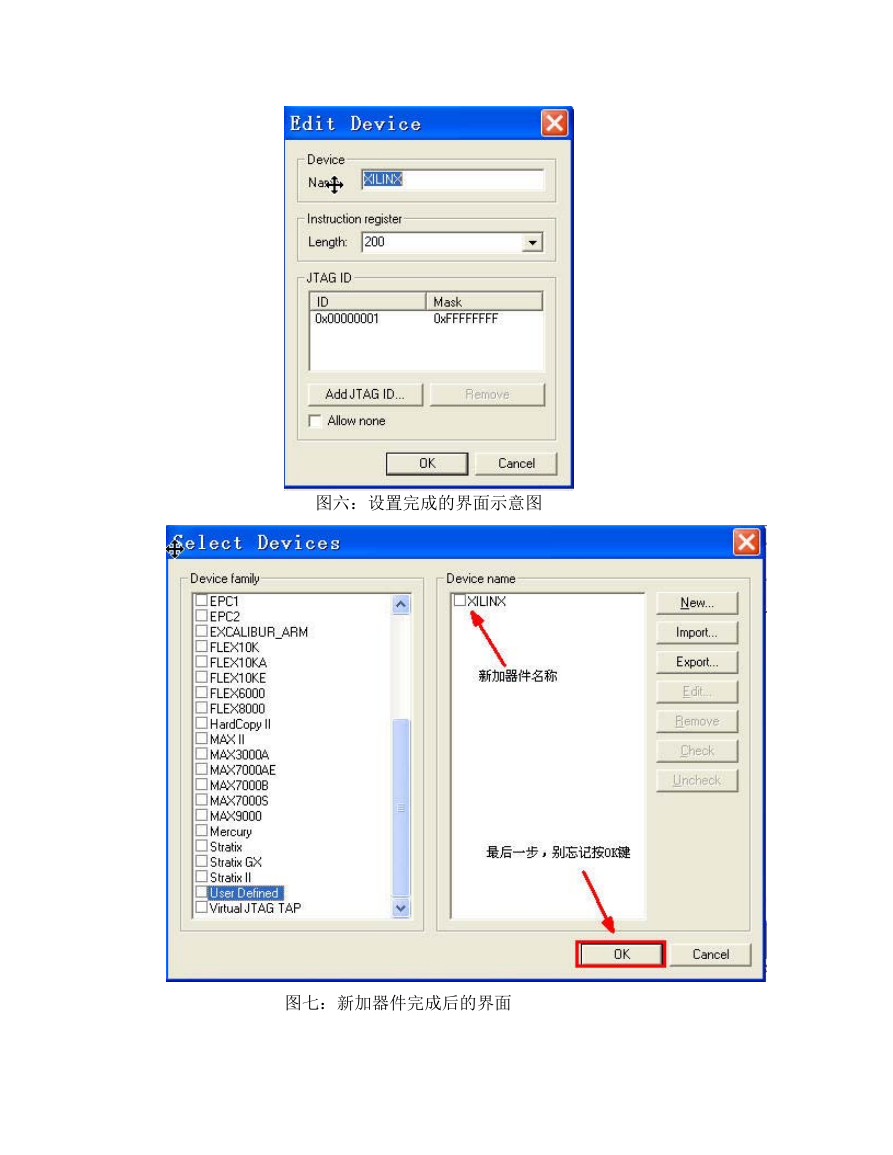

输入设置完毕后点击 OK 结束。这时候我们在 Device family 栏目可以看到

我们新增加的 User Defined,右边栏目看到新加的 XILINX 器件名称。如

图七所示。

图五:Add JTAG ID 界面

�

图六:设置完成的界面示意图

图七:新加器件完成后的界面

�

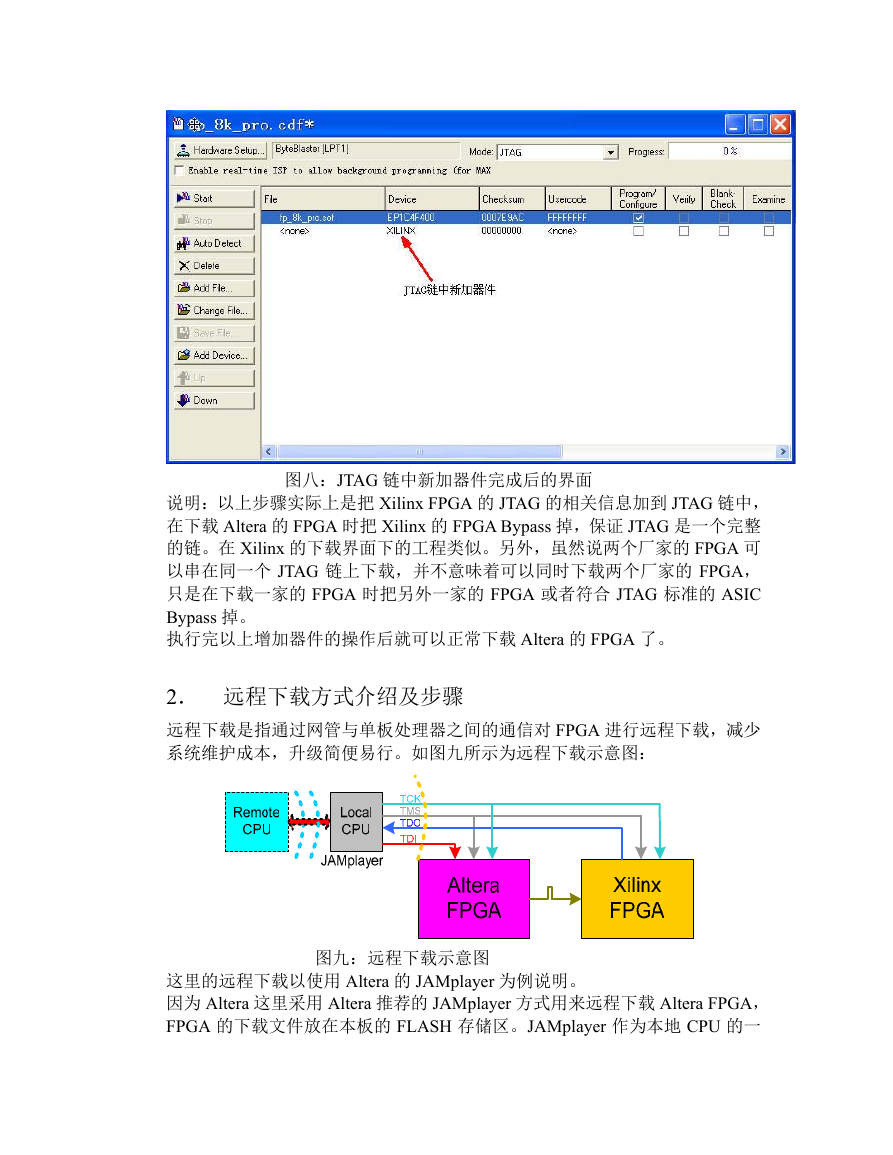

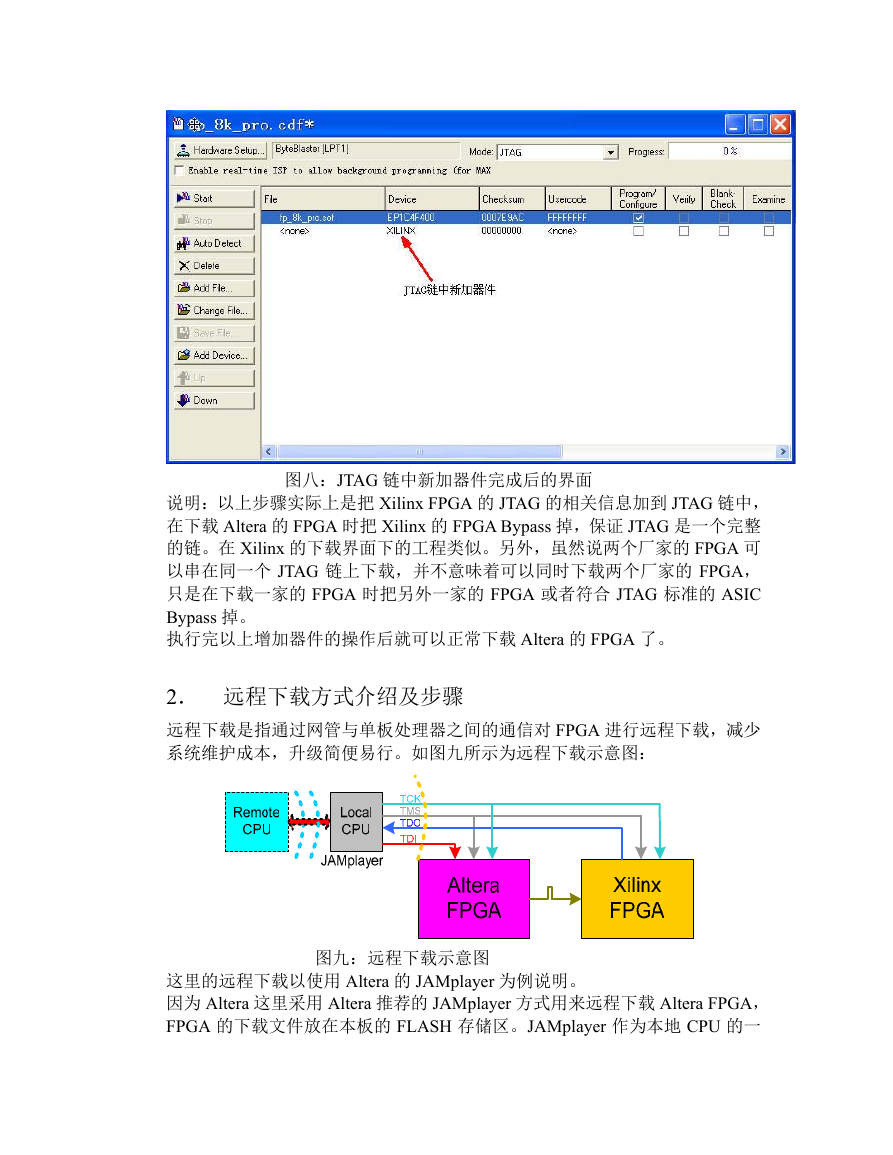

图八:JTAG 链中新加器件完成后的界面

说明:以上步骤实际上是把 Xilinx FPGA 的 JTAG 的相关信息加到 JTAG 链中,

在下载 Altera 的 FPGA 时把 Xilinx 的 FPGA Bypass 掉,保证 JTAG 是一个完整

的链。在 Xilinx 的下载界面下的工程类似。另外,虽然说两个厂家的 FPGA 可

以串在同一个 JTAG 链上下载,并不意味着可以同时下载两个厂家的 FPGA,

只是在下载一家的 FPGA 时把另外一家的 FPGA 或者符合 JTAG 标准的 ASIC

Bypass 掉。

执行完以上增加器件的操作后就可以正常下载 Altera 的 FPGA 了。

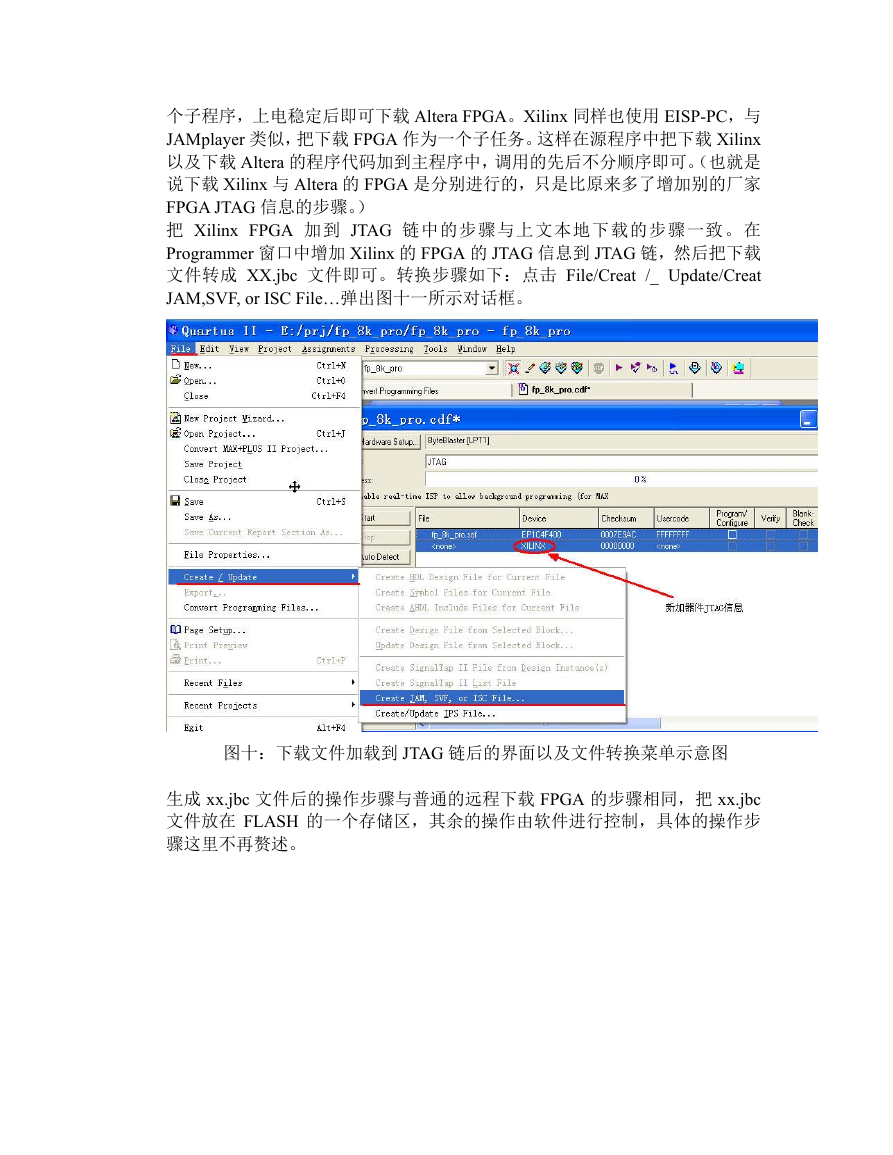

2. 远程下载方式介绍及步骤

远程下载是指通过网管与单板处理器之间的通信对 FPGA 进行远程下载,减少

系统维护成本,升级简便易行。如图九所示为远程下载示意图:

图九:远程下载示意图

这里的远程下载以使用 Altera 的 JAMplayer 为例说明。

因为 Altera 这里采用 Altera 推荐的 JAMplayer 方式用来远程下载 Altera FPGA,

FPGA 的下载文件放在本板的 FLASH 存储区。JAMplayer 作为本地 CPU 的一

�

个子程序,上电稳定后即可下载 Altera FPGA。Xilinx 同样也使用 EISP-PC,与

JAMplayer 类似,把下载 FPGA 作为一个子任务。这样在源程序中把下载 Xilinx

以及下载 Altera 的程序代码加到主程序中,调用的先后不分顺序即可。(也就是

说下载 Xilinx 与 Altera 的 FPGA 是分别进行的,只是比原来多了增加别的厂家

FPGA JTAG 信息的步骤。)

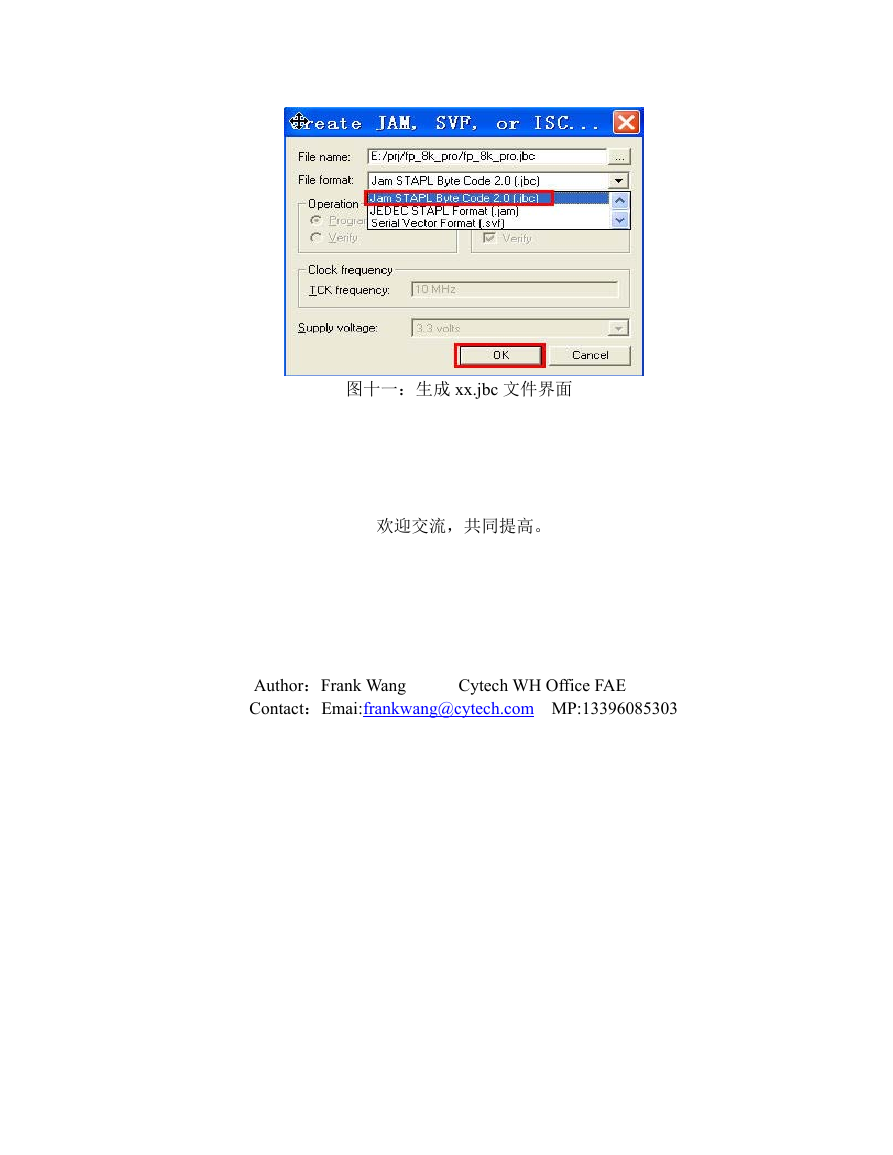

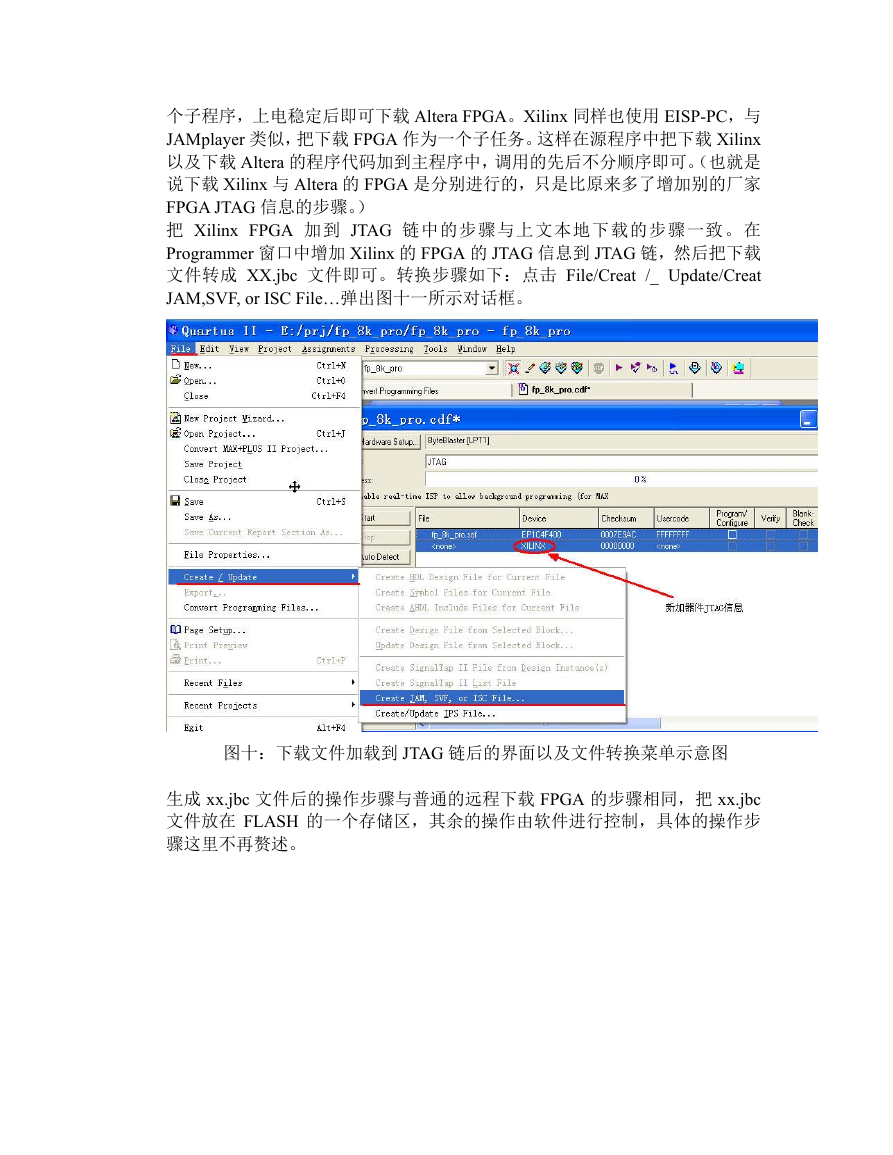

把 Xilinx FPGA 加到 JTAG 链中的步骤与上文本地下载的步骤一致。在

Programmer 窗口中增加 Xilinx 的 FPGA 的 JTAG 信息到 JTAG 链,然后把下载

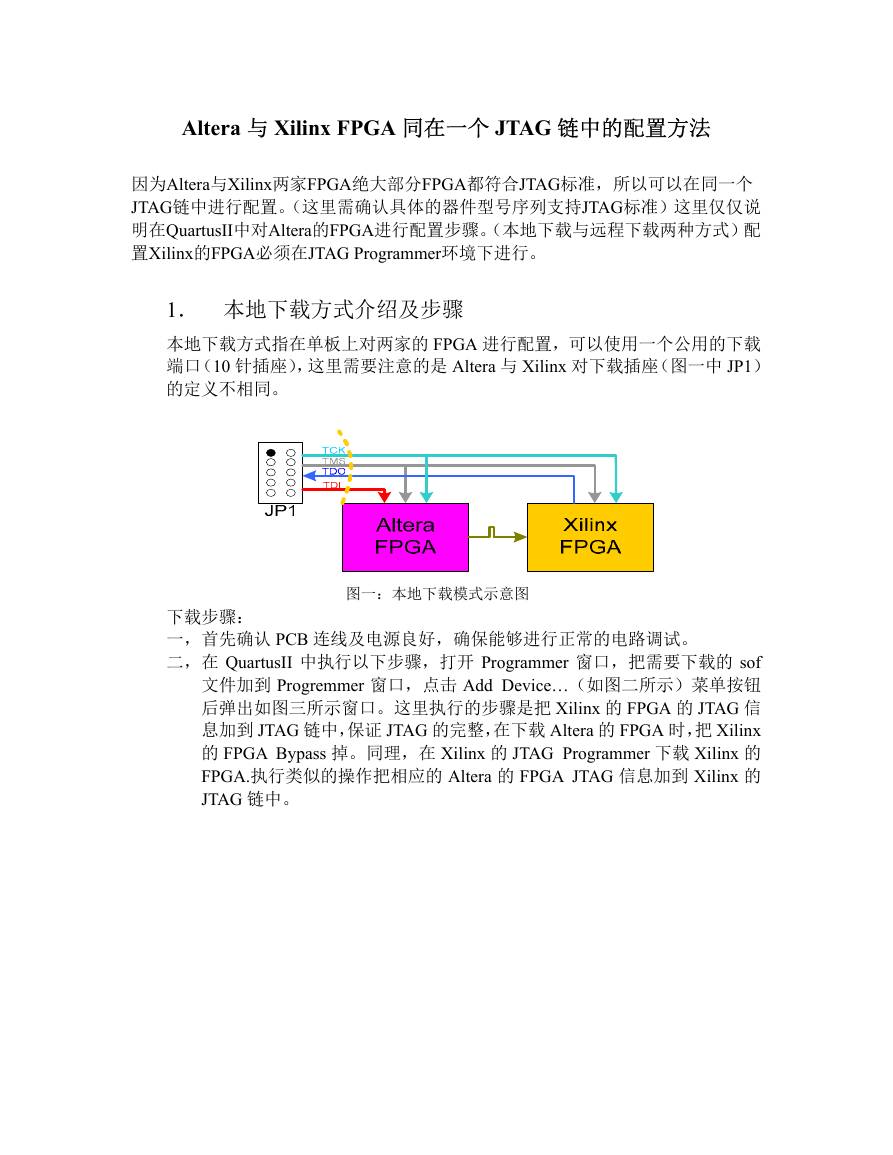

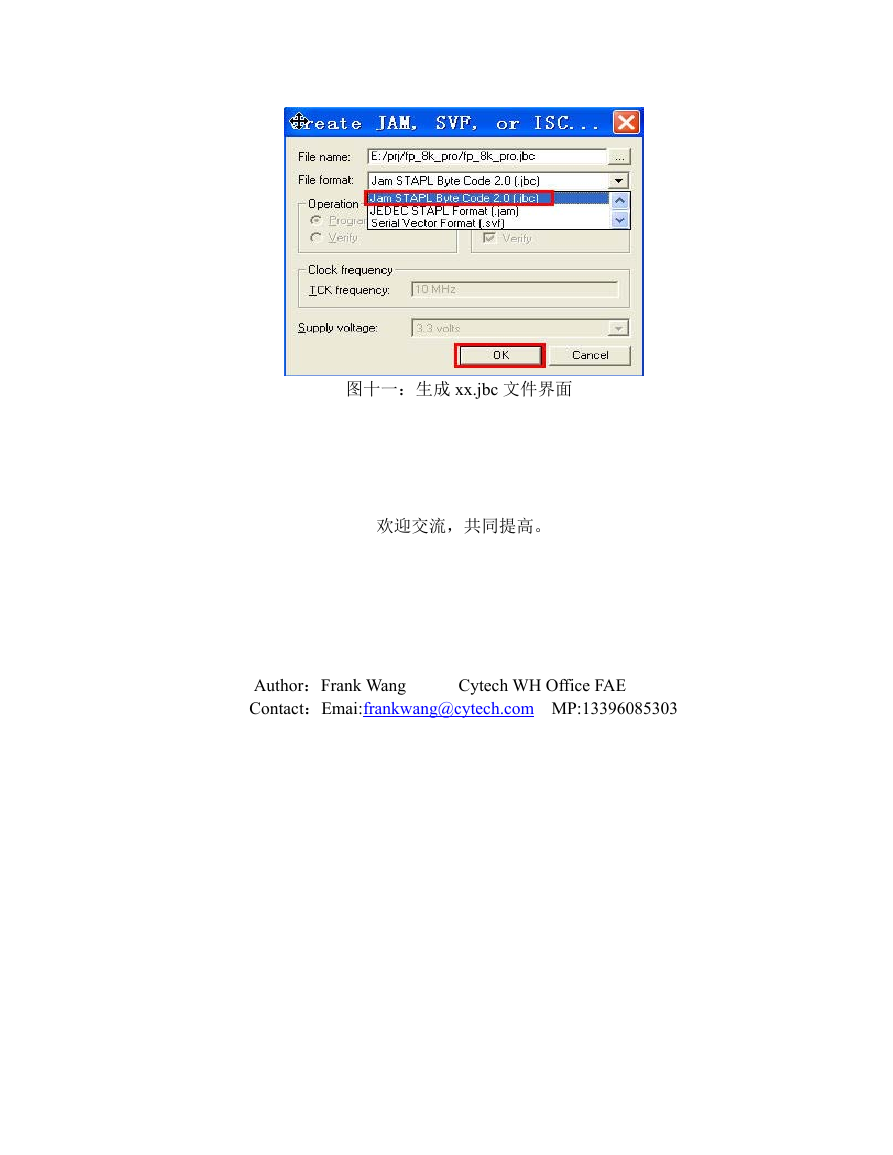

文件转成 XX.jbc 文件即可。转换步骤如下:点击 File/Creat /_ Update/Creat

JAM,SVF, or ISC File…弹出图十一所示对话框。

图十:下载文件加载到 JTAG 链后的界面以及文件转换菜单示意图

生成 xx.jbc 文件后的操作步骤与普通的远程下载 FPGA 的步骤相同,把 xx.jbc

文件放在 FLASH 的一个存储区,其余的操作由软件进行控制,具体的操作步

骤这里不再赘述。

�

图十一:生成 xx.jbc 文件界面

欢迎交流,共同提高。

Author:Frank Wang Cytech WH Office FAE

Contact:Emai:frankwang@cytech.com MP:13396085303

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc