We are limited only by our energy and imagenation.

一、嵌入式系统开发的基础知识

1.嵌入式系统的特点、分类、发展与应用,熟悉嵌入式系统的逻辑组成。

(1)特点:

专用性

隐蔽性 :嵌入式系统是被包装在内部

资源受限:要求小型化、轻型化、低功耗及低成本,因此软硬件资源受到限制

高可靠性:任何误动作都可能会产生致命的后果

软件固化:软件都固化在只读存储器 ROM 中,用户不能随意更改其程序功能

实时性

(2)逻辑组成

硬件:

1)处理器(运算器、控制器、存储器)

目前所有的处理器都是微处理器 中央处理器(CPU)和协助处理器(数字信号处理器

DSP、图像处理器、通信处理器)

2)存储器(随机存储器 RAM 和只读存储器 ROM)

RAM 分为动态 DRAM 和静态 SRAM 两种。DRAM 电路简单、集成度高、功耗小、成本低,但

速度稍慢慢;SRAM 电路较复杂、集成度低、功耗较大、成本高,但工作速度很快,适合用

作指令和数据的高速缓冲存储器 RAM 当关机或断电时,其中的信息都会消失,属于易失性存

储器

ROM 属于不易失性存储器。分为电可擦可编程只读存储器(存放固件)和闪速存储器

(Flash ROM 简称内存)。内存的工作原理:在低

压下,存储的信息可读但不可写,这类似于 ROM;在较高的电压下,

所存储的信息可以更改和删除,这有类似于 RAM。

3)I/O 设备与 I/O 接口

4)数据总线

软件

(3)分类

按嵌入式系统的软硬件技术复杂程度进行分类:

1 )低端系统 采用 4 位或 8 位单片机,在工控领域和白色家电领域占主导地位,如计算

器、遥控器、充电器、空调、传真机、BP 机等。

2)中端系统 采用 8 位/16 位/32 位单片机,主要用于普通手机、摄像机、录像机、电子

游戏机等。

3)高端系统采用 32 位/64 位单片机,主要用于智能手机、调制解调器、掌上计算机、路

由器、数码相机等。

(4)发展

20 世纪 60 年代初,第一个工人的现代嵌入式系统(阿波罗导航计算机);

20 世纪 60 年代中期,嵌入式计算机批量生产;

20 世纪 70 年代,微处理器出现;

1

�

We are limited only by our energy and imagenation.

20 世纪 80 年代中期,外围电路的元器件被集成到处理器芯片中,昂贵的模拟电路元件

能被数字电路替代;

20 世纪 90 年代中期 SOC 出现,集成电路进入超深亚微米乃至纳米加工时代

2.嵌入式系统的组成与微电子技术(集成电路、EDA、SoC、IP 核等技术的作用和发展)

2.1 集成电路 IC

集成电路的制造大约需要几百道工序,工艺复杂。集成电路是在硅衬底上制作而成的。

硅衬底是将单晶硅锭经切割、研磨和抛光后制成的像镜面一样光滑的圆形薄片,它的厚度不

足 1mm,其直径可以是 6、8、12 英寸甚至更大这种硅片称为硅抛光片,用于集成电路的制

造。

制造集成电路的工艺技术称为硅平面工艺,包括氧化、光刻、掺杂等多项工序。把这些

工序反复交叉使用,最终在硅片上制成包含多层电路及电子元件的集成电路。

集成电路的特点:体积小、重量轻、可靠性高。其工作速度主要取决于逻辑门电路的晶

体管的尺寸。尺寸越小,工作频率就越高,门电路的开关速度就越快。

2.2 EDA(电子设计自动化)

2.3 SoC 芯片(片上系统)

既包含数字电路,也可以包含模拟电路,还可以包含数模混合电路和射频电路。SoC 芯

片可以是一个 CPU,单核 SoC,也可以由多个 CPU 和/或 DSP,即多核 SoC。

开发流程:

(1)总体设计 可以采用系统设计语言 System C(或称 IEEE 1666,它是 C++的扩充)

或 System Vetilog 语言对 SoC 芯片的软硬件作统一的描述,按照系统需求说明书确定 SoC

的性能能参数,并据此进行系统全局的设计。

(2)逻辑设计 将总体设计的结果用 RTL(寄存器传输级描述语言)语言进行描述(源

文件)后,在使用逻辑综合将源文件进行综合生成,生成最简的布尔表达式核心好的连接关

系(以类型为 EDF 的 EDA 工业标准文件表示)。

(3)综合和仿真

(4)芯片制造 借助 EDA 中的布局布线工具。

2.4 IP 核

IC 设计文件:逻辑门级,包括各种基本的门电路;寄存器传输级,如寄存器、译码器、

数据转换器;行为级,如 CPU、DSP、存储器、总线与接口电路等。

核库中的设计文件均属于知识产权 IP 保护的范畴,所以称为“知识产权核”或“IP 核”。

IP 核是开发 SoC 的重要保证。按 IC 设计文件的类型,IP 通常分为:软核、固核、硬核。

IP 核的复用可以减少研发成本,缩短研发时间,是实现 SoC 的快速设计,尽早投放市场的

有效途径。

目前主要的 CPU 内核有 ARM、MIPS、PowerPC、Coldfile、x86、8051 等。ARM 内核占所

有 32 位嵌入式 RISC 处理器的 90%以上。

3.嵌入式系统与数字媒体(文本、图像和音频/视频等数字媒体的表示与处理)

(1)文本

2

�

We are limited only by our energy and imagenation.

含义:在计算机中的文字信息,最常用的一种数字媒体。

字符集及其编码

1)西方字符的编码

ASCII 字符集和 ASCII 编码,基本的 ASCII 字符集共 128 个字符,每个字符使用 7

个二进位制进行编码。

2)汉字的编码

汉子国家编码标准有 GB2312 和 GB18030。每个汉字用 2 个字节表示。GB2312 只有 6763

个汉字,经常不够用。GB18030 字符集与 UCS/Unicode 字符集基本兼容,采用不等长的编

码方法,单字节编码表示 ASCII 字符,与 ASCII 码兼容;双字节表示汉字,与 GB2312 保

持向下兼容(即 GB2312 中有的 GB18030 字符集都有)

3)UCS/Unicode 编码

文本类型

1)简单文本

只能顺序阅读。

2)丰富格式文本

有插图、对文字颜色等定义,调整页面,文本布局,插入声音视频等。

3)超文本

通过超链接实现跳转、导航、回溯等操作

(2)图像

图像获取过程的核心是模拟信号的数字化,处理步骤为:

1)扫描 将画面网格化,每个网格为一个取样点;

2)分色 将每个取样点的颜色分解成三原色;

3)取样 测量每个取样点的每个分量(基色)亮度值;

4)量化 把模拟量使用数字量来表示,A/D 转换;

数字图像的主要参数:图像大小(水平分辨率*竖直分辨率)、位平面数目、像素深

度、颜色模型;

一幅图像的数据量计算公式:

图像数据量=图像大小*像素深度/8

(3)音频/视频

音频/视频信息的数字化,处理步骤为:

1)取样

2)量化

3)编码

数字音频的主要参数:取样频率、量化位数、声道数目、使用的压缩编码方法、比特

率(每秒钟的数据量)

压缩前 波形声音的码率(比特率)= 取样频率 * 量化为数 * 声道数(单位 b/s)

压缩后 码率 = 压缩前码率 / 压缩倍数(压缩比)

3

�

We are limited only by our energy and imagenation.

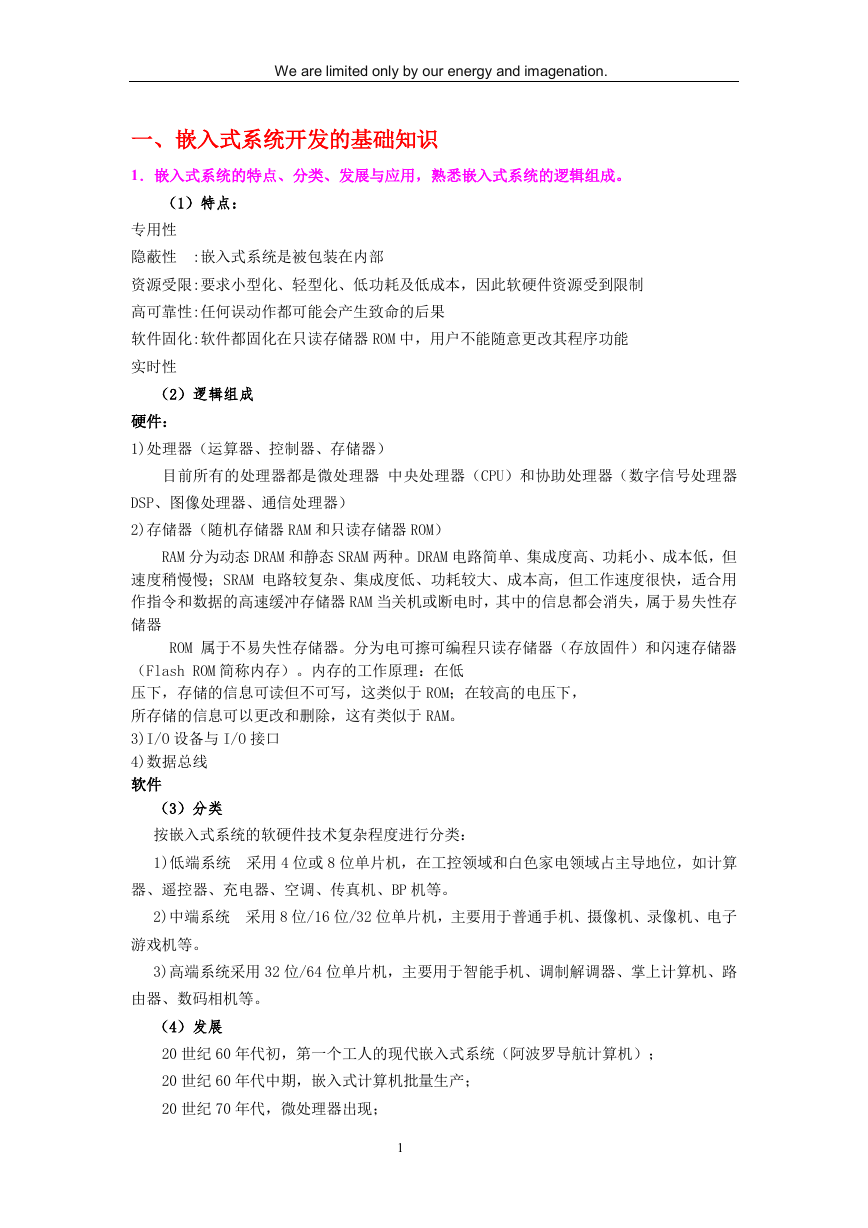

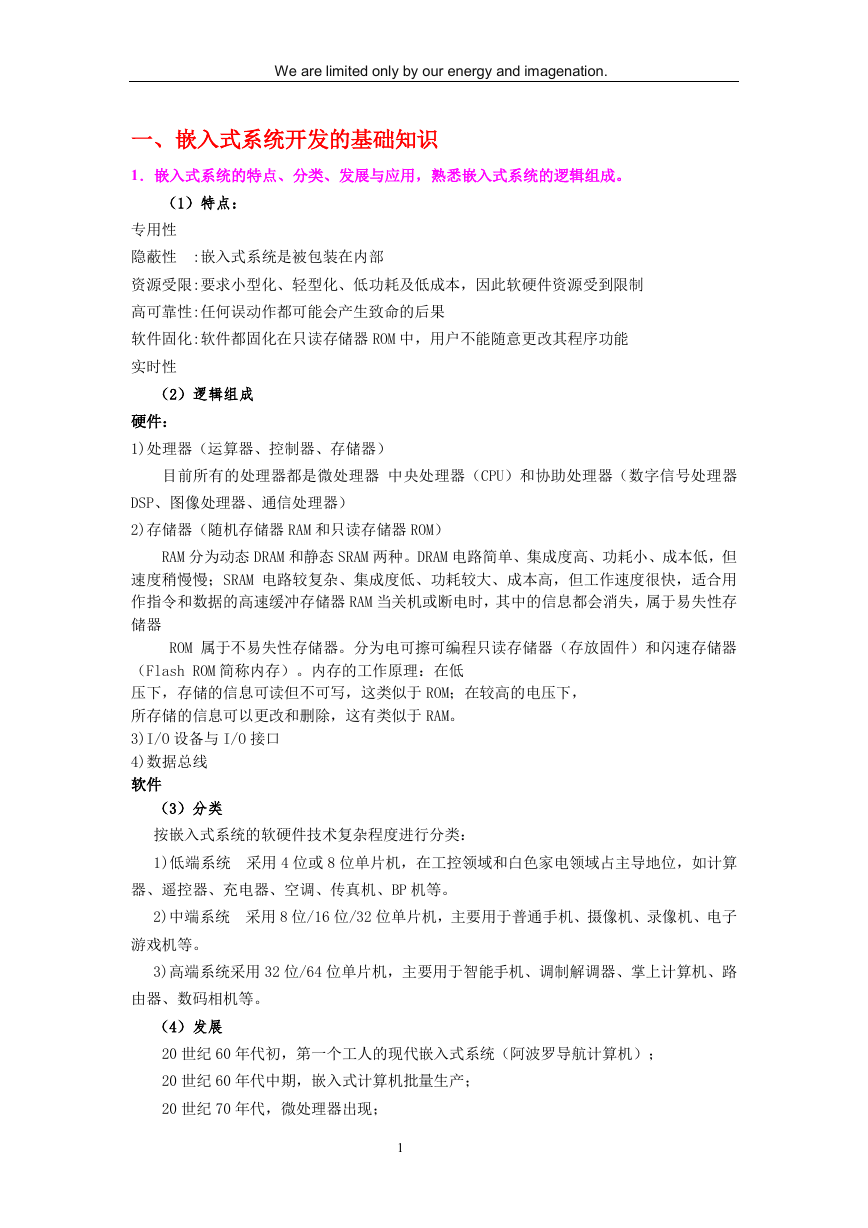

4.嵌入式系统与网络通信技术(数字通信与计算机网络,TCP/IP 协议,互联网接入技术

等)

(1)数字通信

(2)计算机网络

(3)音频/ TCP/IP 协议

(4)互联网接入技术

二、嵌入式处理器

1.嵌入式处理器的结构、特点与分类(不同类型的典型嵌入式处理器及其特点,嵌入式处

理器分类等)

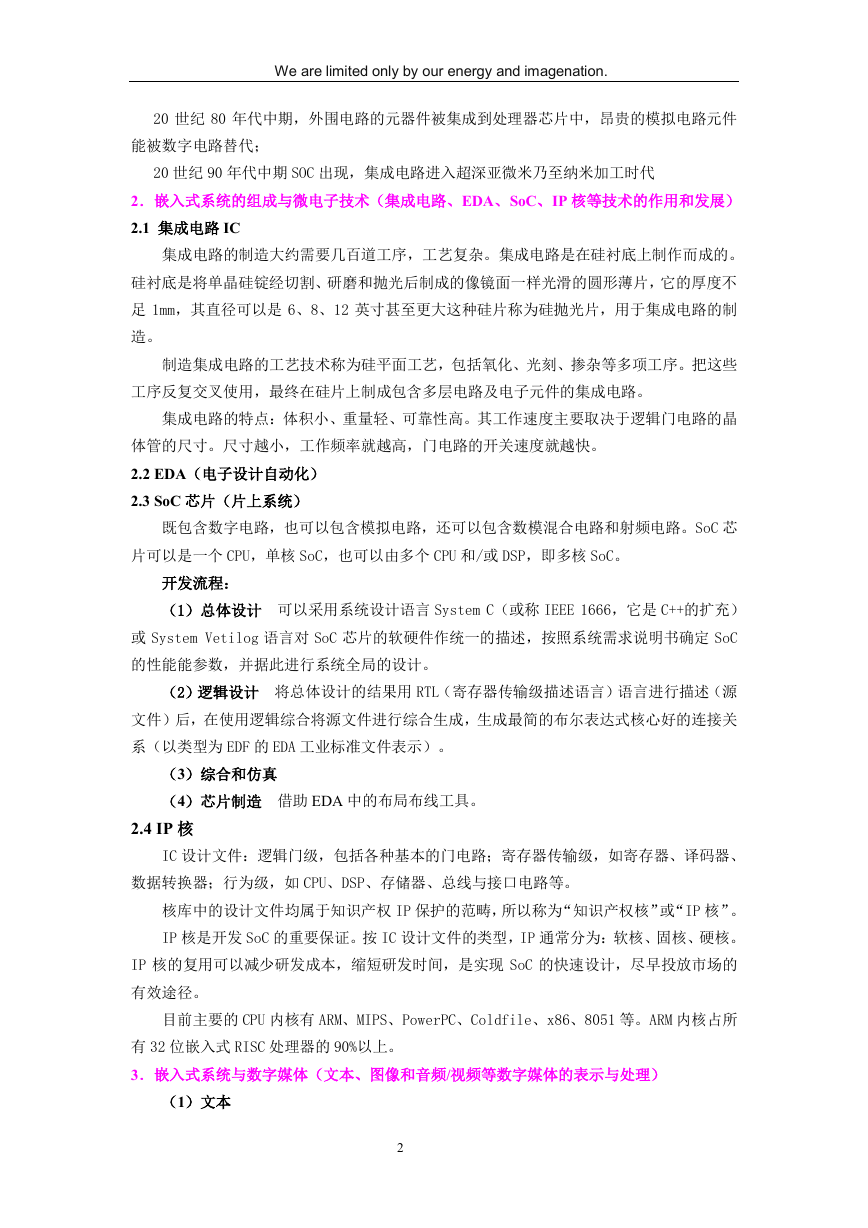

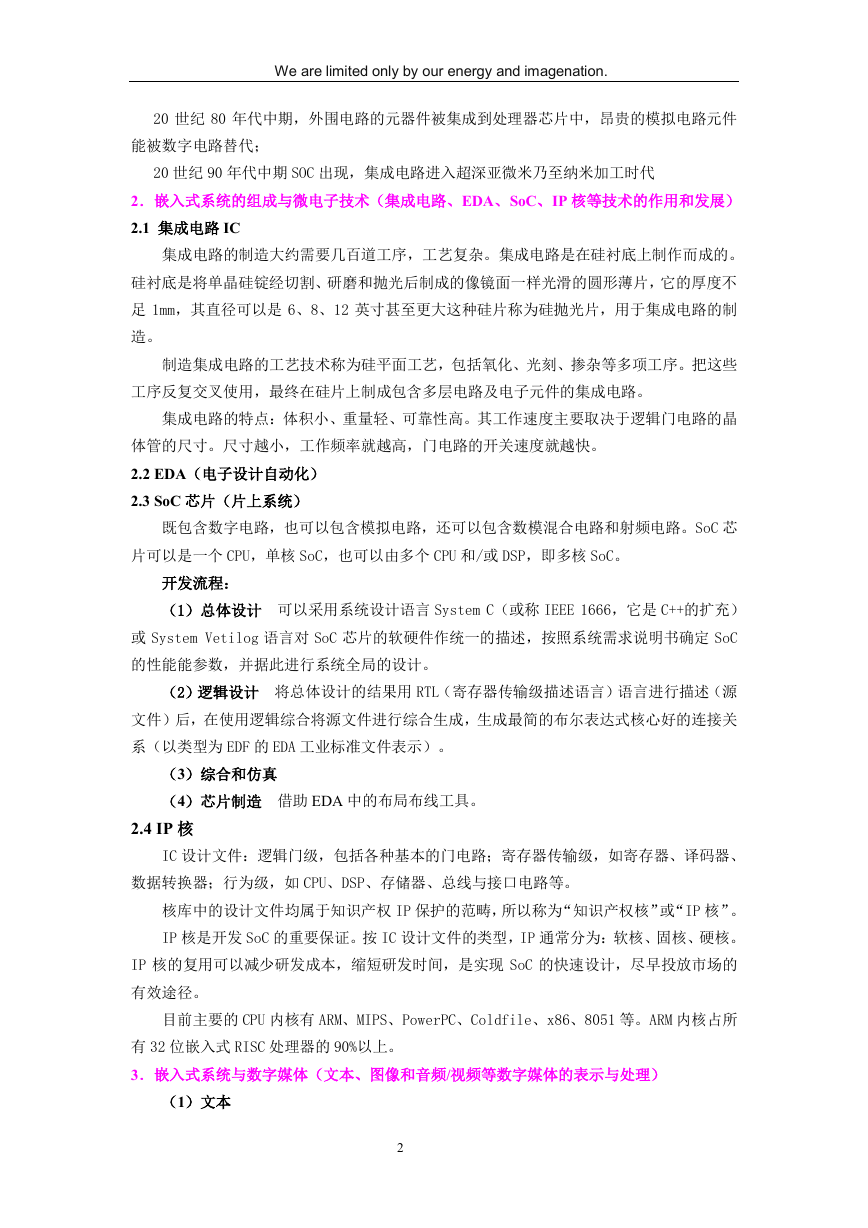

(1)不同内核嵌入式微控制器性能比较

性能

内核

51 内核

其他 8 位内核

16 位内核

其他 32 位内核

ARM

处理速度

低能耗

代码密度

内存>64KB

向量中断

低中段延时

低成本

多供资源

编译器选择

软件可移植性

差

好

差

差

好

好

好

好

好

好

差

好

差

差

好

好

好

差

一般

一般

一般

好

一般

差

好

好

好

差

一般

一般

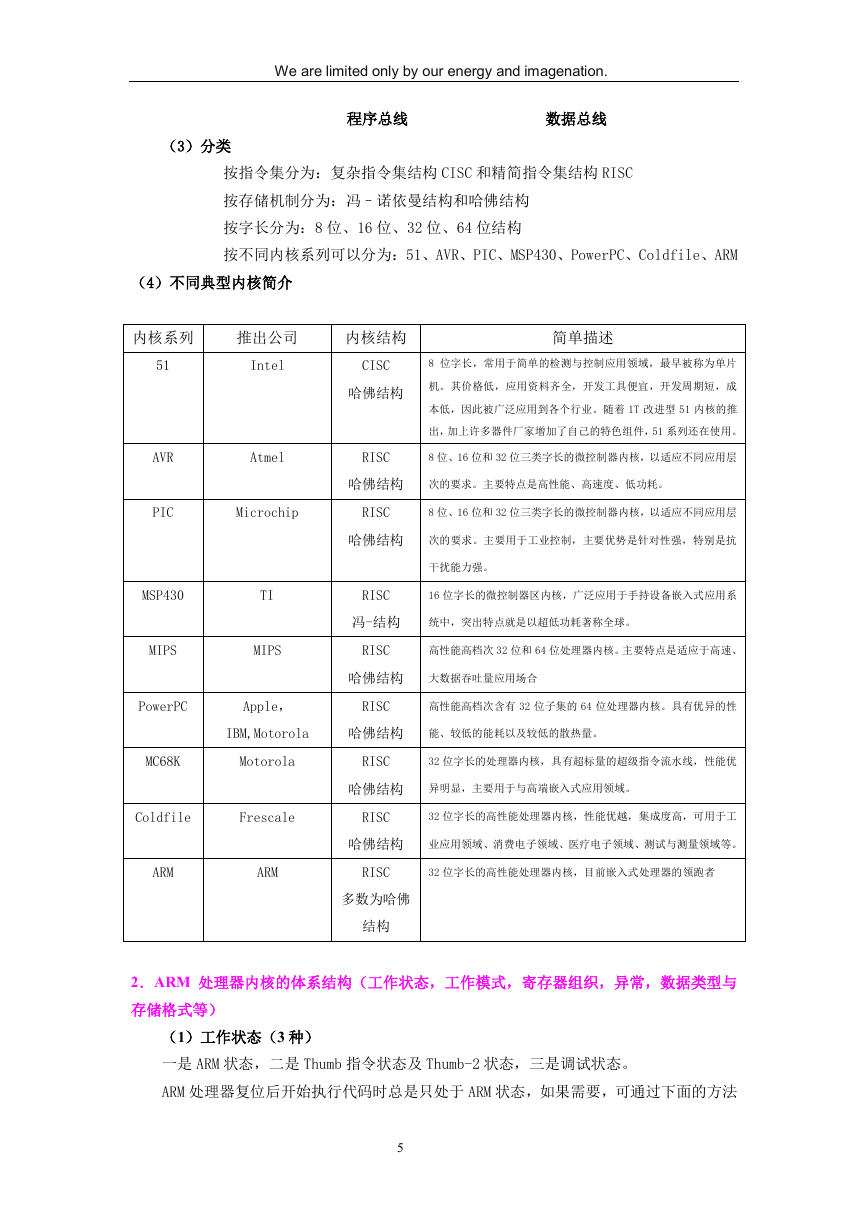

(2)冯–诺依曼结构和哈佛结构的区别

两者连接 CPU 程序存储器和数据存储器的方式不同

Cortex-M 内核

好

好

好

好

好

好

好

好

好

好

好

差

差

好

一般

差

差

差

一般

一般

冯–诺依曼结构

CPU 程序/数据存储器

哈佛结构 程序存储器 CPU 数据存储器

4

�

We are limited only by our energy and imagenation.

程序总线

数据总线

(3)分类

按指令集分为:复杂指令集结构 CISC 和精简指令集结构 RISC

按存储机制分为:冯–诺依曼结构和哈佛结构

按字长分为:8 位、16 位、32 位、64 位结构

按不同内核系列可以分为:51、AVR、PIC、MSP430、PowerPC、Coldfile、ARM

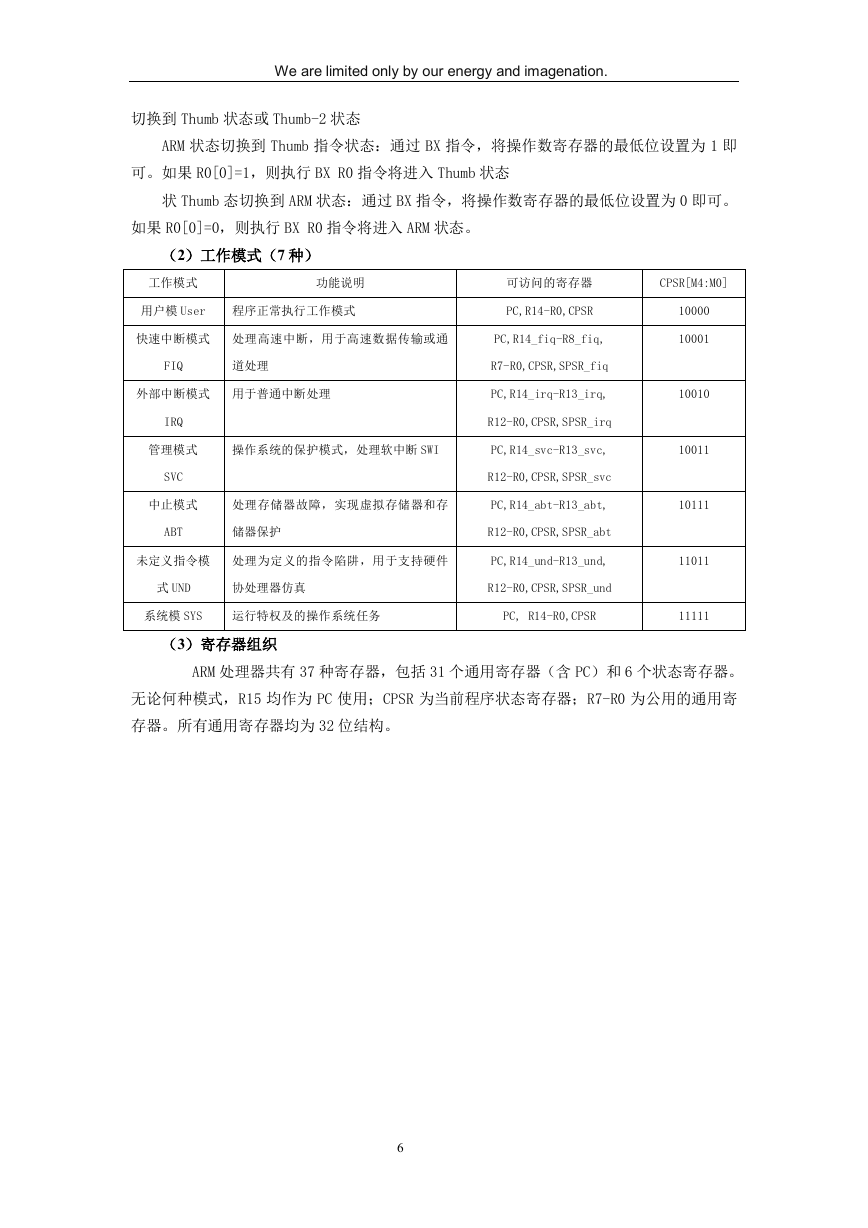

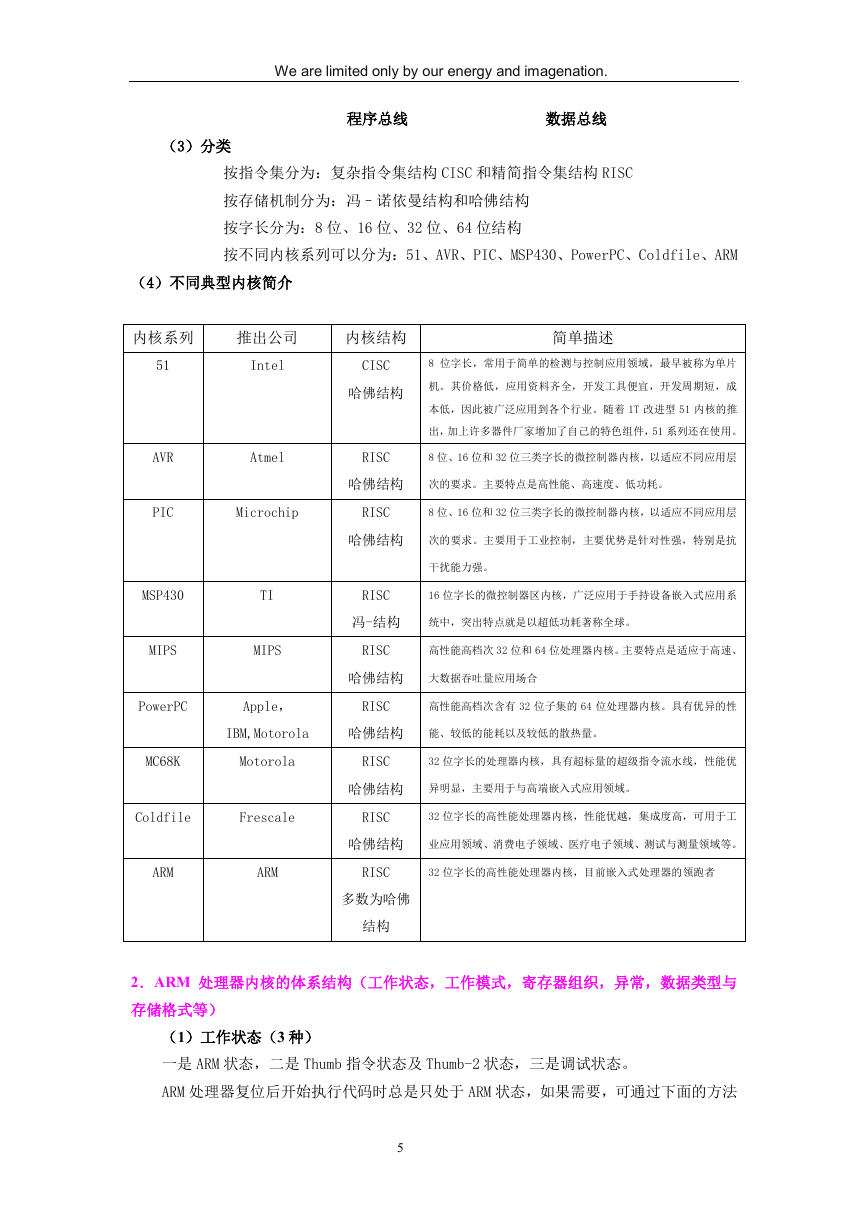

(4)不同典型内核简介

内核系列

推出公司

内核结构

简单描述

51

Intel

CISC

8 位字长,常用于简单的检测与控制应用领域,最早被称为单片

哈佛结构

机。其价格低,应用资料齐全,开发工具便宜,开发周期短,成

本低,因此被广泛应用到各个行业。随着 1T 改进型 51 内核的推

出,加上许多器件厂家增加了自己的特色组件,51 系列还在使用。

AVR

Atmel

RISC

8 位、16 位和 32 位三类字长的微控制器内核,以适应不同应用层

哈佛结构

次的要求。主要特点是高性能、高速度、低功耗。

PIC

Microchip

RISC

8 位、16 位和 32 位三类字长的微控制器内核,以适应不同应用层

哈佛结构

次的要求。主要用于工业控制,主要优势是针对性强,特别是抗

干扰能力强。

MSP430

TI

RISC

16 位字长的微控制器区内核,广泛应用于手持设备嵌入式应用系

冯-结构

统中,突出特点就是以超低功耗著称全球。

MIPS

MIPS

RISC

高性能高档次 32 位和 64 位处理器内核。主要特点是适应于高速、

哈佛结构

大数据吞吐量应用场合

PowerPC

Apple,

RISC

高性能高档次含有 32 位子集的 64 位处理器内核。具有优异的性

IBM,Motorola

哈佛结构

能、较低的能耗以及较低的散热量。

MC68K

Motorola

RISC

32 位字长的处理器内核,具有超标量的超级指令流水线,性能优

哈佛结构

异明显,主要用于与高端嵌入式应用领域。

Coldfile

Frescale

RISC

32 位字长的高性能处理器内核,性能优越,集成度高,可用于工

哈佛结构

业应用领域、消费电子领域、医疗电子领域、测试与测量领域等。

ARM

ARM

RISC

32 位字长的高性能处理器内核,目前嵌入式处理器的领跑者

多数为哈佛

结构

2.ARM 处理器内核的体系结构(工作状态,工作模式,寄存器组织,异常,数据类型与

存储格式等)

(1)工作状态(3 种)

一是 ARM 状态,二是 Thumb 指令状态及 Thumb-2 状态,三是调试状态。

ARM 处理器复位后开始执行代码时总是只处于 ARM 状态,如果需要,可通过下面的方法

5

�

We are limited only by our energy and imagenation.

切换到 Thumb 状态或 Thumb-2 状态

ARM 状态切换到 Thumb 指令状态:通过 BX 指令,将操作数寄存器的最低位设置为 1 即

可。如果 R0[0]=1,则执行 BX R0 指令将进入 Thumb 状态

状 Thumb 态切换到 ARM 状态:通过 BX 指令,将操作数寄存器的最低位设置为 0 即可。

如果 R0[0]=0,则执行 BX R0 指令将进入 ARM 状态。

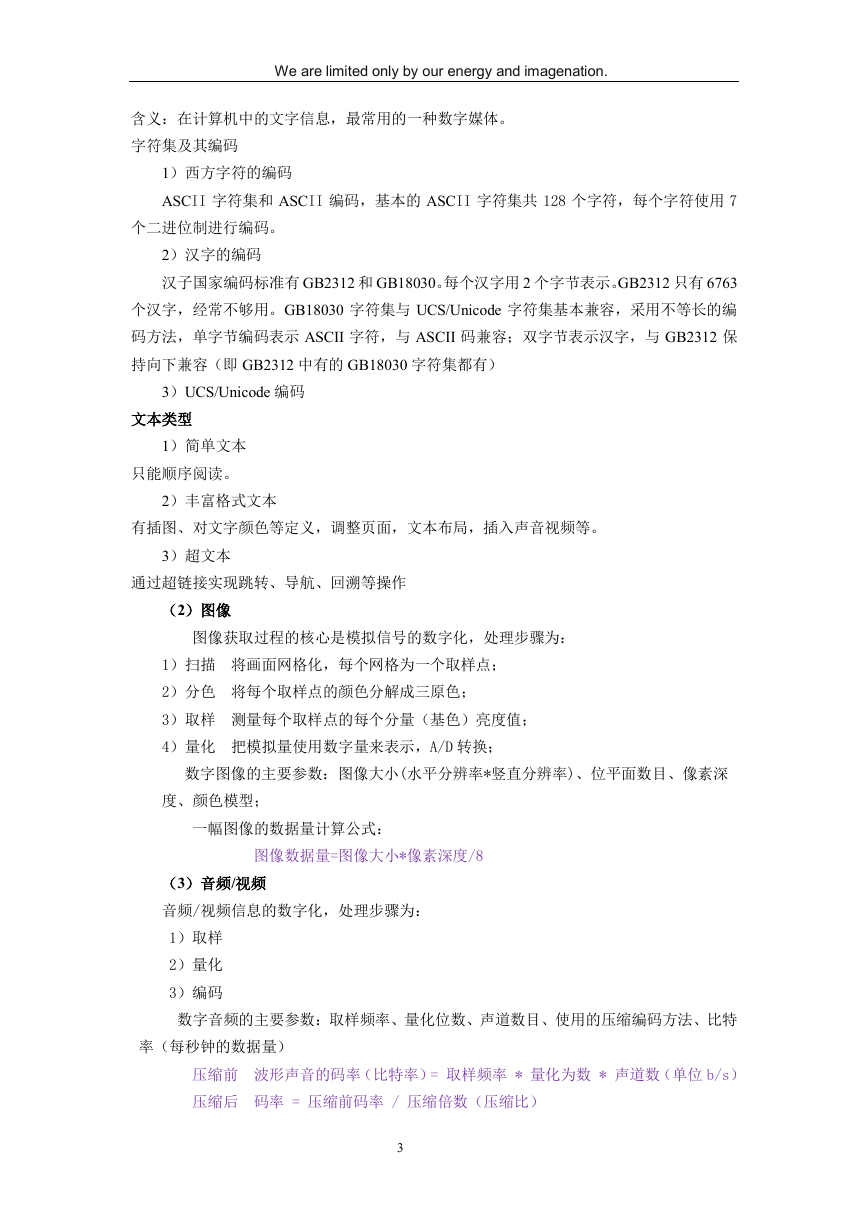

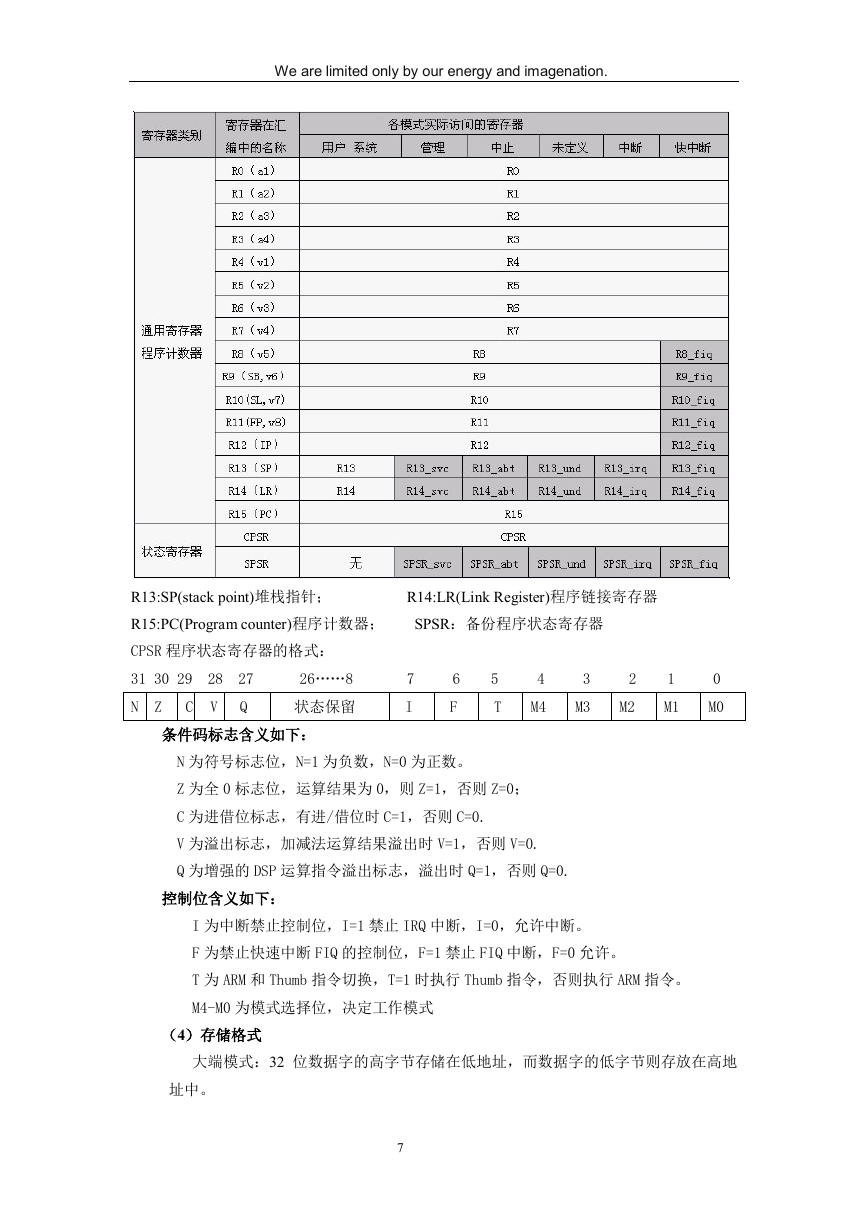

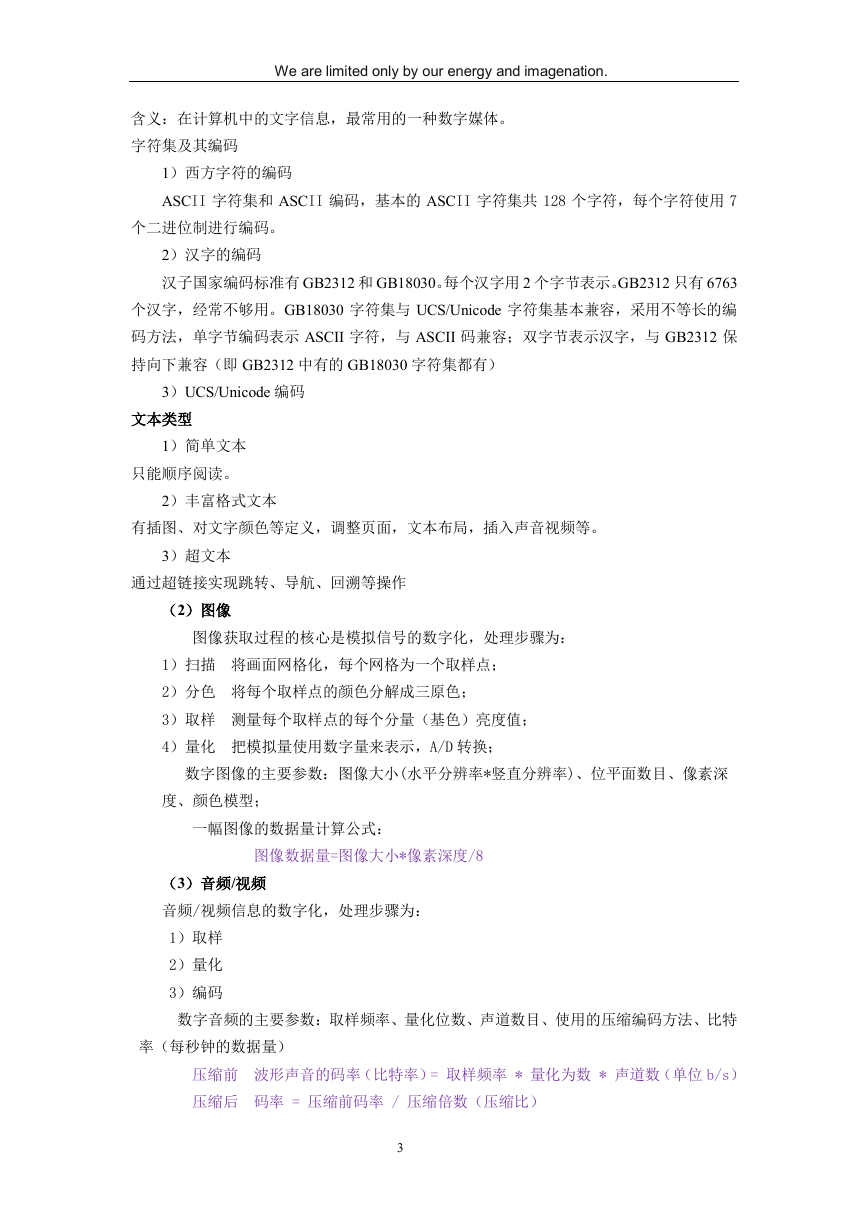

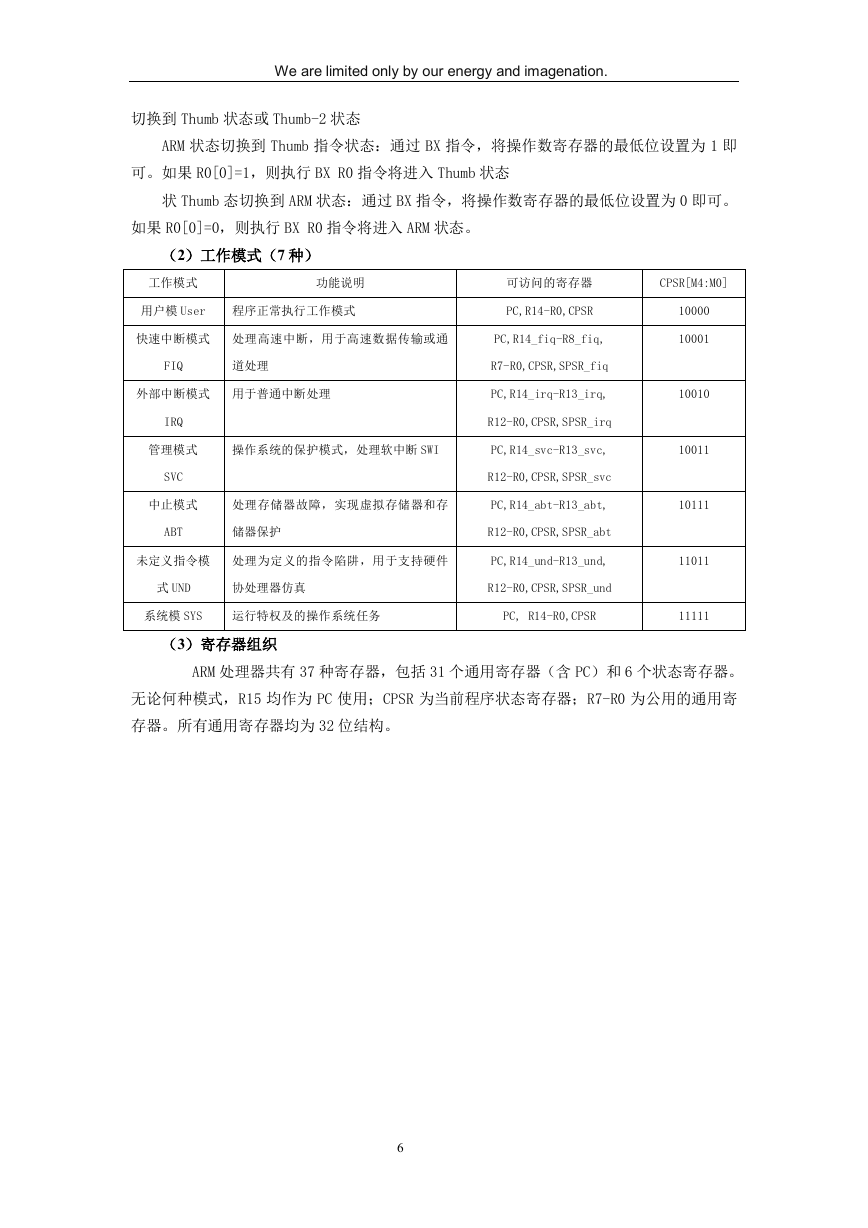

(2)工作模式(7 种)

工作模式

功能说明

可访问的寄存器

CPSR[M4:M0]

用户模 User 程序正常执行工作模式

PC,R14-R0,CPSR

快速中断模式

处理高速中断,用于高速数据传输或通

PC,R14_fiq-R8_fiq,

FIQ

道处理

R7-R0,CPSR,SPSR_fiq

10000

10001

外部中断模式

用于普通中断处理

PC,R14_irq-R13_irq,

10010

IRQ

R12-R0,CPSR,SPSR_irq

管理模式

操作系统的保护模式,处理软中断 SWI

PC,R14_svc-R13_svc,

10011

SVC

R12-R0,CPSR,SPSR_svc

中止模式

处理存储器故障,实现虚拟存储器和存

PC,R14_abt-R13_abt,

10111

ABT

储器保护

R12-R0,CPSR,SPSR_abt

未定义指令模

处理为定义的指令陷阱,用于支持硬件

PC,R14_und-R13_und,

11011

式 UND

协处理器仿真

R12-R0,CPSR,SPSR_und

系统模 SYS 运行特权及的操作系统任务

PC, R14-R0,CPSR

11111

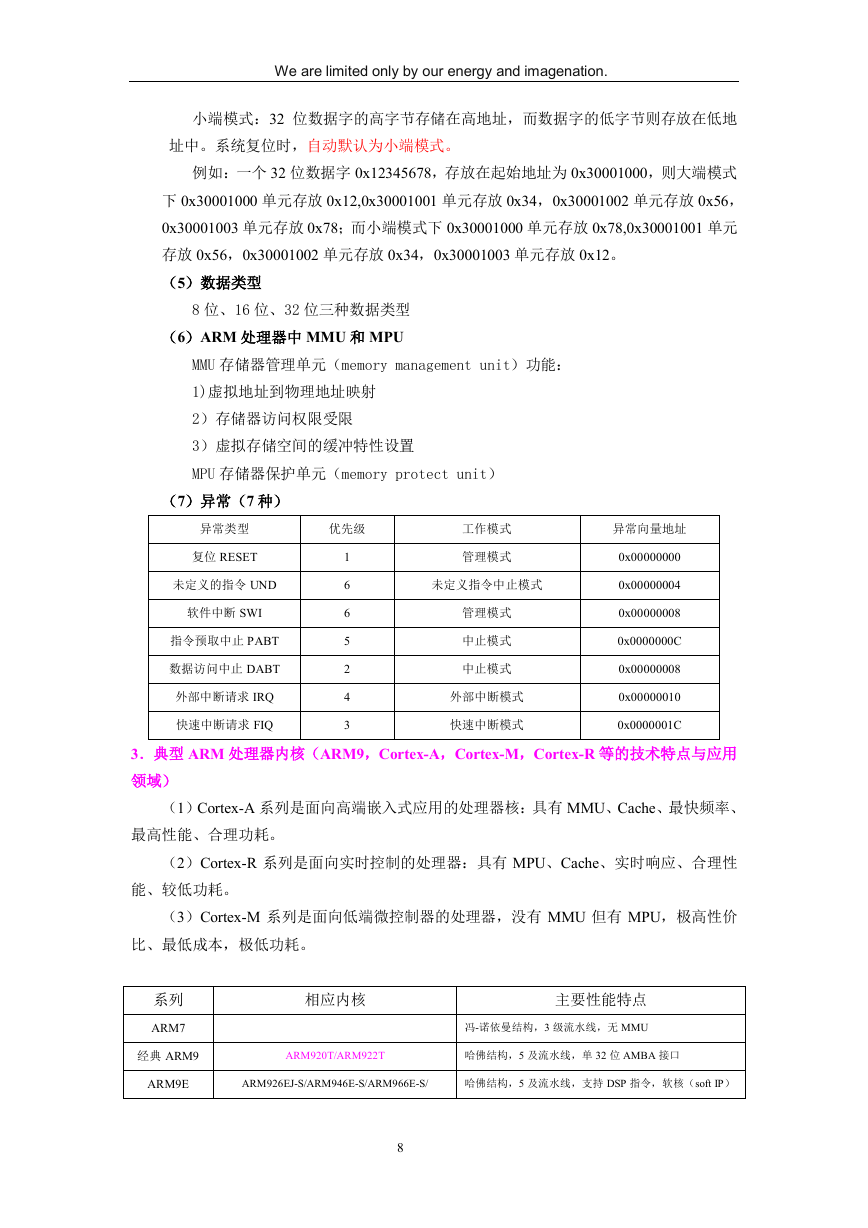

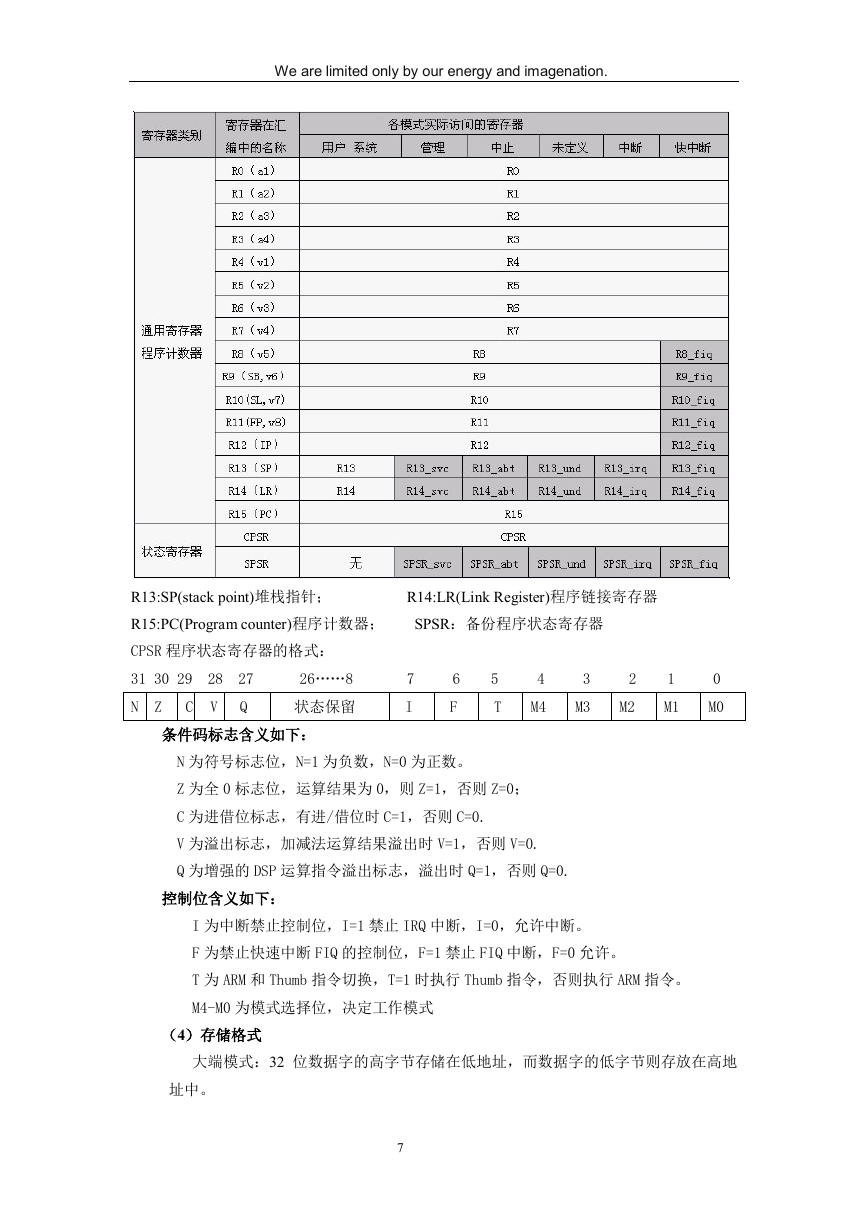

(3)寄存器组织

ARM 处理器共有 37 种寄存器,包括 31 个通用寄存器(含 PC)和 6 个状态寄存器。

无论何种模式,R15 均作为 PC 使用;CPSR 为当前程序状态寄存器;R7-R0 为公用的通用寄

存器。所有通用寄存器均为 32 位结构。

6

�

We are limited only by our energy and imagenation.

R13:SP(stack point)堆栈指针;

R14:LR(Link Register)程序链接寄存器

R15:PC(Program counter)程序计数器;

SPSR:备份程序状态寄存器

CPSR 程序状态寄存器的格式:

31 30 29 28 27 26……8 7 6 5 4 3 2 1 0

N Z

C V Q

状态保留

I

F

T

M4

M3

M2

M1

M0

条件码标志含义如下:

N 为符号标志位,N=1 为负数,N=0 为正数。

Z 为全 0 标志位,运算结果为 0,则 Z=1,否则 Z=0;

C 为进借位标志,有进/借位时 C=1,否则 C=0.

V 为溢出标志,加减法运算结果溢出时 V=1,否则 V=0.

Q 为增强的 DSP 运算指令溢出标志,溢出时 Q=1,否则 Q=0.

控制位含义如下:

I 为中断禁止控制位,I=1 禁止 IRQ 中断,I=0,允许中断。

F 为禁止快速中断 FIQ 的控制位,F=1 禁止 FIQ 中断,F=0 允许。

T 为 ARM 和 Thumb 指令切换,T=1 时执行 Thumb 指令,否则执行 ARM 指令。

M4-M0 为模式选择位,决定工作模式

(4)存储格式

大端模式:32 位数据字的高字节存储在低地址,而数据字的低字节则存放在高地

址中。

7

�

We are limited only by our energy and imagenation.

小端模式:32 位数据字的高字节存储在高地址,而数据字的低字节则存放在低地

址中。系统复位时,自动默认为小端模式。

例如:一个 32 位数据字 0x12345678,存放在起始地址为 0x30001000,则大端模式

下 0x30001000 单元存放 0x12,0x30001001 单元存放 0x34,0x30001002 单元存放 0x56,

0x30001003 单元存放 0x78;而小端模式下 0x30001000 单元存放 0x78,0x30001001 单元

存放 0x56,0x30001002 单元存放 0x34,0x30001003 单元存放 0x12。

(5)数据类型

8 位、16 位、32 位三种数据类型

(6)ARM 处理器中 MMU 和 MPU

MMU 存储器管理单元(memory management unit)功能:

1)虚拟地址到物理地址映射

2)存储器访问权限受限

3)虚拟存储空间的缓冲特性设置

MPU 存储器保护单元(memory protect unit)

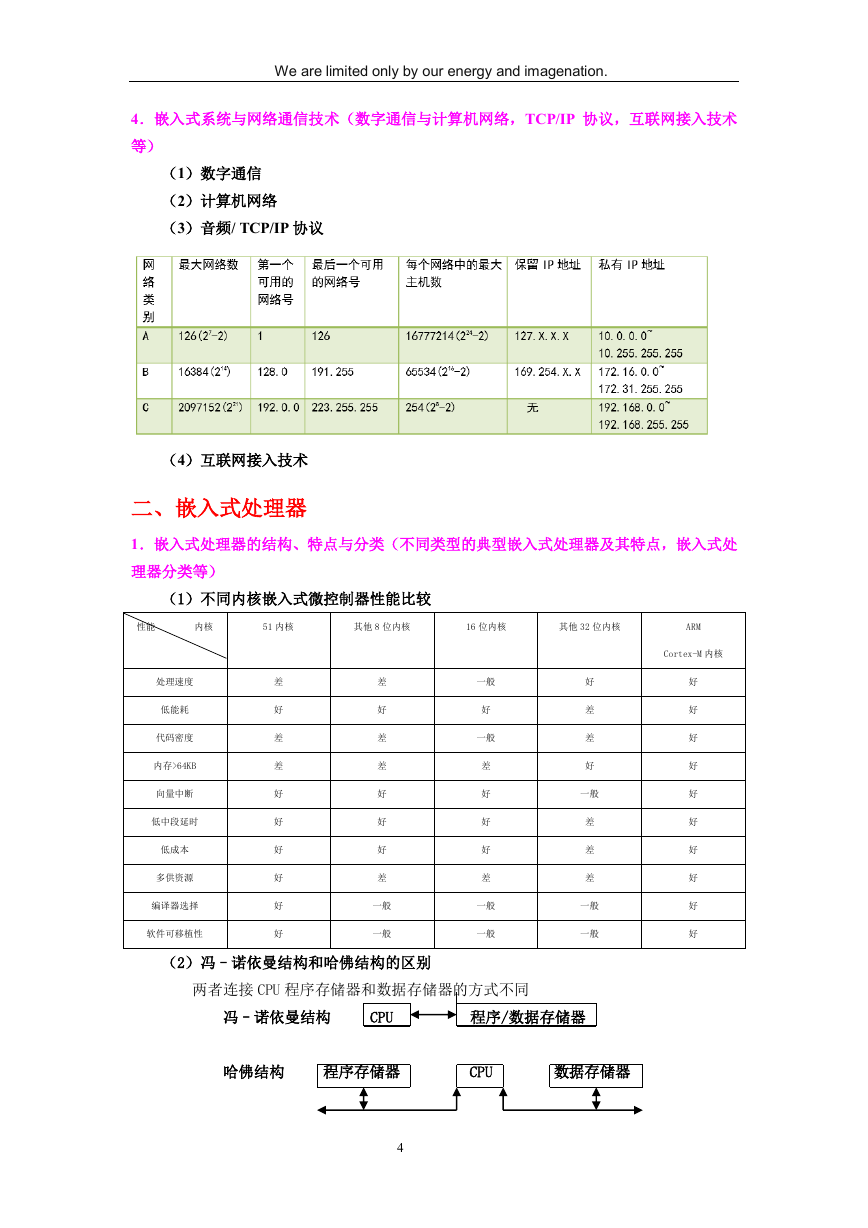

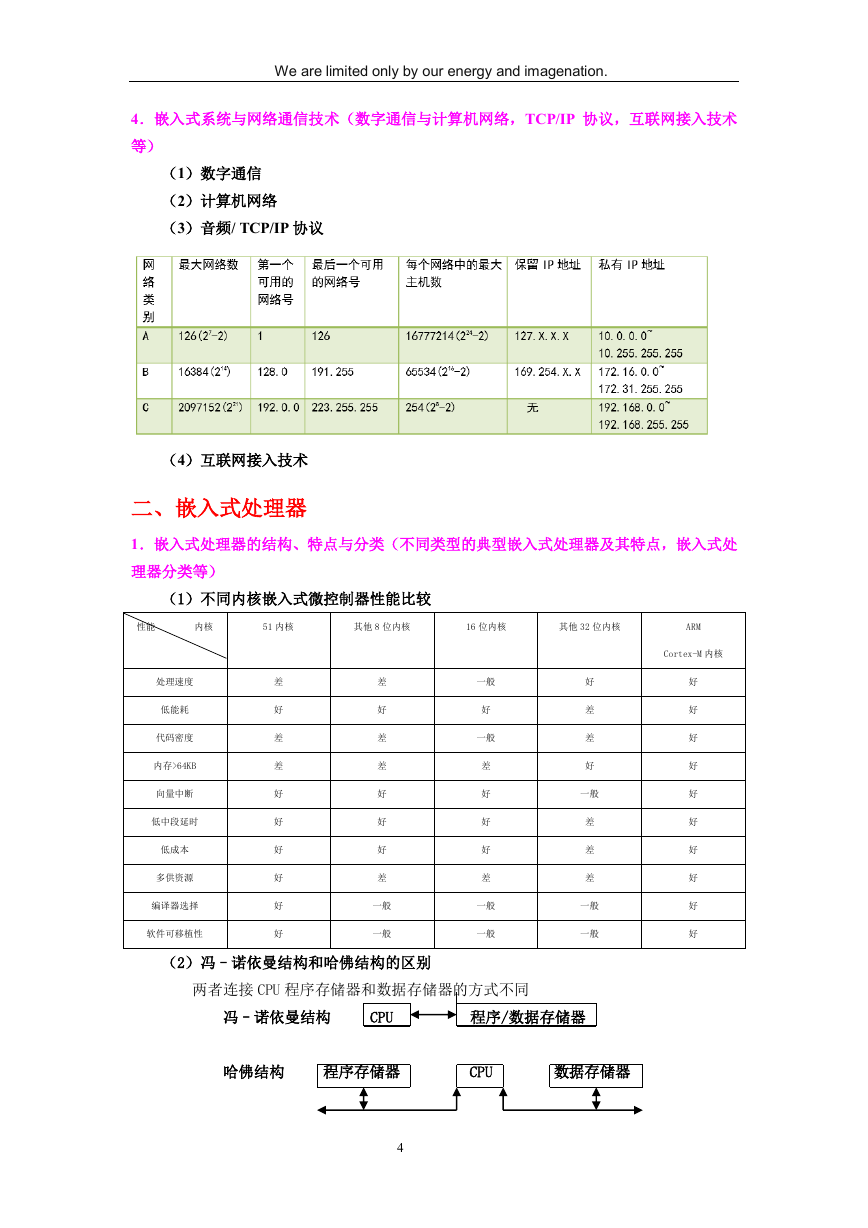

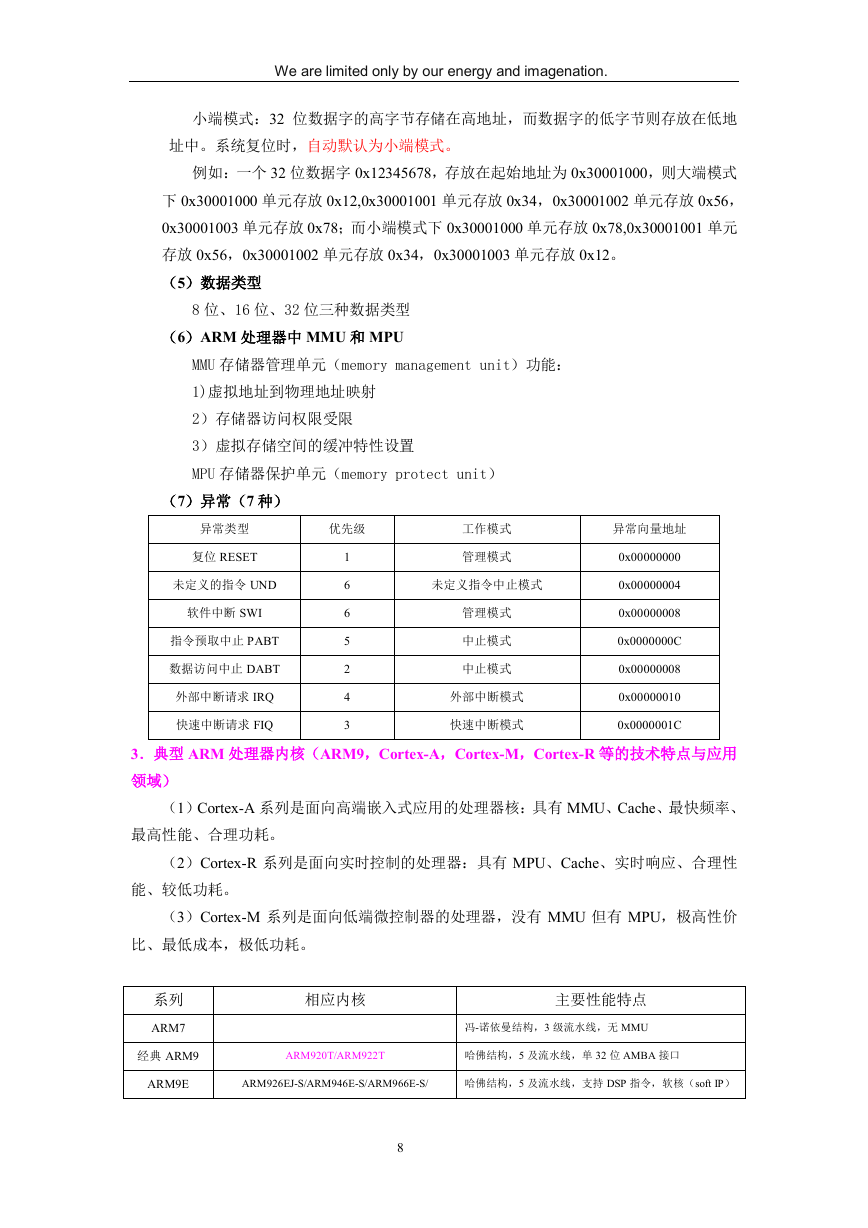

(7)异常(7 种)

异常类型

优先级

复位 RESET

未定义的指令 UND

软件中断 SWI

指令预取中止 PABT

数据访问中止 DABT

外部中断请求 IRQ

快速中断请求 FIQ

1

6

6

5

2

4

3

工作模式

管理模式

异常向量地址

0x00000000

未定义指令中止模式

0x00000004

管理模式

中止模式

中止模式

外部中断模式

快速中断模式

0x00000008

0x0000000C

0x00000008

0x00000010

0x0000001C

3.典型 ARM 处理器内核(ARM9,Cortex-A,Cortex-M,Cortex-R 等的技术特点与应用

领域)

(1)Cortex-A 系列是面向高端嵌入式应用的处理器核:具有 MMU、Cache、最快频率、

最高性能、合理功耗。

(2)Cortex-R 系列是面向实时控制的处理器:具有 MPU、Cache、实时响应、合理性

能、较低功耗。

(3)Cortex-M 系列是面向低端微控制器的处理器,没有 MMU 但有 MPU,极高性价

比、最低成本,极低功耗。

系列

ARM7

相应内核

主要性能特点

冯-诺依曼结构,3 级流水线,无 MMU

经典 ARM9

ARM920T/ARM922T

哈佛结构,5 及流水线,单 32 位 AMBA 接口

ARM9E

ARM926EJ-S/ARM946E-S/ARM966E-S/

哈佛结构,5 及流水线,支持 DSP 指令,软核(soft IP)

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc