2

山西电子技术

2010年第 4期

文章编号 : 1674

4578 (2010) 04

0019

03

应用实践

一种基于 FPGA的正弦波信号发生器的设计

薛鹏飞 1 , 师 晶 2

(1. 中北大学信息与通信工程学院 ,山西 太原 030051; 2. 山西航天机电设备研究所 ,山西 太谷 030800)

摘 要 :现代测试领域中 ,经常需要信号发生器提供多种多样的的测试信号去检验实际电路中存在的设计问

题 。传统的信号发生器多采用模拟电路搭建 。以正弦波信号发生器为例 ,结合 DDS直接数字合成技术 ,基于 FP

GA设计其他外围电路构成正弦波信号发生器 。相比传统的模拟信号发生器 ,该电路具有设计简单 ,升级容易 ,波

形稳定等特点 。

关键词 : FPGA; DDS; 正弦波信号发生器

中图分类号 : TP346 文献标识码 : A

0 引言

信号发生器是用来为各种电路提供测试信号的仪器 ,在

工程应用和测试领域有着非常广泛的应用 。目前传统的信

号发生器是使用模拟电路或者专用芯片搭建而成 ,但是存在

频率不高 ,稳定性较差 ,且不易扩展和调试的缺陷 ;而采用

DDS直接数字频率合成技术设计的信号发生器 ,改变了以往

的设计思路 ,在精度 、灵活性上大大超越了模拟信号发生器 。

随着可编程逻辑器件 FPGA 的迅速发展 [ 1 ] ,基于 FPGA 控制

的 DDS信号发生器使得电路设计更加简单 ,而且通过预留

的端口 可 轻 松 进 行 二 次 开 发 。本 文 通 过 A ltera 公 司 的

EPF10K10LC84

1 系统硬件结构

4芯片 ,成功实现了正弦波信号发生器 。

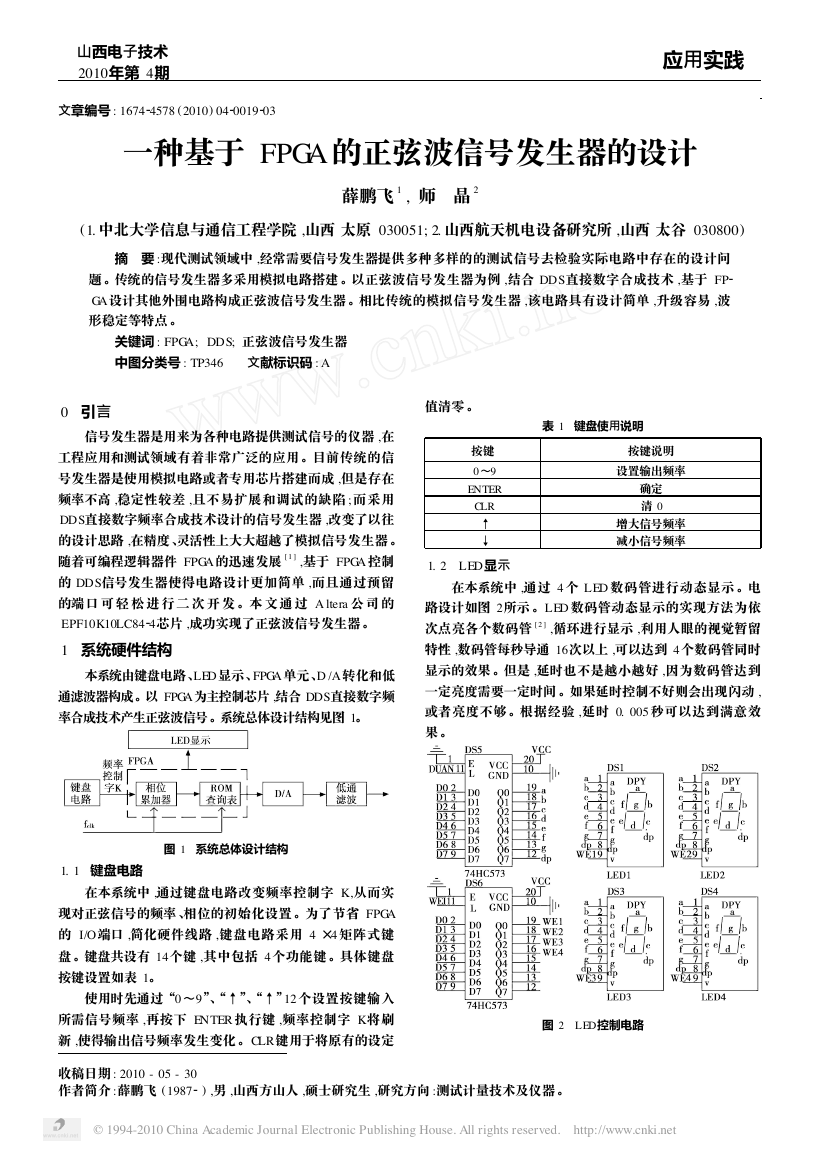

本系统由键盘电路、LED显示、FPGA单元、D /A转化和低

通滤波器构成。以 FPGA为主控制芯片 ,结合 DDS直接数字频

率合成技术产生正弦波信号。系统总体设计结构见图 1。

值清零 。

表 1 键盘使用说明

按键

0~9

ENTER

CLR

↑

↓

1. 2 LED显示

按键说明

设置输出频率

确定

清 0

增大信号频率

减小信号频率

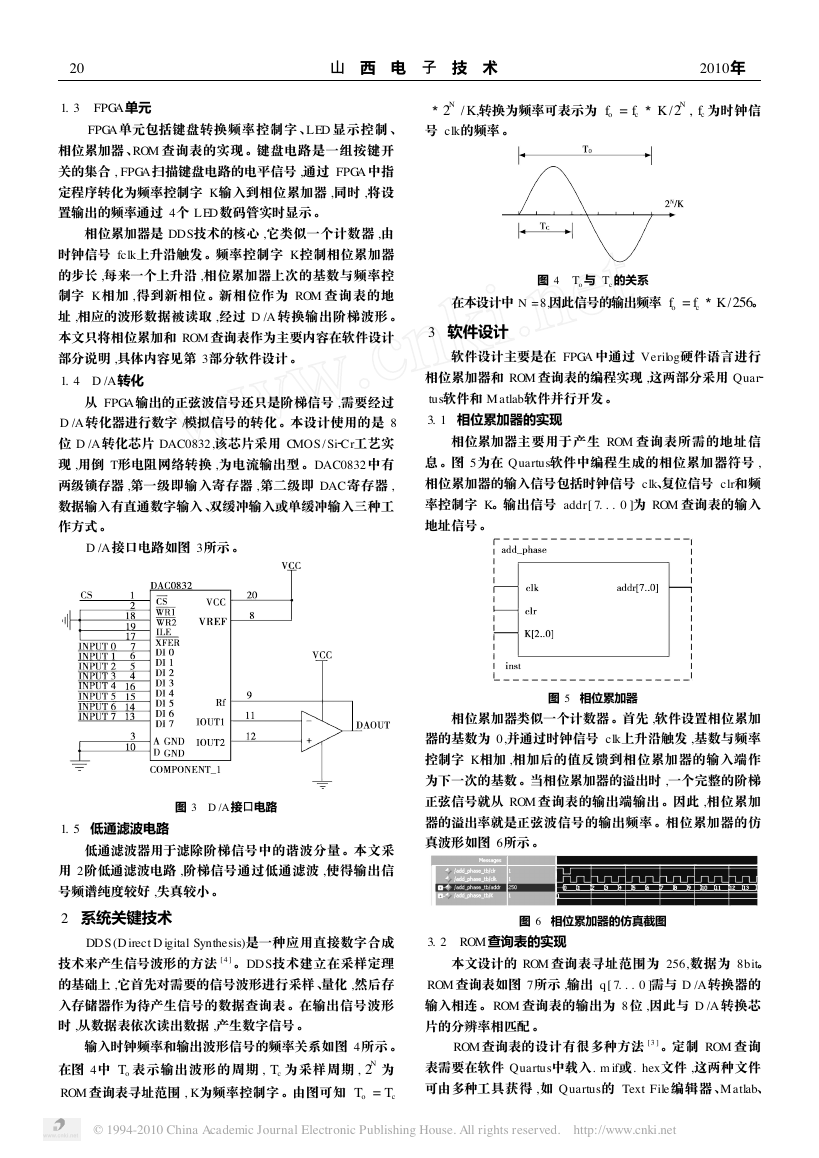

在本系统中 ,通过 4 个 LED 数码管进行动态显示 。电

路设计如图 2所示 。LED 数码管动态显示的实现方法为依

次点亮各个数码管 [ 2 ] ,循环进行显示 ,利用人眼的视觉暂留

特性 ,数码管每秒导通 16次以上 ,可以达到 4个数码管同时

显示的效果 。但是 ,延时也不是越小越好 ,因为数码管达到

一定亮度需要一定时间 。如果延时控制不好则会出现闪动 ,

或者亮度不够 。根据经验 ,延时 0. 005 秒可以达到满意效

果 。

图 1 系统总体设计结构

1. 1 键盘电路

在本系统中 ,通过键盘电路改变频率控制字 K,从而实

现对正弦信号的频率 、相位的初始化设置 。为了节省 FPGA

的 I/O端口 ,简化硬件线路 ,键盘电路采用 4 ×4 矩阵式键

盘 。键盘共设有 14个键 ,其中包括 4个功能键 。具体键盘

按键设置如表 1。

使用时先通过“0~9”、“↑”、“↑”12个设置按键输入

所需信号频率 ,再按下 ENTER 执行键 ,频率控制字 K将刷

新 ,使得输出信号频率发生变化 。CLR键用于将原有的设定

图 2 LED控制电路

收稿日期 : 2010 - 05 - 30

作者简介 :薛鹏飞 (1987

) ,男 ,山西方山人 ,硕士研究生 ,研究方向 :测试计量技术及仪器 。

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

02

1. 3 FPGA单元

山 西 电 子 技 术 2010年

2N / K,转换为频率可表示为 fo = fc

K /2N , fc 为时钟信

FPGA单元包括键盘转换频率控制字 、LED 显示控制 、

号 clk的频率 。

相位累加器 、ROM 查询表的实现 。键盘电路是一组按键开

关的集合 , FPGA扫描键盘电路的电平信号 ,通过 FPGA 中指

定程序转化为频率控制字 K输入到相位累加器 ,同时 ,将设

置输出的频率通过 4个 LED数码管实时显示 。

相位累加器是 DDS技术的核心 ,它类似一个计数器 ,由

时钟信号 fclk上升沿触发 。频率控制字 K控制相位累加器

的步长 ,每来一个上升沿 ,相位累加器上次的基数与频率控

制字 K相加 ,得到新相位 。新相位作为 ROM 查询表的地

址 ,相应的波形数据被读取 ,经过 D /A 转换输出阶梯波形 。

本文只将相位累加和 ROM 查询表作为主要内容在软件设计

部分说明 ,具体内容见第 3部分软件设计 。

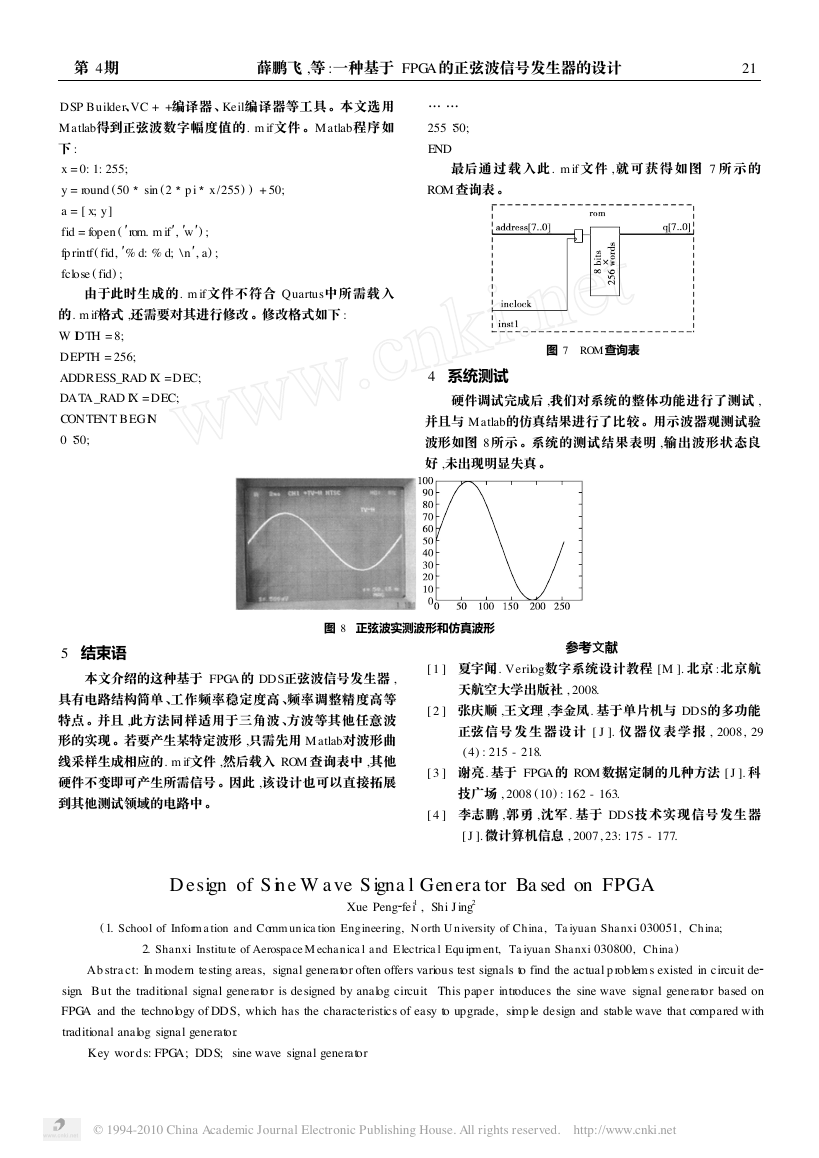

1. 4 D /A转化

从 FPGA输出的正弦波信号还只是阶梯信号 ,需要经过

D /A转化器进行数字 /模拟信号的转化 。本设计使用的是 8

位 D /A转化芯片 DAC0832,该芯片采用 CMOS/ Si

Cr工艺实

现 ,用倒 T形电阻网络转换 ,为电流输出型 。DAC0832中有

两级锁存器 ,第一级即输入寄存器 ,第二级即 DAC寄存器 ,

数据输入有直通数字输入 、双缓冲输入或单缓冲输入三种工

作方式 。

D /A接口电路如图 3所示 。

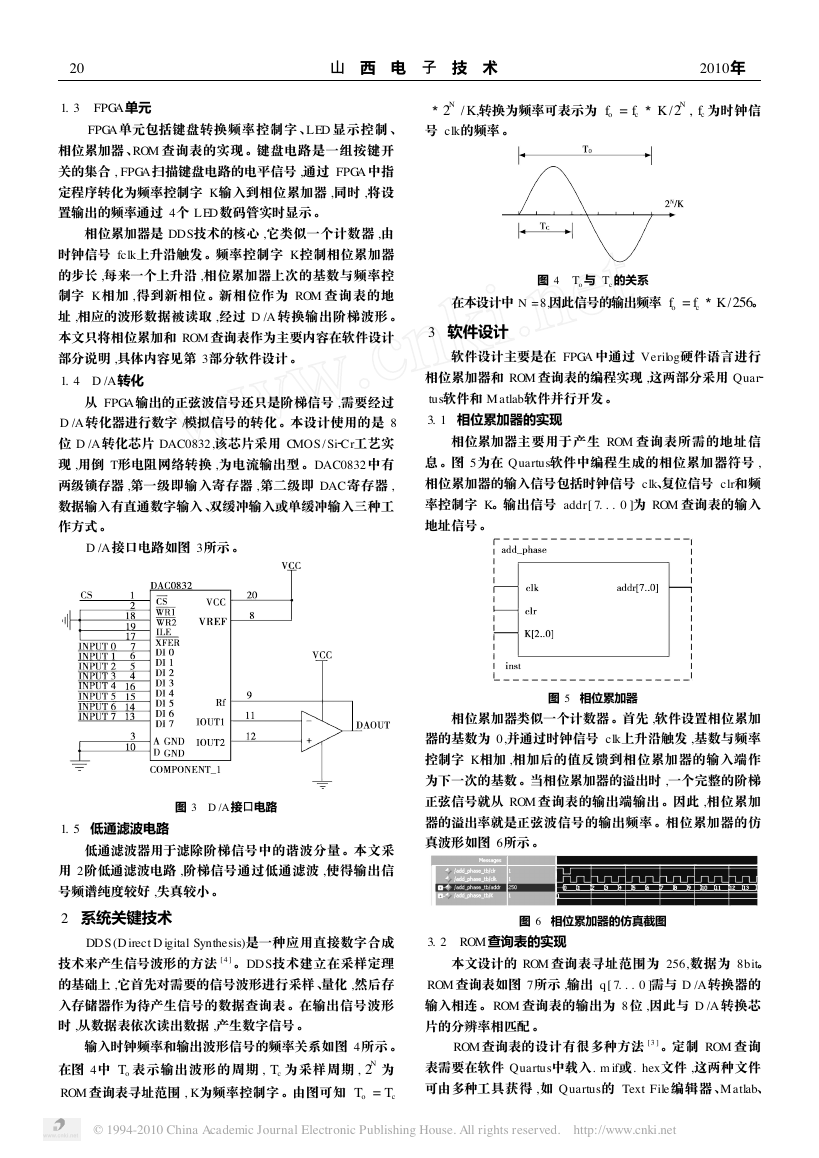

图 4 To 与 Tc 的关系

在本设计中 N =8,因此信号的输出频率 fo = fc

K /256。

3 软件设计

软件设计主要是在 FPGA 中通过 Verilog硬件语言进行

相位累加器和 ROM 查询表的编程实现 ,这两部分采用 Quar

tus软件和 M atlab软件并行开发 。

3. 1 相位累加器的实现

相位累加器主要用于产生 ROM 查询表所需的地址信

息 。图 5为在 Quartus软件中编程生成的相位累加器符号 ,

相位累加器的输入信号包括时钟信号 clk、复位信号 clr和频

率控制字 K。输出信号 addr[ 7. . . 0 ]为 ROM 查询表的输入

地址信号 。

图 3 D /A接口电路

1. 5 低通滤波电路

低通滤波器用于滤除阶梯信号中的谐波分量 。本文采

用 2阶低通滤波电路 ,阶梯信号通过低通滤波 ,使得输出信

号频谱纯度较好 ,失真较小 。

2 系统关键技术

DDS(D irect D igital Synthesis)是一种应用直接数字合成

技术来产生信号波形的方法 [ 4 ] 。DDS技术建立在采样定理

的基础上 ,它首先对需要的信号波形进行采样 、量化 ,然后存

入存储器作为待产生信号的数据查询表 。在输出信号波形

时 ,从数据表依次读出数据 ,产生数字信号 。

输入时钟频率和输出波形信号的频率关系如图 4所示 。

在图 4中 To 表示输出波形的周期 , Tc 为采样周期 , 2N 为

ROM 查询表寻址范围 , K为频率控制字 。由图可知 To = Tc

图 5 相位累加器

相位累加器类似一个计数器 。首先 ,软件设置相位累加

器的基数为 0,并通过时钟信号 clk上升沿触发 ,基数与频率

控制字 K相加 ,相加后的值反馈到相位累加器的输入端作

为下一次的基数 。当相位累加器的溢出时 ,一个完整的阶梯

正弦信号就从 ROM 查询表的输出端输出 。因此 ,相位累加

器的溢出率就是正弦波信号的输出频率 。相位累加器的仿

真波形如图 6所示 。

图 6 相位累加器的仿真截图

3. 2 ROM 查询表的实现

本文设计的 ROM 查询表寻址范围为 256,数据为 8bit。

ROM 查询表如图 7所示 ,输出 q[ 7. . . 0 ]需与 D /A转换器的

输入相连 。ROM 查询表的输出为 8位 ,因此与 D /A 转换芯

片的分辨率相匹配 。

ROM 查询表的设计有很多种方法 [ 3 ] 。定制 ROM 查询

表需要在软件 Quartus中载入. m if或. hex文件 ,这两种文件

可由多种工具获得 ,如 Quartus的 Text File编辑器 、M atlab、

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2

第 4期 薛鹏飞 ,等 :一种基于 FPGA的正弦波信号发生器的设计

12

2

DSP Builder、VC + +编译器 、Keil编译器等工具 。本文选用

Matlab得到正弦波数字幅度值的. m if文件 。M atlab程序如

下 :

x = 0: 1: 255;

y = round (50

a = [ x; y]

fid = fopen ( ′rom. m if′, ′w′) ;

fp rintf( fid, ′% d: % d; \ n′, a) ;

fclose ( fid) ;

x/255) ) + 50;

sin (2

p i

… …

255∶50;

END

最后通过载入此. m if文件 , 就可获得如图 7 所 示的

ROM 查询表 。

由于此时生成的. m if文件不符合 Quartus中所需载入

的. m if格式 ,还需要对其进行修改 。修改格式如下 :

W IDTH = 8;

DEPTH = 256;

ADDRESS_RAD IX =DEC;

DATA_RAD IX =DEC;

CONTENT BEGIN

0∶50;

图 7 ROM查询表

4 系统测试

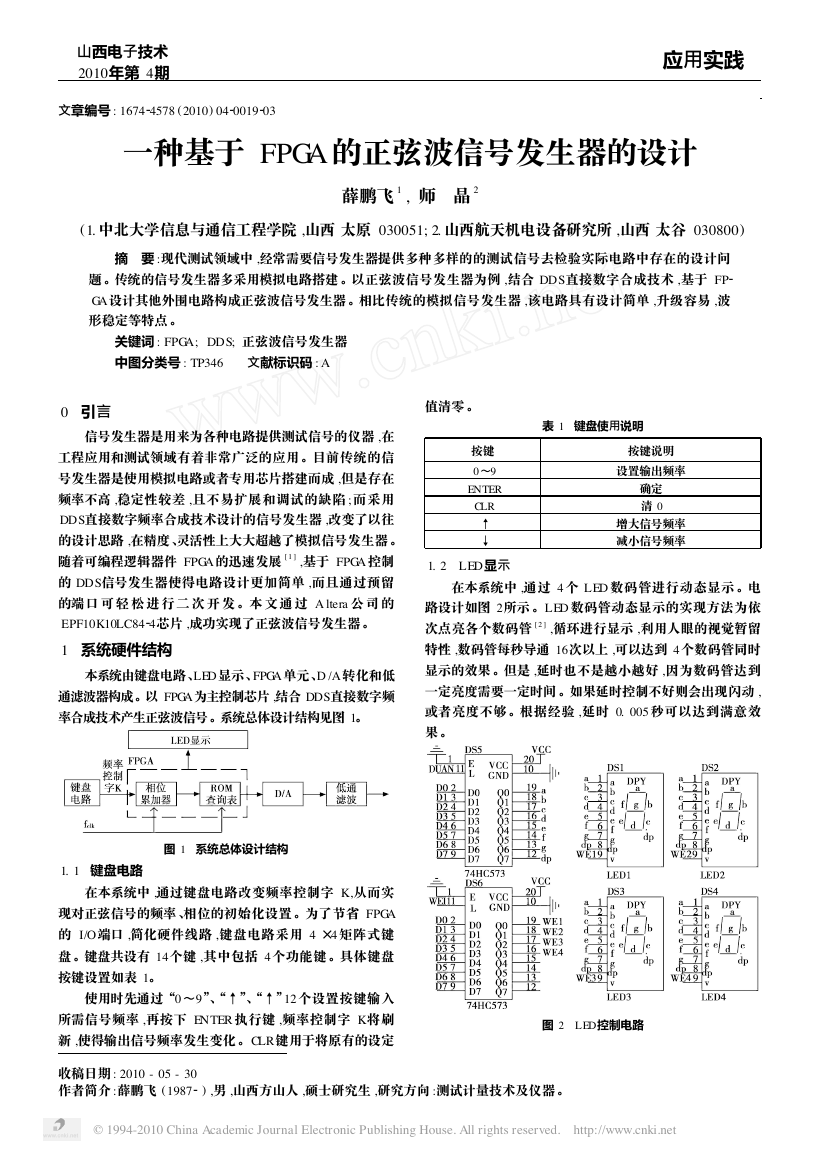

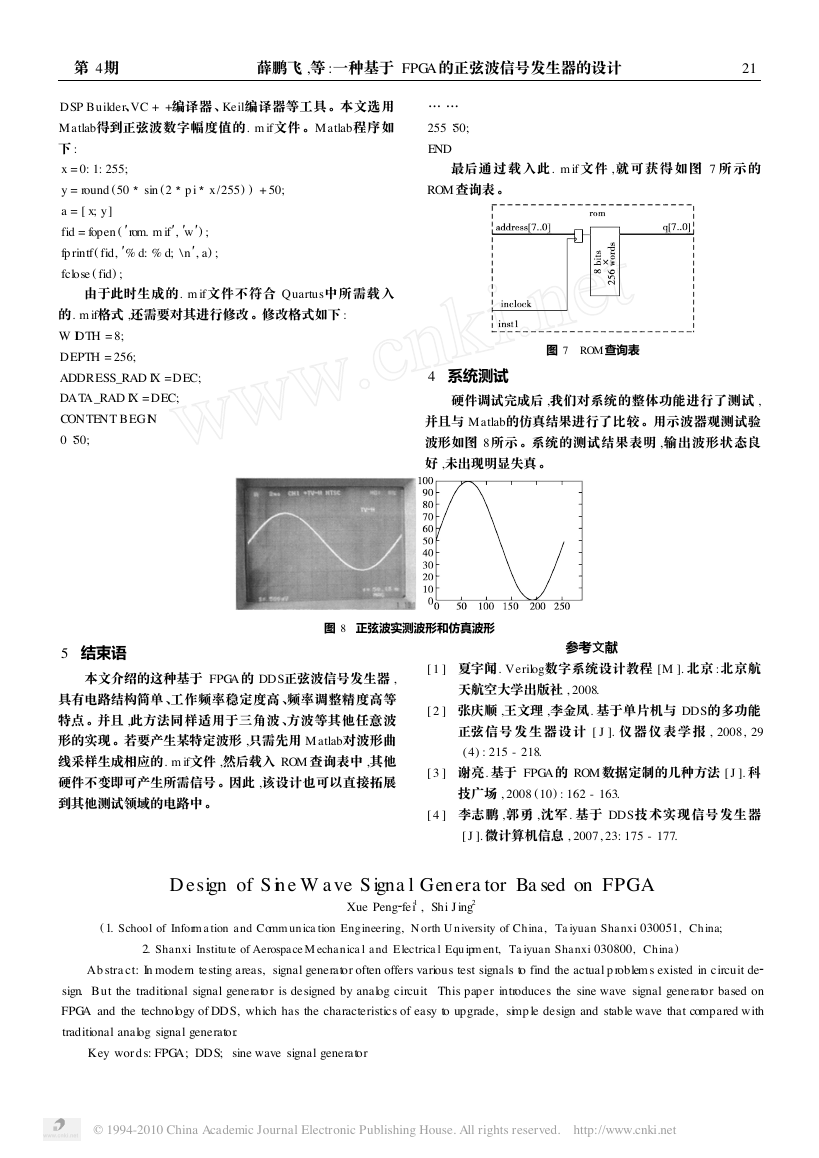

硬件调试完成后 ,我们对系统的整体功能进行了测试 ,

并且与 Matlab的仿真结果进行了比较 。用示波器观测试验

波形如图 8所示 。系统的测试结果表明 ,输出波形状态良

好 ,未出现明显失真 。

图 8 正弦波实测波形和仿真波形

5 结束语

本文介绍的这种基于 FPGA的 DDS正弦波信号发生器 ,

具有电路结构简单 、工作频率稳定度高 、频率调整精度高等

特点 。并且 ,此方法同样适用于三角波 、方波等其他任意波

形的实现 。若要产生某特定波形 ,只需先用 M atlab对波形曲

线采样生成相应的. m if文件 ,然后载入 ROM 查询表中 ,其他

硬件不变即可产生所需信号 。因此 ,该设计也可以直接拓展

到其他测试领域的电路中 。

参考文献

[ 1 ] 夏宇闻. Verilog数字系统设计教程 [M ]. 北京 :北京航

天航空大学出版社 , 2008.

[ 2 ] 张庆顺 ,王文理 ,李金凤. 基于单片机与 DDS的多功能

正弦信号 发 生 器 设 计 [ J ]. 仪 器 仪 表 学 报 , 2008, 29

(4) : 215 - 218.

[ 3 ] 谢亮. 基于 FPGA的 ROM 数据定制的几种方法 [ J ]. 科

技广场 , 2008 (10) : 162 - 163.

[ 4 ] 李志鹏 ,郭勇 ,沈军. 基于 DDS技术实现信号发生器

[ J ]. 微计算机信息 , 2007, 23: 175 - 177.

D esign of S ine W ave S igna l Genera tor Ba sed on FPGA

Xue Peng

fei1 , Shi J ing2

( 1. S chool of Inform ation and Comm un ica tion Engineering, N orth U n iversity of China, Ta iyuan S hanxi 030051, China;

2. Shanx i Institute of A erospace M echanical and E lectrical Equ ipm ent, Taiyuan Shanx i 030800, China)

Abstract: In modern testing areas, signal generator often offers various test signals to find the actual p roblem s existed in circuit de

sign. But the traditional signal generator is designed by analog circuit. This paper introduces the sine wave signal generator based on

FPGA and the technology of DDS, which has the characteristics of easy to upgrade, simp le design and stable wave that compared with

traditional analog signal generator.

Key words: FPGA; DDS; sine wave signal generator

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc